JP5166017B2 - セラミックス配線基板の製造方法、およびそれを用いた半導体装置の製造方法 - Google Patents

セラミックス配線基板の製造方法、およびそれを用いた半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5166017B2 JP5166017B2 JP2007501552A JP2007501552A JP5166017B2 JP 5166017 B2 JP5166017 B2 JP 5166017B2 JP 2007501552 A JP2007501552 A JP 2007501552A JP 2007501552 A JP2007501552 A JP 2007501552A JP 5166017 B2 JP5166017 B2 JP 5166017B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- solder

- alloy

- solder layer

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/24—Reinforcing the conductive pattern

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73257—Bump and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/09—Use of materials for the conductive, e.g. metallic pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3457—Solder materials or compositions; Methods of application thereof

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

- Y10T29/49165—Manufacturing circuit on or in base by forming conductive walled aperture in base

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Die Bonding (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Manufacturing Of Printed Wiring (AREA)

Description

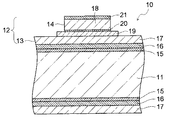

まず、セラミックス基板11として直径75mm×高さ0.2mmの窒化アルミニウム質焼結体製基板を用意した。この窒化アルミニウム基板11を洗浄した後、その表面にスパッタ法により厚さ0.1μmのTi膜から下地金属層15、厚さ0.2μmのPt膜からなる第1の拡散防止層16、主導体層として厚さ0.5μmの第1のAu層17を順に積層した。

第2の拡散防止層19の構成材料を変更する以外は、上記した実施例1〜7と同様にして試料を作製し、後述する特性評価に供した。実施例8〜11における第2の拡散防止層19の構成材料は表1に示す通りである。

半田層18の組成を変更する以外は、上記した実施例1〜7と同様にして試料を作製し、後述する特性評価に供した。実施例12〜16における半田層18の組成は表1に示す通りである。

空孔抑制層20の構成材料および厚さを変更する以外は、上記した実施例1〜7と同様にして試料を作製し、後述する特性評価に供した。実施例17〜20における空孔抑制層20の構成材料および厚さは表1に示す通りである。

空孔抑制層20の形成を省略する以外は、上記した実施例1〜7と同様にして試料を作製し、後述する特性評価に供した。なお、比較例1は半田層18に70質量%Au−30質量%Sn組成の合金を適用した例である。比較例2は半田層18に82質量%Au−18質量%Sn組成の合金を適用した例である。比較例3は半田層18に95質量%Sn−5質量%Ag組成の合金を適用した例である。

Au−Sn半田合金層を有する例については、330〜350℃程度の温度に保持したヒータブロック上に各配線基板を置き、約5秒後に配線基板上にSiチップを載置して接合した。Ag−Sn半田合金層を有する例では250〜260℃程度の温度に加熱し、Cu−Sn半田合金層を有する例では240〜260℃程度の温度に加熱して、それぞれSiチップを接合した。Siチップは配線基板との接合面に厚さ0.05μmのTi膜、厚さ0.1μmのPt膜、厚さ1.0μmのAu膜が順に被着形成されたものであり、その形状は0.9mm×0.3mm×高さ0.4mmとした。Siチップの搭載は各例に対してそれぞれ4個の配線基板について実施した。

上記した空孔の有無の評価と同様にして、各例の配線基板上にSiチップを搭載した後、Siチップの横方向から荷重を加えるシェアテストを行った。シェアテストは各例に対して6個ずつ実施した。シェアテストにおいて、密着性が良好な場合はSiチップ内部での破壊モードを示す。この際、Siの破壊強度は材料強度によるので、シェア強度の数値はばらつきが大きいものとなる。そこで、密着性の判断は一定の強度(当該サイズでは1200kgf)以上の値でSi破壊モードを示す場合に密着性が良好と判断し、全ての試料が良好なものを○、3〜5個の試料が良好なものを△、良好な試料が2個以下の場合を×とした。シェア強度の平均値と併せて評価結果を表2に示す。

上記した実施例と同様にして、窒化アルミニウム基板11上に厚さ0.1μmのTi膜からなる下地金属層15、厚さ0.2μmのPt膜からなる第1の拡散防止層16、主導体層として厚さ0.5μmの第1のAu層17を順に積層した。次いで、主導体層としての第1のAu層17上に、真空蒸着法により厚さ0.1μmのPt膜からなる第2の拡散防止層19、厚さ100nmのAu膜からなる空孔抑制層20、厚さ2μmの65質量%Au−35質量%Sn組成のSn合金膜からなる半田層18を順に形成した。

上記した空孔の有無評価と同様にして、各例の配線基板をヒータブロック上に置き、表面に酸化膜ができないように不活性ガスを吹き付けながら、半田層表面の光沢変化を約60秒間観察することによって、半田層の溶融性(濡れ性)を評価した。これは半田層の融点が保持温度より上昇した場合には高融点相が析出し、表面光沢が弱くなる現象を利用したものである。半田層の完全溶融時間の判定は表面光沢が維持された時間で評価した。

上記した半田層の完全溶融時間試験を実施した各試料について、金属顕微鏡(100倍)で半田層の濡れ広がり状態を観察、評価した。半田層の濡れ広がり領域が第2の拡散防止層上のみである場合を○、半田層の濡れ広がり領域が第1のAu層上まではみ出した場合を×として評価した。

Claims (2)

- 配線層を有するセラミックス配線基板を製造する方法であって、

セラミックス基板の表面に下地金属層、第1の拡散防止層および第1のAu層を順に積層して、前記配線層における配線部を形成する工程と、

前記配線部上に第2の拡散防止層、空孔抑制層および少なくともSnを15〜99.3質量%含むSn合金半田層を順に積層して、前記配線層における接続部を形成する工程と

を具備し、

前記下地金属層はTiからなり、

前記第1および第2の拡散防止層は、Ptまたはこれを基とする合金からなり、前記第1の拡散防止層は0.1μm以上0.4μm以下の範囲の厚さを有し、前記第2の拡散防止層は0.05μm以上1μm以下の範囲の厚さを有し、かつ前記第2の拡散防止層はその外周部が前記半田層の端部から1μm以上100μm以下の範囲ではみ出した形状であり、

前記空孔抑制層は、AuまたはAuを85質量%以上含むAu−Sn合金からなり、30nm以上500nm以下の範囲の厚さを有し、

前記半田層はAu、Ag、Bi、およびCuから選ばれる少なくとも1種を含むSn合金からなり、かつ1μm以上5μm以下の範囲の厚さを有し、

前記配線部および前記接続部はPVD法、CVD法またはめっき法により形成される

ことを特徴とするセラミックス配線基板の製造方法。 - 請求項1記載の製造方法によりセラミックス配線基板を製造した後、前記半田層を加熱して、前記半田層を介して半導体素子を電気的および機械的に接続することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007501552A JP5166017B2 (ja) | 2005-02-07 | 2006-01-30 | セラミックス配線基板の製造方法、およびそれを用いた半導体装置の製造方法 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005030092 | 2005-02-07 | ||

| JP2005030092 | 2005-02-07 | ||

| JP2007501552A JP5166017B2 (ja) | 2005-02-07 | 2006-01-30 | セラミックス配線基板の製造方法、およびそれを用いた半導体装置の製造方法 |

| PCT/JP2006/301415 WO2006082770A1 (ja) | 2005-02-07 | 2006-01-30 | セラミックス配線基板とその製造方法、およびそれを用いた半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012193144A Division JP5417505B2 (ja) | 2005-02-07 | 2012-09-03 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2006082770A1 JPWO2006082770A1 (ja) | 2008-06-26 |

| JP5166017B2 true JP5166017B2 (ja) | 2013-03-21 |

Family

ID=36777154

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007501552A Active JP5166017B2 (ja) | 2005-02-07 | 2006-01-30 | セラミックス配線基板の製造方法、およびそれを用いた半導体装置の製造方法 |

| JP2012193144A Active JP5417505B2 (ja) | 2005-02-07 | 2012-09-03 | 半導体装置 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012193144A Active JP5417505B2 (ja) | 2005-02-07 | 2012-09-03 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7795732B2 (ja) |

| JP (2) | JP5166017B2 (ja) |

| TW (1) | TW200637441A (ja) |

| WO (1) | WO2006082770A1 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008026839A1 (de) * | 2007-12-20 | 2009-07-02 | Osram Opto Semiconductors Gmbh | Verfahren zum Herstellen eines optoelektronischen Bauelements in Dünnschichttechnik |

| TWI436382B (zh) * | 2009-04-02 | 2014-05-01 | Nat Univ Tsing Hua | 應用磁力控制可活動式電感器的方法及其裝置 |

| CN103140026B (zh) * | 2013-02-04 | 2015-12-02 | 深圳市佳捷特陶瓷电路技术有限公司 | 陶瓷覆铜板及其制备方法 |

| US9676047B2 (en) | 2013-03-15 | 2017-06-13 | Samsung Electronics Co., Ltd. | Method of forming metal bonding layer and method of manufacturing semiconductor light emitting device using the same |

| DE102015108668B4 (de) * | 2015-06-02 | 2018-07-26 | Rogers Germany Gmbh | Verfahren zur Herstellung eines Verbundmaterials |

| TWI638433B (zh) * | 2017-10-24 | 2018-10-11 | 英屬維京群島商艾格生科技股份有限公司 | 元件次黏著載具及其製造方法 |

| JP7181843B2 (ja) * | 2019-07-30 | 2022-12-01 | 日本特殊陶業株式会社 | 配線基板、および配線基板の製造方法 |

| CN113905531B (zh) * | 2021-12-10 | 2022-03-01 | 四川英创力电子科技股份有限公司 | 一种印制电路板线路制作方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05190973A (ja) * | 1992-01-14 | 1993-07-30 | Toshiba Corp | 半導体レーザ用サブマウント |

| JPH11284281A (ja) * | 1998-03-30 | 1999-10-15 | Sharp Corp | 半導体レーザ装置の製造方法 |

| JP2000288770A (ja) * | 1999-03-31 | 2000-10-17 | Kyocera Corp | AuSn多層ハンダ |

| JP2002252316A (ja) * | 2001-02-26 | 2002-09-06 | Kyocera Corp | 配線基板 |

| JP2002359427A (ja) * | 2002-02-18 | 2002-12-13 | Sumitomo Electric Ind Ltd | サブマウントおよび半導体装置 |

| JP2002368020A (ja) * | 2002-04-30 | 2002-12-20 | Sumitomo Electric Ind Ltd | サブマウントおよび半導体装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2901091B2 (ja) * | 1990-09-27 | 1999-06-02 | 株式会社日立製作所 | 半導体装置 |

| US5367195A (en) * | 1993-01-08 | 1994-11-22 | International Business Machines Corporation | Structure and method for a superbarrier to prevent diffusion between a noble and a non-noble metal |

| JP3377553B2 (ja) * | 1993-05-13 | 2003-02-17 | 三菱電機株式会社 | 半導体レーザ装置 |

| US6590913B1 (en) * | 1999-05-14 | 2003-07-08 | Triquint Technology Holding Co. | Barrier layer and method of making the same |

| JP3910363B2 (ja) * | 2000-12-28 | 2007-04-25 | 富士通株式会社 | 外部接続端子 |

| JP3912130B2 (ja) * | 2002-02-18 | 2007-05-09 | 住友電気工業株式会社 | サブマウント |

| JP3982284B2 (ja) * | 2002-03-06 | 2007-09-26 | 住友電気工業株式会社 | サブマウントおよび半導体装置 |

-

2006

- 2006-01-30 US US11/815,722 patent/US7795732B2/en active Active

- 2006-01-30 JP JP2007501552A patent/JP5166017B2/ja active Active

- 2006-01-30 WO PCT/JP2006/301415 patent/WO2006082770A1/ja not_active Application Discontinuation

- 2006-02-03 TW TW095103797A patent/TW200637441A/zh unknown

-

2012

- 2012-09-03 JP JP2012193144A patent/JP5417505B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05190973A (ja) * | 1992-01-14 | 1993-07-30 | Toshiba Corp | 半導体レーザ用サブマウント |

| JPH11284281A (ja) * | 1998-03-30 | 1999-10-15 | Sharp Corp | 半導体レーザ装置の製造方法 |

| JP2000288770A (ja) * | 1999-03-31 | 2000-10-17 | Kyocera Corp | AuSn多層ハンダ |

| JP2002252316A (ja) * | 2001-02-26 | 2002-09-06 | Kyocera Corp | 配線基板 |

| JP2002359427A (ja) * | 2002-02-18 | 2002-12-13 | Sumitomo Electric Ind Ltd | サブマウントおよび半導体装置 |

| JP2002368020A (ja) * | 2002-04-30 | 2002-12-20 | Sumitomo Electric Ind Ltd | サブマウントおよび半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013016838A (ja) | 2013-01-24 |

| US7795732B2 (en) | 2010-09-14 |

| JP5417505B2 (ja) | 2014-02-19 |

| WO2006082770A1 (ja) | 2006-08-10 |

| TW200637441A (en) | 2006-10-16 |

| TWI312647B (ja) | 2009-07-21 |

| US20090050920A1 (en) | 2009-02-26 |

| JPWO2006082770A1 (ja) | 2008-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5417505B2 (ja) | 半導体装置 | |

| KR100940164B1 (ko) | 서브마운트 및 반도체 장치 | |

| JP5688412B2 (ja) | 半導体コンポーネント配列体の対向する電気的接続部を熱的に接触させる方法 | |

| WO2004015756A1 (ja) | サブマウントおよび半導体装置 | |

| JP4814503B2 (ja) | 半導体素子とその製造方法、及び電子部品ユニット | |

| TWI440068B (zh) | 基材接合方法以及半導體元件 | |

| JP2002134822A (ja) | 半導体発光装置およびその製造方法 | |

| JP7248774B2 (ja) | 半導体チップを基板の上に固定する方法および電子構成素子 | |

| JP4537877B2 (ja) | セラミックス配線基板とそれを用いた半導体装置 | |

| KR20040085043A (ko) | 열확산 모듈의 제조 방법 및 열확산 모듈 | |

| JP5122098B2 (ja) | メタライズ基板、半導体装置 | |

| KR20040014475A (ko) | 소자 접합용 기판 및 그 제조 방법 | |

| JP3912130B2 (ja) | サブマウント | |

| JP2023527668A (ja) | キャリア基板およびキャリア基板の製造方法 | |

| JP2006216766A (ja) | セラミックス配線基板とそれを用いた半導体装置 | |

| JP2002124524A (ja) | 配線基板 | |

| JP5693610B2 (ja) | 電子デバイスの製造方法および該方法により製造された電子デバイス | |

| CN110352502B (zh) | 用于将半导体芯片固定在导线框架上的方法和电子器件 | |

| JP7223772B2 (ja) | 電子部品の接合方法および接合構造体 | |

| JP2002151629A (ja) | 配線基板 | |

| JP2002252316A (ja) | 配線基板 | |

| JP2003258356A (ja) | サブマウント |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110614 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110812 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110812 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111220 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120220 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120903 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120910 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121220 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5166017 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |