JP5118713B2 - 回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 - Google Patents

回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 Download PDFInfo

- Publication number

- JP5118713B2 JP5118713B2 JP2010039591A JP2010039591A JP5118713B2 JP 5118713 B2 JP5118713 B2 JP 5118713B2 JP 2010039591 A JP2010039591 A JP 2010039591A JP 2010039591 A JP2010039591 A JP 2010039591A JP 5118713 B2 JP5118713 B2 JP 5118713B2

- Authority

- JP

- Japan

- Prior art keywords

- shield case

- substrate

- circuit module

- end surface

- leg

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 17

- 239000000758 substrate Substances 0.000 claims description 144

- 238000005304 joining Methods 0.000 claims description 45

- 229910000679 solder Inorganic materials 0.000 claims description 36

- 238000000034 method Methods 0.000 claims description 6

- 230000001678 irradiating effect Effects 0.000 claims description 5

- 238000005476 soldering Methods 0.000 claims 1

- 230000006870 function Effects 0.000 description 4

- 239000002184 metal Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000009545 invasion Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 238000005549 size reduction Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/552—Protection against radiation, e.g. light or electromagnetic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/04—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/10—Containers; Seals characterised by the material or arrangement of seals between parts, e.g. between cap and base of the container or between leads and walls of the container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0655—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K9/00—Screening of apparatus or components against electric or magnetic fields

- H05K9/0007—Casings

- H05K9/002—Casings with localised screening

- H05K9/0022—Casings with localised screening of components mounted on printed circuit boards [PCB]

- H05K9/0024—Shield cases mounted on a PCB, e.g. cans or caps or conformal shields

- H05K9/0026—Shield cases mounted on a PCB, e.g. cans or caps or conformal shields integrally formed from metal sheet

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16152—Cap comprising a cavity for hosting the device, e.g. U-shaped cap

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/166—Material

- H01L2924/167—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Health & Medical Sciences (AREA)

- Electromagnetism (AREA)

- Toxicology (AREA)

- Shielding Devices Or Components To Electric Or Magnetic Fields (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

- Casings For Electric Apparatus (AREA)

Description

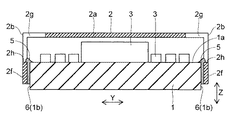

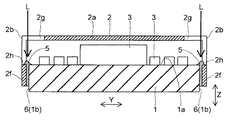

1a 実装面

1b、1c 側端面

2 シールドケース

2a 天面部

2b 側部(第1側部)

2c 側部(第2側部)

2d、2e 先端

2f 脚部

2g 開口部

2h 面

3 電子部品

5 半田(接合部材)

6 端面スルーホール

11 回路モジュール

Claims (10)

- 実装面および前記実装面に繋がる側端面を有し、前記実装面に電子部品が実装される基板と、

天面部および前記天面部の外周に立設された複数の側部を有するシールドケースと、

前記基板と前記シールドケースとを接合する接合部材とを備え、

前記接合部材が半田であり、

前記基板の側端面の一部と重畳する脚部が前記シールドケースの複数の側部のうちの所定の側部から延ばされているとともに、前記基板の側端面の一部と前記シールドケースの脚部とが前記半田で接合されており、

前記基板の側端面の一部と前記シールドケースの脚部との重畳部分を露出させるための開口部が前記シールドケースの所定の側部から天面部に跨るように形成されていることを特徴とする回路モジュール。 - 前記基板に端面スルーホールが形成されており、

前記シールドケースの脚部に接合される前記基板の側端面の一部が前記端面スルーホールの内側面とされていることを特徴とする請求項1に記載の回路モジュール。 - 前記端面スルーホールの形状が半長円形状とされていることを特徴とする請求項2に記載の回路モジュール。

- 前記シールドケースの複数の側部が互いに対向する一対の第1側部を含み、

前記シールドケースの少なくとも一対の第1側部のそれぞれが、前記脚部が延ばされ、かつ、前記開口部が形成された所定の側部とされていることを特徴とする請求項1〜3のいずれかに記載の回路モジュール。 - 前記シールドケースの複数の側部が互いに対向する一対の第2側部をさらに含み、

前記シールドケースの少なくとも一対の第2側部のそれぞれの先端が前記基板の実装面に当接していることを特徴とする請求項4に記載の回路モジュール。 - 前記基板の板厚方向で見て、前記シールドケースの開口部の内側面のうちの前記脚部側の面の位置と前記基板の実装面の位置とが同じとなっていることを特徴とする請求項1〜5のいずれかに記載の回路モジュール。

- 請求項1〜6のいずれかに記載の回路モジュールを備えていることを特徴とする電子機器。

- 請求項1〜6のいずれかに記載の回路モジュールの製造方法であって、

実装面および前記実装面に繋がる側端面を有する基板を作製し、前記基板の実装面に電子部品を実装する工程と、

天面部および前記天面部の外周に立設された複数の側部を有するシールドケースを作製する工程と、

前記基板と前記シールドケースとを接合部材で接合する工程とを備え、

前記接合部材が半田であり、

前記シールドケースを作製する際に、前記基板の側端面の一部と重畳する脚部を前記シールドケースの複数の側部のうちの所定の側部から延ばすとともに、前記基板の側端面の一部と前記シールドケースの脚部との重畳部分が露出されるような開口部を前記シールドケースの所定の側部から天面部に跨るように形成し、

前記基板の側端面の一部と前記シールドケースの脚部との重畳部分が前記シールドケースの開口部から露出された状態で、前記基板の側端面の一部と前記シールドケースの脚部とを前記半田で接合することを特徴とする回路モジュールの製造方法。 - 前記シールドケースの開口部から前記半田に熱を加えることにより、前記基板の側端面の一部と前記シールドケースの脚部とを前記半田で接合することを特徴とする請求項8に記載の回路モジュールの製造方法。

- 前記半田に加える熱がレーザ光を照射することで発生する熱であることを特徴とする請求項9に記載の回路モジュールの製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010039591A JP5118713B2 (ja) | 2010-02-25 | 2010-02-25 | 回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 |

| US12/946,172 US20110204496A1 (en) | 2010-02-25 | 2010-11-15 | Circuit module, electronic device including the same, and circuit module manufacturing method |

| CN201010587998.1A CN102169877B (zh) | 2010-02-25 | 2010-11-29 | 电路模块、包括电路模块的电子设备及电路模块制造方法 |

| BRPI1005260A BRPI1005260A2 (pt) | 2010-02-25 | 2010-12-02 | módulo de circuito, dispositivo eletrônico que o inclui, e método de fabricação de módulo de circuito |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010039591A JP5118713B2 (ja) | 2010-02-25 | 2010-02-25 | 回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011176154A JP2011176154A (ja) | 2011-09-08 |

| JP5118713B2 true JP5118713B2 (ja) | 2013-01-16 |

Family

ID=44475805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010039591A Expired - Fee Related JP5118713B2 (ja) | 2010-02-25 | 2010-02-25 | 回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20110204496A1 (ja) |

| JP (1) | JP5118713B2 (ja) |

| CN (1) | CN102169877B (ja) |

| BR (1) | BRPI1005260A2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105142328B (zh) * | 2014-06-04 | 2017-12-26 | 安徽省磊鑫科技有限公司 | 一种带安装防护装置的集成电路 |

| EP3462822A1 (de) * | 2017-09-29 | 2019-04-03 | Siemens Aktiengesellschaft | Elektrischer umrichter |

| CN112151467B (zh) * | 2020-09-11 | 2022-11-01 | 安徽龙芯微科技有限公司 | 一种芯片封装体及其制备方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2938820B2 (ja) * | 1996-03-14 | 1999-08-25 | ティーディーケイ株式会社 | 高周波モジュール |

| JP2002016162A (ja) * | 2000-06-28 | 2002-01-18 | Iwaki Electronics Corp | 電子部品モジュール |

| JP2004235184A (ja) * | 2003-01-28 | 2004-08-19 | Matsushita Electric Ind Co Ltd | 高周波装置 |

| JP4096808B2 (ja) * | 2003-05-15 | 2008-06-04 | エプソントヨコム株式会社 | 電子部品用パッケージ及びこれを用いた圧電発振器 |

| JP2007201286A (ja) * | 2006-01-27 | 2007-08-09 | Kyocera Corp | 表面実装モジュールの製造方法および表面実装モジュール |

| JP3969453B1 (ja) * | 2006-05-17 | 2007-09-05 | 株式会社村田製作所 | ケース付き多層モジュール |

| JP4748455B2 (ja) * | 2006-06-16 | 2011-08-17 | 株式会社村田製作所 | 電子部品モジュール |

| JP2008103639A (ja) * | 2006-10-20 | 2008-05-01 | Toyota Motor Corp | インテリジェント・パワー・モジュールの構造、及び、製造方法 |

-

2010

- 2010-02-25 JP JP2010039591A patent/JP5118713B2/ja not_active Expired - Fee Related

- 2010-11-15 US US12/946,172 patent/US20110204496A1/en not_active Abandoned

- 2010-11-29 CN CN201010587998.1A patent/CN102169877B/zh not_active Expired - Fee Related

- 2010-12-02 BR BRPI1005260A patent/BRPI1005260A2/pt not_active Application Discontinuation

Also Published As

| Publication number | Publication date |

|---|---|

| CN102169877B (zh) | 2013-10-30 |

| BRPI1005260A2 (pt) | 2015-12-01 |

| CN102169877A (zh) | 2011-08-31 |

| JP2011176154A (ja) | 2011-09-08 |

| US20110204496A1 (en) | 2011-08-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6891965B2 (ja) | 高周波モジュールおよびその製造方法 | |

| JP6265852B2 (ja) | コネクタ | |

| JP2008235651A (ja) | 半導体装置およびその製造方法 | |

| JP4692152B2 (ja) | 回路モジュール及びその製造方法 | |

| JP2015012031A (ja) | 電子部品モジュール、基板及び電子部品モジュールの製造方法 | |

| JP2012079468A (ja) | 電子回路ユニットおよびその取付構造 | |

| JP5118713B2 (ja) | 回路モジュールおよびそれを備えた電子機器ならびに回路モジュールの製造方法 | |

| JP2008084964A (ja) | 高周波ユニットの製造方法、及び高周波ユニット | |

| JP4876906B2 (ja) | 三次元基板間接続構造体およびそれを用いた立体回路装置 | |

| JP2014063835A (ja) | 回路基板装置、および、電子機器 | |

| JP4131724B2 (ja) | 回路基板への端子の取付構造 | |

| JP5056004B2 (ja) | 三次元基板間接続構造体およびそれを用いた立体回路装置 | |

| JP2008112832A (ja) | 高周波ユニット、及び高周波ユニットの製造方法 | |

| JP2003258476A (ja) | シールド構造 | |

| KR20010051817A (ko) | 차폐 케이스를 구비한 전자 부품 | |

| JP4853276B2 (ja) | 半導体装置の製造方法 | |

| JP2008034731A (ja) | 高周波モジュール、シールドケース装着方法および高周波モジュールの製造方法 | |

| JP2007324246A (ja) | 半導体装置とその製造方法 | |

| JP6102145B2 (ja) | 実装構造体及び実装構造体の製造方法 | |

| JP2008166485A (ja) | モジュール | |

| JP6582635B2 (ja) | モジュール−基板間接続構造 | |

| JP2007258404A (ja) | シールドケース搭載基板とその製造方法 | |

| JP2003174258A (ja) | 電子部品及びその実装構造 | |

| JP2005235806A (ja) | ケース付電子部品 | |

| KR101974920B1 (ko) | 인쇄회로기판 사이의 연결 구조 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120724 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120904 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120925 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121019 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151026 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |