JP4933036B2 - 差動容量素子、差動アンテナ素子及び差動共振素子 - Google Patents

差動容量素子、差動アンテナ素子及び差動共振素子 Download PDFInfo

- Publication number

- JP4933036B2 JP4933036B2 JP2004190375A JP2004190375A JP4933036B2 JP 4933036 B2 JP4933036 B2 JP 4933036B2 JP 2004190375 A JP2004190375 A JP 2004190375A JP 2004190375 A JP2004190375 A JP 2004190375A JP 4933036 B2 JP4933036 B2 JP 4933036B2

- Authority

- JP

- Japan

- Prior art keywords

- shield plate

- differential

- lower electrode

- semiconductor substrate

- projected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Filters And Equalizers (AREA)

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

Description

特許文献1を参照)。

また、本発明の第2の目的は、寄生容量及び寄生抵抗の影響を抑えることが可能な差動アンテナ素子を提供することである。

また、本発明の第3の目的は、寄生容量及び寄生抵抗の影響を抑えることが可能な差動共振素子を提供することを目的とする。

図1Aは、本発明の第1の実施形態に係る差動容量素子1を鉛直上方向から見たときの模式図である。また、図1Bは、図1Aに示す鉛直面A−A’で差動容量素子1を切断した時の断面を矢印Cの方向から見たときの模式図である。図1A及び図1Bには、説明の便宜のため、互いに直交するx軸、y軸及びz軸からなる三次元座標系が示される。ここで、z軸は鉛直上向きを示す。x軸及びy軸は、水平面において、互いに直交する2方向を示しており、y軸は特に、矢印Cの向きに等しく、後述する鉛直面B−B’に平行である。

図8Aは、本発明の第2の実施形態に係る差動容量素子2を鉛直上方向から見たときの模式図である。また、図8Bは、図8Aに示す鉛直面A−A’で差動容量素子2を切断した時の断面を矢印Cの方向から見たときの模式図である。図8A及び図8Bには、説明の便宜のため、互いに直交するx軸、y軸及びz軸からなる三次元座標系が示される。ここで、z軸は鉛直上向きを示す。x軸及びy軸は、水平面において、互いに直交する2方向を示しており、y軸は特に、矢印Cの向きに等しく、後述する鉛直面B−B’に平行である。

図10Aは、本発明の第3の実施形態に係る差動容量素子3を鉛直上方向から見たときの模式図である。また、図10Bは、図10Aに示す鉛直面A−A’で差動容量素子3を切断した時の断面を矢印Cの方向から見たときの模式図である。図10A及び図10Bには、説明の便宜のため、互いに直交するx軸、y軸及びz軸からなる三次元座標系が示される。ここで、z軸は鉛直上向きを示す。x軸及びy軸は、水平面において、互いに直交する2方向を示しており、y軸は特に、矢印Cの向きに等しく、後述する鉛直面B−B’に平行である。

C42+C44 …(2)

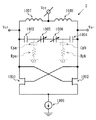

図13は、本発明の第4の実施形態に係る差動スイッチ回路4の構成を示す模式図である。図13において、差動スイッチ回路4は、差動入力端子4001と、制御信号用の入力端子4002と、pチャネルのMOSFET4003と、nチャネルのMOSFET4004及び4005と、従前の実施形態で説明した差動容量素子1−3のいずれかと、差動出力端子4006とを備えている。

図14Aは、本発明の第5の実施形態に係る差動アンテナ素子5を鉛直上方向から見たときの模式図である。また、図14Bは、図14Aに示す鉛直面A−A’で差動容量素子5を切断した時の断面を矢印Cの方向から見たときの模式図である。図14A及び図14Bには、説明の便宜のため、互いに直交するx軸、y軸及びz軸からなる三次元座標系が示される。ここで、z軸は鉛直上向きを示す。x軸及びy軸は、水平面において、互いに直交する2方向を示しており、y軸は特に、矢印Cの向きに等しく、後述する鉛直面B−B’に平行である。

図15は、本発明の第6の実施形態に係るフィルタ回路6の全体的な回路構成を示す模式図である。図15において、フィルタ回路6は、差動入力端子601と、2個の1/2波長共振素子602a及び602bと、2個の容量素子603a及び603bと、差動出力端子604とを備えている。

1003,2001,3001 第1の容量素子

1015,2006 上部電極

1016,2007 下部電極

1004,2002,3002 第2の容量素子

1017,2008 上部電極

1018,2009 下部電極

1022,1023,1024,2005,3005 シールド板

10241,20051 貫通孔

1019 層間膜

1020 半導体基板

Ao オーバーラップ領域

An 非オーバーラップ領域

2003,3003 第3の容量素子

2010 上部電極

2011 下部電極

2004,3004 第4の容量素子

2012 上部電極

2013 下部電極

3015 第1の電極

3016 第2の電極

4 差動スイッチ回路

4001 差動入力端子

4002 制御信号用の入力端子

4003 pチャネルのMOSFET

4004,4005 nチャネルのMOSFET

4006 差動出力端子

5 差動アンテナ素子

5001 第1の平板アンテナ素子

5002 第2の平板アンテナ素子

5003 シールド板

6 フィルタ回路

601 差動入力端子

602a,602b 1/2波長共振素子

603a,603b 容量素子

6021 平板

6022 シールド板

6023 第1の端子

6024 第2の端子

604 差動出力端子

Claims (28)

- 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記上部電極及び前記下部電極のうち、第1の下部電極又は第1の上部電極、及び第2の下部電極又は第2の上部電極のそれぞれには、少なくとも1個の可変容量素子が接続される可変容量回路に用いられる、差動容量素子。 - 投影された各前記下部電極は、前記シールド板からはみ出ている、請求項1に記載の差動容量素子。

- 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記シールド板にはスリットが形成されている、差動容量素子。 - 前記スリットは、前記第1の鉛直面と交差する、請求項3に記載の差動容量素子。

- 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記シールド板には複数の貫通孔が形成されている、差動容量素子。 - 前記複数の貫通孔は、所定の2方向に実質的に等しい間隔に配列されており、

前記複数の貫通孔において、互いに隣り合うもの同士の間隔は、前記シールド板を伝搬する定在波の半波長の整数倍に実質的に等しい、請求項5に記載の差動容量素子。 - 前記シールド板において、所定の2辺から前記第1の鉛直面までの長さは、前記定在波の半波長の整数倍と、前記定在波の4分の1波長との和に実質的に等しい、請求項6に記載の差動容量素子。

- 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記複数の容量素子において、互いに隣り合う2個の容量素子の一方には、差動信号を構成する同相信号が与えられ、他方には、前記差動信号を構成する逆相信号が与えられる、差動容量素子。 - 前記シールド板は、インダクタンス及び/又は抵抗素子を介して、グランドに接続される、請求項1に記載の差動容量素子。

- 前記シールド板において、前記第1の鉛直面と交差する部分がグランドと接続される、

請求項1に記載の差動容量素子。 - 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記上部電極及び前記下部電極のうち、第1の下部電極又は第1の上部電極、及び第2の下部電極又は第2の上部電極のそれぞれには、少なくとも1個の可変容量素子が接続される差動発振回路に用いられる差動容量素子。 - 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記上部電極及び前記下部電極のうち、第1の下部電極及び第2の下部電極にはスイッチ素子が接続されてスイッチ回路に用いられる、差動容量素子。 - 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記上部電極及び前記下部電極のうち、第1の下部電極又は第1の上部電極、及び第2の下部電極又は第2の上部電極のそれぞれには、少なくとも1個の可変容量素子が接続される差動スイッチ回路に用いられる差動容量素子。 - 差動容量素子であって、

鉛直方向に互いに実質的に平行な上部電極及び下部電極を含む複数の容量素子を備え、

前記複数の容量素子のいずれかは、半導体基板上において、第1の鉛直面を基準として、他の前記容量素子と実質的に対称な位置に形成され、

前記差動容量素子はさらに、各前記下部電極と、前記半導体基板との間に配置されるシールド板を備え、

各前記下部電極を鉛直方向から前記シールド板に投影した時、投影された各前記下部電極は、前記シールド板と部分的に重なりを持ち、

投影された各前記下部電極において、前記シールド板と重なりを持つ部分の面積は、各前記下部電極が有する面積の70%以上であるとともに、

前記複数の容量素子の1つ目は、前記半導体基板上において、第1の鉛直面を基準として、基準となる前記容量素子と実質的に対称な位置に形成され、

前記複数の容量素子の2つ目は、前記半導体基板上において、前記第1の鉛直面に直交する第2の鉛直面を基準として、基準となる前記容量素子と実質的に対称な位置に形成され、

前記複数の容量素子の3つ目は、前記半導体基板上において、前記第1及び第2の鉛直面の交線を基準として、対称な位置に形成される、差動容量素子。 - 前記複数の容量素子の内、基準となるもの及び3つ目の双方には、差動信号を構成する同相信号及び逆相信号のいずれか一方が与えられ、1つ目及び2つ目の双方には、前記同相信号及び逆相信号のいずれか他方が与えられる、請求項14に記載の差動容量素子。

- 前記シールド板には、所定の2方向に実質的に等しい間隔で配列される複数の貫通孔が形成されており、前記複数の貫通孔において、互いに隣り合うもの同士の間隔は、前記シールド板を伝搬する定在波の半波長の整数倍に実質的に等しく、

前記シールド板は長方形状の形状を有しており、所定の2辺から前記第1の鉛直面までの長さ、及び他の2辺から前記第2の鉛直面までの長さはそれぞれ、前記定在波の半波長の整数倍と、前記定在波の4分の1波長との和に実質的に等しい、請求項14に記載の差動容量素子。 - 差動アンテナ素子であって、

半導体基板上において、第1の鉛直面を基準として、互いに実質的に対称な位置に形成される複数のアンテナ素子と、

各前記アンテナ素子と、前記半導体基板との間に配置されるシールド板とを備え、

各前記アンテナ素子を鉛直方向から前記シールド板に投影した時、投影された各前記アンテナ素子は、前記シールド板と部分的に重なりを持ち、

投影された各前記アンテナ素子において、前記シールド板と重なりを持つ部分の面積は、各前記アンテナ素子が有する面積の70%以上であるとともに、

前記シールド板にはスリットが形成されている、差動アンテナ素子。 - 前記スリットは、前記第1の鉛直面と交差する、請求項17に記載の差動アンテナ素子。

- 差動アンテナ素子であって、

半導体基板上において、第1の鉛直面を基準として、互いに実質的に対称な位置に形成される複数のアンテナ素子と、

各前記アンテナ素子と、前記半導体基板との間に配置されるシールド板とを備え、

各前記アンテナ素子を鉛直方向から前記シールド板に投影した時、投影された各前記アンテナ素子は、前記シールド板と部分的に重なりを持ち、

投影された各前記アンテナ素子において、前記シールド板と重なりを持つ部分の面積は、各前記アンテナ素子が有する面積の70%以上であるとともに、

前記シールド板には複数の貫通孔が形成されている、差動アンテナ素子。 - 半導体基板上に形成される差動共振素子であって、

第1の鉛直面を基準として、互いに実質的に対称な形状を有し、さらに、互いに実質的に対称な位置に2個の端子を有する少なくとも1個の誘電性の平板と、

前記少なくとも1個の平板と、前記半導体基板との間に配置されるシールド板とを備え、

前記少なくとも1個の平板を鉛直方向から前記シールド板に投影した時、投影された平板は、前記シールド板と部分的に重なりを持つ、差動共振素子。 - 投影された前記少なくとも1個の平板は、前記シールド板からはみ出ている、請求項20に記載の差動共振素子。

- 前記シールド板にはスリットが形成されている、請求項20に記載の差動共振素子。

- 前記スリットは、前記第1の鉛直面と交差する、請求項22に記載の差動共振素子。

- 前記シールド板には複数の貫通孔が形成されている、請求項20に記載の差動共振素子。

- 前記少なくとも1個の平板において、一方端には、差動信号を構成する同相信号が与えられ、他方端には、前記差動信号を構成する逆相信号が与えられる、請求項20に記載の差動共振素子。

- 前記シールド板は、インダクタンス及び/又は抵抗素子を介して、グランドに接続される、請求項20に記載の差動共振素子。

- 前記シールド板において、前記第1の鉛直面と交差する部分がグランドと接続される、請求項20に記載の差動共振素子。

- フィルタ回路に用いられる、請求項20に記載の差動共振素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004190375A JP4933036B2 (ja) | 2003-07-03 | 2004-06-28 | 差動容量素子、差動アンテナ素子及び差動共振素子 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003191267 | 2003-07-03 | ||

| JP2003191267 | 2003-07-03 | ||

| JP2004190375A JP4933036B2 (ja) | 2003-07-03 | 2004-06-28 | 差動容量素子、差動アンテナ素子及び差動共振素子 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005159280A JP2005159280A (ja) | 2005-06-16 |

| JP2005159280A5 JP2005159280A5 (ja) | 2007-04-26 |

| JP4933036B2 true JP4933036B2 (ja) | 2012-05-16 |

Family

ID=34740994

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004190375A Expired - Fee Related JP4933036B2 (ja) | 2003-07-03 | 2004-06-28 | 差動容量素子、差動アンテナ素子及び差動共振素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4933036B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6940707B2 (en) * | 2003-07-03 | 2005-09-06 | Matsushita Electric Industrial Co., Ltd. | Differential capacitor, differential antenna element, and differential resonator |

| JP2014063991A (ja) | 2012-08-31 | 2014-04-10 | Toshiba Corp | 半導体装置、高周波伝送装置および半導体製造方法 |

| JP6030900B2 (ja) * | 2012-09-21 | 2016-11-24 | 旭化成エレクトロニクス株式会社 | チャージポンプ回路 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0752085B2 (ja) * | 1989-10-11 | 1995-06-05 | フジテコム株式会社 | 埋設金属管の深度測定装置 |

| GB2301720B (en) * | 1995-06-01 | 2000-05-24 | Motorola Inc | A MOS switching circuit |

| JP4047064B2 (ja) * | 2001-05-17 | 2008-02-13 | 松下電器産業株式会社 | 高周波半導体装置 |

-

2004

- 2004-06-28 JP JP2004190375A patent/JP4933036B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005159280A (ja) | 2005-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6798305B2 (en) | High frequency oscillator using transmission line resonator | |

| US8760243B2 (en) | Tunable bandpass filter | |

| CN102422533B (zh) | 共模过滤器 | |

| JP6787955B2 (ja) | フィルタ | |

| WO2015042814A1 (en) | Wideband injection locked frequency multipliers, oscillators and dividers using higher order lc resonant tank | |

| JP2009507426A (ja) | 3dmmicバラン及びその製造方法 | |

| JP4494223B2 (ja) | 半導体装置 | |

| EP1496528A2 (en) | Differential capacitor, differential antenna element, and differential resonator | |

| JP5060716B2 (ja) | 受動部品 | |

| US6703904B2 (en) | High frequency oscillator | |

| JP4933036B2 (ja) | 差動容量素子、差動アンテナ素子及び差動共振素子 | |

| JPWO2015025603A1 (ja) | 高周波モジュール | |

| CN1134843C (zh) | 平面介质集成电路 | |

| US9640530B2 (en) | Semiconductor device | |

| JP6800181B2 (ja) | 共振器及びフィルタ | |

| JP2008130683A (ja) | 半導体集積回路装置 | |

| JP2020155836A (ja) | 積層型フィルタ装置 | |

| WO2015029486A1 (ja) | 高周波電力増幅器 | |

| US20220131522A1 (en) | Resonator and filter | |

| US7030443B2 (en) | MIM capacitor | |

| JP6501986B2 (ja) | 半導体装置 | |

| JP6409664B2 (ja) | 高周波共振器及び高周波発振器 | |

| JP2002513229A (ja) | コプレーナ発振回路構造 | |

| EP1211799B1 (en) | Lc oscillator | |

| JP2020171066A (ja) | 共振器及びフィルタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070307 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070307 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100908 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101022 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110812 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110826 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111005 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20111013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111130 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120127 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120216 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150224 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |