JP4843248B2 - 粒子ビーム露光の改善されたパターン規定装置 - Google Patents

粒子ビーム露光の改善されたパターン規定装置 Download PDFInfo

- Publication number

- JP4843248B2 JP4843248B2 JP2005134248A JP2005134248A JP4843248B2 JP 4843248 B2 JP4843248 B2 JP 4843248B2 JP 2005134248 A JP2005134248 A JP 2005134248A JP 2005134248 A JP2005134248 A JP 2005134248A JP 4843248 B2 JP4843248 B2 JP 4843248B2

- Authority

- JP

- Japan

- Prior art keywords

- blank

- line

- group

- aperture

- apertures

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000002245 particle Substances 0.000 title claims description 41

- 230000003287 optical effect Effects 0.000 claims description 12

- 238000010521 absorption reaction Methods 0.000 claims description 2

- 239000000758 substrate Substances 0.000 description 36

- 238000012545 processing Methods 0.000 description 34

- 238000009826 distribution Methods 0.000 description 29

- 238000000034 method Methods 0.000 description 21

- 230000002829 reductive effect Effects 0.000 description 20

- 230000008901 benefit Effects 0.000 description 18

- 235000012431 wafers Nutrition 0.000 description 17

- 230000009467 reduction Effects 0.000 description 14

- 238000012937 correction Methods 0.000 description 11

- 230000004048 modification Effects 0.000 description 11

- 238000012986 modification Methods 0.000 description 11

- 230000008569 process Effects 0.000 description 11

- 230000007547 defect Effects 0.000 description 10

- 230000000694 effects Effects 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- 239000010410 layer Substances 0.000 description 7

- 230000015654 memory Effects 0.000 description 7

- 238000007781 pre-processing Methods 0.000 description 7

- 238000013459 approach Methods 0.000 description 6

- 238000000354 decomposition reaction Methods 0.000 description 6

- 238000012546 transfer Methods 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 238000011161 development Methods 0.000 description 5

- 230000018109 developmental process Effects 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 238000005286 illumination Methods 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000010363 phase shift Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 239000000872 buffer Substances 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 238000010884 ion-beam technique Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 230000004075 alteration Effects 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 3

- 238000001816 cooling Methods 0.000 description 3

- 230000001419 dependent effect Effects 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 230000020169 heat generation Effects 0.000 description 3

- 238000012432 intermediate storage Methods 0.000 description 3

- 230000033001 locomotion Effects 0.000 description 3

- 238000004377 microelectronic Methods 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 230000005855 radiation Effects 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- 238000000638 solvent extraction Methods 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 230000009466 transformation Effects 0.000 description 3

- 101100029960 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) PLM2 gene Proteins 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 238000013523 data management Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 230000003993 interaction Effects 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 230000005405 multipole Effects 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 238000003466 welding Methods 0.000 description 2

- 241001270131 Agaricus moelleri Species 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 235000021028 berry Nutrition 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000003139 buffering effect Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000007306 functionalization reaction Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- -1 hydrogen ions Chemical class 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000002039 particle-beam lithography Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000036314 physical performance Effects 0.000 description 1

- 238000013439 planning Methods 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- G—PHYSICS

- G21—NUCLEAR PHYSICS; NUCLEAR ENGINEERING

- G21K—TECHNIQUES FOR HANDLING PARTICLES OR IONISING RADIATION NOT OTHERWISE PROVIDED FOR; IRRADIATION DEVICES; GAMMA RAY OR X-RAY MICROSCOPES

- G21K1/00—Arrangements for handling particles or ionising radiation, e.g. focusing or moderating

- G21K1/08—Deviation, concentration or focusing of the beam by electric or magnetic means

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/02—Details

- H01J37/04—Arrangements of electrodes and associated parts for generating or controlling the discharge, e.g. electron-optical arrangement or ion-optical arrangement

- H01J37/045—Beam blanking or chopping, i.e. arrangements for momentarily interrupting exposure to the discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/30—Electron-beam or ion-beam tubes for localised treatment of objects

- H01J37/317—Electron-beam or ion-beam tubes for localised treatment of objects for changing properties of the objects or for applying thin layers thereon, e.g. for ion implantation

- H01J37/3174—Particle-beam lithography, e.g. electron beam lithography

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/3175—Lithography

- H01J2237/31774—Multi-beam

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Physics & Mathematics (AREA)

- Analytical Chemistry (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Engineering & Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- High Energy & Nuclear Physics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Electron Beam Exposure (AREA)

Description

次に説明する本発明の好ましい実施例は、米国公開特許第二003−0155534−A1に開示されたパターン規定(PD)システムに基づいている。次の説明において、本発明に適切である限り、PDシステムの技術的背景はまず図1から5(米国公開特許第二003−0155534−A1のシステムに充当する修正例に対応)を参照して説明し、次にPDシステムにおける本発明の実施例を説明する。本発明は次の実施例に限定するのもではなく、本発明の可能な実行例のいくつかを提示するのみであることを理解すべきである。

グレイ・スケール

上述したPML2の概念に基づいて、基板は連続して移動され、またターゲット上の同じ画素が走査動作中一連のアパーチャによって複数回覆われる。従って、ターゲット上のある位置における一つの画素を考慮して、その画素が覆われたきに全アパーチャがスイッチオンされ、これで画素の最大露光結果となり、「ホワイト」シェードが100%に対応する。グレイ・シェード(例えば、20%)が線内のアパーチャの対応する数(例えば、線内に90のアパーチャあがるときに90の20%=18アパーチャ)をスイッチオンすることによって実行される。従って、画素の値を制御する信号がグレイ・スケール・コード、例えばnビットの2進数としてコード化された整数によって表わされる。

以下、本発明をアパーチャの構成がn=6とm=6(n×m=36)の概念で説明する。ウェハに対して説明されるべき最小構成サイズは45nm(45nmの分解線とスペースを伴う45nmノードとする)であり、最小スポットは25nm(図3において画素幅×、一つのアパーチャの幾何学的画像に等しい)である。画像フィールド幅fwは81μmである。200×縮小投射システム(上記説明参照)に関するこの画像フィールドを製造するために、正方形PDフィールドが幅L=16.2mmを有し、線の数pl=L/W=3240に対応し、また3240ビット・ストリームが到来データ・ストリームによってアドレスされることになる。横断方向において、列r1−r3の各々にfw/(n・x)=L/(n・w)=90アパーチャがある。

図14はブランク・プレートのためのデータ事前処理およびデータ・ローディングを示す。既に説明したように、ブランク・プレートへ供給される並列データ(3240線掛ける6グレイ・グループ)の安定流れがある。ブランク・プレートに対して利用可能な線の制限数(例えば、200未満のパッド接続部713)だけがあるという事実のために、マルチプレキシング工程がこのボトルネックの周りで操作するのに使用される。換言すれば、任意の定格(例えば、8MHz)で複数の並列データ(6×3240ビット)が高いデータ定格(144×8=1152MHz)の少数データ(例えば、135ビット)に変換される。ブランク・プレート上で、データがコンバータ721−724内で並列データに変換し直され、供給線gfを介してグレイ・グループに印加することができる。ブランク・プレートでデータ定格を下げるために、供給線がPDフィールドの全周縁の周りに配備される。例えば、上述したように25mmチップ上に生成された16.2mm幅の方形PDフィールドで、80μm幅を有する少なくとも1250までの接着パッドが矩形フレームに沿って線に嵌め込むことができ、16ビット・マルチプレキシング工程によって128MHzまでデータ定格の低減が許容される。

グレイ・スケーリングに関連する可能な欠陥と他の問題を考慮するために、1線当りの欠陥数に依存して可能にされたり、不可能にされたりできるスペア・ブランク開口部を含めることが可能である。このオプションを提供するために、必要とする以上のアパーチャがあるチャネルまたは全チャネルのために構成するこができ、あるいはより有効であると思われれば、付加的な「エキストラ・アパーチャ」グループが各線に付加でき、これによって必要とするときに、例えば対応する接続線の合焦イオン・ビーム修正によって物理的に必要なとき、または設置ロジックを使用するソフトウェア制御スイッチングによって1線当りのアパーチャの特定数を「稼動」することができる。

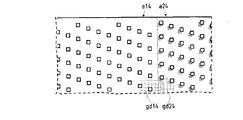

本発明のさらなる発展例として、「インターロッキング・グリッド」による異なるグループの配列アパーチャが実行され、基板上に付加的な露光スポットを生成する。インターロッキング・グリッドにおいて、一つまたはそれ以上のアパーチャが、アパーチャ直径の一部によって、詳しくは正方形または矩形グリッドに対して半径だけ水平および垂直方向に他のグループのベース・アレイにシフトされる。

ストライプa24内のアパーチャ(すなわち、ブランク開口部)は、他のストライプa14内のアパーチャの位置に関して垂直方向と水平方向にアパーチャ幅の半分だけシフトされる。この結果として、効果的なグリッドが両グリッドgd14,gd24の重畳から得られ、効果的グリッドのピッチはベース・グリッドのピッチの半分になる。異なるグリッドに属するブランク開口部が分離したグレイ・グループとしてアドレスされる。

2)任意のアドレス・グリッドに対して必要とするグレイ・レベルが相当低減

3)グレイ・レベル数の低減がPDフィールドのサイズのさらなる低減を許容

4)最も限界的な線(解像度<ノード)の書き取りが同じ走査速度で可能

5)任意のぼやけ(最小外径サイズのパーセント)に対して、小さいリトグラフ・ノードが達成

6)ブランク・アパーチャ・プレート内の総アパーチャの限定数に対して、小さい直径カラムの場合に、レベル当りのアパーチャ数(=冗長性)従来のグリッドと比べてインターロッキング・グリッドに対してより高い、16.2mmの矩形プレートの例によって説明すると、90個のアパーチャがインターロッキング・グリッドを使用してまたはそれぞれインターロッキング・グリッドなしに46個のグレイ・レベル(1レベル当り2アパーチャ)を使用して2×16のグレイ・レベル(1レベル当り3アパーチャ)に副分割することができる。

1)グレイ・レベルの低い数が必要:主な改良の一つは単一走査ストライプ露光処理中に可能な物理的アドレス・グリッドの低減(すなわち、近接露光スポットの距離)である。これはPDフィールド上方に適切な方法でアパーチャの利用可能数を配列し、(補間された画素情報で)適切に変換されたデータ流れによるアパーチャの一部をアドレスすることによって達成される。対応するアドレス・グリッドおよび処理寛容度が、物理的アドレス・グリッドが倍化されて各露光スポットに対するグレイ・レベルの低い数にもかかわらず相当改善される。例えば、12.5nm距離(XおよびY方向に)でインターロッキング・グリッド・スポットと各スポットに対して16グレイ・レベルを有する25nm幅の露光スポットを使用することで、1nmアドレス・グリッド(線の中心のエラー<0.5nm、線の幅のエラー<0.5nm)が、14.6%処理寛容度の優れた線量寛容度で実現することができる。比較の目的で、露光スポット当り64グレイ・レベルさえもないインターロッキング・グリッドなしで、処理寛容度が係数2だけグリッド位置で変化すると、比較的低い処理寛容度を満足させない。

Claims (8)

- 帯電粒子のビームを発生させる帯電粒子源と、

複数のブランク開口部を有するマルチアパーチャ・プレートであって、それぞれのブランク開口部が、第1の状態と第2の状態との間で、ブランク信号によって制御可能な偏向電極を含み、前記第1の状態において、前記ブランク開口部を通って放射する前記帯電粒子のビームの粒子が、所定の経路に沿って進み、前記第2の状態において、前記ブランク開口部を通って放射する前記帯電粒子のビームの粒子が、前記所定の経路を外れて偏向される、マルチアパーチャ・プレートとを備えた帯電粒子ビーム露光装置であって、

前記ブランク開口部の複数のグループは、それぞれのグループが複数のブランク開口部を有するように形成され、それぞれのグループの前記ブランク開口部の対は、電気遅延素子によって互いに電気的に接続され、共通のグループ・ブランク信号によって制御されることを特徴とする帯電粒子ビーム露光装置。 - 異なる数のブランク開口部を有する少なくとも2つのグループのブランク開口部が形成されている請求項1に記載の帯電粒子ビーム露光装置。

- 前記少なくとも2つのグループのそれぞれのブランク開口部の数が、2の累乗に共通の整数を乗じた数に対応している請求項2に記載の帯電粒子ビーム露光装置。

- 一つのグループを除いて全グループのブランク開口部の数が、2の累乗に共通の整数を乗じた数に対応している請求項2に記載の帯電粒子ビーム露光装置。

- それぞれのグループの前記ブランク開口部が、互いに直接的に近接配置されている請求項1〜4のいずれかに記載の帯電粒子ビーム露光装置。

- 前記電気遅延素子が、ブランク開口部の前記偏向電極を制御するための前記ブランク信号を生成するように構成されている請求項1に記載の帯電粒子ビーム露光装置。

- 前記ブランク開口部を通って放射し、かつ、前記所定の経路を外れて偏向される前記帯電粒子のビームの粒子が入射するように配置された吸収面をさら備えた請求項1〜6のいずれかに記載の帯電粒子ビーム露光装置。

- ウェハを取り付けるためのウェハ・ステージと、前記ブランク開口部を通って放射し、前記ウェハ・ステージに取り付けられたウェハ上の所定の経路に沿って進む前記帯電粒子のビームの粒子を方向づけるように構成される帯電粒子光学系とをさらに備えた請求項1〜7のいずれかに記載の帯電粒子ビーム露光装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| ATA755/2004 | 2004-04-30 | ||

| AT7552004 | 2004-04-30 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005328047A JP2005328047A (ja) | 2005-11-24 |

| JP2005328047A5 JP2005328047A5 (ja) | 2008-05-29 |

| JP4843248B2 true JP4843248B2 (ja) | 2011-12-21 |

Family

ID=34658437

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005134248A Expired - Fee Related JP4843248B2 (ja) | 2004-04-30 | 2005-05-02 | 粒子ビーム露光の改善されたパターン規定装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7368738B2 (ja) |

| JP (1) | JP4843248B2 (ja) |

| GB (1) | GB2413694A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9082581B2 (en) | 2013-10-11 | 2015-07-14 | Nuflare Technology, Inc. | Blanking device for multiple charged particle beams |

| US9190238B2 (en) | 2013-11-12 | 2015-11-17 | Nuflare Technology, Inc. | Blanking device for multi charged particle beam, and multi charged particle beam writing method |

| US10133186B2 (en) | 2016-10-20 | 2018-11-20 | Mapper Lithography Ip B.V. | Method and apparatus for aligning substrates on a substrate support unit |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102709143B (zh) | 2003-09-05 | 2016-03-09 | 卡尔蔡司Smt有限责任公司 | 电子光学排布结构、多电子分束检验系统和方法 |

| US7448012B1 (en) | 2004-04-21 | 2008-11-04 | Qi-De Qian | Methods and system for improving integrated circuit layout |

| GB2435348B (en) * | 2004-11-17 | 2009-06-24 | Ims Nanofabrication Ag | Pattern lock system for particle-beam exposure apparatus |

| US8026495B2 (en) | 2005-10-28 | 2011-09-27 | Carl Zeiss Sms Gmbh | Charged particle beam exposure system |

| US7384852B2 (en) * | 2006-10-25 | 2008-06-10 | International Business Machines Corporation | Sub-lithographic gate length transistor using self-assembling polymers |

| US7772575B2 (en) * | 2006-11-21 | 2010-08-10 | D2S, Inc. | Stencil design and method for cell projection particle beam lithography |

| US8426832B2 (en) * | 2006-11-21 | 2013-04-23 | D2S, Inc. | Cell projection charged particle beam lithography |

| US7897522B2 (en) * | 2006-11-21 | 2011-03-01 | Cadence Design Systems, Inc. | Method and system for improving particle beam lithography |

| DE102008010123A1 (de) * | 2007-02-28 | 2008-09-04 | Ims Nanofabrication Ag | Vielstrahl-Ablenkarray-Einrichtung für maskenlose Teilchenstrahl-Bearbeitung |

| NL2001369C2 (nl) * | 2007-03-29 | 2010-06-14 | Ims Nanofabrication Ag | Werkwijze voor maskerloze deeltjesbundelbelichting. |

| JP5491704B2 (ja) * | 2007-05-14 | 2014-05-14 | イーエムエス ナノファブリカツィオン アーゲー | 対向電極アレイ板を有するパターン定義装置 |

| US7958736B2 (en) * | 2007-05-24 | 2011-06-14 | Bio-Rad Laboratories, Inc. | Thermoelectric device and heat sink assembly with reduced edge heat loss |

| EP2187427B1 (en) * | 2008-11-17 | 2011-10-05 | IMS Nanofabrication AG | Method for maskless particle-beam exposure |

| EP2190003B1 (en) * | 2008-11-20 | 2014-10-01 | IMS Nanofabrication AG | Constant current multi-beam patterning |

| US8294125B2 (en) * | 2009-11-18 | 2012-10-23 | Kla-Tencor Corporation | High-sensitivity and high-throughput electron beam inspection column enabled by adjustable beam-limiting aperture |

| JP2011199279A (ja) | 2010-03-18 | 2011-10-06 | Ims Nanofabrication Ag | ターゲット上へのマルチビーム露光のための方法 |

| EP2633545B1 (en) * | 2010-10-26 | 2018-01-24 | Mapper Lithography IP B.V. | Modulation device and charged particle multi-beamlet lithography system using the same |

| NL2006868C2 (en) * | 2011-05-30 | 2012-12-03 | Mapper Lithography Ip Bv | Charged particle multi-beamlet apparatus. |

| JP6087570B2 (ja) * | 2012-10-15 | 2017-03-01 | キヤノン株式会社 | 描画装置、および物品の製造方法 |

| JP6215586B2 (ja) * | 2012-11-02 | 2017-10-18 | 株式会社ニューフレアテクノロジー | マルチ荷電粒子ビーム描画方法及びマルチ荷電粒子ビーム描画装置 |

| JP2014116518A (ja) * | 2012-12-11 | 2014-06-26 | Canon Inc | 描画装置及び物品の製造方法 |

| EP2757571B1 (en) * | 2013-01-17 | 2017-09-20 | IMS Nanofabrication AG | High-voltage insulation device for charged-particle optical apparatus |

| NL2010760C2 (en) | 2013-05-03 | 2014-11-04 | Mapper Lithography Ip Bv | Beam grid layout. |

| JP6097640B2 (ja) * | 2013-06-10 | 2017-03-15 | 株式会社ニューフレアテクノロジー | マルチ荷電粒子ビーム描画方法及びマルチ荷電粒子ビーム描画装置 |

| JP2015023286A (ja) | 2013-07-17 | 2015-02-02 | アイエムエス ナノファブリケーション アーゲー | 複数のブランキングアレイを有するパターン画定装置 |

| EP2830083B1 (en) | 2013-07-25 | 2016-05-04 | IMS Nanofabrication AG | Method for charged-particle multi-beam exposure |

| JP6190254B2 (ja) * | 2013-12-04 | 2017-08-30 | 株式会社ニューフレアテクノロジー | マルチ荷電粒子ビーム描画装置及びマルチ荷電粒子ビーム描画方法 |

| EP2913838B1 (en) | 2014-02-28 | 2018-09-19 | IMS Nanofabrication GmbH | Compensation of defective beamlets in a charged-particle multi-beam exposure tool |

| EP2937889B1 (en) | 2014-04-25 | 2017-02-15 | IMS Nanofabrication AG | Multi-beam tool for cutting patterns |

| EP2937888B1 (en) * | 2014-04-25 | 2019-02-20 | IMS Nanofabrication GmbH | Multi-beam tool for cutting patterns |

| EP3358599B1 (en) | 2014-05-30 | 2021-01-27 | IMS Nanofabrication GmbH | Compensation of dose inhomogeneity using row calibration |

| JP6555619B2 (ja) * | 2014-06-13 | 2019-08-07 | インテル・コーポレーション | 電子ビームスループットのためのデータ削減 |

| JP6522662B2 (ja) * | 2014-06-13 | 2019-05-29 | インテル・コーポレーション | 電子ビームによる一方向の層上金属 |

| WO2015191108A1 (en) | 2014-06-13 | 2015-12-17 | Intel Corporation | Ebeam align on the fly |

| CN106463349B (zh) * | 2014-06-13 | 2019-12-20 | 英特尔公司 | 电子束非通用切具 |

| US10216087B2 (en) * | 2014-06-13 | 2019-02-26 | Intel Corporation | Ebeam universal cutter |

| JP6890373B2 (ja) | 2014-07-10 | 2021-06-18 | アイエムエス ナノファブリケーション ゲーエムベーハー | 畳み込みカーネルを使用する粒子ビーム描画機における結像偏向の補償 |

| KR102459585B1 (ko) * | 2014-08-19 | 2022-10-27 | 인텔 코포레이션 | E 빔 범용 커터를 이용한 교차 스캔 근접 보정 |

| US9568907B2 (en) | 2014-09-05 | 2017-02-14 | Ims Nanofabrication Ag | Correction of short-range dislocations in a multi-beam writer |

| US9761411B2 (en) * | 2015-01-20 | 2017-09-12 | Taiwain Semiconductor Manufacturing Company, Ltd. | System and method for maskless direct write lithography |

| US9653263B2 (en) | 2015-03-17 | 2017-05-16 | Ims Nanofabrication Ag | Multi-beam writing of pattern areas of relaxed critical dimension |

| EP3096342B1 (en) * | 2015-03-18 | 2017-09-20 | IMS Nanofabrication AG | Bi-directional double-pass multi-beam writing |

| US10410831B2 (en) | 2015-05-12 | 2019-09-10 | Ims Nanofabrication Gmbh | Multi-beam writing using inclined exposure stripes |

| KR102358009B1 (ko) * | 2015-11-10 | 2022-02-04 | 삼성전자주식회사 | 빔 투사 장치 및 빔 투사 장치를 이용하여 빔을 투사하는 방법 |

| JP2017168574A (ja) * | 2016-03-15 | 2017-09-21 | 株式会社ニューフレアテクノロジー | マルチ荷電粒子ビームのブランキング装置、マルチ荷電粒子ビームのブランキング方法、及びマルチ荷電粒子ビーム描画装置 |

| JP6709109B2 (ja) * | 2016-05-31 | 2020-06-10 | 株式会社ニューフレアテクノロジー | マルチ荷電粒子ビームのブランキング装置及びマルチ荷電粒子ビーム照射装置 |

| US10325756B2 (en) | 2016-06-13 | 2019-06-18 | Ims Nanofabrication Gmbh | Method for compensating pattern placement errors caused by variation of pattern exposure density in a multi-beam writer |

| US10325757B2 (en) | 2017-01-27 | 2019-06-18 | Ims Nanofabrication Gmbh | Advanced dose-level quantization of multibeam-writers |

| US10522329B2 (en) | 2017-08-25 | 2019-12-31 | Ims Nanofabrication Gmbh | Dose-related feature reshaping in an exposure pattern to be exposed in a multi beam writing apparatus |

| US11569064B2 (en) | 2017-09-18 | 2023-01-31 | Ims Nanofabrication Gmbh | Method for irradiating a target using restricted placement grids |

| US10651010B2 (en) | 2018-01-09 | 2020-05-12 | Ims Nanofabrication Gmbh | Non-linear dose- and blur-dependent edge placement correction |

| US10840054B2 (en) | 2018-01-30 | 2020-11-17 | Ims Nanofabrication Gmbh | Charged-particle source and method for cleaning a charged-particle source using back-sputtering |

| US10483080B1 (en) * | 2018-07-17 | 2019-11-19 | ICT Integrated Circuit Testing Gesellschaft für Halbleiterprüftechnik mbH | Charged particle beam device, multi-beam blanker for a charged particle beam device, and method for operating a charged particle beam device |

| US10593509B2 (en) | 2018-07-17 | 2020-03-17 | ICT Integrated Circuit Testing Gesellschaft für Halbleiterprüftechnik mbH | Charged particle beam device, multi-beam blanker for a charged particle beam device, and method for operating a charged particle beam device |

| US10978270B2 (en) * | 2018-12-19 | 2021-04-13 | ICT Integrated Circuit Testing Gesellschaft für Halbleiterprüftechnik mbH | Charged particle beam device, interchangeable multi-aperture arrangement for a charged particle beam device, and method for operating a charged particle beam device |

| EP3828914A1 (en) * | 2019-02-27 | 2021-06-02 | FEI Company | Charged particle beam device for inspection of a specimen with a plurality of charged particle beamlets |

| US11099482B2 (en) | 2019-05-03 | 2021-08-24 | Ims Nanofabrication Gmbh | Adapting the duration of exposure slots in multi-beam writers |

| KR20200128363A (ko) | 2019-05-03 | 2020-11-12 | 아이엠에스 나노패브릭케이션 게엠베하 | 멀티 빔 라이터에서의 노출 슬롯의 지속 시간 조정 |

| KR20210132599A (ko) | 2020-04-24 | 2021-11-04 | 아이엠에스 나노패브릭케이션 게엠베하 | 대전 입자 소스 |

| EP4095882A1 (en) | 2021-05-25 | 2022-11-30 | IMS Nanofabrication GmbH | Pattern data processing for programmable direct-write apparatus |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6169125A (ja) * | 1984-08-06 | 1986-04-09 | Nippon Telegr & Teleph Corp <Ntt> | 荷電ビ−ム露光装置 |

| US4909864A (en) | 1986-09-16 | 1990-03-20 | Kawasaki Steel Corp. | Method of producing extra-low iron loss grain oriented silicon steel sheets |

| KR950002578B1 (ko) | 1991-03-13 | 1995-03-23 | 후지쓰 가부시끼가이샤 | 전자빔 노광방법 |

| JP3194541B2 (ja) | 1992-07-24 | 2001-07-30 | 富士通株式会社 | 電子ビーム露光装置 |

| US5369282A (en) * | 1992-08-03 | 1994-11-29 | Fujitsu Limited | Electron beam exposure method and system for exposing a pattern on a substrate with an improved accuracy and throughput |

| EP0739531B1 (de) | 1994-01-13 | 1998-07-08 | IMS Ionen Mikrofabrikations Systeme Gesellschaft m.b.H. | Teilchenoptisches abbildungssystem |

| US5528048A (en) * | 1994-03-15 | 1996-06-18 | Fujitsu Limited | Charged particle beam exposure system and method |

| JPH07273006A (ja) * | 1994-03-29 | 1995-10-20 | Fujitsu Ltd | 荷電粒子ビーム露光方法及びその装置 |

| DE19946447B4 (de) | 1998-10-13 | 2012-01-19 | Ims Nanofabrication Ag | Teilchenoptisches Abbildungssystem für Lithographiezwecke |

| US6768125B2 (en) * | 2002-01-17 | 2004-07-27 | Ims Nanofabrication, Gmbh | Maskless particle-beam system for exposing a pattern on a substrate |

| GB2408383B (en) | 2003-10-28 | 2006-05-10 | Ims Nanofabrication Gmbh | Pattern-definition device for maskless particle-beam exposure apparatus |

-

2005

- 2005-04-28 GB GB0508660A patent/GB2413694A/en not_active Withdrawn

- 2005-04-29 US US11/119,514 patent/US7368738B2/en not_active Expired - Fee Related

- 2005-05-02 JP JP2005134248A patent/JP4843248B2/ja not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9082581B2 (en) | 2013-10-11 | 2015-07-14 | Nuflare Technology, Inc. | Blanking device for multiple charged particle beams |

| US9190238B2 (en) | 2013-11-12 | 2015-11-17 | Nuflare Technology, Inc. | Blanking device for multi charged particle beam, and multi charged particle beam writing method |

| US10133186B2 (en) | 2016-10-20 | 2018-11-20 | Mapper Lithography Ip B.V. | Method and apparatus for aligning substrates on a substrate support unit |

Also Published As

| Publication number | Publication date |

|---|---|

| GB0508660D0 (en) | 2005-06-08 |

| JP2005328047A (ja) | 2005-11-24 |

| US20050242303A1 (en) | 2005-11-03 |

| GB2413694A (en) | 2005-11-02 |

| US7368738B2 (en) | 2008-05-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4843248B2 (ja) | 粒子ビーム露光の改善されたパターン規定装置 | |

| JP4858745B2 (ja) | 粒子ビーム処理のための新型のパターン画定法 | |

| NL2003304C2 (en) | Compensation of dose inhomogeneity and image distortion. | |

| JP4995261B2 (ja) | パターン化ビームの総合変調を持つ粒子ビーム露光装置 | |

| JP4423490B2 (ja) | パターンを基板上に露光するマスクレス粒子ビーム装置 | |

| JP5743886B2 (ja) | ターゲットを露光するための方法およびシステム | |

| EP2854154B1 (en) | Charged-particle multi-beam apparatus having correction plate | |

| US8222621B2 (en) | Method for maskless particle-beam exposure | |

| US10410831B2 (en) | Multi-beam writing using inclined exposure stripes | |

| JP5284442B2 (ja) | マスクレス粒子ビーム露光方法 | |

| JP4835897B2 (ja) | 帯電粒子マルチビーム露光装置 | |

| US20150028230A1 (en) | Method for charged-particle multi-beam exposure | |

| JP6589758B2 (ja) | マルチ荷電粒子ビーム描画装置及びマルチ荷電粒子ビーム描画方法 | |

| JP2008117871A (ja) | 電子ビーム描画装置及び電子ビーム描画方法 | |

| JP2005136409A (ja) | マスクレス粒子ビーム露光装置用パターン規定デバイス | |

| US11569064B2 (en) | Method for irradiating a target using restricted placement grids | |

| JP2018182189A (ja) | マルチ荷電粒子ビーム描画装置及びマルチ荷電粒子ビーム描画方法 | |

| JP2019071411A (ja) | 限定的位置付けグリッドを用いるターゲットの照射方法 | |

| JP2019114731A (ja) | マルチ荷電粒子ビーム描画装置及びマルチ荷電粒子ビーム描画方法 | |

| JP2018137358A (ja) | マルチ荷電粒子ビーム描画方法およびマルチ荷電粒子ビーム描画装置 | |

| JP7192254B2 (ja) | マルチ荷電粒子ビーム描画装置及びその調整方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070717 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20080314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080331 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080331 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20080314 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100930 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101221 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20101227 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110124 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110127 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110221 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110915 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111007 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141014 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |