JP4809568B2 - メモリ自己テストの方法と装置 - Google Patents

メモリ自己テストの方法と装置 Download PDFInfo

- Publication number

- JP4809568B2 JP4809568B2 JP2002288612A JP2002288612A JP4809568B2 JP 4809568 B2 JP4809568 B2 JP 4809568B2 JP 2002288612 A JP2002288612 A JP 2002288612A JP 2002288612 A JP2002288612 A JP 2002288612A JP 4809568 B2 JP4809568 B2 JP 4809568B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- test

- self

- data

- locations

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000015654 memory Effects 0.000 title claims description 356

- 238000010998 test method Methods 0.000 title claims description 46

- 238000012360 testing method Methods 0.000 claims description 295

- 238000012545 processing Methods 0.000 claims description 19

- 238000000034 method Methods 0.000 claims description 17

- 238000004519 manufacturing process Methods 0.000 claims description 13

- 238000001514 detection method Methods 0.000 claims description 9

- 230000005055 memory storage Effects 0.000 claims description 6

- 230000004044 response Effects 0.000 claims description 6

- 230000000295 complement effect Effects 0.000 claims description 3

- 230000008859 change Effects 0.000 claims description 2

- 239000002131 composite material Substances 0.000 claims description 2

- 238000013461 design Methods 0.000 description 34

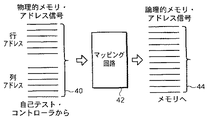

- 238000013507 mapping Methods 0.000 description 27

- 238000003491 array Methods 0.000 description 20

- 238000010586 diagram Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 230000007246 mechanism Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 239000007787 solid Substances 0.000 description 6

- 230000007547 defect Effects 0.000 description 4

- 239000003292 glue Substances 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000009471 action Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 238000013100 final test Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000008439 repair process Effects 0.000 description 2

- 102000010410 Nogo Proteins Human genes 0.000 description 1

- 108010077641 Nogo Proteins Proteins 0.000 description 1

- 241000282372 Panthera onca Species 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000011990 functional testing Methods 0.000 description 1

- 230000008571 general function Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/14—Implementation of control logic, e.g. test mode decoders

- G11C29/16—Implementation of control logic, e.g. test mode decoders using microprogrammed units, e.g. state machines

Landscapes

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Tests Of Electronic Circuits (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Microcomputers (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US025816 | 2001-12-26 | ||

| US10/025,816 US7269766B2 (en) | 2001-12-26 | 2001-12-26 | Method and apparatus for memory self testing |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009243543A Division JP2010015689A (ja) | 2001-12-26 | 2009-10-22 | メモリ自己テストの方法と装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003229000A JP2003229000A (ja) | 2003-08-15 |

| JP2003229000A5 JP2003229000A5 (enExample) | 2005-07-14 |

| JP4809568B2 true JP4809568B2 (ja) | 2011-11-09 |

Family

ID=21828202

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002288612A Expired - Lifetime JP4809568B2 (ja) | 2001-12-26 | 2002-10-01 | メモリ自己テストの方法と装置 |

| JP2009243543A Abandoned JP2010015689A (ja) | 2001-12-26 | 2009-10-22 | メモリ自己テストの方法と装置 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009243543A Abandoned JP2010015689A (ja) | 2001-12-26 | 2009-10-22 | メモリ自己テストの方法と装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7269766B2 (enExample) |

| JP (2) | JP4809568B2 (enExample) |

| GB (1) | GB2383640B (enExample) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6968479B2 (en) * | 2002-03-06 | 2005-11-22 | Hewlett-Packard Development Company, L.P. | Verifying data in a data storage device |

| US7673193B1 (en) * | 2005-08-18 | 2010-03-02 | Rambus Inc. | Processor-memory unit for use in system-in-package and system-in-module devices |

| US7194670B2 (en) | 2004-02-13 | 2007-03-20 | International Business Machines Corp. | Command multiplier for built-in-self-test |

| JP4601305B2 (ja) * | 2004-02-27 | 2010-12-22 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP2005309787A (ja) * | 2004-04-21 | 2005-11-04 | Nec Electronics Corp | 中央演算処理装置及びマイクロコンピュータ |

| KR100735575B1 (ko) * | 2004-06-11 | 2007-07-04 | 삼성전자주식회사 | 메모리의 테스트 모드 인터페이스 방법 및 장치 |

| KR101014413B1 (ko) * | 2004-06-14 | 2011-02-15 | 삼성전자주식회사 | 데이터 캐쉬가 내장된 반도체 집적회로 및 그것의앳-스피드-테스트 방법 |

| US7254793B2 (en) * | 2005-02-04 | 2007-08-07 | Synopsys, Inc. | Latch modeling technique for formal verification |

| US7434119B2 (en) * | 2005-03-07 | 2008-10-07 | Arm Limited | Method and apparatus for memory self testing |

| JP2006268919A (ja) * | 2005-03-22 | 2006-10-05 | Matsushita Electric Ind Co Ltd | メモリの組み込み自己テスト回路および自己テスト方法 |

| US7490280B2 (en) | 2006-02-28 | 2009-02-10 | International Business Machines Corporation | Microcontroller for logic built-in self test (LBIST) |

| US7870454B2 (en) * | 2006-09-12 | 2011-01-11 | International Business Machines Corporation | Structure for system for and method of performing high speed memory diagnostics via built-in-self-test |

| US7805644B2 (en) * | 2007-12-29 | 2010-09-28 | Texas Instruments Incorporated | Multiple pBIST controllers |

| KR20120069404A (ko) | 2010-12-20 | 2012-06-28 | 삼성전자주식회사 | 테스터 및 이를 포함하는 테스트 시스템 |

| US9298573B2 (en) * | 2012-03-30 | 2016-03-29 | Intel Corporation | Built-in self-test for stacked memory architecture |

| US8935586B2 (en) * | 2012-11-08 | 2015-01-13 | International Business Machines Corporation | Staggered start of BIST controllers and BIST engines |

| US8996942B2 (en) * | 2012-12-20 | 2015-03-31 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Suspend SDRAM refresh cycles during normal DDR operation |

| US8904250B2 (en) | 2013-02-14 | 2014-12-02 | Micron Technology, Inc. | Autorecovery after manufacturing/system integration |

| US8943458B1 (en) * | 2013-09-16 | 2015-01-27 | International Business Machines Corporation | Determining chip burn-in workload using emulated application condition |

| JP6570608B2 (ja) * | 2017-12-21 | 2019-09-04 | キヤノン株式会社 | 検査装置、撮像装置、電子機器および輸送装置 |

| JP7031392B2 (ja) * | 2018-03-15 | 2022-03-08 | 富士通株式会社 | エミュレーション装置,エミュレーション方法及びエミュレーションプログラム |

| US10748635B2 (en) * | 2018-03-22 | 2020-08-18 | Marvell Asia Pte, Ltd. | Dynamic power analysis with per-memory instance activity customization |

| CN109710473A (zh) * | 2018-12-19 | 2019-05-03 | 四川虹美智能科技有限公司 | 一种soc板测试方法、装置及系统 |

| US10998075B2 (en) | 2019-09-11 | 2021-05-04 | International Business Machines Corporation | Built-in self-test for bit-write enabled memory arrays |

| US10971242B2 (en) | 2019-09-11 | 2021-04-06 | International Business Machines Corporation | Sequential error capture during memory test |

| US11069422B1 (en) | 2020-07-07 | 2021-07-20 | International Business Machines Corporation | Testing multi-port array in integrated circuits |

| JP7220317B1 (ja) | 2022-02-08 | 2023-02-09 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置およびプログラム方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5173906A (en) | 1990-08-31 | 1992-12-22 | Dreibelbis Jeffrey H | Built-in self test for integrated circuits |

| US5535164A (en) * | 1995-03-03 | 1996-07-09 | International Business Machines Corporation | BIST tester for multiple memories |

| US5661732A (en) * | 1995-05-31 | 1997-08-26 | International Business Machines Corporation | Programmable ABIST microprocessor for testing arrays with two logical views |

| US5633877A (en) * | 1995-05-31 | 1997-05-27 | International Business Machines Corporation | Programmable built-in self test method and controller for arrays |

| JP3274332B2 (ja) * | 1995-11-29 | 2002-04-15 | 株式会社東芝 | コントローラ・大容量メモリ混載型半導体集積回路装置およびそのテスト方法およびその使用方法、並びに半導体集積回路装置およびそのテスト方法 |

| US6001662A (en) * | 1997-12-02 | 1999-12-14 | International Business Machines Corporation | Method and system for providing a reusable configurable self-test controller for manufactured integrated circuits |

| DE19833208C1 (de) * | 1998-07-23 | 1999-10-28 | Siemens Ag | Integrierte Schaltung mit einer Selbsttesteinrichtung zur Durchführung eines Selbsttests der integrierten Schaltung |

| JP2001148199A (ja) * | 1999-11-19 | 2001-05-29 | Mitsubishi Electric Corp | 自己テスト回路内蔵半導体記憶装置 |

| JP2001236797A (ja) * | 1999-12-17 | 2001-08-31 | Fujitsu Ltd | 自己試験回路及びそれを内蔵するメモリデバイス |

| JP2001297598A (ja) * | 2000-04-11 | 2001-10-26 | Toshiba Corp | 半導体集積回路装置、及び半導体集積回路装置の自己テスト方法 |

| US20030167428A1 (en) * | 2001-04-13 | 2003-09-04 | Sun Microsystems, Inc | ROM based BIST memory address translation |

-

2001

- 2001-12-26 US US10/025,816 patent/US7269766B2/en not_active Expired - Lifetime

-

2002

- 2002-07-30 GB GB0217635A patent/GB2383640B/en not_active Expired - Lifetime

- 2002-10-01 JP JP2002288612A patent/JP4809568B2/ja not_active Expired - Lifetime

-

2009

- 2009-10-22 JP JP2009243543A patent/JP2010015689A/ja not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| GB0217635D0 (en) | 2002-09-11 |

| US7269766B2 (en) | 2007-09-11 |

| GB2383640A (en) | 2003-07-02 |

| JP2010015689A (ja) | 2010-01-21 |

| US20030120985A1 (en) | 2003-06-26 |

| JP2003229000A (ja) | 2003-08-15 |

| GB2383640B (en) | 2005-04-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4809568B2 (ja) | メモリ自己テストの方法と装置 | |

| US7062689B2 (en) | Method and apparatus for memory self testing | |

| JP3980827B2 (ja) | 半導体集積回路装置および製造方法 | |

| EP1377981B1 (en) | Method and system to optimize test cost and disable defects for scan and bist memories | |

| US6769081B1 (en) | Reconfigurable built-in self-test engine for testing a reconfigurable memory | |

| US7428680B2 (en) | Programmable memory built-in-self-test (MBIST) method and apparatus | |

| US6643807B1 (en) | Array-built-in-self-test (ABIST) for efficient, fast, bitmapping of large embedded arrays in manufacturing test | |

| US6370661B1 (en) | Apparatus for testing memory in a microprocessor | |

| US7213186B2 (en) | Memory built-in self test circuit with full error mapping capability | |

| WO2007103745A2 (en) | At-speed multi-port memory array test method and apparatus | |

| US20030074618A1 (en) | Dual mode ASIC BIST controller | |

| US7257745B2 (en) | Array self repair using built-in self test techniques | |

| US6862704B1 (en) | Apparatus and method for testing memory in a microprocessor | |

| US20090172487A1 (en) | Multiple pBIST Controllers | |

| CN110415751B (zh) | 一种可参数化配置的存储器内建自测试电路 | |

| US20030074620A1 (en) | Configurable asic memory bist controller employing multiple state machines | |

| Cheng | Comprehensive study on designing memory BIST: algorithms, implementations and trade-offs | |

| US7475313B2 (en) | Unique pBIST features for advanced memory testing | |

| US6901543B2 (en) | Utilizing slow ASIC logic BIST to preserve timing integrity across timing domains | |

| KR100786414B1 (ko) | Dut 테스터 데이터 채널 반전 특성 관리 장치 | |

| US20240210471A1 (en) | Electronic device and method of testing electronic device | |

| JP4922506B2 (ja) | 半導体メモリ試験装置 | |

| Narahari et al. | Modeling and Simulation Experiment on a Built-In Self Test for Memory Fault Detection in SRAM | |

| US20070118778A1 (en) | Method and/or apparatus to detect and handle defects in a memory | |

| Tadiparti | Memory BIST |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080215 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080515 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080520 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080613 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090623 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091022 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20091102 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20091204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100915 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100921 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101004 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20101007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110713 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110819 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140826 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4809568 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |