JP4741192B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4741192B2 JP4741192B2 JP2004008892A JP2004008892A JP4741192B2 JP 4741192 B2 JP4741192 B2 JP 4741192B2 JP 2004008892 A JP2004008892 A JP 2004008892A JP 2004008892 A JP2004008892 A JP 2004008892A JP 4741192 B2 JP4741192 B2 JP 4741192B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- film

- substrate

- composition

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 102

- 239000004065 semiconductor Substances 0.000 title claims description 68

- 238000004519 manufacturing process Methods 0.000 title claims description 44

- 239000000758 substrate Substances 0.000 claims description 125

- 239000000203 mixture Substances 0.000 claims description 59

- 238000010438 heat treatment Methods 0.000 claims description 54

- 239000007789 gas Substances 0.000 claims description 31

- 239000004020 conductor Substances 0.000 claims description 24

- 238000007599 discharging Methods 0.000 claims description 22

- 239000012298 atmosphere Substances 0.000 claims description 13

- 238000011282 treatment Methods 0.000 claims description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 5

- -1 polytetrafluoroethylene Polymers 0.000 claims description 4

- 229920001343 polytetrafluoroethylene Polymers 0.000 claims description 3

- 239000004810 polytetrafluoroethylene Substances 0.000 claims description 3

- 229910001873 dinitrogen Inorganic materials 0.000 claims 1

- 238000003825 pressing Methods 0.000 claims 1

- 239000010408 film Substances 0.000 description 193

- 239000010410 layer Substances 0.000 description 123

- 239000000463 material Substances 0.000 description 49

- 239000004973 liquid crystal related substance Substances 0.000 description 34

- 238000012545 processing Methods 0.000 description 32

- 239000002904 solvent Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 17

- 230000008569 process Effects 0.000 description 17

- 239000002184 metal Substances 0.000 description 16

- 239000010409 thin film Substances 0.000 description 15

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- 229910021417 amorphous silicon Inorganic materials 0.000 description 14

- 239000012535 impurity Substances 0.000 description 14

- 239000011159 matrix material Substances 0.000 description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 14

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 13

- 239000011229 interlayer Substances 0.000 description 12

- 230000001681 protective effect Effects 0.000 description 12

- 239000003566 sealing material Substances 0.000 description 12

- 239000003990 capacitor Substances 0.000 description 11

- 238000005530 etching Methods 0.000 description 11

- 239000011521 glass Substances 0.000 description 11

- 230000015572 biosynthetic process Effects 0.000 description 10

- 239000010949 copper Substances 0.000 description 10

- 229920005989 resin Polymers 0.000 description 10

- 239000011347 resin Substances 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 10

- 238000012546 transfer Methods 0.000 description 10

- 238000000137 annealing Methods 0.000 description 9

- 229910052802 copper Inorganic materials 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 7

- 239000000956 alloy Substances 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 239000011651 chromium Substances 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- 238000004381 surface treatment Methods 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 238000002425 crystallisation Methods 0.000 description 6

- 239000010931 gold Substances 0.000 description 6

- 239000002245 particle Substances 0.000 description 6

- 238000002161 passivation Methods 0.000 description 6

- 125000006850 spacer group Chemical group 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 238000001035 drying Methods 0.000 description 5

- 239000000428 dust Substances 0.000 description 5

- 229910052737 gold Inorganic materials 0.000 description 5

- 239000004033 plastic Substances 0.000 description 5

- 229920003023 plastic Polymers 0.000 description 5

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 5

- 239000004332 silver Substances 0.000 description 5

- 239000007787 solid Substances 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 229910021419 crystalline silicon Inorganic materials 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 238000007639 printing Methods 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 238000009751 slip forming Methods 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 239000004372 Polyvinyl alcohol Substances 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 230000001678 irradiating effect Effects 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920002451 polyvinyl alcohol Polymers 0.000 description 3

- 235000012239 silicon dioxide Nutrition 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 230000018109 developmental process Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 235000019441 ethanol Nutrition 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910052744 lithium Inorganic materials 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 150000002894 organic compounds Chemical class 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000002985 plastic film Substances 0.000 description 2

- 229920006255 plastic film Polymers 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000008439 repair process Effects 0.000 description 2

- 239000010944 silver (metal) Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 230000032258 transport Effects 0.000 description 2

- 230000007723 transport mechanism Effects 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910001148 Al-Li alloy Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- MCMNRKCIXSYSNV-UHFFFAOYSA-N ZrO2 Inorganic materials O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 1

- JFBZPFYRPYOZCQ-UHFFFAOYSA-N [Li].[Al] Chemical compound [Li].[Al] JFBZPFYRPYOZCQ-UHFFFAOYSA-N 0.000 description 1

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 1

- 230000002745 absorbent Effects 0.000 description 1

- 239000002250 absorbent Substances 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 239000003963 antioxidant agent Substances 0.000 description 1

- 230000003078 antioxidant effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 1

- 229910002113 barium titanate Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000007664 blowing Methods 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- TVFDJXOCXUVLDH-UHFFFAOYSA-N caesium atom Chemical compound [Cs] TVFDJXOCXUVLDH-UHFFFAOYSA-N 0.000 description 1

- BRPQOXSCLDDYGP-UHFFFAOYSA-N calcium oxide Chemical compound [O-2].[Ca+2] BRPQOXSCLDDYGP-UHFFFAOYSA-N 0.000 description 1

- ODINCKMPIJJUCX-UHFFFAOYSA-N calcium oxide Inorganic materials [Ca]=O ODINCKMPIJJUCX-UHFFFAOYSA-N 0.000 description 1

- 239000000292 calcium oxide Substances 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000010891 electric arc Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 1

- 238000005984 hydrogenation reaction Methods 0.000 description 1

- 239000003230 hygroscopic agent Substances 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000001989 lithium alloy Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 239000003921 oil Substances 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 238000001579 optical reflectometry Methods 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- JMANVNJQNLATNU-UHFFFAOYSA-N oxalonitrile Chemical compound N#CC#N JMANVNJQNLATNU-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 238000002294 plasma sputter deposition Methods 0.000 description 1

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229940005642 polystyrene sulfonic acid Drugs 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 238000001552 radio frequency sputter deposition Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000009987 spinning Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 239000004408 titanium dioxide Substances 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 239000011882 ultra-fine particle Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

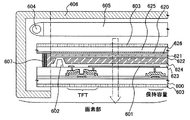

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Application Of Or Painting With Fluid Materials (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004008892A JP4741192B2 (ja) | 2003-01-17 | 2004-01-16 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003009106 | 2003-01-17 | ||

| JP2003009106 | 2003-01-17 | ||

| JP2004008892A JP4741192B2 (ja) | 2003-01-17 | 2004-01-16 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004241770A JP2004241770A (ja) | 2004-08-26 |

| JP2004241770A5 JP2004241770A5 (enExample) | 2006-12-21 |

| JP4741192B2 true JP4741192B2 (ja) | 2011-08-03 |

Family

ID=32964806

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004008892A Expired - Fee Related JP4741192B2 (ja) | 2003-01-17 | 2004-01-16 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4741192B2 (enExample) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006078859A (ja) * | 2004-09-10 | 2006-03-23 | Future Vision:Kk | 表示装置用の基板およびこの基板を用いた表示装置 |

| JP3967347B2 (ja) * | 2004-09-15 | 2007-08-29 | 株式会社フューチャービジョン | 配線形成基板及びそれを用いた表示装置 |

| JP4781066B2 (ja) * | 2004-09-30 | 2011-09-28 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| JP4801406B2 (ja) * | 2004-09-30 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 液晶表示装置の作製方法 |

| JP4754798B2 (ja) * | 2004-09-30 | 2011-08-24 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| JP4801407B2 (ja) * | 2004-09-30 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| US8148895B2 (en) * | 2004-10-01 | 2012-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method of the same |

| KR100998123B1 (ko) * | 2004-10-15 | 2010-12-02 | 파나소닉 주식회사 | 도전성 패턴 및 전자 디바이스의 제조 방법 및 전자디바이스 |

| JP4639758B2 (ja) * | 2004-11-09 | 2011-02-23 | セイコーエプソン株式会社 | 液体吐出方式による立体造形物の造形方法 |

| JP4749133B2 (ja) * | 2004-11-30 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4353145B2 (ja) * | 2005-06-29 | 2009-10-28 | セイコーエプソン株式会社 | 液滴吐出装置 |

| JP4252595B2 (ja) * | 2006-11-21 | 2009-04-08 | 株式会社 日立ディスプレイズ | 液晶表示装置とその製造方法 |

| KR100841374B1 (ko) * | 2007-01-02 | 2008-06-26 | 삼성에스디아이 주식회사 | 유기전계 발광표시장치의 제조방법 |

| JP5459896B2 (ja) * | 2007-03-05 | 2014-04-02 | 株式会社半導体エネルギー研究所 | 配線及び記憶素子の作製方法 |

| JP5364293B2 (ja) * | 2007-06-01 | 2013-12-11 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法およびプラズマcvd装置 |

| WO2009013811A1 (ja) * | 2007-07-24 | 2009-01-29 | Neuro Solution Corp. | 半導体装置 |

| JP5515285B2 (ja) * | 2008-07-25 | 2014-06-11 | 株式会社リコー | Mis積層構造体の作製方法およびmis積層構造体 |

| JP2009272511A (ja) * | 2008-05-09 | 2009-11-19 | Mimaki Engineering Co Ltd | 配線形成装置及び配線形成方法 |

| JP6003582B2 (ja) * | 2012-11-27 | 2016-10-05 | コニカミノルタ株式会社 | 透明電極の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06182980A (ja) * | 1992-12-22 | 1994-07-05 | Matsushita Electric Works Ltd | インクジェットプリンターによる印刷装置 |

| JP3725169B2 (ja) * | 1996-05-15 | 2005-12-07 | セイコーエプソン株式会社 | 塗布膜を有する薄膜デバイスの製造方法 |

| JP3926076B2 (ja) * | 1999-12-24 | 2007-06-06 | 日本電気株式会社 | 薄膜パターン形成方法 |

| JP2002246603A (ja) * | 2001-02-19 | 2002-08-30 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ及びその製造方法 |

-

2004

- 2004-01-16 JP JP2004008892A patent/JP4741192B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004241770A (ja) | 2004-08-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7648897B2 (en) | Method for manufacturing conductive layer and semiconductor device | |

| JP4667529B2 (ja) | 半導体装置の作製方法 | |

| JP4741192B2 (ja) | 半導体装置の作製方法 | |

| JP5256315B2 (ja) | 表示装置の作製方法 | |

| JP5238641B2 (ja) | 半導体装置の作製方法 | |

| KR101061891B1 (ko) | 배선의 제작 방법 | |

| JP4731913B2 (ja) | パターンの形成方法および半導体装置の製造方法 | |

| US20110073865A1 (en) | Display Device and Manufacturing Method Thereof | |

| JP4656843B2 (ja) | 半導体装置の作製方法 | |

| JP4737971B2 (ja) | 液晶表示装置および液晶表示装置の作製方法 | |

| JP4593969B2 (ja) | 配線の作製方法及び表示装置の作製方法 | |

| JP4619050B2 (ja) | 表示装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061108 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061108 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100916 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101118 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110426 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110506 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140513 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140513 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |