以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

(実施形態1)

本実施形態においては、結晶性半導体膜を有する逆スタガ型TFTの作製工程を、図1〜図2を用いて説明する。

図1(A)に示すように、基板101上に第1の導電膜102を形成し、第1の導電膜102上に感光性材料103を塗布又は吐出し乾燥焼成する。次に、感光性材料103を、フォトマスクを用いて部分的に感光、現像し、図1(B)に示すような第1のマスク111、112を形成する。

基板101としては、ガラス基板、石英基板、アルミナなどのセラミック等絶縁物質で形成される基板、シリコンウェハ、金属板等を用いることができる。また、基板101として、320mm×400mm、370mm×470mm、550mm×650mm、600mm×720mm、680mm×880mm、1000mm×1200mm、1100mm×1250mm、1150mm×1300mmのような大面積基板を用いることができる。

第1の導電膜102は、PVD法(Physical Vapor Deposition)、CVD法(Chemical Vapor Deposition)、蒸着法等により基板全面に形成する。

第1の導電膜102は、高融点材料を用いて形成することが好ましい。高融点材料を用いることにより、後の結晶化工程、ゲッタリング工程、活性化工程等の加熱工程が可能となる。高融点材料としては、タングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)等の金属又はその合金、若しくはその金属窒化物を適宜用いることができる。また、これら複数の膜を積層して形成しても良い。代表的には、基板表面側から窒化タンタル膜及びその上に形成されるタングステン膜、窒化タンタル膜及びその上に形成されるモリブデン、窒化チタン膜及びその上に形成されるタングステン膜、窒化チタン膜及びその上に形成されるモリブデン膜等の積層構造としてもよい。また、リンを含有する珪素膜(非晶質半導体膜、結晶性半導体膜を含む)、酸化インジウムスズ、酸化亜鉛、酸化インジウム亜鉛、ガリウムを添加した酸化亜鉛、又は酸化珪素を含む酸化インジウムスズを用いることもできる。

感光性材料103の材料としては、紫外光から赤外光に感光する材料ネガ型感光性材料又はポジ型感光性材料を用いる。感光性材料の代表例としては、エポキシ樹脂、クリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の感光性を示す樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの感光性を示す有機材料等を用いることができる。また、代表的なポジ型感光性樹脂として、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物を有する感光性樹脂が挙げられ、ネガ型感光性樹脂として、ベース樹脂、ジフェニルシランジオール及び酸発生剤などを有する感光性樹脂が挙げられる。

次に、図1(C)に示すように、第1のマスクを用いて、第1の導電膜102をエッチングして、第2の導電膜121a、122aを形成する。第2の導電膜121aは、ゲート電極として機能し、第2の導電膜122aは、ゲート電極においてゲート配線と接続する領域(以下、ゲート電極の接続部と示す。)である。なお、図1(C)においては、第2の導電膜121a、122aは分断された状態で表示されているが、実際には図3(C)に示すように、接続された同一の領域である。

次に、第1のマスクを除去した後、膜厚10〜200nm、好ましくは50〜100nmの第1の絶縁膜123を形成し、第1の絶縁膜上に触媒元素を有する層125及び膜厚50〜250nmの第1の半導体膜124を形成する。ここでは触媒元素とは半導体膜の結晶化を促進又は助長させる元素のことである。なお、この段階では加熱による結晶化は行わない。

第1の絶縁膜123は、ゲート絶縁膜として機能する。第1の絶縁膜123は、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)などを適宜用いることができる。更には、第2の導電膜121a、122aを陽極酸化して、第1の絶縁膜の代わりに、陽極酸化膜を形成しても良い。なお、基板側から不純物などの拡散を防止するため、基板側に接する絶縁膜として、窒化珪素(SiNx)、窒化酸化珪素(SiNxOy)(x>y)などを用い、後に形成される第1の半導体膜124との界面特性から、酸化珪素(SiOx)、酸化窒化珪素(SiOxNy)(x>y)を第1の半導体膜側に形成して、積層構造の第1の絶縁膜を形成することが望ましい。しかしながら、該構造に限定されず、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)等のいずれかを適宜組み合わせて積層構造としてもよい。なお、酸化珪素(SiOx)膜には、水素が含まれている。第1の絶縁膜123は、CVD法、PVD法等の公知の手法により形成する。

また、半導体膜に接する絶縁膜123の最上層に、膜厚0.01〜10nm、好ましくは1〜3nmの窒化珪素膜、あるいは窒化珪素酸化膜を形成すると好ましい。本実施の形態では、半導体膜に結晶化を促進する触媒元素(本実施の形態ではニッケルを用いる)を添加し、結晶化と同時にゲッタリング処理を行って除去する。酸化珪素膜と珪素膜との界面状態は良好であるが、界面において珪素膜中の触媒元素と酸化珪素中の酸素が反応し、金属酸化物(本実施の形態では酸化ニッケル(NiOx))になりやすく、触媒元素がゲッタリングされにくくなる場合がある。また、窒化珪素膜は、窒化珪素膜の応力や、トラップの影響により、半導体膜との界面状態に悪影響を与える恐れがある。よって、半導体膜に接する絶縁膜の最上層に、膜厚0.01〜10nm、好ましくは1〜3nmの窒化珪素膜、あるいは窒化酸化珪素膜を形成する。本実施の形態では、基板101上に窒化酸化珪素膜と酸化窒化珪素膜とを積層した後、酸化窒化珪素膜上に膜厚1〜3nmの窒化酸化珪素膜を形成し、3層の積層構造とする。このような構造であると、半導体膜中の触媒元素のゲッタリング効率も上がり、かつ半導体膜への窒化珪素膜の悪影響も軽減できる。また積層される絶縁膜は、同チャンバー内で真空を破らずに同一温度下で、反応ガスを切り変えながら連続的に形成するとよい。真空を破らずに連続的に形成すると、積層する膜同士の界面が汚染されるのを防ぐことができる。なお、本発明の実施形態においては、第1の絶縁膜123を3層構造で示しているが、これらを代表して第1の絶縁膜123として示す。

第1の半導体膜124としては、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体、非晶質半導体中に0.5nm〜20nmの結晶粒を観察することができる微結晶半導体、及び結晶性半導体から選ばれたいずれかの状態を有する膜で形成する。特に、0.5nm〜20nmの結晶粒を観察することができる微結晶状態はいわゆるマイクロクリスタル(μc)と呼ばれている。いずれも、シリコン、シリコン・ゲルマニウム(SiGe)等を主成分とする半導体膜を用いることができる。なお、セミアモルファスシリコンを、以下セミアモルファス半導体とも表記する。

なお、後の結晶化で良質な結晶構造を有する半導体膜を得るためには、第1の半導体膜124の膜中に含まれる酸素、窒素などの不純物濃度を5×1018/cm3(以下、濃度はすべて二次イオン質量分析法(SIMS)にて測定した原子濃度として示す。)以下に低減させておくと良い。これらの不純物は、触媒元素と反応しやすく、後の結晶化を妨害する要因となり、また、結晶化後においても捕獲中心や再結合中心の密度を増加させる要因となる。

触媒元素を有する層125の形成方法としては、PVD法、CVD法、蒸着法等により第1の絶縁膜123表面に、触媒元素又は触媒元素の珪化物の薄膜を形成する方法、第1の半導体膜124表面に触媒元素を含む溶液を塗布する方法などがある。触媒元素としては、タングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、チタン(Ti)、銅(Cu)、ニッケル(Ni)、白金(Pt)等の一つ又は複数を用いて形成することができる。ここでは、1〜200ppm、好ましくは10〜150ppmのニッケルを含む溶液を塗布する。

次に、TFTのチャネル領域となる領域に3族元素(13族元素、以下、アクセプター型元素と示す。)、または5族元素(15族元素、以下、ドナー型元素と示す。)を低濃度に添加するチャネルドープ工程を全面または選択的に行う。このチャネルドープ工程は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加する。なお、質量分離を行うイオン注入法を用いてもよい。

次に、第1の半導体膜124上に、ドナー型元素が含まれる膜厚80〜250nmの第2の半導体膜132を形成する。珪化物気体にリン、ヒ素のようなドナー型元素を有する気体を加えたプラズマCVD法で成膜する。このような手法により第2の半導体膜を形成することで、第1の半導体膜と第2の半導体膜との界面が形成される。また、ドナー型元素が含まれる第2の半導体膜132としては、第1の半導体膜と同様の半導体膜を形成した後、ドナー型元素をイオンドープ法又はイオン注入法により添加して形成することができる。このときの、第2の半導体膜132では、リンの濃度が1×1019〜3×1021/cm3であることが好ましい。

さらには、上記プラズマCVD法、又はイオンドープ法、イオン注入法を用いて、第1の半導体膜124に接する側に、低濃度領域(以下、n-領域と示す。)、その上に高濃度領域(以下、n+領域と示す。)の積層構造としても良い。このとき、n-領域のドナー型元素の濃度は、1×1017〜3×1019/cm3、好ましくは1×1018〜1×1019/cm3とし、n+領域のドナー型元素の濃度は、n-領域のドナー型元素の10〜100倍とする。また、n-領域の膜厚は50〜200nmであり、n+領域の膜厚は30〜100nm好ましくは40〜60nmである。ここでは、第2の半導体膜132として、波線より第1の半導体膜124側の領域をn-領域とし、その表面にn+領域を示す。

このときのドナー型元素が含まれる第2の半導体膜の不純物のプロファイルを図16に示す。図16(A)は、第1の半導体膜124上に、プラズマCVD法によりドナー型元素が含まれる第2の半導体膜132aを形成した時の、ドナー型元素のプロファイル150aを示す。なお、第2の半導体膜132aは、表面からn+領域144a及びn-領域144bの界面までは、膜の深さ方向に対して一定の濃度(第1の濃度)のドナー型元素が分布している。また、n+領域144a及びn-領域144bの界面から、第1の半導体膜124の界面までは、膜の深さ方向に対して一定の濃度(第2の濃度)のドナー型元素が分布している。このとき、第1の濃度は第2の濃度より高い。

一方、図16(B)は、第1の半導体膜124上に、非晶質半導体、セミアモルファス半導体、微結晶半導体、及び結晶性半導体から選ばれたいずれかの状態を有する半導体膜を形成し、イオンドープ法又はイオン注入法により該半導体膜にドナー型元素を添加して第2の半導体膜132bを形成した時の、ドナー型元素のプロファイル150bを示す。図16(B)に示すように、第2の半導体膜132bの表面付近は、ドナー型元素濃度が比較的高い。この領域をn+領域144aと示す。一方、第1の半導体膜124に近づくにつれ、ドナー型元素濃度が減少している。ドナー型元素濃度が1×1017〜3×1019/cm3の領域、好ましくは1×1018〜1×1019/cm3の領域をn-領域144bと示す。また、n+領域144aのドナー型元素の濃度は、n-領域のドナー型元素の10〜100倍である。

n+領域144aは後にソース領域及びドレイン領域として機能し、n-領域144bはLDD領域として機能する。なお、n+領域とn-領域それぞれの界面は存在せず、相対的なドナー型元素濃度の、濃度の大小によって変化する。このようにイオンドープ法又はイオン注入法により形成されたドナー型元素が含まれる第2の半導体膜132aまたは132bは、添加条件によって濃度プロファイルを制御することが可能であり、n+領域とn-領域の膜厚を適宜制御することが可能である。

なお、ドナー型元素が含まれる第2の半導体膜132aまたは132bは、希ガス元素、代表的にはアルゴンが添加されることにより、結晶格子の歪が形成され、後に行われるゲッタリング工程で、より触媒元素をゲッタリングすることが可能である。

次に、第1の半導体膜124及び第2の半導体膜132を加熱して、第1の半導体膜124の結晶化を行うと共に、図1(E)の矢印で示すように、第1の半導体膜の結晶化を促した触媒元素を第2の半導体膜132に移動させて、触媒元素のゲッタリングを同時に行う。

結晶化は、半導体の結晶化を助長する触媒元素が接した半導体膜の部分でシリサイドが形成され、それを核として進行する。ここでは、脱水素化のための熱処理(400〜550℃、0.5〜2時間)の後、結晶化のための熱処理(550℃〜650℃で1〜24時間)を行う。また、RTA(Rapid Thermal Anneal)、GRTA(Gas Rapid Thermal Anneal)により結晶化を行っても良い。ここで、レーザ光照射を行わず結晶化することで、結晶性のばらつきを低減することが可能であり、後に形成されるTFTのばらつきを抑制することが可能である。また、結晶表面で突起上に結晶成長するリッジ(凸部)が形成されにくいため、半導体領域表面が比較的平坦であり、ゲート絶縁膜と介してゲート電極との間に流れるリーク電流を抑制することが可能である。

また、ゲッタリング工程により、結晶化された第1の半導体膜中の触媒元素がデバイス特性に影響を与えない濃度、即ち膜中のニッケル濃度が1×1018/cm3以下、望ましくは1×1017/cm3以下とすることができる。このような膜を第1の結晶性半導体膜141と示す。また、ゲッタリング後の触媒元素が移動した第2の半導体膜も同様に結晶化されているため、第2の結晶性半導体膜142と示す。更に、本実施形態においては、ゲッタリング工程と共に、第2の結晶性半導体膜142中のドナー型元素の活性化を行っている。

次に、図2(A)に示すように、第2の結晶性半導体膜142上に第2のマスク143を形成し、該第2のマスクを用いて第2の結晶性半導体膜142及び第1の結晶性半導体膜141をエッチングして、図2(B)に示すような第1の半導体領域152及び第2の半導体領域151を形成する。第2のマスク143を形成することで、後に形成される半導体領域の面積を縮小することが可能であり、半導体素子の高集積化や透過型液晶表示装置の開口率を高めることが可能である。

なお、以下の実施形態及び実施例のマスク形成工程において、半導体材料で形成される膜又は領域上に感光性材料を塗布する前には、半導体膜又は領域表面に、膜厚が数nm程度の絶縁膜を形成することが好ましい。この工程により半導体材料と感光性材料とが直接接触すること回避することが可能であり、不純物が半導体膜中に侵入するのを防止できる。なお、絶縁膜の形成方法としては、オゾン水等の酸化力のある溶液を塗布する方法、酸素プラズマ、オゾンプラズマを照射する方法等が挙げられる。

第2の結晶性半導体膜及び第1の結晶性半導体膜は、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3などを代表とするフッ素系ガス、あるいはO2を用いてエッチングすることができる。第2の結晶性半導体膜をエッチングして、第1の半導体領域152を形成し、第1の結晶性半導体膜をエッチングして第2の半導体領域151を形成する。

次に、第2のマスク143を除去した後、図2(C)に示すように、膜厚500〜1500nm、好ましくは500〜1000nmの第3の導電膜153を成膜する。次に、第3の導電膜153上に感光性材料を塗布し、露光した後、現像して、第3のマスク154を形成する。

第3の導電膜153の材料としては、銀(Ag)、金(Au)、銅(Cu)、ニッケル(Ni)、白金(Pt)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、タングステン(W)、アルミニウム(Al)、タンタル(Ta)、モリブデン(Mo)、カドミウム(Cd)、亜鉛(Zn)、鉄(Fe)、チタン(Ti)、シリコン(Si)、ゲルマニウム(Ge)、ジルコニウム(Zr)、バリウム(Ba)等の金属を用いることができる。また、これらの材料からなる導電膜を積層して第3の導電膜を形成することができる。第3の導電膜153は配線として機能する。配線抵抗を低下させるため、低抵抗材料を用いることが好ましい。

ここで、銅を配線として用いる場合のバリア膜としては、窒化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化チタン、窒化タンタルなど窒素を含む絶縁性又は導電性の物質を用いると良い。

次に、図2(D)に示すように第3のマスク154を用いて第3の導電膜153を所望の形状にエッチングして、第4の導電膜162、163を形成する。第4の導電膜162、163は、ソース電極及びドレイン電極として機能する。このとき、第3の導電膜を分断して、ソース電極及びドレイン電極を形成すると共に、ソース配線又はドレイン配線の幅が細くなるようにエッチングすることで、後に形成される液晶表示装置の開口率を高めることが可能である。

次に、第3のマスク154を用いて、第1の半導体領域152の露出部をエッチングして、ソース領域及びドレイン領域として機能する第3の半導体領域164、165を形成する。このとき、第2の半導体領域151の一部がオーバーエッチングされても良い。このときのオーバーエッチングされた第2の半導体領域を第4の半導体領域166と示す。第4の半導体領域166はチャネル形成領域として機能する。

次に、第3のマスクを除去した後、図2(E)に示すように、第4の導電膜162、163及び第4の半導体領域166表面上に、パッシベーション膜として機能する膜厚100〜300nmの第2の絶縁膜171を成膜することが好ましい。パッシベーション膜は、プラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化窒化アルミニウム、または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、その他の絶縁性材料を用いて形成することができる。なお、パッシベーション膜は単層でも積層構造でもよい。ここでは、第4の半導体領域166の界面特性から酸化珪素、又は酸化窒化珪素を形成し、その上に窒化珪素膜、又は窒化酸化珪素膜を成膜することが好ましい。

この後、第4の半導体領域を水素雰囲気又は窒素雰囲気で加熱して水素化することが好ましい。なお、窒素雰囲気で加熱する場合は、第2の絶縁膜に水素を含む絶縁膜を形成することが好ましい。

以上の工程により、結晶性半導体膜を有する逆スタガ型TFTを形成することができる。

次に、第2の絶縁膜171上に、膜厚500〜1500nmの第3の絶縁膜172を形成する。第3の絶縁膜としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシリカガラスに代表されるシロキサンポリマー系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi−O−Si結合を含む無機シロキサンポリマー、アルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表される珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサンポリマー系の絶縁材料を用いることができる。形成方法としては、CVD法、塗布法、印刷法等公知の手法を用いて形成する。なお、塗布法で形成することにより、第3の絶縁膜の表面を平坦化することが可能である。ここでは、塗布法によりアクリル樹脂を塗布し焼成して、第3の絶縁膜を形成する。また、反射型液晶表示装置や半透過型液晶表示装置の場合、第3の絶縁膜は凹凸を有することで、光をより外部に反射することが可能となる。この場合、第3の絶縁膜を液滴吐出法、印刷法等を用いることで、凹凸を有する絶縁膜を形成することが可能である。

なお、第2の絶縁膜171が、後に形成される第5の導電膜173と第4の導電膜162、163との間に寄生容量が生じない程度の膜厚を有する場合、第3の絶縁膜172は必ずしも必要ではない。

次に、第3の絶縁膜172上に第4のマスク(図示しない。)を形成した後、第3の絶縁膜172及び第2の絶縁膜171の一部をエッチングして、ゲート電極の接続部となる第2の導電膜122aを露出する。次に、第4のマスクを除去した後、ゲート配線として機能する膜厚500〜1500nm、好ましくは500〜1000nmの第5の導電膜173を形成する。第4のマスクは、第2のマスク143と同様の手法及び材料を適宜用いることが可能である。第5の導電膜173の材料及び形成方法は、第3の導電膜153と同様の材料及び形成方法を適宜選択すればよい。なお、配線抵抗を抑制するため、低抵抗材料を用いることが好ましい。

次に、第5の導電膜173及び第3の絶縁膜172上に第4の絶縁膜174を形成する。第4の絶縁膜174としては、第3の絶縁膜172と同様の材料を適宜用いることが可能である。また、反射型液晶表示装置又は半透過型液晶表示装置を形成する場合、第4の絶縁膜は凹凸を有することで、光をより外部に反射することが可能となる。この場合、第3の絶縁膜を液滴吐出法、印刷法等を用いることで、凹凸を有する絶縁膜を形成することが可能である。

次に、第4の絶縁膜174上に第5のマスク(図示しない。)を形成した後、第4の絶縁膜174、第3の絶縁膜172及び第2の絶縁膜171の一部をエッチングして、第4の導電膜163の一部を露出する。次に、第5のマスクを除去した後、画素電極として機能する膜厚100〜200nmの第6の導電膜175を形成する。第5のマスクは、第2のマスク143と同様の手法及び材料を適宜用いることが可能である。第6の導電膜175の代表的な材料としては、透光性を有する導電膜、又は反射性を有する導電膜がある。透光性を有する導電膜の材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)、酸化珪素を含む酸化インジウムスズ等が挙げられる。また、反射性を有する導電膜の材料としては、アルミニウム(Al)、チタン(Ti)、銀(Ag)、タンタル(Ta)などの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料、若しくは該金属の窒化物である窒化チタン(TiN)、窒化タンタル(TaN)などが挙げられる。さらには、半透過型液晶表示装置の場合、第6の導電膜を透光性を有する導電膜と、反射性を有する導電膜とで形成すれば良い。

第6の導電膜175の形成方法としては、液滴吐出法、スパッタリング法、蒸着法、CVD法、塗布法等を適宜用いる。液滴吐出法を用いることで、選択的に第6の導電膜を形成することが可能である。また、スパッタリング法、蒸着法、CVD法、塗布法等を用いた場合、第2の導電膜と同様にマスクを形成した後、該マスクを用いて導電膜をエッチングして第6の導電膜を形成する。

なお、ここでは第5の導電膜173としてはゲート配線として機能する導電膜を形成し、第6の導電膜175としては画素電極として機能する導電膜を形成したが、これに限定されない。画素電極として機能する導電膜を形成した後、ゲート配線として機能する導電膜を形成してもよい。

以上の工程により、アクティブマトリクス基板を形成することが可能である。

本実施形態の逆スタガ型TFTは、非晶質半導体膜の結晶化工程と、非晶質半導体膜の結晶化を促進するための触媒元素のゲッタリング工程とを同時に行うことが可能であるため、工程数の削減が可能である。特に、加熱処理数を削減できるため、省エネルギー化が可能であり、また、スループットを向上させることができる。

また、逆スタガ型TFTは、ゲート電極に耐熱性の高い材料を用いており、また活性化工程、ゲッタリング工程、結晶化工程等の加熱処理を行った後、低抵抗材料を用いて信号線、走査線等の配線を形成している。このため、結晶性を有し、不純物触媒元素が少なく、配線抵抗の低いTFTを形成することが可能である。また、本発明の液晶表示装置は、絶縁膜上に画素電極を形成することが可能であり、開口率を増加させることが可能である。

このため、結晶性半導体膜で形成されるため非晶質半導体膜で形成される逆スタガ型TFTと比較して移動度が高い。また、ソース領域及びドレイン領域には、ドナー型元素に加え、触媒元素をも含む。このため、半導体領域との接触抵抗の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な半導体装置を作製することが可能である。

更には、ゲッタリング工程により、成膜段階で半導体膜中に混入する触媒元素をもゲッタリングするため、オフ電流を低減することが可能である。このようなTFTを液晶表示装置のスイッチング素子に設けることにより、コントラストを向上させることが可能である。

(実施形態2)

本実施形態は、実施形態1において、触媒元素の添加領域の異なる例を、図20を用いて説明する。

図20(A)に示すように、実施形態1と同様に基板101上に第2の導電膜121a及び122aを形成し、その上に第1の絶縁膜123を形成する。

次に図20(B)に示すように、第1の絶縁膜123上に第1の半導体膜124を形成し、第1の半導体膜上に触媒元素を有する層125を形成する。

次に図20(C)に示すように、触媒元素を有する層125の上に、ドナー型元素が含まれる第2の半導体膜132を形成する。本実施形態ではリンを有する気体を加えたプラズマCVD方で成膜する。

次に、第1の半導体膜124及び第2の半導体膜132を加熱して、非晶質である第1の半導体膜124の結晶化を行うと共に、図20(D)の矢印で示すように、触媒元素を第2の半導体膜132に移動させて、触媒元素のゲッタリングを同時に行う。図20(D)中の矢印は、第1の半導体膜の結晶化を促した触媒元素の移動の方向である。更に、第2の半導体膜132中のドナー型元素の活性化も同時に行っている。なお、結晶化及びゲッタリング後の第1の半導体膜を第1の結晶性半導体膜141と示す。また、結晶化及びゲッタリング後の触媒元素が移動した第2の半導体膜を、第2の結晶性半導体膜142と示す。

この後、実施形態1と同様の工程により、結晶性半導体膜を有する逆スタガ型TFTを形成することができる。また、実施形態1と同様の効果を有する。

(実施形態3)

本実施形態は、実施形態1において、チャネル形成領域の形成方法の異なる例を図21を用いて説明する。

図21(A)に示すように、実施形態1と同様に、第1のマスク(図示しない。)を用いて基板101上に第2の導電膜121a及び122aを形成し、その上に第1の絶縁膜123を形成した後、第1の絶縁膜上に触媒元素を有する層125を形成する。

次に図21(B)に示すように、触媒元素を有する層125上に第1の半導体膜124を形成する。その上に絶縁膜を形成し、第2のマスク(図示しない。)を用いて絶縁膜の一部をエッチングして保護膜126を形成する。

次に図21(C)に示すように、第2の半導体膜132を基板全面に形成する。その後、熱処理を行うことによって、図21(D)に示すように第1の半導体膜124の結晶化及びゲッタリング及び第2の半導体膜の活性化を同時に行う。図21(D)中の矢印は、第1の半導体膜の結晶化を促した触媒元素が第2の結晶性半導体膜142へ移動する様子を模式的に表したものである。なお、結晶化及びゲッタリング後の第1の半導体膜を第1の結晶性半導体膜141と示す。また、結晶化及びゲッタリング後の触媒元素が移動した第2の半導体膜を、第2の結晶性半導体膜142と示す。

この後、実施形態1と同様の工程により、図21(E)に示すような結晶性半導体膜を有する逆スタガ型TFTを形成することができる。本実施形態のように保護膜を形成しておけば第2の半導体領域151をエッチングせず、残した状態で第3の導電膜153および第2の半導体膜132をエッチングすることができるため歩留まりを向上させることが可能である。また、実施形態1と同様の効果を有する。

(実施形態4)

本実施形態は、実施形態3において、触媒元素の添加領域が異なる例を、図37を用いて説明する。

図37(A)に示すように、実施形態1と同様に、第1のマスク(図示しない。)を用いて基板101上に第2の導電膜121a及び122aを形成し、その上に第1の絶縁膜123を形成した後、第1の絶縁膜上に第1の半導体膜124を形成する。

次に図37(B)に示すように、第1の半導体膜124上に触媒元素を有する層125を形成した後、絶縁膜を形成し、該絶縁膜の一部を第2のマスク(図示しない。)を用いてエッチングして、保護膜126を形成する。

次に図37(C)に示すように、基板全面に第2の半導体膜132を形成した後、熱処理を行い、図37(D)に示すように第1の非晶質半導体膜の結晶化及び触媒元素のゲッタリング及び、第2の半導体膜の活性化を行う。図37(D)中の矢印は、第1の半導体膜の結晶化を促した触媒元素が第2の結晶性半導体膜142へ移動する様子を模式的に表したものである。なお、結晶化及びゲッタリング後の第1の半導体膜を第1の結晶性半導体膜141と示す。また、結晶化及びゲッタリング後の触媒元素が移動した第2の半導体膜を、第2の結晶性半導体膜142と示す。

この後、実施形態1と同様の工程により、図37(E)に示すような結晶性半導体膜を有する逆スタガ型TFTを形成することができる。また、実施形態1と同様の効果を有する。

本実施形態で形成される逆スタガ型TFTは、ゲート電極に耐熱性の高い材料を用いており、また活性化工程、ゲッタリング工程、結晶化工程等の加熱処理を行った後、低抵抗材料を用いて信号線、走査線等の配線を形成している。このため、結晶性を有し、不純物触媒元素が少なく、配線抵抗の低いTFTを形成することが可能である。また、本発明の液晶表示装置は、絶縁膜上に画素電極を形成することが可能であり、開口率を増加させることが可能である。

このため、結晶性半導体膜で形成されるため非晶質半導体膜で形成される逆スタガ型TFTと比較して移動度が高い。また、ソース領域及びドレイン領域には、ドナー型元素に加え、触媒元素をも含む。このため、半導体領域との接触抵抗の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な半導体装置を作製することが可能である。

また、非晶質半導体膜で形成されるTFTと比較して、しきい値のずれが生じにくく、TFT特性のバラツキを低減することが可能である。このため、非晶質半導体膜で形成されるTFTをスイッチング素子として用いた液晶表示装置と比較して、表示ムラを低減することが可能であり、信頼性の高い半導体装置を作製することが可能である。

更には、ゲッタリング工程により、成膜段階で半導体膜中に混入する触媒元素をもゲッタリングするため、オフ電流を低減することが可能である。このようなTFTを液晶表示装置のスイッチング素子に設けることにより、コントラストを向上させることが可能である。

(実施形態5)

本実施形態では、実施形態1で示したアクティブマトリクス基板のソース配線、ゲート配線、及び画素電極の積層の構造について、図3を用いて説明する。

図3(A)は、本実施形態における逆スタガ型TFTと、ゲート配線として機能する第5の導電膜との積層構造を示す図であり、図3(C)のA−Bの断面構造に相当する。

図3(B)は、ソース配線として機能する第4の導電膜、ゲート配線として機能する第5の導電膜、ゲート電極の接続部として機能する第2の導電膜、及び画素電極として機能のする第6の導電膜の積層構造を示す図であり、図3(C)のC−Dの断面構造に相当する。以下、ソース配線として機能する第4の導電膜をソース配線162a、162b、ゲート配線として機能する第5の導電膜をゲート配線173a、173b、ゲート電極の接続部として機能する第2の導電膜をゲート電極の接続部122a、122b、及び画素電極として機能する第6の導電膜を画素電極175と示す。

図3(B)に示すように、ゲート電極の接続部122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線181、ソース配線162b、ドレイン電極163が形成される。また、容量配線181、ソース配線162b、ドレイン電極163、第1の絶縁膜123すべての上に第2の絶縁膜171、第3の絶縁膜172が形成され、第3の絶縁膜172上にゲート配線173aが形成される。即ち、ソース配線、ドレイン電極は、第2の絶縁膜171、第3の絶縁膜172を介してゲート配線173aと交差している。

図3(B)に示すように、ゲート配線173a及び第3の絶縁膜172全ての上に第4の絶縁膜174が形成され、第4の絶縁膜上に画素電極175が形成されている。即ち、第4の絶縁膜を介して、ゲート配線173aの一部を画素電極175が覆っている。画素電極175が形成される第4の絶縁膜174は、平坦化膜で形成されているため、後に画素電極間に充填される液晶材料の配向の乱れを抑制することが可能であり、液晶表示装置のコントラストを向上させることが可能である。

なお、ここでは、第4の絶縁膜174を、ゲート配線173及び第3の絶縁膜172全ての上に形成したが、ゲート配線173及びその周辺の第3の絶縁膜172を覆うように設けてもよい。

また、本実施形態では、図3(C)のE―Fで示すように、ソース配線上に画素電極の端部が形成されている。このため、透過型液晶表示装置の場合、画素電極端部で液晶材料の配向乱れが生じたとしても、その領域をソース配線が覆っているため、表示ムラを低減することが可能である。

(実施形態6)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図4を用いて説明する。

図4(A)は、本実施形態における逆スタガ型TFTとゲート配線との積層構造を示す図であり、図4(C)のA−Bの断面構造に相当する。第1の絶縁膜123上には、第4の半導体領域、ドレイン電極として機能する第4の導電膜(以下、ドレイン電極と示す。)163、画素電極1112、ゲート配線1113が形成される。ドレイン電極163と画素電極1112は絶縁膜を介さないで接続されている。また、ゲート電極の接続部122aとゲート配線1113とは、第1の絶縁膜123を介して接続されている。また、ソース配線162a、ドレイン電極163、画素電極1112、第1の絶縁膜123、ゲート配線1113上にはパッシベーション膜として機能する絶縁膜1114が形成される。

図4(B)は、ソース配線162b、ゲート配線1113、ゲート電極の接続部122b、及び画素電極1112の積層構造を示す図であり、図4(C)のC−Dの断面構造に相当する。

図4(B)に示すように、ゲート電極の接続部122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線181、ソース配線162b、ドレイン電極163、ドレイン電極163に接続する画素電極1112が形成される。また、容量配線181、ソース配線162b上に第2の絶縁膜1111が形成され、第2の絶縁膜1111上にゲート配線1113が形成される。即ち、ソース配線、ドレイン電極は、第2の絶縁膜1111を介してゲート配線1113と交差している。

また、ゲート配線1113と画素電極1112とが重なる領域に第3の絶縁膜を形成してもよい。この場合、画素電極が形成される領域を拡大することが可能であり、開口率を増加させることが可能である。

(実施形態7)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図5を用いて説明する。

図5(A)は、本実施形態における逆スタガ型TFTとゲート配線との積層構造を示す図であり、図5(C)のA−Bの断面構造に相当する。

図5(B)は、ソース配線162b、ゲート配線1121b、ゲート電極の接続部122b、及び画素電極1122の積層構造を示す図であり、図5(C)のC−Dの断面構造に相当する。

図5(B)に示すように、ゲート電極の接続部122a、122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線181、ソース配線162b、ドレイン電極163が形成される。また、容量配線181、ソース配線162b、ドレイン電極163、及び第1の絶縁膜123すべての上に第2の絶縁膜171、第3の絶縁膜172が形成され、第3の絶縁膜172上にゲート配線1121bが形成される。即ち、ソース配線162b、ドレイン電極163は、第2の絶縁膜171、第3の絶縁膜172を介してゲート配線1121bと交差している。

なお、ここでは、図5(C)に示すように、ゲート配線1121bは、画素ごとに形成されており、隣り合う画素に設けられたゲート電極の接続部122a、122bに接続されている。このため、ゲート配線1121bの材料は、特に低抵抗材料である必要はなく、材料の選択の幅が広がる。

また、第3の絶縁膜172全ての上に第4の絶縁膜174が形成され、第4の絶縁膜上に画素電極1122が形成されている。即ち、第4の絶縁膜174を介して、ゲート配線1121bの一部を画素電極1122が覆っている。画素電極1122が形成される第4の絶縁膜174は、平坦化膜で形成されているため、後に画素電極間に充填される液晶材料の配向の乱れを抑制することが可能であり、液晶表示装置のコントラストを向上させることが可能である。

なお、ここでは、第4の絶縁膜174を、ゲート配線1121b及び第3の絶縁膜172全ての上に形成したが、ゲート配線1121b及びその周辺の第3の絶縁膜172を覆うように設けてもよい。

(実施形態8)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図6を用いて説明する。

図6(A)は、本実施形態における逆スタガ型TFTとゲート配線との積層構造を示す図であり、図6(C)のA−Bの断面構造に相当する。第1の絶縁膜123上には、第4の半導体領域、ドレイン電極163、画素電極1132、ゲート配線1133aが形成される。ドレイン電極163と画素電極1132は絶縁膜を介さないで接続されている。

図6(B)は、ソース配線162b、ゲート配線1133b、ゲート電極の接続部122b、及び画素電極1132の積層構造を示す図であり、図6(C)のC−Dの断面構造に相当する。

図6(B)に示すように、ゲート電極の接続部122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線181、ソース配線162b、ドレイン電極163、ドレイン電極163に接続する画素電極1132が形成される。また、容量配線181、ソース配線162b上に第2の絶縁膜1131が形成され、第2の絶縁膜1131上にゲート配線1133bが形成される。即ち、ソース配線、ドレイン電極は、第2の絶縁膜1131を介してゲート配線1133bと交差している。

また、ゲート配線1133bと画素電極1132とが重なる領域に第3の絶縁膜を形成してもよい。この場合、画素電極が形成する領域を拡大することが可能であり、開口率を増加させることが可能である。

(実施形態9)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図7を用いて説明する。

図7(A)は、本実施形態における逆スタガ型TFTとゲート配線として機能する第5の導電膜との積層構造を示す図であり、図7(C)のA−Bの断面構造に相当する。

図7(B)は、ソース配線1143b、ゲート配線1145a、1145b、ゲート電極の接続部122b、及び画素電極1142の積層構造を示す図であり、図7(C)のC−Dの断面構造に相当する。

図7(B)に示すように、ゲート電極の接続部122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線1144、ソース配線1143b、ドレイン電極1147、ゲート配線1145a、1145bが形成される。なお、ゲート配線1145a、1145bは、それぞれ第1の絶縁膜123を介してゲート電極の接続部122a、122bに接続されている。

また、図7(C)に示すように、ゲート配線1145a、1145bは、各画素にそれぞれ設けられている。ここでは、ゲート配線1145a、1145bとソース配線1143b、ドレイン電極1143a、容量配線1144それぞれは、交差していない。このためこれらの電極及び配線を同時に形成できるため、量産性を向上させることが可能である。

また、ゲート配線1145a、1145bとソース配線1143b、ドレイン電極1143a、容量配線1144すべての上に第2の絶縁膜171、第3の絶縁膜172が形成され、第3の絶縁膜172上に導電膜1146a、1146bが形成される。また、導電膜1146a、1146bは、第2の絶縁膜171、第3の絶縁膜172を介して、それぞれゲート配線1145a、1145bと接続している。このため、各画素に設けられたゲート配線は、導電膜1146a、1146bを介して電気的に接続している。また、ソース配線は、第2の絶縁膜171、第3の絶縁膜172を介してゲート配線1145a、1145b及び導電膜1146a、1146bと交差している。

なお、ここでは、導電膜1146a、1146bは、画素ごとに形成されており、隣り合う画素に設けられたゲート電極の接続部122a、122bに接続されている。このため、導電膜1146a、1146bの材料の選択の幅が広がる。

また、第3の絶縁膜172上に第4の絶縁膜174が形成され、第4の絶縁膜上に画素電極1142が形成されている。即ち、第4の絶縁膜を介して、導電膜1146bの一部を画素電極1142が覆っている。画素電極1142が形成される第4の絶縁膜174は、平坦化膜で形成されているため、後に画素電極間に充填される液晶材料の配向の乱れを抑制することが可能であり、液晶表示装置のコントラストを向上させることが可能である。

なお、ここでは、第4の絶縁膜174を、ゲート配線1145a、1145b及び第3の絶縁膜172全ての上に形成したが、ゲート配線1145a、1145b及びその周辺の第3の絶縁膜172を覆うように設けてもよい。

(実施形態10)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図8を用いて説明する。

図8(A)は、本実施形態における逆スタガ型TFTとゲート配線との積層構造を示す図であり、図8(C)のA−Bの断面構造に相当する。第1の絶縁膜123上には、ソース配線1153a、第4の半導体領域、ドレイン電極1157、画素電極1152、ゲート配線1155aが形成される。ドレイン電極1157と画素電極1152は絶縁膜を介さないで接続されている。

図8(B)は、ソース配線1153b、ゲート配線1155a、1155b、ゲート電極の接続部122b、及び画素電極1152の積層構造を示す図であり、図8(C)のC−Dの断面構造に相当する。

図8(B)に示すように、ゲート電極の接続部122b上に第1の絶縁膜123が形成され、第1の絶縁膜123上に、容量配線1154、ソース配線1153b、ドレイン電極1157、ドレイン電極1157に接続する画素電極1152、ゲート配線1155a、1155bが形成される。また、容量配線1154、ソース配線1153b上に第2の絶縁膜1151が形成され、第2の絶縁膜1151上に導電膜1156bが形成される。ゲート配線1155a、1155bは、各画素にそれぞれ設けられている。ここでは、ゲート配線1155a、1155bとソース配線1153b、ドレイン電極1157、容量配線1154それぞれは、交差しておらず、同時に形成できるため、量産性を向上させることが可能である。

また、導電膜1156a、1156bは、第2の絶縁膜1151を介して、それぞれゲート配線1155a、1155bと接続している。このため、各画素に設けられたゲート配線は、導電膜1156a、1156bを介して電気的に接続している。また、ソース配線、ドレイン電極は、第2の絶縁膜1151を介してゲート配線1155a、1155b及び導電膜1156a、1156bと交差している。

本実施形態では、ソース配線、容量配線と、ゲート配線とが交差する領域にのみ第2の絶縁膜1151を設けている。

また、ソース配線1153a、容量配線1154、導電膜1156bと画素電極1152とが重なる領域に第3の絶縁膜を形成してもよい。この場合、画素電極が形成される領域を拡大することが可能であり、開口率を増加させることが可能である。

(実施形態11)

本実施形態では、ゲート配線とソース配線の積層構造の異なるアクティブマトリクス基板について図34を用いて説明する。

図34(A)は、本実施形態における逆スタガ型TFTとゲート配線との積層構造を示す図であり、図34(C)のA−Bの断面構造に相当する。第1の絶縁膜123上には、第4の半導体領域、ドレイン電極1157、画素電極1152が形成される。ドレイン電極1157と画素電極1152は絶縁膜を介さないで接続されている。また、ゲート電極の接続部122a上の第1の絶縁膜は除去されており、その上にゲート配線1165aが形成されている。このような構造により、ゲート電極の接続部とゲート配線との接触抵抗を抑制することが可能である。また、本実施形態のようなゲート電極の接続部122aとゲート配線1165aとの接続構造を、実施形態2乃至実施形態10それぞれに適用することが可能である。

図34(B)は、ソース配線1163b、ゲート配線1165a、1165b、導電膜123b、及び画素電極1152の積層構造を示す図であり、図34(C)のC−Dの断面構造に相当する。

図34(B)に示すように、第2の導電膜121a、ゲート電極の接続部122aと同様の工程で形成された導電膜123bが基板表面には、形成されている。また、ゲート電極の接続部122a表面の第1の絶縁膜を除去するときに、導電膜123bの表面上の第1の絶縁膜を除去する。この後、導電膜123b上に第2の絶縁膜1161形成する。このとき、導電膜123bの両端部が露出するように、第2の絶縁膜1161を形成することが好ましい。

次に、第1の絶縁膜上にドレイン電極を形成すると同時に、導電膜123b上にゲート配線1165a、1165bを形成し、また同時に第2の絶縁膜1161上にソース配線1163b、容量配線1164を形成する。ここでは、これらの導電膜は、交差しておらず、同時に形成できるため、量産性を向上させることが可能である。

また、本実施形態では、画素ごとに形成されたゲート配線1165a、1165bが導電膜123a、123bを介して電気的に接続されている。また、導電膜123b上に形成された第2の絶縁膜1161を介して、ゲート配線とソース配線とが交差している。

本実施形態では、ソース配線、容量配線と、ゲート配線とが交差する領域にのみ第2の絶縁膜1161を設けている。

また、ゲート配線1165a、1165b、容量配線1164、及びソース配線1163a、1163bと画素電極1152とが重なる領域に、第3の絶縁膜を形成してもよい。この場合、画素電極を形成する領域を拡大することが可能であり、開口率を増加させることが可能である。

(実施形態12)

本実施形態では、ドナー型元素を有する半導体膜の代わりに、希ガス元素を有する半導体膜を用いて触媒元素をゲッタリングしてTFTを形成する工程について、図9を用いて説明する。

図9(A)に示すように、実施形態1と同様の工程により第1の半導体膜124を形成する。なお、この後チャネルドープ工程を行っても良い。

次に、第1の半導体膜124上にPVD法、CVD法等の公知の手法により希ガス元素を有する第2の半導体膜232を形成する。第2の半導体膜232としては、非晶質半導体膜であることが好ましい。

次に、第1の半導体膜124及び第2の半導体膜232を実施形態1と同様の手法により加熱して、第1の半導体膜を結晶化すると共に、図9(B)の矢印で示すように、第1の半導体膜124の結晶化を促した触媒元素を第2の半導体膜232に移動させて、触媒元素をゲッタリングする。この工程により、実施形態1と同様に第1の半導体膜中の触媒元素がデバイス特性に影響を与えない濃度、即ち膜中の触媒元素濃度が1×1018/cm3以下、望ましくは1×1017/cm3以下とすることができる。このような膜を第1の結晶性半導体膜241と示す。また、ゲッタリング後の触媒元素が移動した第2の半導体膜も同様に結晶化されているため、第2の結晶性半導体膜242と示す。

次に、図9(C)に示すように、第2の結晶性半導体膜242を除去した後、導電性を有する第3の半導体膜243を成膜する。ここで、第3の半導体膜243としては、珪化物気体にボロン、リン、ヒ素のような13族(3族)又は15族(5族)の元素を有する気体を加えたプラズマCVD法で成膜する。なお、第3の半導体膜243は、非晶質半導体、セミアモルファス半導体、結晶性半導体、マイクロクリスタル(μc)から選ばれたいずれかの状態を有する膜で形成すればよい。なお、第3の半導体膜243が導電性を有する非晶質半導体膜、セミアモルファス半導体、又はマイクロクリスタル(μc)のいずれかである場合は、この後、不純物を活性化する加熱処理を行う。一方、第2の結晶性半導体膜242が導電性を有する結晶性半導体である場合、加熱処理は行わなくとも良い。ここでは、プラズマCVD法により、膜厚100nmのリンが含まれる非晶質珪素膜を成膜した後、550度2時間で加熱して、不純物を活性化する。

次に、図9(D)に示すように、実施形態1と同様の工程により第1の半導体領域252、第2の半導体領域251、第3の導電膜153を形成する。次に、感光性材料を塗布又は吐出した後、露光、現像を行い、図9(D)に示すようなマスク254を形成する。

次に、図9(E)に示すように、ソース電極(ソース配線)162a及びドレイン電極(ドレイン配線)163を形成する。また、実施形態1と同様の工程により、第1の半導体領域をエッチングしてソース領域及びドレイン領域として機能する第3の半導体領域262、及びチャネル形成領域として機能する第4の半導体領域261を形成することができる。

この後、実施形態1と同様の工程により、逆スタガ型TFT及びアクティブマトリクス基板を形成することができる。本実施形態で形成されるTFTを用いることにより実施形態1と同様の効果を得ることができる。また、実施形態1乃至実施形態11のいずれかにも、本実施形態を適用することが可能である。

(実施形態13)

本実施形態では、nチャネルTFTとpチャネルTFTとを同一基板に形成する工程を図10を用いて形成する。

図10(A)に示すように、実施形態1と同様に基板101上に第1の導電膜301、302を形成し、第1の導電膜上に第1の絶縁膜123を形成する。次に、実施形態1と同様の工程により、触媒元素を有する層、及び第1の半導体膜、及びその上にドナー型元素が含まれる第2の半導体膜を形成する。次に、マスクを用いて、第1の半導体膜を所望の形状にエッチングして、第1の半導体領域を形成し、第2の半導体膜を所望の形状にエッチングして、第2の半導体領域を形成する。

次に、第1の半導体領域及び第2の半導体領域を加熱して、第1の半導体領域に含まれる触媒元素を第2の半導体領域に移動させて、触媒元素をゲッタリングする。ここでは、ゲッタリング後の触媒元素が移動した第2の半導体領域を第3の半導体領域312、313と示し、触媒元素濃度が低減された第1の半導体領域を第4の半導体領域311、314と示す。なお、第3の半導体領域及び第4の半導体領域は、それぞれゲッタリング工程の加熱により結晶性化されている。

本実施形態では、各半導体領域を形成した後ゲッタリング工程を行ったが、実施形態1のように、各半導体膜のゲッタリング工程を行った後、半導体膜を所望の形状にエッチングして、各半導体領域を形成しても良い。

次に、第3の半導体領域312、313及び第4の半導体領域311、314表面に酸化膜を形成した後、図10(B)に示すように、マスク321、322を形成する。マスク321は、後にnチャネル型TFTとなる第3の半導体領域313、第4の半導体領域311の全部を覆っている。一方、マスク322は、後にpチャネル型TFTとなる第3の半導体領域312の一部と第4の半導体領域314の一部を覆っている。このとき、マスク322は、後に形成されるpチャネル型TFTのチャネル長よりも狭いことが好ましい。

次に、第3の半導体領域312の露出部に、3族元素(13族元素、以下、アクセプター元素と示す。)を添加し、p型不純物領域324を形成する。このときマスク322に覆われる領域は、n型不純物領域325として残存する。n型を呈する第3の半導体領域312の2〜10倍の不純物濃度となるようにアクセプター型元素を添加することにより、p型不純物領域を形成することができる。

図17に、p型不純物領域の不純物元素のプロファイルを示す。

図17(A)は、CVD法により、n-領域濃度及びn+領域濃度を有する第2の半導体膜を形成した後、アクセプター型元素を添加したときの、各元素のプロファイルを示す。ドナー型元素のプロファイル150aは図16(A)と同様に、第1の濃度及び第2の濃度を示す。また、アクセプター型元素のプロファイル603は、第3の半導体領域表面付近では、濃度が高く、第4の半導体領域314に近づくにつれ、濃度が減少している。n+領域に含まれるドナー型元素の2〜10倍の濃度のアクセプター型元素を有する領域をp+領域602aと示し、n―領域のドナー型元素の2〜10倍の濃度のアクセプター型元素を有する領域をp―領域602bと示す。

図17(B)は、非晶質半導体、セミアモルファス半導体、微結晶半導体、及び結晶性半導体から選ばれたいずれかの状態を有する膜の半導体膜を形成し、イオンドープ法又はイオン注入法により該半導体膜にドナー型元素を添加して、n-領域濃度及びn+領域濃度を有する第2の半導体膜を形成した後、アクセプター型元素を添加したときの、各元素のプロファイルを示す。ドナー型元素のプロファイル150bは図16(A)のドナー型元素のプロファイル150aと同様である。また、アクセプター型元素のプロファイル613は、図17(A)のアクセプター型元素のプロファイル603と同様である。n+領域に含まれるドナー型元素の2〜10倍の濃度のアクセプター型元素を有する領域をp+領域602aと示し、n―領域のドナー型元素の2〜10倍の濃度のアクセプター型元素を有する領域をp―領域602bと示す。

なお、ドナー型元素が含まれる第2の半導体膜132は、希ガス元素、代表的にはアルゴンが添加されることにより、結晶格子の歪が形成され、後に行われるゲッタリング工程で、より触媒元素をゲッタリングすることが可能である。

つぎに、マスク321、322を除去した後、第3の半導体領域313及びp型不純物領域324、n型不純物領域325を加熱して、不純物元素を活性化する。加熱の方法としては、LRTA(Lamp Rapid Thermal Anneal)、GRTA、ファーネスアニール等を適宜用いることができる。ここでは、550度で1時間加熱する。

次に、図10(C)に示すように、実施形態1と同様に、第2の導電膜331、332を形成する。次に、マスク333を形成して、図10(D)に示すように、ソース領域及びドレイン領域として機能する第5の半導体領域343、344を形成する。次に、マスク333を除去した後第2の導電膜331、332及び第5の半導体領域343、344表面上に、パッシベーション膜を成膜することが好ましい。

以上の工程により、同一基板上にnチャネル型TFTとpチャネル型TFTとを形成することができる。本実施形態で形成されるTFTを用いることにより実施形態1と同様の効果を得ることができる。また、単チャネルTFTで形成される駆動回路と比較して、低電圧駆動が可能なCMOS回路を形成することが可能である。更には、ドナー型元素(例えば、リン)と比較してアクセプター型元素(例えば、ボロン)は原子半径が小さいため、比較的低い加速電圧及び濃度で、半導体膜中にアクセプター型元素を添加することが可能である。本実施形態では、アクセプター型元素のみ半導体膜に添加しているため、従来のCOMS回路の作製工程と比較して、短時間、かつ省エネルギーで作製することが可能であり、この結果低コスト化が可能である。

また、実施形態1乃至実施形態12のいずれにも、本実施形態を適用することが可能である。

(実施形態14)

本実施形態では、実施形態13と異なるゲッタリング工程により形成された結晶性半導体膜を有するnチャネル型TFT及びpチャネル型の作製工程について、図11を用いて説明する。

実施形態1に従って、基板101上に第1の導電膜301、302を形成する。次に、実施形態13に従って、図9(B)に示すような、触媒元素を有する層及び第1の半導体膜を形成した後、第1の半導体膜表面に数nmの絶縁膜を形成する。次に、第1のマスクを形成し、第1の半導体膜を所望の形状にエッチングして、図11(A)に示すような第1の半導体領域401、402、触媒元素を有する層125a、125bを形成する。

次に、図11(B)に示すように、第1の半導体領域401、402上に第2のマスク403、404を形成した後、第1の半導体領域の露出部にドナー型元素405を添加する。このとき、ドナー型元素が添加された領域をn型不純物領域406、407と示す。ここでは、イオンドーピング法によりリンを添加する。なお、第2のマスク403、404に覆われた第1の半導体領域には、リンは添加されないが触媒元素は含まれている。

次に、第2のマスク403、404を除去し、第1の半導体領域を加熱して結晶化すると共に、図11(C)の矢印で示すように、第1の半導体領域の結晶化を促した触媒元素を、n型不純物領域406、407に移動させて、触媒元素をゲッタリングする。ここでは、ゲッタリング後の触媒元素が移動した第1の半導体領域をソース領域及びドレイン領域413、414と示し、触媒元素濃度が低減された第1の半導体領域をチャネル形成領域411、412と示す。なお、チャネル形成領域411、412とソース領域及びドレイン領域413,414は、それぞれゲッタリング工程の加熱により結晶性化されており、また、ソース領域及びドレイン領域413,414中に含まれるドナー型元素は活性化されている。

次に、図11(D)に示すように、第3のマスク421、422を形成する。第3のマスク421は、後にnチャネル型TFTとなるチャネル形成領域411及びソース領域及びドレイン領域413の全部を覆っている。一方、第3のマスク422は、後にpチャネル型TFTとなるチャネル形成領域412の一部又は全部を覆っている。このとき、第3のマスク422は、後に形成されるpチャネル型TFTのチャネル長よりも狭いことが好ましい。

次に、ソース領域及びドレイン領域414、及びチャネル形成領域412の露出部に、アクセプター元素を添加し、p型不純物領域424を形成する。このとき、ソース領域及びドレイン領域414のドナー型元素濃度の2〜10倍の濃度となるようにアクセプター型元素を添加することにより、p型不純物領域を形成することができる。

つぎに、第3のマスク421、422を除去した後、ソース領域及びドレイン領域414、及びp型不純物領域424を加熱して、不純物元素を活性化する。加熱の方法としては、LRTA、GRTA、ファーネスアニール等を適宜用いることができる。ここでは、550度で1時間加熱する。

次に、図11(E)に示すように、実施形態13と同様に、第2の導電膜341、342を形成する。次に、第2の導電膜341、342及びチャネル形成領域411、412の表面上に、パッシベーション膜を成膜することが好ましい。

以上の工程により、同一基板上にnチャネル型TFTとpチャネル型TFTとを形成することができる。本実施形態で形成されるTFTを用いることにより実施形態1と同様の効果を得ることができる。更には、実施形態6と比較して、成膜工程が削減できるため、スループットを向上させることが可能である。

なお、実施形態1乃至実施形態14(ただし実施形態12は除く)のいずれかにも、本実施形態を適用することが可能である。

(実施形態15)

本実施形態においては、実施形態13を用いてゲッタリング工程を行った結晶性半導体膜を用いてnチャネルTFTとpチャネルTFTとを同一基板に形成する工程を図12を用いて形成する。

実施形態13の工程にしたがって、基板101上に第1の導電膜301、302を形成し、第1の導電膜上に第1の絶縁膜123を形成する。次に、触媒元素を有する層、第1の半導体膜と、希ガス元素を有する第2の半導体膜を形成する。次に、第1の半導体膜及び第2の半導体膜を実施形態1と同様の手法により加熱して結晶化すると共に、図12(A)の矢印で示すように、第1の半導体膜の結晶化を促す触媒元素を第2の半導体膜に移動させて、触媒元素をゲッタリングする。触媒元素がゲッタリングされた第1の半導体膜を第1の結晶性半導体膜501と示す。また、ゲッタリング後の触媒元素が移動した第2の半導体膜も同様に結晶化されているため、第2の結晶性半導体膜502と示す。

次に、図12(B)に示すように、第2の結晶性半導体膜502をエッチングした後、第1の結晶性半導体膜501表面に数nmの絶縁膜を成膜する。次に、第1のマスクを形成して第1の結晶性半導体膜をエッチングして第1の半導体領域511、512を形成する。次に、第2のマスク513、514を形成する。第2のマスク513は、後にnチャネル型TFTのチャネル形成領域となる部分を覆っている。一方、第2のマスク514は、後にpチャネル型TFTとなる第1の半導体領域512の全部を覆っている。次に、第1の半導体領域511の露出部にドナー型元素515を添加する。このとき、ドナー型元素515が添加された領域をn型不純物領域516と示す。また、第2のマスク513に覆われた領域はチャネル形成領域517として機能する。

次に、第2のマスク513、514を除去した後、図12(C)に示すように、新たに第3のマスク521、522を形成する。第3のマスク521は、後にnチャネル型TFTとなるチャネル形成領域517及びn型不純物領域516の全部を覆っている。一方、第3のマスク522は、後にpチャネル型TFTのチャネル形成領域となる領域を覆う。

次に、半導体領域512の露出部に、アクセプター型元素523を添加し、p型不純物領域524を形成する。また、第3のマスク522に覆われた領域はチャネル形成領域525として機能する。つぎに、第3のマスク521、522を除去した後、n型不純物領域516及びp型不純物領域524を加熱して、不純物元素を活性化する。加熱の方法としては、LRTA、GRTA、ファーネスアニール等を適宜用いることができる。

次に、図12(D)に示すように、実施形態1と同様に、第2の導電膜341、342を形成する。この後、チャネル形成領域517、525の一部をエッチングしてもよい。次に、第2の導電膜341、342及びチャネル形成領域517、525の表面上に、パッシベーション膜を成膜することが好ましい。

以上の工程により、同一基板上にnチャネル型TFTとpチャネル型TFTとを形成することができる。本実施形態で形成されるTFTを用いることにより実施形態1と同様の効果を得ることができる。

なお、実施形態1乃至実施形態13のいずれかにも、本実施形態を適用することが可能である。

(実施形態16)

本実施形態では実施形態14の変形例を用いて、nチャネルTFTとpチャネルTFTとを同一基板に形成する工程を、図13を用いて形成する。

実施形態14にしたがって、図13(A)に示すように、触媒元素及びドナー型元素を有する第3の半導体領域312、313及び第4の半導体領域311、314を形成する。次に、図13(B)に示すように、マスク321を形成した後、第3の半導体領域312にアクセプター型元素323を添加してp型不純物領域601を形成する。このとき、n型不純物領域である第3の半導体領域312の2〜10倍の濃度となるようにアクセプター型元素323を添加することにより、p型不純物領域を形成することができる。また、アクセプター型元素323としてボロンを用いた場合、分子半径が小さいため、第3の半導体領域より深いところまで添加される。このため、添加条件によっては、第4の半導体領域の上部にボロンが添加される。この後、第3の半導体領域313及びp型不純物領域601を加熱して、アクセプター型元素及びドナー型元素を活性化する。なお、ここでは、第4の半導体領域314にまでアクセプター元素を添加しないように、ドーピング条件を制御する。

次に、実施形態15にしたがって第2の導電膜331、332を形成する。次に、マスクを用いて、第2の導電膜331、332、第3の半導体領域313及びp型不純物領域601の露出部をエッチングして、図13(D)に示すようなソース領域及びドレイン領域として機能する第5の半導体領域343、621、及びチャネル形成領域として機能する第6の半導体領域345、622を形成することができる。この後、導電膜341、342及びチャネル形成領域345、622の表面上に、パッシベーション膜を成膜することが好ましい。

以上の工程により、同一基板上にnチャネル型TFTとpチャネル型TFTとを形成することができる。本実施形態で形成されるTFTを用いることにより実施形態1と同様の効果を得ることができる。更には、実施形態14と同様に、アクセプター型元素のみ半導体膜に添加しているため、従来のCMOS回路の作製工程と比較して、短時間で、かつ省エネルギー作製することが可能であり、この結果低コスト化が可能である

なお、実施形態1乃至実施形態12のいずれかにも、本実施形態を適用することが可能である。

(実施形態17)

本実施形態では、上記実施形態において、ゲート電極とソース電極及びドレイン電極との端部の位置関係、即ちゲート電極の幅とチャネル長の大きさの関係について、図14及び図15を用いて説明する。

図14(A)は、ゲート電極121a上をソース電極及びドレイン電極の端部がz1だけ重なっている。ここでは、ゲート電極121aと、ソース電極及びドレイン電極とが重なっている領域をオーバーラップ領域と呼ぶ。即ち、ゲート電極の幅y1がチャネル長x1よりも大きい。オーバーラップ領域の幅z1は、(y1−x1)/2で表される。このようなオーバーラップ領域を有するnチャネルTFTは、ソース電極及びドレイン電極と、半導体領域との間に、図9(B)で示すようなn+領域とn−領域とを有することが好ましい。この構造により、電界の緩和効果が大きくなり、ホットキャリア耐性を高めることが可能となる。

図14(B)は、ゲート電極121aの端部と、ソース電極及びドレイン電極の端部が一致している。即ち、ゲート電極の幅y2とチャネル長x2とが等しい。

図14(C)は、ゲート電極121aとソース電極及びドレイン電極の端部とがz3だけ離れている。ここでは、ゲート電極121aと、ソース電極及びドレイン電極とが離れている領域をオフセット領域と呼ぶ。即ち、ゲート電極の幅y3がチャネル長x3よりも小さい。オフセット領域の幅z3は、(x3−y3)/2で表される。このような構造のTFTは、オフ電流を低減することができるため、該TFTを表示装置のスイッチング素子として用いた場合、コントラストを向上させることができる。

図15(A)は、ゲート電極の幅y4が、チャネル長x4よりも大きい。また、ゲート電極121aの第1の端部とソース電極又はドレイン電極の一方の端部とが一致し、ゲート電極121aの第2の端部とソース電極又はドレイン電極の他方の端部とがz4だけ重なっている。オーバーラップ領域の幅z4は、(y4−x4)で表される。

図15(B)は、ゲート電極の幅y5が、チャネル長x5よりも小さい。また、ゲート電極121aの第1の端部とソース電極又はドレイン電極の一方の端部とが一致し、ゲート電極121aの第2の端部とソース電極又はドレイン電極の他方の端部とがz5だけ離れている。オフセット領域の幅z5は、(x5−y5)で表される。ゲート電極121aの第1の端部と端部が一致する電極をソース電極とし、オフセット領域を有する電極をドレイン電極とすることで、ドレイン電極付近での電界緩和が可能となる。

さらには、半導体領域が複数のゲート電極を覆ういわゆるマルチゲート構造のTFTとしても良い。この様な構造のTFTも、オフ電流を低減することができる。

なお、実施形態1乃至実施形態16のいずれかにも、本実施形態を適用することが可能である。

(実施形態18)

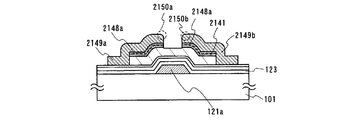

上記実施形態において、チャネル形成領域表面に対して垂直な端部を有するソース電極及びドレイン電極を示したが、この構造に限定されない。図18に示すように、チャネル形成領域表面に対して90度より大きく、180度未満、好ましくは135〜145度を有する端部であってもよい。また、ソース電極とチャネル形成領域表面との角度をθ1、ドレイン電極とチャネル形成領域表面との角度をθ2とすると、θ1とθ2が等しくてもよい。また、異なっていてもよい。このような形状のソース電極及びドレイン電極は、ドライエッチング法により形成することが可能である。

また、図19に示すように、ソース電極及びドレイン電極2149a、2149bの端部が湾曲面2150a、2150bを有していても良い。

なお、実施形態1乃至実施形態17のいずれかにも、本実施形態を適用することが可能である。