JP4727018B2 - アクティブマトリクス型表示装置 - Google Patents

アクティブマトリクス型表示装置 Download PDFInfo

- Publication number

- JP4727018B2 JP4727018B2 JP2000053470A JP2000053470A JP4727018B2 JP 4727018 B2 JP4727018 B2 JP 4727018B2 JP 2000053470 A JP2000053470 A JP 2000053470A JP 2000053470 A JP2000053470 A JP 2000053470A JP 4727018 B2 JP4727018 B2 JP 4727018B2

- Authority

- JP

- Japan

- Prior art keywords

- shielding film

- film

- pixel

- light

- source signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【発明の属する技術分野】

本願発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。特に本願発明は、画素マトリクス回路とその周辺に設けられる駆動回路を同一基板上に設けた液晶表示装置に代表される電気光学装置、および電気光学装置を搭載した電子機器に関する。尚、本願明細書において半導体装置とは、半導体特性を利用することで機能する装置全般を指し、上記電気光学装置およびその電気光学装置を搭載した電子機器も半導体装置に含む。

【0002】

【従来の技術】

最近、安価なガラス基板上に薄膜トランジスタ(TFT)を作製する技術が急速に発達してきている。その理由は、アクティブマトリクス型液晶表示装置の需要が高まったことにある。アクティブマトリクス型液晶表示装置は、マトリクス状に配置された数十〜数百万個もの各画素のそれぞれに薄膜トランジスタを配置し、各画素電極に出入りする電荷を薄膜トランジスタのスイッチング機能により制御するものである。

【0003】

各画素電極と対向電極との間には液晶が挟み込まれ、一種のコンデンサを形成している。従って、薄膜トランジスタによりこのコンデンサへの電荷の出入りを制御することで液晶の電気光学的特性を変化させ、液晶パネルを透過する光を制御して画像表示を行うことができる。また、このような構成でなるコンデンサは電流のリークにより次第にその保持電圧が減少するため、液晶の電気光学特性が変化して画像表示のコントラストが悪化するという問題を持つ。

【0004】

そこで、液晶で構成されるコンデンサと直列に保持容量と呼ばれる別のコンデンサを設置し、リーク等で損失した電荷を液晶で構成されるコンデンサに供給する構成が一般的となっている。

【0005】

保持容量の構造は様々であるが、遮蔽膜と画素電極との間に誘電体としての酸化膜を挟み込んだ構造が挙げられる。遮蔽膜とは、透過型液晶表示装置の画素マトリクス部において、薄膜トランジスタが光の照射によって導電性が変動するのを防止するための、遮光性を有する被膜である。

【発明が解決しようとする課題】

遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量は、遮蔽膜を一定の電位に保つために、基準電位が印加されたコモン線に接続されている。

【0006】

そこで工程上、遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線を接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にコンタクトホールをあける必要があった。コンタクトホールはマスクを用いたフォトリソグラフィーによって形成される。

【0007】

アクティブマトリクス型液晶表示装置は、その作製工程においてマスクを用いたフォトリソグラフィーを、遮蔽膜とコモン線の間に設けられた層間絶縁膜にコンタクトホールをあける工程の他に、例えば活性層の形成工程、ゲート絶縁膜の形成工程、画素電極の形成工程、ゲート線及びソース信号線の形成工程等で行っている。マスクを用いたフォトリソグラフィーは、アクティブマトリクス型液晶表示装置の作製工程数を増やす要因となっており、高い歩留まりを達成するためには、作製工程数を減らすことが望まれていた。

【0008】

【課題を解決するための手段】

アクティブマトリクス型液晶表示装置において、画素TFTに接続しているソース信号線に逆の極性の電圧を印加する駆動方法をソースライン反転という。このソースライン反転とは、液晶に常に1つの向きの電界が印加されることによって、液晶が劣化するのを防ぐために行われる。図4に示すように、ソース信号線1ラインごとに極性が逆の信号を印加し、1フレーム期間ごとに信号の極性を反転させることで、液晶に常に1つの向きの電界が印加されることによって液晶が劣化するのを防ぐ。1フレーム期間とは全ての画素が1つの画面を表示する期間を示す。

【0009】

このソースライン反転を用いた場合、遮蔽膜の電位の変動も平均化される。そのために、遮蔽膜を一定の電位(基準電位)に保たれたコモン線に接続しなくても、遮蔽膜の電位は時間的に平均を取るとほぼ一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量において、遮蔽膜をフローティングにすることが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線とを接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによってコンタクトホールをあける必要がなくなる。よってアクティブマトリクス型液晶表示装の作製工程を削減し、高い歩留まりを達成することが可能になり、またその作製コストを抑えることが可能になる。

【0010】

また上記構成に加えて、遮蔽膜とコモン線との間に大容量のカップリング容量を形成すると、遮蔽膜の電位の変動ΔVが小さくなる。ΔVは遮蔽膜とコモン線との間に形成されるカップリング容量の容量値Cと遮蔽膜にかかる電荷量Qによって、その値が決まる。しかし、電荷量Qは画素数、ソース信号線に入力される信号の電圧の値によって固定されてしまうので、実際には遮蔽膜の電位の変動ΔVの値はカップリング容量の容量値Cによって決定されてしまう。このCの値が大きければ大きいほどΔVは小さくなり、遮蔽膜の電位をより一定に保つことが可能になる。

【0011】

遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成した場合、上述した遮蔽膜をフローティングにするだけの構成と同じく、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによってコンタクトホールをあける必要がなくなる。カップリング容量の容量値は、ゲート信号線1ラインに画素TFTを介して接続されている全ての保持容量の容量値の合計の10倍以上であれば良い。よってアクティブマトリクス型液晶表示装置の作製工程を削減し、高い歩留まりを達成することが可能になり、またその作製コストを抑えることが可能になる。またそれに加えて、遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成した場合は、遮蔽膜の電位をさらに一定に保つことが可能になるため、良好なコントラストを得ることができる。

【0012】

以下に本願発明の構成を述べる。

【0013】

本願発明のある実施の形態によると、複数の画素TFTと、前記画素TFTに電気的に接続された画素電極と、遮蔽膜とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に誘電体を有することを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0014】

また本願発明のある実施の形態によると、複数のソース信号線と、複数のゲート信号線と、複数の画素TFTと、前記画素TFTに電気的に接続された画素電極と、遮蔽膜とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、

前記複数の画素TFTは前記ソース信号線と前記ゲート信号線に電気的に接続されており、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に誘電体が設けられており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0015】

また本願発明のある実施の形態によると、複数のソース信号線と、複数のゲート信号線と、複数の画素TFTと、画素電極と、遮蔽膜とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、ソース領域、ドレイン領域及びチャネル形成領域を有する活性層とを有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記ソース領域またはドレイン領域は前記ソース信号線に接続されており、

前記ドレイン領域またはソース領域は前記画素電極に接続されており、

前記画素電極と前記遮蔽膜の間に誘電体が設けられており、

前記遮蔽膜はフローティングになっており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0016】

また本願発明のある実施の形態によると、複数のソース信号線と、複数のゲート信号線と、複数の画素TFTと、画素電極と、遮蔽膜とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、活性層とを有し、

前記活性層はチャネル形成領域と、前記チャネル形成領域に接している第2の不純物領域と、前記第2の不純物領域に接している第1の不純物領域を有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記第1の不純物領域の一方は前記画素電極に接続されており、

前記第1の不純物領域のもう一方は前記ソース信号線に接続されており、

前記画素電極と前記遮蔽膜の間に誘電体が設けられており、

前記遮蔽膜はフローティングになっており、

前記第2の不純物領域は、前記ゲート絶縁膜を介して、前記ゲート電極と重なっており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0017】

また本願発明のある実施の形態によると、複数のソース信号線と、複数のゲート信号線と、複数の画素TFTと、画素電極と、遮蔽膜とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、活性層とを有し、

前記活性層はチャネル形成領域と、前記チャネル形成領域に接している第2の不純物領域と、前記チャネル形成領域を挟んで設けられた第1の不純物領域とを有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記第1の不純物領域の一方は前記画素電極に接続されており、

前記第1の不純物領域のもう一方は前記ソース信号線に接続されており、

前記画素電極と前記遮蔽膜の間に誘電体が設けられており、

前記遮蔽膜はフローティングになっており、

前記第2の不純物領域は、前記ゲート絶縁膜を介して、前記ゲート電極と重なっており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0018】

前記誘電体は、前記遮蔽膜を陽極酸化して形成される陽極酸化膜であっても良い。

【0019】

前記遮蔽膜は、アルミニウム(Al)、チタン(Ti)またはタンタル(Ta)を有する膜であっても良い。

【0020】

前記遮蔽膜は100〜300nmの厚さであっても良い。

【0021】

前記ゲート電極は、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、から選ばれた一種または複数種の元素を有していても良い。

【0022】

前記アクティブマトリクス型液晶表示装置を3つ備えたリアプロジェクターであっても良い。

【0023】

前記アクティブマトリクス型液晶表示装置を3つ備えたフロントプロジェクターであっても良い。

【0024】

前記アクティブマトリクス型液晶表示装置を1つ備えた単板式リアプロジェクターであっても良い。

【0025】

前記アクティブマトリクス型液晶表示装置を2備えたゴーグル型ディスプレイであっても良い。

【0026】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、遮蔽膜と、一定の基準電位に保たれたコモン線とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重ならないことを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0027】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、複数のソース信号線と、複数のゲート信号線と、遮蔽膜と、一定の基準電位に保たれたコモン線とが設けられた基板を有するアクティブマトリクス型液晶表示装置であって、

前記複数の画素TFTは前記ソース信号線と前記ゲート信号線に電気的に接続されており、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重なっておらず、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0028】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、複数のソース信号線と、複数のゲート信号線と、遮蔽膜と、一定の基準電位に保たれたコモン線とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、ソース領域、ドレイン領域及びチャネル形成領域を有する活性層とを有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記ソース領域またはドレイン領域は前記ソース信号線に接続されており、

前記ドレイン領域またはソース領域は前記画素電極に接続されており、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重なっておらず、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0029】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、複数のソース信号線と、複数のゲート信号線と、遮蔽膜と、一定の基準電位に保たれたコモン線とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、活性層とを有し、

前記活性層はチャネル形成領域と、前記チャネル形成領域に接している第2の不純物領域と、前記第2の不純物領域に接している第1の不純物領域を有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記第1の不純物領域の一方は前記画素電極に接続されており、

前記第1の不純物領域のもう一方は前記ソース信号線に接続されており、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重なっておらず、

前記第2の不純物領域は、前記ゲート絶縁膜を介して、前記ゲート電極と重なっており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0030】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、複数のソース信号線と、複数のゲート信号線と、遮蔽膜と、一定の基準電位に保たれたコモン線とが設けられた第1の基板と、

対向電極が設けられた第2の基板と、

前記画素電極と前記対向電極との間に挟まれた液晶と、

を有するアクティブマトリクス型液晶表示装置において、

前記各画素TFTは、ゲート電極と、ゲート絶縁膜と、活性層とを有し、

前記活性層はチャネル形成領域と、前記チャネル形成領域に接している第2の不純物領域と、前記チャネル形成領域を挟んで設けられた第1の不純物領域とを有し、

前記ゲート電極は前記ゲート信号線に接続されており、

前記第1の不純物領域の一方は前記画素電極に接続されており、

前記第1の不純物領域のもう一方は前記ソース信号線に接続されており、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重なっておらず、

前記第2の不純物領域は、前記ゲート絶縁膜を介して、前記ゲート電極と重なっており、

前記複数のソース信号線1本ごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0031】

また本願発明のある実施の形態によると、複数の画素TFT及び前記複数の画素TFTに電気的に接続された画素電極を有する画素マトリクス部と、遮蔽膜と、一定の基準電位に保たれたコモン線と、ソース信号線駆動回路とが設けられた第1の基板と、

対向遮蔽膜が設けられた第2の基板と、

を有するアクティブマトリクス型液晶表示装置において、

前記遮蔽膜はフローティングになっており、

前記画素電極と前記遮蔽膜との間に第1の誘電体を有し、

前記遮蔽膜と前記コモン線との間に第2の誘電体を有し、

前記第2の誘電体は前記画素マトリクス部と重なっておらず、

前記ソース信号線駆動回路はサンプリング回路を有しており、

前記対向遮蔽膜は、前記遮蔽膜の一部及び前記サンプリング回路と重なっていることを特徴とするアクティブマトリクス型液晶表示装置が提供される。このことによって上記目的が達成される。

【0032】

前記第1の誘電体は、前記遮蔽膜を陽極酸化して形成される陽極酸化膜であっても良い。

【0033】

前記第2の誘電体は、前記遮蔽膜を陽極酸化して形成される陽極酸化膜であっても良い。

【0034】

前記遮蔽膜は、アルミニウム(Al)、チタン(Ti)またはタンタル(Ta)を有する膜であっても良い。

【0035】

前記遮蔽膜は100〜300nmの厚さであっても良い。

【0036】

前記ゲート電極は、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、から選ばれた一種または複数種の元素を有していても良い。

【0037】

前記アクティブマトリクス型液晶表示装置を3つ備えたリアプロジェクターであっても良い。

【0038】

前記アクティブマトリクス型液晶表示装置を3つ備えたフロントプロジェクターであっても良い。

【0039】

前記アクティブマトリクス型液晶表示装置を1つ備えた単板式リアプロジェクターであっても良い。

【0040】

前記アクティブマトリクス型液晶表示装置を2つ備えたゴーグル型ディスプレイであっても良い。

【0041】

なお、本願発明の遮蔽膜は寄生容量の影響を避けるため、ソース信号線駆動回路上に設けないことが好ましい。

【0042】

【発明の実施の形態】

以下に本願発明を、実施例をもって説明する。ただし、本願発明は、以下の実施例に限定されるわけではない。

【0043】

【実施例】

図1〜図31を用いて、本願発明の実施例を説明する。

【0044】

(実施例1)

本実施例では、本願発明を用いたアクティブマトリクス型液晶表示装置の一例について、図1を用いて説明する。

【0045】

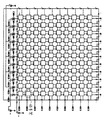

図1に本願発明の保持容量を用いたアクティブマトリクス型液晶表示装置の回路図の一例を示す。ソース信号線駆動回路11、ゲート信号線駆動回路12、アクティブマトリクス回路13、画素TFT14、画素電極と対向電極との間に液晶を挟んだ液晶セル15、画素電極と遮蔽膜の間に誘電体を挟んで形成される保持容量16、ソース信号線17、ゲート信号線18が図1に示されるように設けられている。ソース信号線駆動回路11とゲート信号線駆動回路12は、一般に駆動回路と総称されている。この駆動回路は、アクティブマトリクス回路でなる画素マトリクス部と同一基板上に一体形成されている。

【0046】

また、アクティブマトリクス部13では、ソース信号線駆動回路11に接続されたソース信号線17と、ゲート信号線駆動回路12に接続されたゲート信号線18が交差している。そのソース信号線17とゲート信号線18に囲まれた領域、画素部19に、画素の薄膜トランジスタ(画素TFT)14と、対向電極と画素電極の間に液晶を挟んだ液晶セル15と、保持容量16が設けられている。

【0047】

保持容量16は画素電極と遮蔽膜の間に誘電体としての酸化膜を挟んだ構成となっており、全ての遮蔽膜はコモン線とは接続されていないフローティング(Floating)の状態となっている。

【0048】

ソース信号線17に入力された画像信号は、画素TFT14により選択され、所定の画素電極に書き込まれる。

【0049】

ソース信号線駆動回路11から出力されたタイミング信号によりサンプリングされた画像信号が、ソース信号線17に供給される。

【0050】

画素TFT14は、ゲート信号線駆動回路12からゲート信号線18を介して入力される選択信号により動作する。

【0051】

ソース信号線17に入力される画像信号は、ソース信号線17の1ラインごとに極性を逆にして印加し、1フレーム期間ごとに信号の極性を反転させることで、液晶に常に1つの向きの電界が印加されることによって液晶が劣化するのを防ぐ。このようにソースライン反転で液晶を駆動させて、遮蔽膜をコモン線に接続せずにフローティングとしている。このような構成にすることで、遮蔽膜をコモン線に接続しなくても、遮蔽膜の電位が時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量を形成することが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線を接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装の作製コストを抑えることが可能になる。

【0052】

次に、図1における画素部19の詳しい構造について、図2を用いて説明する。

【0053】

まず、図2において、21は活性層、22はゲート信号線、23はソース信号線、24は活性層とソース信号線とのコンタクト部、25はドレイン配線(ドレイン電極)、26は活性層とドレイン配線とのコンタクト部である。

【0054】

次に、図3は、図2(A)に遮蔽膜27と画素電極28を重ね合わせた状態を示している。なお、画素電極28は一部点線で表しているが、これは下層の遮蔽膜との位置関係を明瞭にするためである。

【0055】

図3に示すように、画素電極28は画像表示領域29の外周部分で遮蔽膜27と重なるように形成されている。この画素電極28と遮蔽膜27とが重なる領域30が保持容量17として機能することになる。

【0056】

また、31はドレイン配線25と画素電極28とのコンタクト部である。コンタクト部31には遮蔽膜27を設けることができないが、ドレイン配線25で完全に遮光されるので、TFTに光が当たるようなことはない。

【0057】

次に図1で示したソース信号線駆動回路の一例について説明する。図5に図1で示したソース信号線駆動回路11のブロック図を示す。CLKはクロック信号、CLKBは反転したクロック信号、SPはスタートパルス信号、SL/Rは駆動方向切り替え信号を示している。

【0058】

図5の具体的な回路構成の一例を図6に示す。シフトレジスタ回路101、レベルシフト回路102、サンプリング回路103、画像信号線104が図に示すように配置されている。

【0059】

クロック信号(CLK)、反転したクロック信号(CLKb)、スタートパルス信号(SP)および駆動方向切り替え信号(SL/R)は図5に示されている配線からシフトレジスタ回路に入力される。

【0060】

ソース信号線駆動回路の外部から入力されたクロック信号(CLK)(例えば10V)がシフトレジスタ回路101に入力される。そして、入力されたクロック信号および同じ時にシフトレジスタ回路101に入力したスタートパルス信号とによってシフトレジスタ回路101が動作し、画像のサンプリングのためのタイミング信号を順に生成する。

【0061】

生成されたタイミング信号はレベルシフト回路(LS)102に入力され電圧振幅レベルが上げられる。ここで本明細書において電圧振幅レベルとは信号の最も高い電位と最も低い電位の差(電位差)の絶対値を意味しており、電圧振幅レベルが高くなる(上げられる)とは電位差が大きくなることを意味し、電圧振幅レベルが低くなるとは電位差が小さくなることを意味する。電圧振幅レベルが上げられたタイミング信号はアナログスイッチ105を有するサンプリング回路103に入力され、入力されたタイミング信号に基づいてサンプリング回路103が画像信号をサンプリングする動作をする。サンプリングされた画像信号はソース信号線(S1〜Sn)を介して画素マトリクス部に入力される。

【0062】

サンプリングされる画像信号は画像信号線ごとに逆の極性で印加されている。

これによってソース信号線1ラインごとに逆の極性の画像信号がサンプリングされ液晶に印加される。言い換えるとソースライン反転で液晶が駆動することとなる。そのため遮蔽膜を一定の電位(基準電位)に保たれたコモン線に接続しなくても、遮蔽膜の電位は時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量において、遮蔽膜をフローティングにすることが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線とを接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装の作製コストを抑えることが可能になる。

【0063】

図7にアナログスイッチ105とレベルシフト回路102の具体的な回路図を示す。

【0064】

図7(A)にアナログスイッチの等価回路図を示す。画像信号が入力される信号(IN、INb)によってサンプリングされる。図7(B)にレベルシフト回路の等価回路図を示す。INは信号が入力されることを意味し、INbはINの反転信号が入力されることを意味する。また、Vddhはプラスの電圧、Vssはマイナスの電圧の印加を示している。レベルシフト回路は、INに入力された信号を高電圧化し反転させた信号が、OUTbから出力されるように設計されている。つまり、INにHiが入力されるとOUTbからVss相当の信号が、Loが入力されるとOUTbからVddh相当の信号が出力される。

【0065】

次に本願発明の画素マトリクス回路とその周辺に設けられる駆動回路のTFTを同時に作製する方法の一例について、図8〜図10を用いて説明する。なお、本願発明はこの作製方法に限られない。

【0066】

〔島状半導体層、ゲート絶縁膜形成の工程:図8(A)〕

図8(A)において、基板6001には、無アルカリガラス基板や石英基板を使用することが望ましい。その他にもシリコン基板や金属基板の表面に絶縁膜を形成したものを基板としても良い。

【0067】

そして、基板6001のTFTが形成される表面には、酸化シリコン膜、窒化シリコン膜、または窒化酸化シリコン膜からなる下地膜6002をプラズマCVD法やスパッタ法で100〜400nmの厚さに形成した。例えば下地膜6002として、窒化シリコン膜6002を25〜100nm、ここでは50nmの厚さに、酸化シリコン膜6003を50〜300nm、ここでは150nmの厚さとした2層構造で形成すると良い。下地膜6002は基板からの不純物汚染を防ぐために設けられるものであり、石英基板を用いた場合には必ずしも設けなくても良い。

【0068】

次に下地膜6002の上に20〜100nmの厚さの、非晶質シリコン膜を公知の成膜法で形成した。非晶質シリコン膜は含有水素量にもよるが、好ましくは400〜550℃で数時間加熱して脱水素処理を行い、含有水素量を5atom%以下として、結晶化の工程を行うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製方法で形成しても良いが、膜中に含まれる酸素、窒素などの不純物元素を十分低減させておくことが望ましい。ここでは、下地膜と非晶質シリコン膜とは、同じ成膜法で形成することが可能であるので両者を連続形成しても良い。下地膜を形成後、一旦大気雰囲気にさらされないようにすることで表面の汚染を防ぐことが可能となり、作製されるTFTの特性バラツキを低減させることができる。

【0069】

非晶質シリコン膜から結晶質シリコン膜を形成する工程は、公知のレーザー結晶化技術または熱結晶化の技術を用いれば良い。また、シリコンの結晶化を助長する触媒元素を用いて熱結晶化の方法で結晶質シリコン膜を作製しても良い。その他に、微結晶シリコン膜を用いても良いし、結晶質シリコン膜を直接堆積成膜しても良い。さらに、単結晶シリコンを基板上に貼りあわせるSOI(Silicon On Insulators)の公知技術を使用して結晶質シリコン膜を形成しても良い。

【0070】

こうして形成された結晶質シリコン膜の不要な部分をエッチング除去して、島状半導体層6004〜6006を形成した。結晶質シリコン膜のnチャネル型TFTが作製される領域には、しきい値電圧を制御するため、あらかじめ1×1015〜5×1017cm-3程度の濃度でボロン(B)を添加しておいても良い。

【0071】

次に、島状半導体層6004〜6006を覆って、酸化シリコンまたは窒化シリコンを主成分とするゲート絶縁膜6007を形成した。ゲート絶縁膜6007は、10〜200nm、好ましくは50〜150nmの厚さに形成すれば良い。

例えば、プラズマCVD法でN2OとSiH4を原料とした窒化酸化シリコン膜を75nm形成し、その後、酸素雰囲気中または酸素と塩酸の混合雰囲気中、800〜1000℃で熱酸化して115nmのゲート絶縁膜としても良い。(図8(A))

【0072】

〔n-領域の形成:図8(B)〕

島状半導体層6004、6006及び配線を形成する領域の全面と、島状半導体層6005の一部(チャネル形成領域となる領域を含む)にレジストマスク6008〜6011を形成し、n型を付与する不純物元素を添加して低濃度不純物領域6012、6013を形成した。この低濃度不純物領域6012、6013は、後にCMOS回路のnチャネル型TFTに、ゲート絶縁膜を介してゲート電極と重なるLDD領域(本明細書中ではLov領域という。なお、ovとはoverlapの意味である。)を形成するための不純物領域である。なお、ここで形成された低濃度不純物領域に含まれるn型を付与する不純物元素の濃度を(n-)で表すこととする。従って、本明細書中では低濃度不純物領域6012、6013をn-領域と言い換えることができる。

【0073】

ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法でリンを添加した。勿論、質量分離を行うイオンインプランテーション法を用いても良い。この工程では、ゲート絶縁膜6007を通してその下の半導体層にリンを添加した。添加するリン濃度は、5×1017〜5×1018atoms/cm3の範囲にするのが好ましく、ここでは1×1018atoms/cm3とした。

【0074】

その後、レジストマスク6008〜6011を除去し、窒素雰囲気中で400〜900℃、好ましくは550〜800℃で1〜12時間の熱処理を行い、この工程で添加されたリンを活性化する工程を行った。

【0075】

〔ゲート電極用および配線用導電膜の形成:図8(C)〕

第1の導電膜6014を、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素またはいずれかを主成分とする導電性材料で、10〜100nmの厚さに形成した。第1の導電膜6014としては、例えば窒化タンタル(TaN)や窒化タングステン(WN)を用いることが望ましい。さらに、第1の導電膜6014上に第2の導電膜6015をTa、Ti、Mo、Wから選ばれた元素またはいずれかを主成分とする導電性材料で、100〜400nmの厚さに形成した。例えば、Taを200nmの厚さに形成すれば良い。また、図示しないが、第1の導電膜6014の下に導電膜6014、6015(特に導電膜6015)の酸化防止のためにシリコン膜を2〜20nm程度の厚さで形成しておくことは有効である。

【0076】

〔p−chゲート電極、配線電極の形成とp++領域の形成:図9(A)〕

レジストマスク6016〜6019を形成し、第1の導電膜と第2の導電膜(以下、積層膜として取り扱う)をエッチングして、pチャネル型TFTのゲート電極6020、ゲート信号線6021、6022を形成した。なお、nチャネル型TFTとなる領域の上には全面を覆うように導電膜6023、6024を残した。

【0077】

そして、レジストマスク6016〜6019をそのまま残してマスクとし、pチャネル型TFTが形成される半導体層6004の一部に、p型を付与する不純物元素を添加する工程を行った。ここではボロンをその不純物元素として、ジボラン(B2H6)を用いてイオンドープ法(勿論、イオンインプランテーション法でも良い)で添加した。ここでは5×1020〜3×1021atoms/cm3の濃度にボロンを添加した。なお、ここで形成された不純物領域に含まれるp型を付与する不純物元素の濃度を(p++)で表すこととする。従って、本明細書中では不純物領域6025、6026をp++領域と言い換えることができる。

【0078】

なお、この工程において、レジストマスク6016〜6019を使用してゲート絶縁膜6007をエッチング除去して、島状半導体層6004の一部を露出させた後、p型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0079】

〔n―chゲート電極の形成:図9(B)〕

次に、レジストマスク6016〜6019を除去した後、レジストマスク6027〜6030を形成し、nチャネル型TFTのゲート電極6031、6032を形成した。このときゲート電極6031はn-領域6012、6013とゲート絶縁膜を介して重なるように形成した。

【0080】

〔n+領域の形成:図9(C)〕

次に、レジストマスク6027〜6030を除去し、レジストマスク6033〜6035を形成した。そして、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域を形成する工程を行った。レジストマスク6035はnチャネル型TFTのゲート電極6032を覆う形で形成した。これは、後の工程において画素マトリクス回路のnチャネル型TFTに、ゲート電極と重ならないようにLDD領域を形成するためである。

【0081】

そして、n型を付与する不純物元素を添加して不純物領域6036〜6040を形成した。ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm3とした。なお、ここで形成された不純物領域6038〜6040に含まれるn型を付与する不純物元素の濃度を(n+)で表すこととする。従って、本明細書中では不純物領域6038〜6040をn+領域と言い換えることができる。また、不純物領域6036、6037は既にn-領域が形成されていたので、厳密には不純物領域6038〜6040よりも若干高い濃度でリンを含む。

【0082】

なお、この工程において、レジストマスク6033〜6035およびゲート電極6031をマスクとしてゲート絶縁膜6007をエッチングし、島状半導体膜6005、6006の一部を露出させた後、n型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0083】

〔n--領域の形成:図10(A)〕

次に、レジストマスク6033〜6035を除去し、画素マトリクス回路のnチャネル型TFTとなる島状半導体層6006にn型を付与する不純物元素を添加する工程を行った。こうして形成された不純物領域6041〜6044には前記n-領域と同程度かそれより少ない濃度(具体的には5×1016〜1×1018atoms/cm3)のリンが添加されるようにした。なお、ここで形成された不純物領域6041〜6044に含まれるn型を付与する不純物元素の濃度を(n--)で表すこととする。従って、本明細書中では不純物領域6041〜6044をn--領域と言い換えることができる。また、この工程ではゲート電極で隠された不純物領域6068、6069を除いて全ての不純物領域にn?の濃度でリンが添加されているが、非常に低濃度であるため無視して差し支えない。

【0084】

〔熱活性化の工程:図10(B)〕

次に、後に第1の層間絶縁膜の一部となる保護絶縁膜6045を形成した。保護絶縁膜6045は窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は100〜400nmとすれば良い。

【0085】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネスアニール法で活性化工程を行った。加熱処理は、窒素雰囲気中において300〜650℃、好ましくは400〜550℃、ここでは450℃、2時間の熱処理を行った。

【0086】

さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0087】

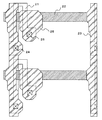

〔層間絶縁膜、ソース/ドレイン電極、遮蔽膜、画素電極、保持容量の形成:図10(C)〕

活性化工程を終えたら、保護絶縁膜6045の上に0.5〜1.5μm厚の層間絶縁膜6046を形成した。前記保護絶縁膜6045と層間絶縁膜6046とでなる積層膜を第1の層間絶縁膜とした。

【0088】

その後、それぞれのTFTのソース領域またはドレイン領域に達するコンタクトホールが形成され、ソース電極6047〜6049と、ドレイン電極6050、6051を形成した。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。これで図2に示した状態と同じになる。図2で示す活性層21は図10の活性層6004〜6006に相当し、ゲート信号線22およびドレイン配線25は同じドレイン電極6050、6051として表されている。ソース信号線23はソース電極6047〜6049として示されている。

【0089】

次に、パッシベーション膜6052として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50〜500nm(代表的には200〜300nm)の厚さで形成した。その後、この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。なお、ここで後に画素電極とドレイン電極を接続するためのコンタクトホールを形成する位置において、パッシベーション膜6052に開口部を形成しておいても良い。

【0090】

その後、有機樹脂からなる第2の層間絶縁膜6053を約1μmの厚さに形成した。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成した。

【0091】

次に、画素マトリクス回路となる領域において、第2の層間絶縁膜6053上に遮蔽膜6054を形成した。遮蔽膜6054はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ばれた元素またはいずれかを主成分とする膜で100〜300nmの厚さに形成した。そして、遮蔽膜6054の表面に陽極酸化法またはプラズマ酸化法により30〜150nm(好ましくは50〜75nm)の厚さの酸化膜6055を形成した。ここでは遮蔽膜6054としてアルミニウム膜またはアルミニウムを主成分とする膜を用い、誘電体6055として酸化アルミニウム膜(アルミナ膜)を用いた。

【0092】

なお、ここでは遮蔽膜の表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCVD法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜厚は30〜150nm(好ましくは50〜75nm)とすることが好ましい。また、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond like carbon)膜または有機樹脂膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良い。

【0093】

次に、パッシベーション膜6052及び第2の層間絶縁膜6053にドレイン電極6051に達するコンタクトホールを形成し、画素電極6056を形成した。なお、画素電極6057、6058はそれぞれ隣接する別の画素の画素電極である。画素電極6056〜6058は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成した。

【0094】

また、この時、画素電極6056と遮蔽膜6054とが酸化膜6055を介して重なった領域6059が保持容量を形成した。

【0095】

こうして同一基板上に、駆動回路となるCMOS回路と画素マトリクス回路とを有したアクティブマトリクス基板が完成した。なお、駆動回路となるCMOS回路にはpチャネル型TFT6081、nチャネル型TFT6082が形成され、画素マトリクス回路にはnチャネル型TFTでなる画素TFT6083が形成された。

【0096】

CMOS回路のpチャネル型TFT6081には、チャネル形成領域6062、ソース領域6063、ドレイン領域6064がそれぞれp+領域で形成された。また、nチャネル型TFT6082には、チャネル形成領域6065、ソース領域6066、ドレイン領域6067、ゲート絶縁膜を介してゲート電極と重なったLDD領域(以下、Lov領域という。なお、ovとはoverlapの意である。)6068、6069が形成された。この時、ソース領域6066、ドレイン領域6067はそれぞれ(n-+n+)領域で形成され、Lov領域6068、6069はn-領域で形成された。

【0097】

また、画素TFT6083には、チャネル形成領域6070、6071、ソース領域6072、ドレイン領域6073、ゲート絶縁膜を介してゲート電極と重ならないLDD領域(以下、Loff領域という。なお、offとはoffsetの意である。)6074〜6077、Loff領域6075、6076に接したn+領域6078が形成された。この時、ソース領域6072、ドレイン領域6073はそれぞれn+領域で形成され、Loff領域6074〜6077はn--領域で形成された。

【0098】

チャネル長3〜7μmに対してLov領域の長さ(幅)は0.5〜3.0μm、代表的には1.0〜1.5μmとすれば良い。また、画素TFT6083に設けられるLoff領域6074〜6077の長さ(幅)は0.5〜3.5μm、代表的には2.0〜2.5μmとすれば良い。

【0099】

図27に、コモン線と、FPCからの引き出し端子との接合部分を示す。基板6001、図10(C)に示したnチャネル型TFTを有するゲート信号線駆動回路2702、コモン線2703、遮蔽膜2704、誘電体2705、ITO膜2706、フィラー2707、樹脂2708、FPCからの引き出し端子上に成膜されたITO膜2709、FPCからの引き出し端子2710が図27に示すように設けられている。

【0100】

遮蔽膜2704とITO膜2706と、その間に挟まれた誘電体2705とによって、カップリング容量が形成されている。ITO膜2706は、ゲート信号線駆動回路2702上に設けられており、ゲート信号線駆動回路2702の下に設けられたコモン線2703と接続している。FPCからの引き出し端子2710上にはFPC側のITO膜2709が形成されており、FPCからの引き出し端子2710上のFPC側のITO膜2709とITO膜2706とは、フィラー2707と樹脂2708とによって接続されている。

【0101】

樹脂2708は光硬化性の樹脂であっても、熱硬化性の樹脂であっても良く、また光硬化性の樹脂と熱硬化性の樹脂との混合物であっても良い。光硬化性の樹脂と熱硬化性の樹脂との混合物を用いた場合、光によって仮接着の後、熱を加えて圧着させることにより接続する。またフィラーは導電性の材料であることが必要である。大きさの異なるフィラーを2種類以上用いても良く、この場合、サイズの小さいフィラーはスペーサとして働くので導電性でなくても良く、サイズの大きい粒子は電気的に接続させる働きをするので導電性であることが必要である。

【0102】

本願発明では、ソースライン反転によって液晶を駆動してやり、かつ遮蔽膜を一定の電位(基準電位)に保たれたコモン線に接続しない。ソースライン反転によって、遮蔽膜の電位は時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量において、遮蔽膜をフローティングにすることが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線とを接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装の作製コストを抑えることが可能になる。

【0103】

(実施例2)

本実施例では、実施例1の遮蔽膜をフローティングにするという構成に加えて、遮蔽膜とコモン線との間に大容量のカップリング容量を形成する例について説明する。なおTFTの作製方法の記載は省略するが、実施例1と同じプロセスを用いても良い。

【0104】

図11に本願発明の保持容量を用いたアクティブマトリクス型液晶表示装置の回路図の一例を示す。ソース信号線駆動回路301、ゲート信号線駆動回路302、アクティブマトリクス回路303、画素TFT304、画素電極と対向電極との間に液晶を挟んだ液晶セル305、画素電極と遮蔽膜の間に誘電体を挟んで形成される保持容量306、ソース信号線307、ゲート信号線308が図11に示されるように設けられている。またカップリング容量310がフローティングになっている遮蔽膜とコモン線との間に設けられている。ソース信号線駆動回路301とゲート信号線駆動回路302は、一般に駆動回路と総称されている。この駆動回路は、アクティブマトリクス回路でなる画素マトリクス部と同一基板上に一体形成されている。

【0105】

また、アクティブマトリクス部303では、ソース信号線駆動回路301に接続されたソース信号線307と、ゲート信号線駆動回路302に接続されたゲート信号線308が交差している。そのソース信号線307とゲート信号線308に囲まれた領域、画素部309に、画素の薄膜トランジスタ(画素TFT)304と、対向電極と画素電極の間に液晶を挟んだ液晶セル305と、保持容量306が設けられている。またコモン線311と遮蔽膜312とが図に示すように設けられている。

【0106】

保持容量306は画素電極と遮蔽膜312の間に誘電体としての酸化膜を挟んだ構成となっており、全ての遮蔽膜312はコモン線311とは接続されていないフローティング(Floating)となっている。

【0107】

またカップリング容量310の容量値は、ゲート信号線1ラインに画素TFTを介して接続されている全ての保持容量の容量値の合計の10倍以上であれば良い。

【0108】

ソース信号線307に入力された画像信号は、画素TFT304により選択され、所定の画素電極に書き込まれる。

【0109】

ソース信号線駆動回路301から出力されたタイミング信号によりサンプリングされた画像信号が、ソース信号線307に供給される。

【0110】

画素TFT304は、ゲート信号線駆動回路302からゲート信号線308を介して入力される選択信号により動作する。

【0111】

ソース信号線に入力される画像信号は、ソース信号線1ラインごとに極性を逆にして印加し、1フレーム期間ごとに信号の極性を反転させることで、液晶に常に1つの向きの電界が印加されることによって液晶が劣化するのを防ぐ。このようにソースライン反転で液晶を駆動させて、遮蔽膜をコモン線に接続せずにフローティングとしている。このような構成にすることで、遮蔽膜をコモン線に接続しなくても、遮蔽膜の電位が時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量を形成することが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線を接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装置の作製コストを抑えることが可能になる。またそれに加えて、遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成した場合は、遮蔽膜の電位の変動ΔVが小さくなる。カップリング容量の容量値が大きければ大きいほどΔVは小さくなり、遮蔽膜の電位をより一定に保つことが可能になるため、良好なコントラストを得ることができる。

【0112】

図23に図11の上面及び断面の概略図を示す。図23(B)は図23(A)のA−A’における断面図である。

【0113】

ソース信号線駆動回路411(図11に示すところの301)、ゲート信号線駆動回路402、アクティブマトリクス部413(図11に示すところの303)、遮蔽膜404、ITO膜406、コモン線407、FPC414が図23(A)に示すように設けられている。

【0114】

ITO膜406とコモン線407は電気的に接続されており、コモン線407はFPC414によって基板の外部に接続され、一定の電位(基準電位)に保たれている。

【0115】

コモン線407に接続されたITO膜406と遮蔽膜404の重なった部分にカップリング容量416(図11で示すところの310)が形成されている。

【0116】

基板401、ゲート信号線駆動回路402(図11に示すところの302)、層間絶縁膜403、遮蔽膜404(図11に示すところの311)、誘電体405、ITO膜406、コモン線407(図11に示すところの312)、フィラー412、樹脂410、FPCからの引き出し端子上に成膜されたITO膜409、FPCからの引き出し端子408が図23に示すように設けられている。

【0117】

遮蔽膜404とITO膜406と、その間に挟まれた誘電体405とによって、カップリング容量が形成されている。ITO膜406は、ゲート信号線駆動回路402上に設けられており、ゲート信号線駆動回路402の下に設けられたコモン線407と接続している。FPCからの引き出し端子408上にはFPC側のITO膜409が接するように形成されており、FPCからの引き出し端子408上のFPC側のITO膜409とITO膜406とは、フィラー412と樹脂410とによって接続されている。

【0118】

樹脂410は光硬化性の樹脂であっても、熱硬化性の樹脂であっても良く、また光硬化性の樹脂と熱硬化性の樹脂との混合物であっても良い。光硬化性の樹脂と熱硬化性の樹脂との混合物を用いた場合、光によって仮接着の後、熱を加えて圧着させることにより接続する。またフィラーは導電性の材料であることが必要である。大きさの異なるフィラーを2種類以上用いても良く、この場合、サイズの小さいフィラーはスペーサとして働くので導電性でなくても良く、サイズの大きい粒子は電気的に接続させる働きをするので導電性であることが必要である。

【0119】

ITO膜406とコモン線407は電気的に接続されている。コモン線407に接続されているITO膜406と、遮蔽膜404と、その間に設けられた誘電体405によって、図11に示すところのカップリング容量310が形成されている。

【0120】

遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成した場合の画素電位のシミュレーションの結果を図12、図25及び図26を用いて説明する。

【0121】

図12(A)は、遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成したアクティブマトリクス型液晶表示装置にソース線1本おきに白黒の縦縞を表示させたときの、画素電極の電極波形のシミュレーションの結果である。画素数は10×10とし、ゲート信号線側駆動回路上全てに300nFの容量値のカップリング容量を形成したと仮定した。図12(A)は、画面の中央もしくはその隣の画素電極の電極波形の図である。0ms〜16msが1番目の画面を表示したときの画素電位で、16ms〜32msが2番目の画面を表示したときの画素電位である。画素電位は8Vを基準として±5Vの信号を画素電極に印加している。

【0122】

図25は図12のアクティブマトリクス基板のシミュレーションのモデルとなった回路図である。図26は図25における画素部の詳しい回路図である。画素TFT3501、保持容量3502が図26に示すように設けられている。図12に示したシミュレーションは図25におけるpointAの電位を測定したものである。

【0123】

遮蔽膜をフローティングにせずに、低抵抗(1Ω)コモン線(COM)に接続して基準電位に保った場合のシミュレーションの結果を比較のために図12(B)に示す。

【0124】

図12(A)と図12(B)を比較するとほぼ同じシミュレーション結果が得られたことがわかる。つまり、遮蔽膜をコモン線に接続せずにフローティングにし、遮蔽膜とコモン線との間にカップリング容量を設けた場合でも、画素電位の変動は見られず、遮蔽膜をフローティングにせずに、コモン線(COM)に接続して基準電位に保った場合と同程度の画像表示が可能であることがわかった。よって画質を落とすことなく、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによってコンタクトホールをあける作製工程を削減し、高い歩留まりを達成することが可能になり、またその作製コストを抑えることが可能になる。

【0125】

(実施例3)

画素マトリクス回路とその周辺に設けられる駆動回路のTFTを同時に作製する方法を、実施例1に示した以外の方法で作製する例について、図13〜図15を用いて説明する。本実施例で開示するプロセスを用いて、本願発明のアクティブマトリクス型表示装置を形成しても良い。

【0126】

〔島状半導体層、ゲート絶縁膜形成の工程:図13(A)〕

図13(A)において、基板7001には、無アルカリガラス基板や石英基板を使用することが望ましい。その他にもシリコン基板や金属基板の表面に絶縁膜を形成したものを基板としても良い。

【0127】

そして、基板7001のTFTが形成される表面には、酸化シリコン膜、窒化シリコン膜、または窒化酸化シリコン膜からなる下地膜をプラズマCVD法やスパッタ法で100〜400nmの厚さに形成した。例えば下地膜として、窒化シリコン膜7002を25〜100nm、ここでは50nmの厚さに、酸化シリコン膜7003を50〜300nm、ここでは150nmの厚さとした2層構造で形成すると良い。下地膜は基板からの不純物汚染を防ぐために設けられるものであり、石英基板を用いた場合には必ずしも設けなくても良い。

【0128】

次に下地膜の上に20〜100nmの厚さの、非晶質シリコン膜を公知の成膜法で形成した。非晶質シリコン膜は含有水素量にもよるが、好ましくは400〜550℃で数時間加熱して脱水素処理を行い、含有水素量を5atom%以下として、結晶化の工程を行うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製方法で形成しても良いが、膜中に含まれる酸素、窒素などの不純物元素を十分低減させておくことが望ましい。ここでは、下地膜と非晶質シリコン膜とは、同じ成膜法で形成することが可能であるので両者を連続形成しても良い。下地膜を形成後、一旦大気雰囲気にさらされないようにすることで表面の汚染を防ぐことが可能となり、作製されるTFTの特性バラツキを低減させることができる。

【0129】

非晶質シリコン膜から結晶質シリコン膜を形成する工程は、公知のレーザー結晶化技術または熱結晶化の技術を用いれば良い。また、シリコンの結晶化を助長する触媒元素を用いて熱結晶化の方法で結晶質シリコン膜を作製しても良い。その他に、微結晶シリコン膜を用いても良いし、結晶質シリコン膜を直接堆積成膜しても良い。さらに、単結晶シリコンを基板上に貼りあわせるSOI(Silicon On Insulators)の公知技術を使用して結晶質シリコン膜を形成しても良い。

【0130】

こうして形成された結晶質シリコン膜の不要な部分をエッチング除去して、島状半導体層7004〜7006を形成した。結晶質シリコン膜のnチャネル型TFTが作製される領域には、しきい値電圧を制御するため、あらかじめ1×1015〜5×1017cm-3程度の濃度でボロン(B)を添加しておいても良い。

【0131】

次に、島状半導体層7004〜7006を覆って、酸化シリコンまたは窒化シリコンを主成分とするゲート絶縁膜7007を形成した。ゲート絶縁膜7007は、10〜200nm、好ましくは50〜150nmの厚さに形成すれば良い。例えば、プラズマCVD法でN2OとSiH4を原料とした窒化酸化シリコン膜を75nm形成し、その後、酸素雰囲気中または酸素と塩酸の混合雰囲気中、800〜1000℃で熱酸化して115nmのゲート絶縁膜としても良い。(図13(A))

【0132】

〔n-領域の形成:図13(B)〕

島状半導体層7004、7006及び配線を形成する領域の全面と、島状半導体層7005の一部(チャネル形成領域となる領域を含む)にレジストマスク7008〜7011を形成し、n型を付与する不純物元素を添加して低濃度不純物領域7012を形成した。この低濃度不純物領域7012は、後にCMOS回路のnチャネル型TFTに、ゲート絶縁膜を介してゲート電極と重なるLDD領域(本明細書中ではLov領域という。なお、ovとはoverlapの意味である。)を形成するための不純物領域である。なお、ここで形成された低濃度不純物領域に含まれるn型を付与する不純物元素の濃度を(n-)で表すこととする。従って、本明細書中では低濃度不純物領域7012をn-領域と言い換えることができる。

【0133】

ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法でリンを添加した。望ましければ、質量分離を行うイオンインプランテーション法を用いても良い。この工程では、ゲート絶縁膜7007を通してその下の半導体層にリンを添加した。添加するリン濃度は、5×1017〜5×1018atoms/cm3の範囲にするのが好ましく、ここでは1×1018atoms/cm3とした。

【0134】

その後、レジストマスク7008〜7011を除去し、窒素雰囲気中で400〜900℃、好ましくは550〜800℃で1〜12時間の熱処理を行ない、この工程で添加されたリンを活性化する工程を行なった。

【0135】

〔ゲート電極用および配線用導電膜の形成:図13(C)〕

第1の導電膜7013を、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素またはいずれかを主成分とする導電性材料で、10〜100nmの厚さに形成した。第1の導電膜7013としては、例えば窒化タンタル(TaN)や窒化タングステン(WN)を用いることが望ましい。さらに、第1の導電膜7013上に第2の導電膜7014をTa、Ti、Mo、Wから選ばれた元素またはいずれかを主成分とする導電性材料で、100〜400nmの厚さに形成した。例えば、Taを200nmの厚さに形成すれば良い。また、図示しないが、第1の導電膜7013の下に導電膜7013、7014(特に導電膜7014)の酸化防止のためにシリコン膜を2〜20nm程度の厚さで形成しておくことは有効である。

【0136】

〔p−chゲート電極、配線電極の形成とp++領域の形成:図14(A)〕

レジストマスク7015〜7018を形成し、第1の導電膜と第2の導電膜(以下、積層膜として取り扱う)をエッチングして、pチャネル型TFTのゲート電極7019、ゲート信号線7020、7021を形成した。なお、nチャネル型TFTとなる領域の上には全面を覆うように導電膜7022、7023を残した。

【0137】

そして、レジストマスク7015〜7018をそのまま残してマスクとし、pチャネル型TFTが形成される半導体層7004の一部に、p型を付与する不純物元素を添加する工程を行った。ここではボロンをその不純物元素として、ジボラン(B2H6)を用いてイオンドープ法(勿論、イオンインプランテーション法でも良い)で添加した。ここでは5×1020〜3×1021atoms/cm3の濃度にボロンを添加した。なお、ここで形成された不純物領域に含まれるp型を付与する不純物元素の濃度を(p++)で表すこととする。従って、本明細書中では不純物領域7024、7025をp++領域と言い換えることができる。

【0138】

なお、この工程において、レジストマスク7015〜7018を使用してゲート絶縁膜7007をエッチング除去して、島状半導体層7004の一部を露出させた後、p型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0139】

〔n―chゲート電極の形成:図14(B)〕

次に、レジストマスク7015〜7018を除去した後、レジストマスク7026〜7029を形成し、nチャネル型TFTのゲート電極7030、7031を形成した。このときゲート電極7030はn-領域7012とゲート絶縁膜を介して重なるように形成した。

【0140】

〔n+領域の形成:図14(C)〕

次に、レジストマスク7026〜7029を除去し、レジストマスク7032〜7034を形成した。そして、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域を形成する工程を行なった。レジストマスク7034はnチャネル型TFTのゲート電極7031を覆う形で形成した。これは、後の工程において画素マトリクス回路のnチャネル型TFTに、ゲート電極と重ならないようにLDD領域を形成するためである。

【0141】

そして、n型を付与する不純物元素を添加して不純物領域7035〜7039を形成した。ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm3とした。なお、ここで形成された不純物領域7037〜7039に含まれるn型を付与する不純物元素の濃度を(n+)で表すこととする。従って、本明細書中では不純物領域7037〜7039をn+領域と言い換えることができる。また、不純物領域7035は既にn-領域が形成されていたので、厳密には不純物領域7037〜7039よりも若干高い濃度でリンを含む。

【0142】

なお、この工程において、レジストマスク7032〜7034およびゲート電極7030をマスクとしてゲート絶縁膜7007をエッチングし、島状半導体膜7005、7006の一部を露出させた後、n型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0143】

〔n--領域の形成:図15(A)〕

次に、レジストマスク7032〜7034を除去し、画素マトリクス回路のnチャネル型TFTとなる島状半導体層7006にn型を付与する不純物元素を添加する工程を行った。こうして形成された不純物領域7040〜7043には前記n-領域と同程度かそれより少ない濃度(具体的には5×1016〜1×1018atoms/cm3)のリンが添加されるようにした。なお、ここで形成された不純物領域7040〜7043に含まれるn型を付与する不純物元素の濃度を(n--)で表すこととする。従って、本明細書中では不純物領域7040〜7043をn--領域と言い換えることができる。また、この工程ではゲート電極で隠された不純物領域7067を除いて全ての不純物領域にn?の濃度でリンが添加されているが、非常に低濃度であるため無視して差し支えない。

【0144】

〔熱活性化の工程:図15(B)〕

次に、後に第1の層間絶縁膜の一部となる保護絶縁膜7044を形成した。保護絶縁膜7044は窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は100〜400nmとすれば良い。

【0145】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネスアニール法で活性化工程を行った。加熱処理は、窒素雰囲気中において300〜650℃、好ましくは400〜550℃、ここでは450℃、2時間の熱処理を行った。

【0146】

さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0147】

〔層間絶縁膜、ソース/ドレイン電極、遮蔽膜、画素電極、保持容量の形成:図15(C)〕

活性化工程を終えたら、保護絶縁膜7044の上に0.5〜1.5μm厚の層間絶縁膜7045を形成した。前記保護絶縁膜7044と層間絶縁膜7045とでなる積層膜を第1の層間絶縁膜とした。

【0148】

その後、それぞれのTFTのソース領域またはドレイン領域に達するコンタクトホールが形成され、ソース電極7046〜7048と、ドレイン電極7049、7050を形成した。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。

【0149】

次に、パッシベーション膜7051として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50〜500nm(代表的には200〜300nm)の厚さで形成した。その後、この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。なお、ここで後に画素電極とドレイン電極を接続するためのコンタクトホールを形成する位置において、パッシベーション膜7051に開口部を形成しておいても良い。

【0150】

その後、有機樹脂からなる第2の層間絶縁膜7052を約1μmの厚さに形成した。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成した。

【0151】

次に、画素マトリクス回路となる領域において、第2の層間絶縁膜7052上に遮蔽膜7053を形成した。遮蔽膜7053はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ばれた元素またはいずれかを主成分とする膜で100〜300nmの厚さに形成した。そして、遮蔽膜7054の表面に陽極酸化法またはプラズマ酸化法により30〜150nm(好ましくは50〜75nm)の厚さの酸化膜7054を形成した。ここでは遮蔽膜7053としてアルミニウム膜またはアルミニウムを主成分とする膜を用い、誘電体7054として酸化アルミニウム膜(アルミナ膜)を用いた。

【0152】

なお、ここでは遮蔽膜の表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCVD法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜厚は30〜150nm(好ましくは50〜75nm)とすることが好ましい。また、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond like carbon)膜または有機樹脂膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良い。

【0153】

次に、第2の層間絶縁膜7052にドレイン電極7050に達するコンタクトホールを形成し、画素電極7055を形成した。なお、画素電極7056、7057はそれぞれ隣接する別の画素の画素電極である。画素電極7055〜7057は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成した。

【0154】

また、この時、画素電極7055と遮蔽膜7053とが酸化膜7054を介して重なった領域7058が保持容量を形成した。

【0155】

こうして同一基板上に、ドライバー回路となるCMOS回路と画素マトリクス回路とを有したアクティブマトリクス基板が完成した。なお、ドライバー回路となるCMOS回路にはpチャネル型TFT7081、nチャネル型TFT7082が形成され、画素マトリクス回路にはnチャネル型TFTでなる画素TFT7083が形成された。

【0156】

CMOS回路のpチャネル型TFT7081には、チャネル形成領域7061、ソース領域7062、ドレイン領域7063がそれぞれp+領域で形成された。また、nチャネル型TFT7082には、チャネル形成領域7064、ソース領域7065、ドレイン領域7066、ゲート絶縁膜を介してゲート電極と重なったLDD領域(以下、Lov領域という。なお、ovとはoverlapの意である。)7067が形成された。この時、ソース領域7065、ドレイン領域7066はそれぞれ(n-+n+)領域で形成され、Lov領域7067はn-領域で形成された。

【0157】

また、画素TFT7083には、チャネル形成領域7068、7069、ソース領域7070、ドレイン領域7071、ゲート絶縁膜を介してゲート電極と重ならないLDD領域(以下、Loff領域という。なお、offとはoffsetの意である。)7072〜7075、Loff領域7073、7074に接したn+領域7076が形成された。この時、ソース領域7070、ドレイン領域7071はそれぞれn+領域で形成され、Loff領域7072〜7075はn--領域で形成された。

【0158】

また、チャネル長3〜7μmに対してLov領域の長さ(幅)は0.5〜3.0μm、代表的には1.0〜1.5μmとすれば良い。また、画素TFT7083に設けられるLoff領域7072〜7075の長さ(幅)は0.5〜3.5μm、代表的には2.0〜2.5μmとすれば良い。

【0159】

図28に、コモン線と、FPCからの引き出し端子との接合部分を示す。基板7001、図15(C)に示したnチャネル型TFTを有するゲート信号線駆動回路2902、コモン線2903、遮蔽膜2904、誘電体2905、ITO膜2906、フィラー2907、樹脂2908、FPCからの引き出し端子上に成膜されたITO膜2909、FPCからの引き出し端子2910が図28に示すように設けられている。

【0160】

遮蔽膜2904とITO膜2906と、その間に挟まれた誘電体2905とによって、カップリング容量が形成されている。ITO膜2906は、ゲート信号線駆動回路2902上に設けられており、ゲート信号線駆動回路2902の下に設けられたコモン線2903と接続している。FPCからの引き出し端子2910上にはFPC側のITO膜2909が接するように形成されており、FPCからの引き出し端子2910上のFPC側のITO膜2909とITO膜2906とは、フィラー2907と樹脂2908とによって接続されている。

【0161】

樹脂2908は光硬化性の樹脂であっても、熱硬化性の樹脂であっても良く、また光硬化性の樹脂と熱硬化性の樹脂との混合物であっても良い。光硬化性の樹脂と熱硬化性の樹脂との混合物を用いた場合、光によって仮接着の後、熱を加えて圧着させることにより接続する。またフィラーは導電性の材料であることが必要である。大きさの異なるフィラーを2種類以上用いても良く、この場合、サイズの小さいフィラーはスペーサとして働くので導電性でなくても良く、サイズの大きい粒子は電気的に接続させる働きをするので導電性であることが必要である。

【0162】

本願発明では、ソースライン反転によって液晶を駆動してやり、かつ遮蔽膜を一定の電位(基準電位)に保たれたコモン線に接続しない。ソースライン反転によって、遮蔽膜の電位は時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量において、遮蔽膜をフローティングにすることが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線とを接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装の作製コストを抑えることが可能になる。

【0163】

(実施例4)

上述の実施例1〜3で説明した本願発明の液晶表示装置は、図16に示すような3板式のプロジェクタに用いることができる。

【0164】

図16において、2401は白色光源、2402〜2405はダイクロイックミラー、2406ならびに2407は全反射ミラー、2408〜2410は本願発明の液晶表示装置、および2411は投影レンズである。

【0165】

(実施例5)

また、上述の実施例1〜3で説明した本願発明の液晶表示装置は、図17に示すような3板式のプロジェクタに用いることもできる。

【0166】

図17において、2501は白色光源、2502ならびに2503はダイクロイックミラー、2504〜2506は全反射ミラー、2507〜2509は本願発明の液晶表示装置、および2510はダイクロイックプリズム、および2511は投影レンズである。

【0167】

(実施例6)

また、上述の実施例1〜3で説明した本願発明の液晶表示装置は、図18に示すような単板式のプロジェクタに用いることもできる。

【0168】

図18において、2601はランプとリフレクターとから成る白色光源である。2602、2603、および2604は、ダイクロイックミラーであり、それぞれ青、赤、緑の波長領域の光を選択的に反射する。2605はマイクロレンズアレイであり、複数のマイクロレンズによって構成されている。2606は本願発明の液晶表示装置である。2607はフィールドレンズ、2608は投影レンズ、2609はスクリーンである。

【0169】

(実施例7)

上記実施例5〜7のプロジェクタは、その投影方法によってリアプロジェクターとフロントプロジェクターとがある。

【0170】

図19(A)はフロント型プロジェクタ−であり、本体10001、本願発明の液晶表示装置10002、光源10003、光学系10004、スクリーン10005で構成されている。なお、図19(A)には、液晶表示装置を1つ組み込んだフロントプロジェクターが示されているが、液晶表示装置を3つ(R、G、Bの光にそれぞれ対応させる)組み込むことによって、より高解像度・高精細のフロント型プロジェクタを実現することができる。

【0171】

図19(B)はリア型プロジェクターであり、10006は本体、10007は液晶表示装置であり、10008は光源であり、10009はリフレクター、10010はスクリーンである。なお、図19(B)には、アクティブマトリクス型半導体表示装置を3つ(R、G、Bの光にそれぞれ対応させる)組み込んだリア型プロジェクタが示されている。

【0172】

(実施例8)

本実施例では、本願発明の液晶表示装置をゴーグル型ディスプレイに用いた例を示す。

【0173】

図20を参照する。2801はゴーグル型ディスプレイ本体である。2802−Rならびに2802−Lは本願発明の液晶表示装置であり、2803−Rならびに2803−LはLEDバックライトであり、2804−Rならびに2804−Lは光学素子である。

【0174】

(実施例9)

本願発明の液晶表示装置には他に様々な用途がある。本実施例では、本願発明の液晶表示装置を組み込んだ半導体装置について説明する。

【0175】

このような半導体装置には、ビデオカメラ、スチルカメラ、カーナビゲーション、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話など)などが挙げられる。それらの一例を図21に示す。

【0176】

図21(A)は携帯電話であり、本体11001、音声出力部11002、音声入力部11003、本願発明の液晶表示装置11004、操作スイッチ11005、アンテナ11006で構成される。

【0177】

図21(B)はビデオカメラであり、本体12007、本願発明の液晶表示装置12008、音声入力部12009、操作スイッチ12010、バッテリー12011、受像部12012で構成される。

【0178】

図21(C)はモバイルコンピュータであり、本体13001、カメラ部13002、受像部13003、操作スイッチ13004、本願発明の液晶表示装置1305で構成される。

【0179】

図21(D)は携帯書籍(電子書籍)であり、本体14001、本願発明の液晶表示装置14002、14003、記憶媒体14004、操作スイッチ14005、アンテナ14006で構成される。

【0180】

(実施例10)

【0181】

本実施例においては、本願発明の液晶表示装置をノートブック型パーソナルコンピュータに用いた例を図22に示す。

【0182】

3001はノートブック型パーソナルコンピュータ本体であり、3002は本願発明の液晶表示装置である。また、バックライトにはLEDが用いられている。なお、バックライトに従来のように陰極管を用いても良い。

【0183】

(実施例11)

本実施例では、遮蔽膜をアクティブマトリクス部を有するアクティブマトリクス基板上だけではなく、対向基板上にも設ける例について説明する。

【0184】

基板(アクティブマトリクス基板)501、ソース信号線駆動回路511、ゲート信号線駆動回路502、アクティブマトリクス部513、遮蔽膜504、ITO膜506、コモン線507、FPC514が図24(A)に示すように設けられている。また対向基板上に設けられた対向遮蔽膜517が図に示すようにソース信号線駆動回路511全体と重なっており、遮蔽膜504と一部重なっている。この実施例では対向遮蔽膜504をソース信号線駆動回路511全体と重なるように、対向基板上に設けたが、ソース信号線駆動回路が有するサンプリング回路のみと重なるようにしても良い。

【0185】

ITO膜506とコモン線507は電気的に接続されており、コモン線507はFPC514によって基板の外部に接続され、一定の電位(基準電位)に保たれている。

【0186】

コモン線507に接続されたITO膜506と遮蔽膜504の重なった部分にカップリング容量516が形成されている。

【0187】

対向遮蔽膜517と遮蔽膜504の重なっている部分(重複部)518は、外部からの光がソース信号線駆動回路511に入射するのを防ぐ。光がソース信号線駆動回路511、特にソース信号線駆動回路が有するサンプリング回路に入射すると、サンプリング回路を構成する薄膜トランジスタ(TFT)のオフ電流が増加してしまい、ノイズの原因となる。対向遮蔽膜517は、Tiを有していることが望ましく、Tiを有することで光が対向遮蔽膜517に反射してソース信号線駆動回路に入射するのを防ぐ。また重複部518を20μm以上設けることが、ソース信号線駆動回路511への光の入射を防ぐのに効果的である。

【0188】

図24(B)に、図24(A)のA−A’における断面図を示す。基板501、アクティブマトリクス部513、層間絶縁膜512、遮蔽膜504、誘電体505、対向基板521、対向基板側層間絶縁膜522、対向基板側遮蔽膜517が図に示すように設けられている。基板501と対向基板521はスペーサ(図示せず)を挟んで、シール材(図示せず)により接着される。遮蔽膜504と対向基板側遮蔽膜517は一部重なっており、この重なりの幅Lは20μm以上あることが好ましい。

【0189】

また、アクティブマトリクス基板上の回路は、実施例1〜3と同様の方法で作製すれば良い。また以下の実施例で開示される方法を用いても良い。

【0190】

(実施例12)

本願発明の画素マトリクス回路とその周辺に設けられる駆動回路のTFTを同時に作製する実施例1に示した以外の方法の一例について、図29を用いて説明する。なお、本願発明はこの作製方法に限られない。

【0191】

実施例1の図8(C)の工程まで同様に形成する。次にレジストマスクを用いて、第1の導電膜と第2の導電膜(以下、積層膜として取り扱う)をエッチングして、pチャネル型TFTのゲート電極8001、nチャネル型TFTのゲート電極8002、ゲート信号線8003a、8003bを形成した。このときゲート電極8002はn-領域6012、6013とゲート絶縁膜を介して重なるようにした。(図29(A))

【0192】

そして、pチャネル型TFTのゲート電極8001、nチャネル型TFTのゲート電極8002、ゲート信号線8003a、8003bをそれぞれマスクとして、n型を付与する不純物を添加した。こうして形成された不純物領域8004、8005、8006、8007、8008には、図8(B)で示した前記n-領域と同程度かそれより少ない濃度(具体的には5×1016〜1×1018atoms/cm3)のリンが添加されるようにした。なお、ここで形成された不純物領域8004〜8008に含まれるn型を付与する不純物元素の濃度を(n--)で表すこととする。従って、本明細書中では不純物領域8004〜8008をn--領域と言い換えることができる。また、この工程ではゲート電極で隠された不純物領域8009、8010を除いて全ての不純物領域にn?の濃度でリンが添加されているが、非常に低濃度であるため無視して差し支えない。(図29(B))

【0193】

次に、レジストマスク8011〜8014を形成した。そして、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域を形成する工程を行なった。レジストマスク8012はnチャネル型TFTのゲート電極8002を覆う形で形成した。これは、後の工程において画素マトリクス回路のnチャネル型TFTに、ゲート電極と重ならないようにLDD領域を形成するためである。

【0194】

そして、n型を付与する不純物元素を添加して不純物領域8016〜8022を形成した。ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm3とした。なお、ここで形成された不純物領域8018〜8022に含まれるn型を付与する不純物元素の濃度を(n+)で表すこととする。従って、本明細書中では不純物領域8018〜8022をn+領域と言い換えることができる。また、不純物領域8009、8010は既にn-領域が形成されていたので、厳密には不純物領域8020〜8022よりも若干高い濃度でリンを含む。(図29(C))

【0195】

なお、この工程において、レジストマスク8011〜8014をマスクとしてゲート絶縁膜6007をエッチングし、島状半導体膜6005、6006の一部を露出させた後、n型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0196】

レジストマスク8024を、nチャネル型TFTとなる領域の上全面を覆うように形成した。そして、レジストマスク8024をマスクとし、pチャネル型TFTが形成される半導体層6004の一部に、p型を付与する不純物元素を添加する工程を行った。ここではボロンをその不純物元素として、ジボラン(B2H6)を用いてイオンドープ法(勿論、イオンインプランテーション法でも良い)で添加した。ここでは5×1020〜3×1021atoms/cm3の濃度にボロンを添加した。なお、ここで形成された不純物領域に含まれるp型を付与する不純物元素の濃度を(p+)で表すこととする。従って、本明細書中では不純物領域8025、8026をp+領域と言い換えることができる。(図29(D))

【0197】

なお、この工程において、レジストマスク8024を使用してゲート絶縁膜6007をエッチング除去して、島状半導体層6004の一部を露出させた後、p型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、島状半導体膜に与えるダメージも少ないし、スループットも向上する。

【0198】

次に、添加された不純物元素(リンまたはボロン)の活性化工程を行う。本実施例ではこの活性化工程をファーネスアニールまたはランプアニールによって行うことが好ましい。ファーネスアニールを用いる場合、450〜650℃、好ましくは500〜550℃、ここでは500℃、4時間の熱処理を行うことにする。(図29(E))

【0199】

本実施例の場合、nチャネル型TFTおよびpチャネル型TFTの双方のソース領域またはドレイン領域に、必ずn+領域に相当する濃度のリンが含まれた領域を有する。そのため、熱活性化のための熱処理工程において、リンによるニッケルのゲッタリング効果を得ることができる。即ち、チャネル形成領域から矢印で示す方向へニッケルが移動し、ソース領域またはドレイン領域に含まれるリンの作用によってゲッタリングされる。これは特に結晶化を促進させる金属、例えばニッケルを用いた場合に有効である。

【0200】

このように本実施例を実施すると、島状半導体膜に添加された不純物元素の活性化工程と、結晶化に用いた触媒元素のゲッタリング工程とを兼ねることができ、工程の簡略化に有効である。

【0201】

そして実施例1で上述したように、図10(C)に示したのと同様の工程で、画素マトリクス回路とその周辺に設けられる駆動回路のTFTを完成する。なお、本実施例で示した作製工程は一例であり、作製工程の順序は本実施例の形態に限られない。

【0202】

(実施例13)

本実施例では、本願発明のアクティブマトリクス回路の断面図及び上面図の、図23で示したものとは別の例について説明する。図30に図11の上面及び断面の概略図を示す。図30(A)は本願発明のアクティブマトリクス回路の上面図である。

【0203】

基板601に、ソース信号線駆動回路611(図11に示すところの301)、ゲート信号線駆動回路602(図11に示すところの302)、アクティブマトリクス部613(図11に示すところの303)、遮蔽膜604、ITO膜606、コモン線607、FPC614が図30(A)に示すように設けられている。

【0204】

ITO膜606とコモン線607は、接続部608において電気的に接続しており、コモン線607はFPC614によって基板の外部に接続され、一定の電位(基準電位)に保たれている。

【0205】

コモン線607に接続されたITO膜606と遮蔽膜604の重なった部分にカップリング容量616(図11で示すところの310)が形成されている。本実施例においてITO膜606はゲート信号線駆動回路602の一部を覆うように形成されているため、容量値の大きいカップリング容量616を形成することが可能である。なおITO膜606をゲート信号線駆動回路602全体を覆うように形成しても良い。

【0206】

図30(B)は、図30(A)のA−A’における断面図である。基板601、ゲート信号線駆動回路602が有するnチャネル型TFTの1つ616、層間絶縁膜617、遮蔽膜604(図11に示すところの311)、誘電体605、ITO膜606、コモン線607(図11に示すところの312)、フィラー612、樹脂610、FPCからの引き出し端子上に成膜されたITO膜609、FPCからの引き出し端子615が図30(B)に示すように設けられている。

【0207】

遮蔽膜604とITO膜606と、その間に挟まれた誘電体605とによって、カップリング容量が形成されている。ITO膜606は、ゲート信号線駆動回路602上に設けられており、言い換えると、ゲート信号線駆動回路602が有するnチャネル型TFTの1つ616の上に設けられている。

【0208】

またITO膜606は、基板601上に設けられたコモン線607と、接続部608において接続している。なお本実施例ではITO膜606とコモン線607とを直接接続しているが、別の配線等を間に介して接続することにより、ITO膜606とコモン線607とを電気的に接続しても良いことは言うまでもない。

【0209】

FPCからの引き出し端子615上にはFPC側のITO膜609が接するように形成されており、FPCからの引き出し端子615上のFPC側のITO膜609とITO膜606とは、フィラー612と樹脂610とによって接続されている。

【0210】

樹脂610は光硬化性の樹脂であっても、熱硬化性の樹脂であっても良く、また光硬化性の樹脂と熱硬化性の樹脂との混合物であっても良い。光硬化性の樹脂と熱硬化性の樹脂との混合物を用いた場合、光によって仮接着の後、熱を加えて圧着させることにより接続する。またフィラーは導電性の材料であることが必要である。大きさの異なるフィラーを2種類以上用いても良く、この場合、サイズの小さいフィラーはスペーサとして働くので導電性でなくても良く、サイズの大きい粒子は電気的に接続させる働きをするので導電性であることが必要である。

【0211】

本実施例のアクティブマトリクス回路と駆動回路は、これまでの実施例で開示した方法を用いて作製することが可能である。

【0212】

(実施例14)

本実施例では、本願発明を用いた電気光学装置のうち、図16〜図22で示した以外のものについて、その一例を図31に示す。

【0213】

図31(A)はディスプレイであり、筐体2001、支持台2002、表示部2003等を含む。本願発明は表示部2003に適用することができる。

【0214】

図31(B)は頭部取り付け型のディスプレイの一部(右片側)であり、本体2201、信号ケーブル2202、頭部固定バンド2203、スクリーン部2204、光学系2205、表示部2206等を含む。本願発明は表示部2206に適用できる。

【0215】

図31(C)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2301、表示部2302、スピーカ部2303、記録媒体2304、操作スイッチ2305で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本願発明は表示部2302に適用することができる。

【0216】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜3、11〜13のどのような組み合わせからなる構成を用いても実現することができる。

【0217】

【発明の効果】

ソースライン反転で液晶を駆動させて、遮蔽膜をコモン線に接続せずにフローティングとしている。このような構成にすることで、遮蔽膜をコモン線に接続しなくても、遮蔽膜の電位が時間的に平均を取ると一定に保たれるので、遮蔽膜と画素電極との間に誘電体を挟み込んだ構造の保持容量を形成することが可能になる。よって遮蔽膜をパターニングによって形成した後に、遮蔽膜とコモン線を接続するために、遮蔽膜とコモン線との間に設けられた層間絶縁膜にマスクを用いたフォトリソグラフィーによるコンタクトホールをあける必要がなくなる。このため作製工程を削減し、高い歩留まりを達成することが可能になり、またアクティブマトリクス型液晶表示装の作製コストを抑えることが可能になる。またそれに加えて、遮蔽膜をフローティングにして遮蔽膜とコモン線との間に大容量のカップリング容量を形成した場合は、遮蔽膜の電位をさらに一定に保つことが可能になるため、良好なコントラストを得ることができる。

【0218】

なお、上記実施例はTFTの活性層として珪素膜を例にとって説明したが、必要に応じて不純物を添加したり、Si−Ge化合物など、他の半導体を用いても良い。また画素が有するTFTとして、ダブルゲート構造を有するTFTを示したが、シングルゲート構造を有していても良いし、他のマルチゲート構造を有していても良い。また画素が有するTFTの活性層が、a−Si(アモルファスシリコン)を有していても良い。

【図面の簡単な説明】

【図1】 本願発明のアクティブマトリクス回路の回路図。

【図2】 本願発明の画素マトリクス回路の上面構造を示す図。

【図3】 本願発明の画素マトリクス回路の上面構造を示す図。

【図4】 ソースライン反転の概念を示す図。

【図5】 ソース信号線駆動回路のブロック図。

【図6】 ソース信号線駆動回路の回路図。

【図7】 アナログスイッチとレベルシフト回路の等価回路図。

【図8】 本願発明のTFTの作製工程を示す断面図。

【図9】 本願発明のTFTの作製工程を示す断面図。

【図10】 本願発明のTFTの作製工程を示す断面図。

【図11】 本願発明のアクティブマトリクス回路の回路図。

【図12】 本願発明のシミュレーション結果を示す図。

【図13】 本願発明のTFTの作製工程を示す断面図。

【図14】 本願発明のTFTの作製工程を示す断面図。

【図15】 本願発明のTFTの作製工程を示す断面図。

【図16】 本願発明の液晶表示装置を用いた3板式プロジェクタの概略構成図。

【図17】 本願発明の液晶表示装置を用いた3板式プロジェクタの概略構成図。

【図18】 本願発明の液晶表示装置を用いた単板式プロジェクタの概略構成図。

【図19】 本願発明の液晶表示装置を用いたフロントプロジェクタおよびリアプロジェクタの概略構成図。

【図20】 本願発明の液晶表示装置を用いたゴーグル型ディスプレイの概略構成図。

【図21】 本願発明の液晶表示装置を用いた電子機器の例。

【図22】 本願発明の液晶表示装置を用いたノートブック型パーソナルコンピュータの概略構成図。

【図23】 本願発明のアクティブマトリクス回路の断面図及び上面図。

【図24】 本願発明のアクティブマトリクス回路の上面図。

【図25】 アクティブマトリクス基板のシミュレーションのモデルとなる回路図。

【図26】 アクティブマトリクス基板のシミュレーションのモデルとなる回路における画素部の回路図。

【図27】 ゲート信号線駆動回路上に設けられたITOに接続されたコモン線と、FPCの取り出し端子との接合部分の断面図。

【図28】 ゲート信号線駆動回路上に設けられたITOに接続されたコモン線と、FPCの取り出し端子との接合部分の断面図。

【図29】 本願発明のTFTの作製工程を示す断面図。

【図30】 本願発明のアクティブマトリクス回路の断面図及び上面図。

【図31】 本願発明の液晶表示装置を用いた電子機器の例。

【符号の説明】

11 ソース信号線駆動回路

12 ゲート信号線駆動回路

13 アクティブマトリクス部

14 画素TFT

15 液晶

16 保持容量

17 ソース信号線

18 ゲート信号線

19 画素部

Claims (8)

- 基板上に形成された複数のソース信号線と、

前記基板上に形成された複数のゲート信号線と、

前記基板上に形成された複数の画素トランジスタと、

前記複数の画素トランジスタ上に形成された遮光性を有する被膜と、

前記遮光性を有する被膜上の前記画素トランジスタに電気的に接続された画素電極と、

前記画素電極と前記遮光性を有する被膜との間に設けられた誘電体と、を有し、

前記画素電極と、前記遮光性を有する被膜と、前記誘電体とで容量が形成され、

前記複数の画素トランジスタは前記ソース信号線と前記ゲート信号線に電気的に接続され、

前記遮光性を有する被膜はフローティングになっており、

前記複数のソース信号線1ラインごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型表示装置。 - 基板上に形成された一定の基準電位に保たれたコモン線と、

前記コモン線上の複数のソース信号線と、

前記コモン線上の複数のゲート信号線と、

前記コモン線上の複数の画素トランジスタ及び前記複数の画素トランジスタに電気的に接続された画素電極を有する画素マトリクス部と、

前記複数の画素トランジスタ上に形成された遮光性を有する被膜と、

前記画素電極と前記遮光性を有する被膜との間に設けられた第1の誘電体と、

前記遮光性を有する被膜と前記コモン線との間に設けられた第2の誘電体と、

を有し、

前記画素電極と、前記遮光性を有する被膜と、前記第1の誘電体とで第1の容量が形成され、

前記遮光性を有する被膜と、前記コモン線と、前記第2の誘電体とで第2の容量が形成され、

前記複数の画素トランジスタは前記ソース信号線と前記ゲート信号線に電気的に接続され、

前記遮光性を有する被膜はフローティングになっており、

前記複数のソース信号線1ラインごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型表示装置。 - 第1の基板上に形成された一定の基準電位に保たれたコモン線と、

前記コモン線上の複数のソース信号線と、

前記コモン線上の複数のゲート信号線と、

前記コモン線上の複数の画素トランジスタ及び前記複数の画素トランジスタに電気的に接続された画素電極を有する画素マトリクス部と、

前記複数の画素トランジスタ上に形成された第1の遮光性を有する被膜と、

前記画素電極と前記第1の遮光性を有する被膜との間に設けられた第1の誘電体と、

前記第1の遮光性を有する被膜と前記コモン線との間に設けられた第2の誘電体と、

ソース信号線駆動回路と、

第2の基板上に形成された第2の遮光性を有する被膜と、

を有し、

前記画素電極と、前記第1の遮光性を有する被膜と、前記第1の誘電体とで第1の容量が形成され、

前記第1の遮光性を有する被膜と、前記コモン線と、前記第2の誘電体とで第2の容量が形成され、

前記第1の遮光性を有する被膜と前記第2の遮光性を有する被膜とが対向するように配置され、

前記複数の画素トランジスタは前記ソース信号線と前記ゲート信号線に電気的に接続され、

前記第1の遮光性を有する被膜はフローティングになっており、

前記ソース信号線駆動回路はサンプリング回路を有し、

前記第2の遮光性を有する被膜は、前記第1の遮光性を有する被膜の一部及び前記サンプリング回路と重なり、

前記複数のソース信号線1ラインごとに極性が逆の信号を印加し、前記複数のソース信号線のそれぞれに印加される前記信号の極性を1フレーム期間ごとに反転させることを特徴とするアクティブマトリクス型表示装置。 - 請求項2又は請求項3において、

前記第2の誘電体は前記画素マトリクス部と重ならないことを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至請求項4のいずれか一項において、

対向電極と、

前記画素電極と前記対向電極との間に挟まれた液晶と、を有することを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至請求項5のいずれか一項において、

前記遮光性を有する被膜は、アルミニウム、チタン、又はタンタルを含む膜であることを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至請求項6のいずれか一項に記載の前記アクティブマトリクス型表示装置を備えたプロジェクター。

- 請求項1乃至請求項6のいずれか一項に記載の前記アクティブマトリクス型表示装置を備えた電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000053470A JP4727018B2 (ja) | 1999-03-05 | 2000-02-29 | アクティブマトリクス型表示装置 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP1999059455 | 1999-03-05 | ||

| JP5945599 | 1999-03-05 | ||

| JP11-59455 | 1999-03-05 | ||

| JP2000053470A JP4727018B2 (ja) | 1999-03-05 | 2000-02-29 | アクティブマトリクス型表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010048528A Division JP4975124B2 (ja) | 1999-03-05 | 2010-03-05 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000321603A JP2000321603A (ja) | 2000-11-24 |

| JP2000321603A5 JP2000321603A5 (ja) | 2007-04-26 |

| JP4727018B2 true JP4727018B2 (ja) | 2011-07-20 |

Family

ID=26400503

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000053470A Expired - Lifetime JP4727018B2 (ja) | 1999-03-05 | 2000-02-29 | アクティブマトリクス型表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4727018B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4536198B2 (ja) * | 1999-03-15 | 2010-09-01 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| KR100737910B1 (ko) * | 2000-11-27 | 2007-07-10 | 삼성전자주식회사 | 폴리실리콘형 박막트랜지스터 제조방법 |

| JP4655943B2 (ja) * | 2006-01-18 | 2011-03-23 | セイコーエプソン株式会社 | 電気光学装置及びその製造方法、並びに導電層の接続構造 |

| KR20080015696A (ko) | 2006-08-16 | 2008-02-20 | 삼성전자주식회사 | 액정 표시 장치 |

| JP2013214085A (ja) * | 2013-06-04 | 2013-10-17 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| WO2020121876A1 (ja) * | 2018-12-12 | 2020-06-18 | シャープ株式会社 | 走査アンテナおよび走査アンテナの製造方法 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3825486B2 (ja) * | 1994-12-09 | 2006-09-27 | 三洋電機株式会社 | 液晶表示装置 |

| JP3784491B2 (ja) * | 1997-03-28 | 2006-06-14 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

-

2000

- 2000-02-29 JP JP2000053470A patent/JP4727018B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000321603A (ja) | 2000-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4975124B2 (ja) | 液晶表示装置 | |

| JP6158848B2 (ja) | 液晶表示装置 | |

| JP5292451B2 (ja) | 半導体表示装置 | |

| US7391055B1 (en) | Capacitor, semiconductor device and manufacturing method thereof | |

| US7662704B2 (en) | Electro-optical device, method of manufacturing the same, electronic apparatus, and semiconductor device | |

| JP2002319679A (ja) | 半導体装置 | |

| JP5051942B2 (ja) | 半導体装置 | |

| JP4727018B2 (ja) | アクティブマトリクス型表示装置 | |

| US6690434B1 (en) | Active matrix liquid crystal display device | |

| JP4536198B2 (ja) | 液晶表示装置 | |

| JP3886698B2 (ja) | 液晶表示装置、液晶表示装置の駆動方法、ディスプレイ、プロジェクター、ゴーグル型ディスプレイ、携帯情報端末及びコンピュータ | |

| JP2000347634A (ja) | 液晶表示装置 | |

| JP4459332B2 (ja) | アクティブマトリクス型液晶表示装置 | |

| JP5084114B2 (ja) | プロジェクター | |

| JP4283281B2 (ja) | 液晶表示装置及び半導体装置 | |

| JP3950906B2 (ja) | 半導体装置及びプロジェクター | |

| JP4050264B2 (ja) | 液晶表示装置並びにそれを備えたディスプレイ、プロジェクター、ゴーグル型ディスプレイ、及び携帯情報端末 | |

| JP2005031696A (ja) | 液晶表示装置及びその駆動方法 | |

| JP2004111562A (ja) | 素子基板及びその製造方法、電気光学装置、投射型表示装置 | |

| JP2004355034A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070227 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100104 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100112 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100817 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101006 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110405 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110413 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4727018 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140422 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140422 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |