JP4724924B2 - 表示装置の製造方法 - Google Patents

表示装置の製造方法 Download PDFInfo

- Publication number

- JP4724924B2 JP4724924B2 JP2001032688A JP2001032688A JP4724924B2 JP 4724924 B2 JP4724924 B2 JP 4724924B2 JP 2001032688 A JP2001032688 A JP 2001032688A JP 2001032688 A JP2001032688 A JP 2001032688A JP 4724924 B2 JP4724924 B2 JP 4724924B2

- Authority

- JP

- Japan

- Prior art keywords

- display device

- light emitting

- layer

- semiconductor light

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

- H10H20/821—Bodies characterised by their shape, e.g. curved or truncated substrates of the light-emitting regions, e.g. non-planar junctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H29/00—Integrated devices, or assemblies of multiple devices, comprising at least one light-emitting semiconductor element covered by group H10H20/00

- H10H29/10—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00

- H10H29/14—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00 comprising multiple light-emitting semiconductor components

- H10H29/142—Two-dimensional arrangements, e.g. asymmetric LED layout

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/817—Bodies characterised by the crystal structures or orientations, e.g. polycrystalline, amorphous or porous

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

Landscapes

- Led Devices (AREA)

- Led Device Packages (AREA)

Description

【発明の属する技術分野】

本発明は表示装置およびその製造方法に関するものであり、更に詳しくは、発光源である半導体発光素子を埋め込んだ絶縁層を薄層化させて露出される半導体発光素子の上端部に導電体膜を形成させることによって上端部電極が引き出されている表示装置およびその製造方法に関するものである。

【0002】

【従来の技術】

絶縁層で被覆された半導体装置の電極を外部へ引き出す方法として、リソグラフィによって絶縁層にコンタクトホールを穿設し、そのコンタクトホール内に導体材料を例えばスパッタリング法によって埋め込むと共に、絶縁層の表面に導体膜を形成させることが広く行われている。

【0003】

【発明が解決しようとする課題】

図17は半導体装置50内の電極51を引き出す過程を示す図あるが、図17のAは電極51が設けられたシリコン基板52とその表面に形成されたSiO2 絶縁層53を示す断面図である。そして、この電極51を絶縁層53の上面側へ引き出す場合には、図17のBに示すように、電極51の存在する箇所を定めてコンタクトホール54が穿設される。この時、コンタクトホール54は電極51と位置ずれし易く、電極51が微小である程位置ずれの確率は増大する。

【0004】

また、コンタクトホール54を導体金属で埋め、絶縁層53の上面に引き出し電極を設けるために、例えばアルミニウムのような導体金属55のスパッタリングまたは蒸着が行われる。しかし、この時の導体金属粒子の直進性によって、図17のCに示すように、コンタクトホール54の底部には導体金属55が付着するが、コンタクトホール54の上端開口の内周部にデポジットし成長する導体金属55の影となって、コンタクトホール54の側壁には導体金属55が付着しにくい。更に進むと、図17のDに示すように、コンタクトホール54はその側壁部分で接続不良を生じたり、内部に空洞を残した状態で開口が閉じられるようなトラブルを招くに至る。

【0005】

本発明は上述の問題に鑑みてなされ、基体面に半導体発光素子を配し絶縁層で被覆して取り付けた表示装置において、半導体発光素子の上端部電極が簡易かつ確実に引き出された表示装置およびその製造方法を提供することを課題とする。

【0006】

なおこのような接続の簡易化に関して、絶縁層をエッチバックするものとして次に示すような先行技術がある。すなわち、特開平7−142579号公報には、コンタクトホールに代わるコンタクト配線が採用されている。図18は表面伝導型電子放出素子(SCE)を要素とする画像表示装置を製造する場合の下層配線と上層配線とをコンタクト配線で接続する過程を示す図であるが、図18のAに示すように、絶縁性基板61上に形成された下層配線62に金属を電子線ビーム蒸着し不要部をリフトアップすることによってコンタクト配線63を形成させ、続いて図18のBに示すように、スパッタ法によって全面に酸化ケイ素等の絶縁膜64を形成させ、更に、図18のCに示すように、全面にフォトレジスト65を形成させた後、図18のDに示すように、エッチバックして平坦化させながらコンタクト配線63の表面を露出させ、図18のEに示すように、上層配線66を施した多層配線が開示されている。しかし、この方法はコンタクト配線を露出させるものであり、半導体発光素子を露出させるものではない。

【0007】

また、特開平7−94124号公報には、電界放出陰極を備えた表示装置における発光素子の製造方法として、図19のAに示すように、基板70の一方の主表面に陰極チップ70aを形成し、図19のBに示すように、基板70上にスパッタリングによって絶縁膜72、陽極層73を順次に形成させ、更に、図19のCに示すように、スパッタリングによって蛍光材層74を形成させ、次いで図16のDに示すように、ポリイミド樹脂層75を披着させて平坦化させた後、ポリイミド樹脂層75をエッチバックして蛍光材層74の隆起部分を露呈させ、その周囲にポリイミド樹脂層75を残存させる。そして、図19のEに示すように、残存するポリイミド樹脂層75をマスクとして蛍光材層74、陽極層73、絶縁膜72を順次に選択的にエッチングして、陰極チップ70aを露呈させることが行われている。しかし、この方法は陰極チップを露出させること自体を目的とするものであり、露出させた半導体発光素子上端部電極を引き出すためのものではない。

【0008】

【課題を解決するための手段】

上記の課題は請求項1または請求項14の構成によって解決されるが、その解決手段を説明すれば、次の如くである。

【0009】

請求項1の表示装置は、複数の半導体発光素子が基体面に配置され取り付けられた表示装置において、半導体発光素子を埋め込んだ絶縁層が選択的または非選択的に薄層化されて露出される半導体発光素子の上端部に導体膜が形成されて、半導体発光素子の上端部電極が絶縁層の上面に引き出されている装置である。このような表示装置は、絶縁層に上端部電極を引き出すためのコンタクトホールを設けないので、コンタクトホールと上端部電極との位置ずれやコンタクトホール内における接続不良とも無縁であり、半導体発光素子の上端部電極が簡易かつ確実に接続されたものとなる。

【0010】

請求項1に従属する請求項2の表示装置は、絶縁層がポリイミド樹脂、エポキシ樹脂、合成ゴムを含む塗膜形成の可能な高分子化合物、または塗膜形成の可能なガラスからなる装置である。このような表示装置は、絶縁層が塗布によって形成されるので、基体面の面積が大である場合にも絶縁層が簡易に形成され、表示装置は低コスト化される。

請求項1に従属する請求項3の表示装置は、絶縁層がCVD(化学的気相成長)法またはスパッタリング法によって形成される酸化ケイ素または窒化ケイ素からなる装置である。このような表示装置は、無機物の絶縁層によって優れた耐熱性を示す。

【0011】

請求項1に従属する請求項4の表示装置は、絶縁層の薄層化が酸素プラズマ雰囲気下のドライエッチング法、化学的機械的研摩法、または両者の組み合わせによって行われた装置である。このような表示装置は、採用される絶縁層の材料種や薄層化の状況に応じて最も適切な方法が取捨選択されたものとなる。

請求項1に従属する請求項5の表示装置は、半導体発光素子が発光領域から基体面上の下端面へ向かう方向を主たる発光方向とするものであり、発光領域より上部に下方への反射面を有している装置である。このような表示装置は、半導体発光素子の発光を反射面によって効果的に発光方向の下端面へ向かわせる。

【0012】

請求項5に従属する請求項6の表示装置は、半導体発光素子が角錐形状または角錐台形状に形成されており、それらが有する面のうち少なくとも傾斜面の何れか一面が反射面とされている装置である。このような表示装置は多角錐または多角錐台の傾斜面、多角錐台にあっては上面も反射面とすることによって、発光を下端面側へ集中させ得る。

請求項5に従属する請求項7の表示装置は、半導体発光素子が窒化ガリウム系半導体の六方晶からなり、少なくとも(1,−1,0,1)面に平行な活性層すなわち発光領域を備えている装置である。このような表示装置は窒化ガリウム系半導体の(0,0,0,1)面に平行な活性層の発光効率が高いこと、更には(1,−1,0,1)面に設ける電極面を反射面とすることが可能であり、優れた発光性能を示す。

【0013】

請求項7に従属する請求項8の表示装置は、半導体発光素子が、成長の基板面上で、(0,0,0,1)面を下端面とし(1,−1,0,1)面およびこれと等価な面を傾斜面として、六角錐形状または六角錐台形状に選択的に結晶成長された窒化ガリウム系半導体からなり、(1,−1,0,1)面およびこれと等価な面に平行な活性層を備えている装置である。このような表示装置は窒化ガリウム系半導体の(1,−1,0,1)面に平行な活性層の発光効率が高いこと、更には(1,−1,0,1)面に設ける電極面を反射面とすることが可能であり、発光を下端面側へ集中させ、高輝度の表示装置を与える。

請求項1に従属する請求項9の表示装置は、単色の半導体発光素子、またはそれぞれ異なる色を発光する複数種の半導体発光素子の組み合わせを配置した画像表示装置または照明装置である。このような表示装置は明瞭な、または明僚かつ多彩な画像または照明を提供する。

【0014】

請求項1に従属する請求項10の表示装置は、半導体発光素子が第一導電型半導体層と活性層と第二導電型半導体層を順次積層し、更に第二導電型半導体層に上端部電極が形成されたものであり、かつ上端部電極と導体膜が同一種の金属で形成されている装置である。このような表示装置は、導体膜から形成される引き出し電極と上端部電極とが強固かつ安定に接合されたものとなる。

請求項1に従属する請求項11の表示装置は、半導体発光素子が第一導電型半導体層と活性層と第二導電型半導体層を順次積層したものであり、絶縁層が薄層化されて露出される第二導電型半導体層と絶縁層とからなる面に導体膜を形成させることにより、上端部電極と導体膜が一体的に形成されたものである。このような表示装置は、第二導電型半導体層への上端部電極の取り付けと導体膜の形成とが同時に行われて工程数が削減されていることから低いコストである。

【0015】

請求項1に従属する請求項12の表示装置は、半導体発光素子が第一導電型半導体層と活性層と第二導電型半導体層を順次積層し、更に第二導電型半導体層に所定厚さのコンタクトメタル層を介して上端部電極を形成させたものであり、かつ上端部電極と導体膜が同一種の金属で形成されている装置である。このような表示装置は、導体膜から形成される引き出し電極と上端部電極とが強固かつ安定に接合されたものとなるほか、上端部電極の反射率が大であり反射光が発光の取り出し方向へ集められることから、発光効率が高い。

請求項1に従属する請求項13の表示装置は、半導体発光素子が第一導電型半導体層と活性層と第二導電型半導体層を順次積層し、更に第二導電型半導体層に所定厚さのコンタクトメタル層を形成させたものであり、絶縁層が薄層化されて露出されるコンタクトメタル層と絶縁層とからなる面に導体膜を形成させることにより、上端部電極と導体膜が一体的に形成された装置である。このような表示装置は、上端部電極の反射率が大であり反射光が発光の取り出し方向へ集められることから発光効率が高く、更には、上端部電極と導体膜が一体的に形成されていることから工程数が削減されており、製造コストを低下させる。

【0016】

請求項14の表示装置の製造方法は、複数の半導体発光素子を基体面に配置して取り付ける表示装置の製造方法において、半導体発光素子を絶縁層で埋め込む工程と、絶縁層を選択的または非選択的に薄層化させて半導体発光素子の上端部を露出させる工程と、露出された上端部に導体膜を形成させる工程とによって半導体発光素子の上端部電極を絶縁層の上面に引き出す製造方法である。このような表示装置の製造方法は、半導体発光素子を被覆する絶縁層にコンタクトホールを設けないので、コンタクトホールと半導体発光素子の上端部電極との位置ずれやコンタクトホール内での接続不良とは無縁であり、半導体発光素子の上端部電極を簡易かつ確実に絶縁層の上面へ引き出し得る。

【0017】

請求項14に従属する請求項15の表示装置の製造方法は、エポキシ樹脂、ポリイミド樹脂、合成ゴムを含む塗膜形成の可能な高分子化合物、または塗膜形成の可能なガラスを塗布して絶縁層を形成する方法である。このような表示装置の製造方法は、基体面の面積が大である場合にも簡易に絶縁層を形成させることができる。

請求項14に従属する請求項16の表示装置の製造方法は、CVD法またはスパッタリング法によって酸化ケイ素または窒化ケイ素を堆積させて絶縁層を形成する方法である。このような表示装置の製造方法は、これら無機物の絶縁層により耐熱温度の高い製造装置を与える。

【0018】

請求項14に従属する請求項17の表示装置の製造方法は、絶縁層を酸素プラズマ雰囲気下のドライエッチング法、化学的機械的研摩法、または両者の組み合わせによって薄層化する方法である。このような表示装置の製造方法は、絶縁層の材料種や薄層化の状況に応じて最も適切な方法を採用することができる。

請求項14に従属する請求項18の表示装置の製造方法は、半導体発光素子として、発光領域から基体面上の下端面へ向かう方向が主たる発光方向であり、発光領域より上部に下方への反射面を有するものを使用する方法である。このような表示装置の製造方法は、半導体発光素子の反射面によって発光を効果的に下端面へ向かわせ表示装置の輝度を高める。

【0019】

請求項18に従属する請求項19の表示装置の製造方法は、半導体発光素子として、角錐形状または角錐台形状に形成されており、それらの有する面のうち少なくとも傾斜面の何れか一面が反射面とされているものを使用する製造方法である。このような表示装置の製造方法は、多角錐または多角錐台の傾斜面、および多角錐台にあっては上面も反射面として半導体発光素子の発光を下端面側へ集中させることができる。

請求項18に従属する請求項20の表示装置の製造方法は、半導体発光素子として、窒化ガリウム系半導体の六方晶からなり、(1,−1,0,1)面に平行な活性層を備えたものを使用する製造方法である。このような表示装置の製造方法は、窒化ガリウム系半導体発光素子の(1,−1,0,1)面に平行な活性層が高い発光効率を示すことから、優れた発光性能の表示装置を与える。

【0020】

請求項20に従属する請求項21の表示装置の製造方法は、半導体発光素子として、成長の基板面上で、(0,0,0,1)面を下端面とし、(1,−1,0,1)面およびこれと等価な面を傾斜面として六角錐または六角錐台形状に選択的に結晶成長された窒化ガリウム系半導体からなり、(1,−1,0,1)面およびこれと等価な面に平行な活性層を備えているものを使用する製造方法である。このような表示装置の製造方法は、活性層が高い発光効率を示すこと、(1,−1,0,1)面に設ける電極面が反射面となって発光を下端面側へ集中させることから、特に輝度の高い表示装置を与える。

【0021】

請求項14に従属する請求項22の表示装置の製造方法は、半導体素子として、第一導電型半導体層と活性層と第二導電型半導体層が順次積層され、更に第二導電型半導体層に上端部電極が形成されたものを使用し、導体膜を上端部電極と同一種の金属によって形成する方法である。このような表示装置の製造方法は、導体膜から形成される引き出し電極と上端部電極を強固かつ安定に接合させる。

請求項14に従属する請求項23の表示装置の製造方法は、半導体素子として、第一導電型半導体層と活性層と第二導電型半導体層が順次積層されたものを使用し、絶縁層を薄層化させて露出される第二導電型半導体層と絶縁層とからなる面に導体膜を形成させることにより、上端部電極と導体膜を一体的に形成する方法である。このような表示装置の製造方法は、上端部電極と導体膜とを一体とし、第二導電型半導体層への上端部電極の取り付けと導体膜の形成とを同時に行うことから工程数が削減され、低コストの表示装置を与える。

【0022】

請求項14に従属する請求項24の表示装置の製造方法は、半導体素子として、第一導電型半導体層と活性層と第二導電型半導体層が順次積層され、更に第二導電型半導体層に所定厚さのコンタクトメタル層を介して上端部電極が形成されたものを使用し、導体膜を上端部電極と同一種の金属によって形成する方法である。このような表示装置の製造方法は、上端部電極の反射率が大であり、反射光が発光の取り出し方向へ集められて発光効率を高めるほか、導体膜から形成される引き出し電極と上端部電極とを強固かつ安定に接合させる。

【0023】

請求項14に従属する請求項25の表示装置の製造方法は、半導体素子として、第一導電型半導体層と活性層と第二導電型半導体層が順次積層され、更にコンタクトメタル層が形成されたものを使用し、絶縁膜が薄層化されて露出するコンタクトメタル層と絶縁層とからなる面に導体膜を形成させることにより、上端部電極と導体膜を一体的に形成する方法である。このような表示装置の製造方法は、上端部電極の反射率が大であり反射光が発光の取り出し方向へ集められることから表示装置の発光効率を高くし、更には、上端部電極と導体膜とを一体とし、第二導電型半導体層への上端部電極の取り付けと導体膜の形成とを同時に行うことから工程数が削減され、表示装置を低コスト化させる。

【0024】

【発明の実施の形態】

本発明の表示装置およびその製造方法は、上述したように、複数の半導体発光素子が基体面に配置され取り付けられた表示装置において、半導体発光素子を埋め込んだ絶縁層が選択的または非選択的に薄層化されて露出される半導体発光素子の上端部に導体膜が形成されて、半導体発光素子の上端部電極が絶縁層の上面に引き出されている表示装置およびその製造方法である。

【0025】

半導体発光素子は、それを覆う絶縁層を薄層化させることによって露出される上端部に導体膜を形成させて上端部電極を絶縁層の上面に引き出すものである限りにおいて、半導体発光素子の製造方法や材料構成、結晶構造は特に限定されない。すなわち、半導体発光素子は発光ダイオードまたは半導体レーザの一つの原料となる化合物半導体ウェーハからダイシングされる例えば300μmサイズの微少な半導体チップであってもよく、またサファイアのような成長の基板上で選択的に結晶成長させた10〜100μmサイズの極く微少な半導体であってもよい。

【0026】

半導体発光素子を基板上で選択的に結晶成長させる場合には、基板面は半導体発光素子と同様な格子定数を持つものであることが好ましいが、このことは必須の要件ではない。通常はサファイア(Al2 O3 )の(0,0,0,1)面が成長に使用されるが、サファイアとGaN系半導体とでは格子定数が10%以上異なるほか熱膨張係数も異なり、界面でクラックを生じ易い。これを回避するために、サファイアの(0,0,0,1)面に、一旦、低温度、例えば500℃でGaNを極薄に形成させてバッファ−層とし、その上へ高温度、例えば1000℃でGaNを結晶成長させることが好ましい。バッファ−層には窒化アルミニウム(AlN)も使用され得る。サファイアは上記の(0,0,0,1)面以外の面、例えば(1,−1,0,1)面で結晶成長させることができる。またサファイア以外に、シリコンカーバイド(SiC)、窒化ガリウム(GaN)、シリコン(Si)、砒化ガリウム(GaAs)等も成長の基板として使用されるが、結晶成長が可能であればこれら以外の基板を使用してもよい。

【0027】

半導体発光素子が透明な基体面に固定され、上端部から基体面側へ向う方向を主たる発光方向とする場合、半導体発光素子の形状によって、基体面側、すなわち半導体発光素子の下端面側への輝度を向上させることが可能である。半導体発光素子の発光領域である活性層からの発光のうち、発光領域から上方へ向かう光は上端部の電極面等を反射面として下端面側へ向かう光とし得るが、下端面と垂直な側面へ向かう光は側面で反射させても下端面側へ向かう光とはなりにくい。従って、半導体発光素子は発光領域より上部に下端面と鋭角の反射面、中でも下端面となす角度が45±20度の範囲内にある傾斜面を有するものであることが望ましく、このような傾斜面に反射面を設けることにより側方ヘ向かう光を反射させて効果的に下端面の方へ向かう光とすることができる。なお、傾斜面が下端面となす角度を上記の範囲外とした場合には、側方へ向かう光を反射させても下端面へ向かう光量はそれ程には増大しないので高輝度化の効果は認め難くなる。

【0028】

上記の傾斜面は、片流れ屋根的傾斜面、切妻屋根的傾斜面、寄せ棟屋根的傾斜面であってもよい。更には半導体発光素子が角錐形状または角錐台形状を有するものであることが好ましい。角錐、角錐台の傾斜面、および角錐台にあっては上面も反射面とすることにより、半導体発光素子の発光を一層効果的に下端面側へ向けることができる。ここに言う角錐または角錐台には、三角錐、四角錐、五角錐、六角錐から円錐に近似した多角錐に至る各種の角錐と、それらに対応する角錐台が含まれる。そのほか、上記の下端面と鋭角の傾斜面を有するものとして、上記の傾斜面を窪みの傾斜面とするカルデラ状の窪みを上端部に有する半導体発光素子であってもよい。そして、上記のような傾斜面を有する半導体発光素子は選択的な結晶成長によって自然発生的に得られるものであってもよく、選択的結晶成長の後に面出し加工を施したものであってもよい。上記のような傾斜面を得る加工手段としてイオンビームやレーザビームを使用することができる。また、化合物半導体ウェーハから微小な半導体発光素子をダイシングして切り出す時に傾斜面を与えたものであってもよい。

【0029】

半導体発光素子として使用する化合物半導体のうち、緑色に発光するリン化ガリウム(GaP)や、赤色に発光するヒ化リン化ガリウム(GaAsP)、ヒ化アルミニウムガリウム(AlGaAs)等は立方晶に属し、選択的に結晶成長させた場合に六面体となり、上記のような下端面に対する傾斜面を持たないので、後加工して傾斜面を設けて反射面とすることは好ましい選択である。他方、青色に発光する窒化ガリウム系半導体は六方晶に属し、成長の基板面に(0,0,0,1)面を下端面として選択的に結晶成長された窒化ガリウム系半導体は下端面とほぼ50度の角度に傾斜する(1,−1,0,1)面とこれに等価な面を持つ六角錐形状または六角錐台形状に成長するが、(1,−1,0,1)面に平行な活性層を設けることにより優れた発光性を示し、かつ(1,−1,0,1)面に設ける電極面を光の反射面とすることにより、光は下端面側へ向けて効果的に集中され、極めて高輝度の半導体発光素子を与える。なお、上記した窒化ガリウム(GaN)はガリウム(Ga)と同族のアルミニウム(Al)、インジウム(In)、タリウム(Tl)が窒化ガリウム(GaN)内のGaの一部を置換するものであってもよい。また、下端面である(0,0,0,1)面に対する(1,−1,0,1)面の角度は±5度の範囲内で同等の発光性を示す。

【0030】

化合物半導体ウェーハからダイシングされたチップ状の微小な半導体発光素子、または成長の基板面で選択的に結晶成長された極く微小な半導体発光素子を基体面に配置し取り付けるために、半導体発光素子を覆うように基体の全面に絶縁層を形成させる。絶縁層としては、CVD法またはスパッタリング法によって、酸化ケイ素または窒化ケイ素を成膜させることにより耐熱性の良好な表示装置が得られる。酸化ケイ素はPSG(フォスフォシリケートガラス)、BSG(ボロシリケートガラス)、またはBPSG(ボロフォスフォシリケートガラス)であってもよい。これらの無機物を絶縁層として使用する場合、得られる半導体発光素子は耐熱性に優れたものとなるが、適用に高温を要することが多い。

【0031】

また塗布法によって、塗膜形成の可能な高分子化合物または塗膜形成の可能なガラスによって絶縁層を形成させてもよい。高分子化合物としては、ポリイミド樹脂、エポキシ樹脂、塩化ビニル系共重合樹脂、含フッ素樹脂、ポリカーボネート樹脂、ポリウレタン樹脂や、各種合成ゴムが含まれる。また、ガラスの塗膜を形成させてもよい。塗膜形成の可能なガラス材料としては半導体装置の製造時にスピンコートされているスピンオングラスを例示し得る。塗布による方法はCVD法やスパッタリング法と比較して基板面の面積が大である場合にも容易に絶縁層を形成することができる。

【0032】

絶縁層で半導体発光素子を埋め込んだ後、絶縁層を選択的または非選択的に薄層化させて半導体発光素子の上端部を露出させる。この薄層化は、ドライエッチングおよび化学的機械的研摩をそれぞれが単独で、またはこれらを組み合わせて好適に行われる。この時、絶縁層の薄層化に伴って露出される半導体発光素子は残し絶縁層のみを薄層化させる選択的な薄層化を施すか、または半導体発光素子と共に絶縁層を薄層化させる非選択的な薄層化を施す。非選択的な薄層化を行えば当然なことながら半導体発光素子と絶縁層とは同一平面になる。非選択的薄層化には化学的機械的研摩法が採用されるが、勿論、これ以外の方法で施してもよい。

【0033】

ドライエッチングは酸素プラズマの雰囲気下に行うことが望ましい。勿論、アルゴンガスのような不活性ガスを共存させてもよい。すなわち、絶縁層に高分子材料を使用した場合には、酸素プラズマは直接に高分子材料と反応して燃焼、ガス化させるので、エッチャントガスであるフッ素化炭素を使用せずとも、薄層化が可能である。また、絶縁層にケイ素化合物を使用した場合には、酸素プラズマはエッチャントガスと反応し、ケイ素と結合し易いフッ素ラジカルの発生を助長する。化学的機械的研摩法は基板の薄板化に広く実施されている方法をそのまま適用することができる。

【0034】

なお、高分子化合物やガラスを塗布した後、固化させる前に過剰な塗液をスキージやドクターブレード等で掻き取ってもよい。また掻き取ったものは、固化後に絶縁層の薄層化が不要である場合もあるが、半導体発光素子の上端部には絶縁層が箔状に残るので、固化後にドライエッチングして箔状の絶縁層を除去することが必要である。

【0035】

絶縁層を選択的または非選択的に薄層化させて半導体発光素子の上端部を露出させた後に導体膜を形成させるが、導体膜には半導体発光素子の上端部電極の金属と同一種の金属を使用することが望ましい。これは異種金属を重ねる場合には合金の境界面での合金の形成し易さ、熱膨張係数の差などへの考慮を要せず、上端部電極と導体膜との確実な接合を得ることが出来るからである。

【0036】

また、導体膜の形成方法として、半導体発光素子の第二導電型半導体(p型半導体)層に上端部電極を設けることなく絶縁層に埋め込み、同様な手順を経て露出される第二導電型半導体層に対して、例えばAl膜を形成させることにより、上端部電極(p電極)と導体膜とを一体的に形成させてもよく工程を簡略化させ得る。Al膜を形成させる前に第二導電型半導体層の上にオーミックコンタクトを得るためのメタル層を設けることにより一層好ましい結果を与える。

【0037】

また、青色に発光する窒化ガリウム系半導体発光素子は、例えば第一導電型半導体としてのn型半導体に活性層、第二導電型半導体としてのp型半導体が順次積層された構成を有しており、このp型半導体に上端部電極(p電極)、n型半導体に下端部電極(n電極)が取り付けられ、活性層に電流が注入されて発生する光が取り出される。このような半導体発光素子は、活性層から下端の透明な基体側へ向かう光に、活性層から上端部へ向かう光をp電極との界面で反射させて加えることができるという利点がある。なお、p型半導体とp電極との間にオーミック接触を得るべくコンタクトメタル層を介在させることが行われる。勿論、n型半導体とn電極との間にコンタクトメタル層を介在させることも行われる。

【0038】

しかし、活性層から上端部へ向かう光をp電極との界面で反射させる場合には、コンタクトメタル層の厚さを大にすると十分な反射率が得られないということが見い出された。すなわち、半導体発光素子にコンタクトメタル層を設ける場合にはNi、Co、またはSbによるメタル層を光の侵入長もしくは侵入長以下の厚さに形成させることによって反射率の向上することが認められたのである。具体的にはコンタクトメタル層を20nm以下の厚さに形成させることによって反射率の向上が認められ、一層効果的には10nm以下とすることが好ましく、5nm以下とすることが更に好ましく、1nmの厚さであっても有効なことが確認されている。従って本発明で使用する半導体発光素子は第二導電型半導体層に上記のような厚さの制限されたコンタクトメタル層を介して上端部電極が取り付けられているものを含む。

【0039】

図14は本発明において使用される窒化ガリウム系半導体発光素子の一例の断面図である。この半導体発光素子51は、GaN系化合物半導体を積層して形成した発光部を有しており、図示を省略した透明なサファイアの基体上に、GaNバッファ層を介してSiがドープされたn型窒化ガリウム(GaN:Si)層14、光を発生させるInGaN活性層15、Mgがドープされたp型窒化ガリウム(Ga:Mg)層16とが積層された構造を有している。Siがドープされたn型GaN層14は第一導電型クラッド層として機能し、Mgがドープされたp型GaN層16は第二導電型クラッド層として機能して、本素子はダブルヘテロ構造となっている。

【0040】

第二導電型クラッド層であるp型GaN層16には、更にオーミック接触を図るためのコンタクトメタル層であるNi層17が形成されており、このNi層17の厚さは、後述するように活性層15で発生する光の侵入長もしくは侵入長以下の厚さとされ、一例として厚さ約10nmのものが使用される。このNi層17上に形成されるp電極18は例えばAl、Agからなる薄膜であり、コンタクトメタル層であるNi層17を透過した光はp電極18の界面で反射する。なお、p電極18は上述したAl、Agからなる薄膜のほか、これらのAl、Agの上にAuやPtなどの金属層を積層した構造であっても良い。n型GaN半導体からなる平板状の下地部12にもその下端面に、またはマスク13の一部を開口して電極が設けられるが図14では図示を省略している。

【0041】

図15は図14の符号Eの□印で示す部分の拡大断面図である。図15に示すように、窒化ガリウム系半導体発光素子51はInGaN活性層15をそれぞれクラッド層であるn型GaN層14とp型GaN層16の間に介在させたダブルヘテロ構造を有し、そのp型GaN層16の上側に、オーミック接触を図るコンタクトメタル層であるNi層17が形成され、更にNi層17の上にAlもしくはAgからなるp電極18が形成されている。このNi層17の厚さtは、活性層15で発生する光の侵入長λもしくはこれ以下とされ、例えば略約10nmとされるが、発生する光に応じて厚さtを変えることもでき、更には蒸着法、メッキ法などによって形成される際の膜質などに応じて変えることのできる寸法である。光が金属表面で反射する場合、エネルギーを有する電磁波としての光は、金属表面よりも侵入長と称される長さλだけ金属表面から侵入し、完全反射の場合にはフォノン相互作用によって同じエネルギーを受取って反射をする。一方、オーミックコンタクトを達成するためには、極めて薄い膜でも十分であり、本件発明者が行った実験結果からは、例えばNi層17の厚さtが1nmというように極めて薄いものであっても発光動作が確認されている。このことから、Ni層17の厚さtは、活性層15で発生する光の侵入長λもしくはそれ以下の厚さとすることで、その上のp型電極18での反射効率を高めることができる。

【0042】

図16はGaN層、Ni層、Ag層(電極)の積層構造に対して、Ni層の厚さtを変化させながら発光した光を反射させ、その反射率を算出したものである。図16に示すように、Ni層の厚さtが薄い方が反射率が高くなり、Ni層の厚さが増加するに従って反射率が低くなって行く傾向にある。そして20nmを超える厚さの場合、その反射率は相対値で0.4以下であり、少なくとも0.4以上の反射率を得る場合にはNi層の厚さtを20nm以下とすることが必要であり、好ましくは10nm以下とされる。更に反射率として0.6やそれ以上の値を得る場合にはNi層の厚さtを5nm以下とすることが望ましい。そして同様な事実はGaN層、Ni層、Al層(電極)の積層構造に対して、Ni層の厚さを変化させた場合にも認められており、0.5以上の反射率を得るにはNi層の厚さを20nm以下とすることが必要であると認められている。

【0043】

上述したように、半導体発光素子である発光ダイオードには、材料によってそれぞれ赤色(R)、緑色(G)、青色(B)に発光するものがあるので、これらの発光ダイオードを組み合わせて画素を構成し、輝度の高いフルカラーの画像表示装置とすることができる。勿論、単色、例えば赤色の発光ダイオードのみを二次元に配置し、プログラムされたスイッチングによって画像の形状を時間的に変化させるような表示装置とすることもできる。上記の発光ダイオードに共振ミラーを設けることにより半導体レーザとすることは容易であるので、単色または三原色を組み合わせた半導体レーザによる照明装置や道路標識を製造することも可能である。

【0044】

【実施例】

次に、本発明の表示装置およびその製造方法を実施例により図面を参照して具体的に説明する。

【0045】

(実施例1)

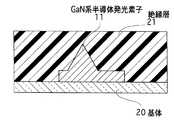

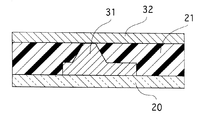

図1から図4までは表示装置に使用される半導体発光素子の製造過程を示す断面図である。図1は六角錐形状に結晶成長された半導体発光素子である発光ダイオード11を基板20の上面に配置して埋め込むように絶縁層21が設けられた状態を示す。

【0046】

この発光ダイオード11の詳細は図5のAの断面図および図5のBの平面図に示す。図示を省略したサファイア基板の(0,0,0,1)面上のSiO2 マスクの開口部に温度500℃で極薄のGaNバッファー層を成長させ、続いてシリコンをドーピングしたn型窒化ガリウム(GaN:Si)を1000℃で平板状に成長させて図5のAに示す下地部12とし、更にその上へ設けたSiO2 マスク13の開口部に温度1000℃で結晶成長させることにより六角錐形状のn型(GaN:Si)14が得られる。そして、この六角錐の傾斜面である(1,−1,0,1)面およびこれと等価な傾斜面に、成長温度を下げてInGaNからなる活性層15を設け、更にその上へマグネシウムをドーピングしたp型窒化ガリウム(GaN:Mg)16を成長させた後、p型窒化ガリウム層16の表面に蒸着してp電極18を設けたものである。すなわち前述した図14におけるコンタクトメタル層17は設けられていないものである。n型窒化ガリウム半導体からなる平板状の下地部12にも、その下端面に、またはマスク13の一部を開口して電極が設けられるが図5では図示を省略している。

【0047】

図1は上記のようにして形成されたGaN系発光ダイオード11を基板20上に移し、エポキシ樹脂で覆うように絶縁層21を設けて固定したものを簡略化して図示したものである。

【0048】

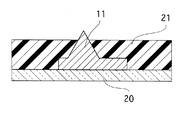

図2は図1のエポキシ樹脂からなる絶縁層21を酸素プラズマ雰囲気のドライエッチングによって選択的にエッチバックすることにより、発光ダイオード11の上端部が露出され、図5に示した発光ダイオード11の上端部電極18が露出された状態を示している。そして、図3はエッチバックされた絶縁層21の表面にAlからなる導体膜22を形成させたものであるが、この時、発光ダイオード11の上端部の上方では当然のことながら導体膜22は突出した形状となる。

【0049】

図4はリソグラフィによって導体膜22の要部を残して引き出し電極23とし、不要部は除去したものである。図4では示していないが、n型(GaN:Si)半導体の下地部12からの引き出し電極は、予め引き出し電極が設けられた基板20を使用してもよく、また基板20に引き出し電極が予め設けられていない場合には、基板20と分離した後、六角錐形状の下端面の周縁部に引き出し電極を設けるか、下端面全体を引き出し用透明電極で覆ってから最終的な基板に接合することができる。勿論、これら以外の方法で引き出してもよい。また、上記において、Ni/Auのp電極18に対して形成させたAlの導体膜22に代えて、p電極18のAuと同一のAuからなる導体膜22を形成させたが、その結果、p電極18と一層確実に接合された引き出し電極23が得られた。

【0050】

(実施例2)

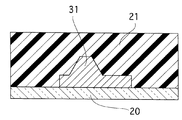

実施例1では六角錐形状の窒化ガリウム系半導体を使用する場合を説明したが、本実施例では、図6から図9によって、表示装置に使用される六角錐台形状の窒化ガリウム系半導体を使用する場合について説明する。すなわち、窒化ガリウム系半導体は結晶成長に十分な時間が与えられなかった場合には六角錐台形状となるが、図6はこのような六角錐台形状の窒化ガリウム系半導体31を絶縁層21で被覆して基板20上に固定したものを簡略化して示した図であり、その窒化ガリウム系半導体31の構成は、シリコンをドープしたn型窒化ガリウム(GaN:Si)を六角錐台形状に選択的に結晶成長させた後、六角錐台の上面である(0,0,0,1)面および傾斜面である(1,−1,0,1)面に、InGaNの活性層、更にその上へマグネシウムをドーピングしたp型窒化ガリウムを成長させ、上端部のp型窒化ガリウム半導体の表面にはコンタクトメタル層として略10nm厚さのNi層を蒸着し、その上へ略100nm厚さのAl層を蒸着して上端部電極としてのp電極を設けたものである。。そして、上記のようにして形成されたGaN系発光ダイオード31を覆うようにエポキシ樹脂を塗布して絶縁層21を設けることにより基板20面上に固定したものである。

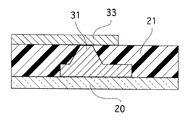

【0051】

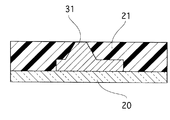

図7は絶縁層21を実施例1と同様に選択的にエッチバックすることによって六角錐台形状の窒化ガリウム系半導体31の上面である(0,0,0,1)面のp電極のAl層が露出された状態を示す。そして図8はエッチバックした面の全面にp電極と同一のAlによる導体膜32を形成させたものであり、図9はリソグラフィによって導体膜32の要部を残して引き出し電極33とし、不要部は除去したものである。図9にもn型電極の引き出しは示されていないが、実施例1の場合と同様に行われる。

【0052】

(実施例3)

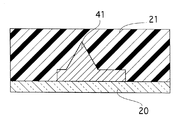

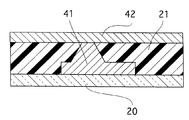

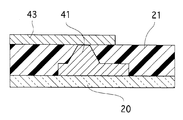

実施例1と実施例2においては絶縁層21のみを選択的に薄膜化させる場合を説明したが、実施例3においては絶縁層21を非選択的に半導体発光素子と共に薄層化させる場合を図10から図13までによって説明する。図10は実施例1における図1と同様な図であるが、使用されている六角錐形状のGaN系発光ダイオード41は図5に示したものと異なりp電極18の形成されていないものが使用されている。すなわち、図10はこのようなGaN系発光ダイオード41を基板20上においてエポキシ樹脂からなる絶縁層21で被覆して固定した状態を示す。そして図11は、図10の状態において絶縁層21と共にGaN系発光ダイオード41も研削する非選択的な化学的機械的研摩を施し薄膜化させることによって、絶縁層21の研削面とGaN系発光ダイオード41の研削面とを同一面としたものである。この時点において発光ダイオード41の研削面の外周部分はp型半導体の研削面となっている。続く図12は図11の研削面にAlを蒸着することによりp電極を形成させると同時に一体的に導体膜42を形成させたものである。この時、コンタクトメタル層を形成させてから、Alの導体膜42を形成させてもよいことは言うまでもない。図13はリソグラフィによって導体膜42の要部を残して引き出し電極43とし、不要部は除去したものである。図13には示していないが、n型電極の引き出しは実施例1の場合と同様に行われる。

【0053】

以上、本発明の表示装置およびその製造方法を実施例によって説明したが、勿論、本発明はこれらに限られることなく、本発明の技術的思想に基づいて種々の変形が可能である。

【0054】

例えば本実施例においては、サファイアの(0,0,0,1)面に結晶成長され、(0,0,0,1)面を下端面とし、(1,−1,0,1)面を傾斜面とした六角錐形状または六角錐台形状のGaN系発光ダイオード11を例示したが、これ以外のGaN系発光ダイオード、例えばサファイアの(0,0,0,1)面で選択的に結晶成長させて得られる六角柱形状のGaN系半導体や、裏返しにした舟底形で(1,1,−2,2)面と(1,−1,0,1)面を有する六方晶のGaN系半導体、更にはサファイアの(1,−1,0,1)面に結晶成長される六方晶のGaN系半導体から得られる半導体発光素子についても、絶縁層で被覆した後に絶縁層を薄層化させることによってコンタクトホールを設けることなく上端部の電極を引き出すことができる。

【0055】

また本実施例においては、六方晶となるGaN系半導体による青色の発光素子を例示したが、それ以外の化合物半導体による半導体発光素子についても本発明を適用することができる。例えば緑色に発光するリン化ガリウム(GaP)や赤色に発光するヒ化リン化ガリウム(GaAsP)、ヒ化アルミニウムガリウム(AlGaAs)は何れも立方晶に属し、成長の基板上で選択的に結晶成長させると六面体として得られるが、これらから得られる半導体発光素子についても、絶縁層で被覆した後に絶縁層を薄層化させることによってコンタクトホールを設けることなく上端部の電極を引き出すことができる。従って、青色を発光する窒素ガリウムの半導体発光素子を含めた三原色の半導体発光素子を組み合わせてフルカラーの表示装置を製造することができる。

【0056】

また本実施例においては、図5に示したように、p型半導体16が上側、n型半導体14が下側となっているGaN系半導体発光素子11を示したが、これらの位置を逆にした半導体発光素子であってもよい。

また本実施例においては、半導体発光素子として発光ダイオードを例示したが、周知のように、発光ダイオードに共振器を設けることによって半導体レーザが得られるので、発光ダイオードに代えて半導体レーザによる照明装置を製造することができる。

【0057】

【発明の効果】

半発明の表示装置およびその製造方法は上述したような形態で実施され、次に述べるような効果を奏する。

【0058】

請求項1の表示装置によれば、絶縁層で被覆され埋め込まれている半導体発光素子の上端部電極を引き出すために、コンタクトホールを穿設せず、絶縁層を選択的または非選択的に薄層化させ、露出される半導体発光素子の上端部に導体膜を形成して上端部電極を引き出すので、コンタクトホールを設ける場合におけるコンタクトホールと上端部電極との位置ずれや、コンタクトホール内での接続不良とは無縁であり、引き出し電極を簡易かつ確実に設けることができる。

【0059】

請求項2の表示装置によれば、塗膜形成の可能な高分子化合物または塗膜形成の可能なガラスを絶縁層として半導体発光素子を被覆し埋め込んでいるので、半導体発光装置を配置する基体の面積が大である場合にも、絶縁層が簡易に形成され低コストである。

請求項3の表示装置によれば、酸化ケイ素または窒化ケイ素からなる絶縁層が形成されているので、良好な耐熱性を示す。

請求項4の表示装置によれば、半導体発光素子を露出させる絶縁層の薄膜化が酸素プラズマ雰囲気下のドライエッチング、化学的機械的研摩、または両者の組み合わせが、絶縁層の材料種、薄膜化の状況に応じて合理的に採用されるので低コストである。

【0060】

請求項5の表示装置によれば、基体面に固定された半導体発光素子の発光方向が上端部から下端面へ向かう方向であり、発光領域より上部に下方への反射面を持っているので、発光が下端面へ向う方向へ集められる。

請求項6の表示装置によれば、半導体発光素子が角錐形状または角錐台形状に形成されており、それらの有する面のうち少なくとも傾斜面の何れか一面が反射面とされているので、発光が発光方向へ集められ高い輝度を示す。

請求項7の表示装置によれば、半導体発光素子が窒化ガリウム系半導体からなり、少なくとも(1,−1,0,1)面に平行な発光効率の高い活性層に加えて(1,−1,0,1)面に設ける電極面を反射面とすることにより、優れた発光性能を示す。

【0061】

請求項8の表示装置によれば、半導体発光素子が成長の基板面上で、(0,0,0,1)面を下端面とし(1,−1,0,1)面およびこれと等価な面を傾斜面として六角錐形状または六角錐台形状に選択的に結晶成長された窒化ガリウム系半導体からなり、(1,−1,0,1)面およびこれと等価な面に平行な活性層を備えているので、発光効率の高い活性層からの光を下端面側へ集中させることでき、高輝度の表示を与える。

請求項9の表示装置によれば、単色の半導体発光素子、またはそれぞれ異なる色に発光する複数種の半導体発光素子の組み合わせが配置されているので、明僚な、または明瞭かつ多彩な画像表示または照明を提供する。

【0062】

請求項10の表示装置によれば、半導体発光素子の上端部電極と同一種の金属が導体膜の形成に使用されているので、導体膜から得られる引き出し電極は上端部電極と良好で安定な接合性を示す。

請求項11の表示装置によれば、半導体発光素子の露出された第二導電型半導体が露出された絶縁層の面に導体膜を形成させ、上端部電極と導体膜とを一体的に形成させるので工程数が削減され、それに応じて表示装置のコストを低下させる。

【0063】

請求項12の表示装置によれば、第二導電型半導体に所定厚さのコンタクトメタル層を介して上端部電極が形成されており、かつ上端部電極と同一種の金属が導体膜の形成に使用されているので、上端部電極面の反射率が大で反射光が発光の取り出し方向へ効果的に集められることから発光効率が高く、かつその引き出し電極は上端部電極と良好で安定な接合性を示す。

請求項13の表示装置によれば、第二導電型半導体に形成された所定厚さのコンタクトメタル層が露出された絶縁層の面に導体膜を形成させ、上端部電極と導体膜とを一体的に形成させるので、上端部電極の反射光が発光の取り出し方向へ集中されて表示装置の発光効率が高く、更には工程数が削減され低コストである。

【0064】

請求項14の表示装置の製造方法によれば、透明な基体面に配置した半導体発光素子を絶縁層で被覆して埋め込んだ後、絶縁層を選択的または非選択的に薄層化させて半導体発光素子の上端部を露出させることによって上端部電極を絶縁層の上面へ引き出し、通常的なコンタクトホールは設けないのでコンタクトホールに伴うトラブルを回避することができ、半導体発光素子の上端部電極を簡易かつ確実に引き出すことができる。

請求項15の表示装置の製造方法によれば、半導体発光素子を埋め込み基体面に固定する絶縁層を塗膜形成の可能な高分子化合物、または塗膜生成の可能なガラスによって形成させるので、基体面の面積が大である場合にも絶縁膜を簡易かつ低コストで形成させる。

請求項16の表示装置の製造方法によれば、半導体発光素子を埋め込み基体面に固定する絶縁層をCVDまたはスパッタリングによる酸化ケイ素または窒化ケイ素によって形成させるので、耐熱性の良好な表示装置を提供する。

【0065】

請求項17の表示装置の製造方法によれば、半導体発光素子を露出させる絶縁層の薄膜化を酸素プラズマ雰囲気下のドライエッチング、化学的機械的研摩、または両者の組み合わせから、絶縁層の材料種、薄層化の状況に応じ適切な方法を選んで効果的に実施することができる。

請求項18の表示装置の製造方法によれば、半導体発光素子として、発光領域から下端面へ向かう方向を主たる発光方向とし、発光領域より上部に下方への反射面を有するものを使用するので、反射面によって発光を効果的に下端面へ向かわせ、表示装置の輝度を高める。

【0066】

請求項19の表示装置の製造方法によれば、半導体発光素子として、角錐形状または角錐台形状に形成され、それらの有する面のうち少なくとも傾斜面の何れか一面が反射面とされているものを使用するので、多角錐または多角錐台の傾斜面、多角錐台にあっては上面も反射面として、半導体発光素子の発光を下端面側へ向かわせることができる。

請求項20の表示装置の製造方法によれば、半導体発光素子として窒化ガリウムの六方晶からなり、(1,−1,0,1)面に平行な活性層を備えたものを使用するので、この活性層が高い発光効率を示すことから、(1,−1,0,1)面に設ける電極面を反射面として優れた発光性能の表示装置を与える。

【0067】

請求項21の表示装置の製造方法によれば、半導体発光素子として(0,0,0,1)面を下端面とし、(1,−1,0,1)面およびこれと等価な面からなる傾斜面として六角錐状または六角錐台形状に選択的に結晶成長された窒化ガリウム系半導体からなり、(1,−1,0,1)面およびこれと等価な面、すなわち6傾斜面に平行な活性層を備えたものを使用するので、この活性層が高い発光効率を示すことから、6傾斜面に設ける電極面を反射面として優れた発光性能の表示装置を与える。

【0068】

請求項22の表示装置の製造方法によれば、導体膜に上端部電極と同一種の金属が使用されているので、表示装置の導体膜から形成される引き出し電極は上端部電極と良好で安定な接合性を持つ。

請求項23の表示装置の製造方法によれば、上端部電極と導体膜とが一体的に形成されるので、工程が簡略化され低コストの表示装置となる。

【0069】

請求項24の表示装置の製造方法によれば、第二導電型半導体に所定厚さのコンタクトメタル層を介して上端部電極が形成された半導体発光素子が使用され、導体膜に上端部電極と同一種の金属が使用されるので、上端部電極の反射光が発光の取り出し方向へ集中されて発光効率が高く、更には導体膜から形成される引き出し電極が上端部電極と良好で安定な接合性を持つ表示装置を与える。

請求項25の表示装置の製造方法によれば、第二導電型半導体に所定厚さのコンタクトメタル層を介して上端部電極が形成され、上端部電極と導体膜が一体的に形成されるので、反射光を効果的に利用して発光効率が大であり、工程数が削減され低コストの表示装置を提供する。

【図面の簡単な説明】

【図1】図1から図4までは六角錐形状の半導体発光素子を埋め込んだ絶縁層を選択的にエッチバックして半導体発光素子に引き出し電極を設ける過程を示す断面図であり、図1は半導体発光素子が基体面上で絶縁層によって被覆、固定されている状態を示す断面図である。

【図2】図1の絶縁層を選択的にエッチバックして、半導体発光素子の上端部が露出された状態を示す。

【図3】図2のエッチバックされた絶縁層の上面に導体膜が形成された状態を示す。

【図4】図3の導体膜の要部を引き出し電極として残し不要部は取り除いた状態を示す。

【図5】六角錐形状に結晶成長されたGaN系半導体発光素子の詳細を示す図であり、Aは縦断面図、Bは平面図である。

【図6】図6から図9までは絶縁層を選択的にエッチバックして六角錐台形状の半導体発光素子に引き出し電極を設ける過程を示す断面図であり、図6は六角錐台形状の半導体発光素子が基体面上で絶縁層によって被覆、固定されている状態を示す断面図である。

【図7】図6の絶縁層を選択的にエッチバックして、六角錐台形状の半導体発光素子の上面が絶縁層の上面と同一面となって露出された状態を示す。

【図8】図7のエッチバックされた絶縁層および半導体発光素子の上面に導体膜が形成された状態を示す。

【図9】図8の導体膜の要部は引き出し電極として残し不要部は取り除いた状態を示す。

【図10】図10から図13までは、非選択的な薄層化によって六角錐形状の半導体発光素子に引き出し電極を設ける過程を示す断面図であり、図10は六角錐形状の半導体発光素子が基体面上で絶縁層によって被覆、固定されている状態を示す断面図である。

【図11】図10の絶縁層を非選択的に薄層化させて、六角錐形状の半導体発光素子の上端部が共に研削され、絶縁層の上面と同一面となって半導体発光素子が露出された状態を示す。

【図12】図11の薄層化された絶縁層および半導体発光素子の上面に導体膜が形成された状態を示す。

【図13】図12の導体膜の要部は引き出し電極として残し、不要部は取り除いた状態を示す。

【図14】本発明で使用される半導体発光素子の一例の断面図である。

【図15】図14において□印で示す部分の拡大図である。

【図16】GaN/Ni/Ag積層構造の反射率のNi層の厚さ依存性を計算して求めた特性図である。

【図17】半導体装置において絶縁層にコンタクトホ−ルを穿設して内部電極に引き出し電極を設ける過程を示す図であり、Aは事前の状態、Bはコンタクトホールを穿設した状態、Cは導体金属をスパッタリングして、コンタクトホ−ルの底面には付着するが内周面には充分に付着しにくい状態、Dはコンタクトホ−ルの開口部がほとんど塞がれて、接続不良および空洞を生じている状態を示す。

【図18】下層配線に上層配線を接続する場合のコンタクトホールに代わるコンタクト配線を示す図であり、Aは下層配線に対してコンタクト配線が電子ビーム蒸着された状態、Bは全体を覆って絶縁膜が形成された状態、Cは更にフォトレジストを形成させた状態、Dはエッチバックしてコンタクト配線の上端部を露出させた状態、Eは上層配線を形成させた状態を示す。

【図19】放電用陰極チップと蛍光材層、陽極層を近接した位置で配置する方法を示す図であり、Aは基板に設けられた陰極チップ、Bはその上へ絶縁層、陽極層を形成させた状態、Cは更に蛍光材層を形成させた状態、Dはその上へポリイミド樹脂層を形成させた後、ポリイミド樹脂層をエッチバックして蛍光材層の隆起部分を露呈させた状態、Eは露呈された蛍光材層の周囲のポリイミド樹脂層をマスクとして蛍光材層、陽極層、絶縁膜をエッチングして、陰極チップを露呈させた状態を示す。

【符号の説明】

11、31、41、51……GaN系半導体発光素子、15……活性層、16……p型半導体、17……コンタクトメタル、18……p電極、20……基体、21……絶縁層、22、32、42……導体膜、23、33、43……引き出し電極。

Claims (5)

- 複数の半導体発光素子を透明な基体面に配置して取り付ける表示装置の製造方法であって、

前記基体面に、前記半導体発光素子として、第一導電型半導体層、活性層、第二導電型半導体層、及び前記活性層で発生する光の侵入長以下の厚みを有するコンタクトメタル層を、この順番で積層させ、

前記半導体発光素子が埋め込まれるように、前記基体面に絶縁層を形成し、

前記絶縁層を選択的または非選択的に薄層化させて前記半導体発光素子の上端部に位置する前記コンタクトメタル層を露出させ、

前記露出されたコンタクトメタル層と前記絶縁層とからなる上面に導体膜を形成することで、前記第二導電型半導体層にオーミック接続される上端部電極とこれを前記上面に引き出す引き出し電極とを一体的に形成するとともに、前記活性層から前記上面へ向かう光を前記透明な基体側へ反射させる反射面を形成する

表示装置の製造方法。 - 請求項1に記載の表示装置の製造方法であって、

前記コンタクトメタル層は、Ni、Co、又はSbからなる

表示装置の製造方法。 - 請求項1又は2に記載の表示装置の製造方法であって、

前記コンタクトメタル層の厚みは、20nm以下である

表示装置の製造方法。 - 請求項3に記載の表示装置の製造方法であって、

前記コンタクトメタル層の厚みは、10nm以下である

表示装置の製造方法。 - 請求項4に記載の表示装置の製造方法であって、

前記コンタクトメタル層の厚みは、5nm以下である

表示装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001032688A JP4724924B2 (ja) | 2001-02-08 | 2001-02-08 | 表示装置の製造方法 |

| US10/071,909 US6825499B2 (en) | 2001-02-08 | 2002-02-07 | Display system and method of producing the same |

| US10/931,594 US7060542B2 (en) | 2001-02-08 | 2004-09-01 | Display system and method of producing the same |

| US11/093,444 US7250314B2 (en) | 2001-02-08 | 2005-03-30 | Display system and method of producing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001032688A JP4724924B2 (ja) | 2001-02-08 | 2001-02-08 | 表示装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002237618A JP2002237618A (ja) | 2002-08-23 |

| JP4724924B2 true JP4724924B2 (ja) | 2011-07-13 |

Family

ID=18896570

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001032688A Expired - Lifetime JP4724924B2 (ja) | 2001-02-08 | 2001-02-08 | 表示装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US6825499B2 (ja) |

| JP (1) | JP4724924B2 (ja) |

Families Citing this family (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7018531B2 (en) * | 2001-05-30 | 2006-03-28 | Honeywell International Inc. | Additive dispensing cartridge for an oil filter, and oil filter incorporating same |

| JP3996408B2 (ja) * | 2002-02-28 | 2007-10-24 | ローム株式会社 | 半導体発光素子およびその製造方法 |

| KR100481216B1 (ko) * | 2002-06-07 | 2005-04-08 | 엘지전자 주식회사 | 볼 그리드 어레이 패키지 및 그의 제조 방법 |

| TWI228323B (en) * | 2002-09-06 | 2005-02-21 | Sony Corp | Semiconductor light emitting device and its manufacturing method, integrated semiconductor light emitting device and manufacturing method thereof, image display device and its manufacturing method, illumination device and manufacturing method thereof |

| US6986693B2 (en) | 2003-03-26 | 2006-01-17 | Lucent Technologies Inc. | Group III-nitride layers with patterned surfaces |

| DE10335081A1 (de) * | 2003-07-31 | 2005-03-03 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung einer Vielzahl von optoelektronischen Halbleiterchips und optoeleketronischer Halbleiterchip |

| DE10335080A1 (de) * | 2003-07-31 | 2005-03-03 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung einer Vielzahl von optoelektronischen Halbleiterchips und optoelektronischer Halbleiterchip |

| TWI313071B (en) * | 2003-10-15 | 2009-08-01 | Epistar Corporatio | Light-emitting semiconductor device having enhanced brightness |

| TWI281758B (en) * | 2004-04-28 | 2007-05-21 | Showa Denko Kk | Transparent positive electrode |

| WO2006022399A1 (en) * | 2004-08-24 | 2006-03-02 | Showa Denko K.K. | Positive electrode for compound semiconductor light-emitting device |

| US20070205969A1 (en) | 2005-02-23 | 2007-09-06 | Pixtronix, Incorporated | Direct-view MEMS display devices and methods for generating images thereon |

| US8519945B2 (en) | 2006-01-06 | 2013-08-27 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US8482496B2 (en) | 2006-01-06 | 2013-07-09 | Pixtronix, Inc. | Circuits for controlling MEMS display apparatus on a transparent substrate |

| US9261694B2 (en) | 2005-02-23 | 2016-02-16 | Pixtronix, Inc. | Display apparatus and methods for manufacture thereof |

| US8159428B2 (en) | 2005-02-23 | 2012-04-17 | Pixtronix, Inc. | Display methods and apparatus |

| US8310442B2 (en) | 2005-02-23 | 2012-11-13 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US7616368B2 (en) | 2005-02-23 | 2009-11-10 | Pixtronix, Inc. | Light concentrating reflective display methods and apparatus |

| US9082353B2 (en) | 2010-01-05 | 2015-07-14 | Pixtronix, Inc. | Circuits for controlling display apparatus |

| US7999994B2 (en) | 2005-02-23 | 2011-08-16 | Pixtronix, Inc. | Display apparatus and methods for manufacture thereof |

| US9229222B2 (en) | 2005-02-23 | 2016-01-05 | Pixtronix, Inc. | Alignment methods in fluid-filled MEMS displays |

| US9158106B2 (en) | 2005-02-23 | 2015-10-13 | Pixtronix, Inc. | Display methods and apparatus |

| US20070034882A1 (en) * | 2005-08-15 | 2007-02-15 | Takayoshi Fujii | Semiconductor light-emitting device |

| US7544974B2 (en) | 2005-08-23 | 2009-06-09 | Showa Denko K.K. | Positive electrode for compound semiconductor light-emitting device |

| DE102005041099A1 (de) * | 2005-08-30 | 2007-03-29 | Osram Opto Semiconductors Gmbh | LED-Chip mit Glasbeschichtung und planarer Aufbau- und Verbindungstechnik |

| US8526096B2 (en) | 2006-02-23 | 2013-09-03 | Pixtronix, Inc. | Mechanical light modulators with stressed beams |

| KR100755598B1 (ko) * | 2006-06-30 | 2007-09-06 | 삼성전기주식회사 | 질화물 반도체 발광소자 어레이 |

| US7952109B2 (en) * | 2006-07-10 | 2011-05-31 | Alcatel-Lucent Usa Inc. | Light-emitting crystal structures |

| DE112007001950T5 (de) * | 2006-08-21 | 2009-07-02 | Innotec Corporation, Zeeland | Elektrische Vorrichtung mit platinenloser Montageanordnung für elektrische Komponenten |

| JP5082752B2 (ja) * | 2006-12-21 | 2012-11-28 | 日亜化学工業株式会社 | 半導体発光素子用基板の製造方法及びそれを用いた半導体発光素子 |

| CN102176486B (zh) | 2007-01-17 | 2015-06-24 | 伊利诺伊大学评议会 | 通过基于印刷的组装制造的光学系统 |

| US9176318B2 (en) | 2007-05-18 | 2015-11-03 | Pixtronix, Inc. | Methods for manufacturing fluid-filled MEMS displays |

| US8530255B2 (en) * | 2007-02-28 | 2013-09-10 | Sony Corporation | Method of manufacturing semiconductor laser, semiconductor laser, optical pickup, optical disk device, method of manufacturing semiconductor device, semiconductor device, and method of growing nitride type group III-V compound semiconductor layer |

| US7712933B2 (en) * | 2007-03-19 | 2010-05-11 | Interlum, Llc | Light for vehicles |

| US8408773B2 (en) | 2007-03-19 | 2013-04-02 | Innotec Corporation | Light for vehicles |

| CN101364628B (zh) * | 2007-08-06 | 2013-06-26 | 晶元光电股份有限公司 | 半导体发光装置及其制造方法 |

| US8230575B2 (en) * | 2007-12-12 | 2012-07-31 | Innotec Corporation | Overmolded circuit board and method |

| US7815339B2 (en) | 2008-01-09 | 2010-10-19 | Innotec Corporation | Light module |

| EP2332185A2 (en) * | 2008-09-08 | 2011-06-15 | 3M Innovative Properties Company | Electrically pixelated luminescent device |

| US8169679B2 (en) | 2008-10-27 | 2012-05-01 | Pixtronix, Inc. | MEMS anchors |

| US8513685B2 (en) | 2008-11-13 | 2013-08-20 | 3M Innovative Properties Company | Electrically pixelated luminescent device incorporating optical elements |

| US8242510B2 (en) * | 2010-01-28 | 2012-08-14 | Intersil Americas Inc. | Monolithic integration of gallium nitride and silicon devices and circuits, structure and method |

| CN104916258B (zh) | 2010-02-02 | 2018-02-16 | 追踪有限公司 | 用于控制显示装置的电路 |

| JP2013519121A (ja) | 2010-02-02 | 2013-05-23 | ピクストロニックス・インコーポレーテッド | 低温封孔流体充填ディスプレイ装置を製造するための方法 |

| US9022631B2 (en) | 2012-06-13 | 2015-05-05 | Innotec Corp. | Flexible light pipe |

| US9134552B2 (en) | 2013-03-13 | 2015-09-15 | Pixtronix, Inc. | Display apparatus with narrow gap electrostatic actuators |

| US10418527B2 (en) | 2014-10-31 | 2019-09-17 | eLux, Inc. | System and method for the fluidic assembly of emissive displays |

| US10520769B2 (en) | 2014-10-31 | 2019-12-31 | eLux, Inc. | Emissive display with printed light modification structures |

| US10535640B2 (en) | 2014-10-31 | 2020-01-14 | eLux Inc. | System and method for the fluidic assembly of micro-LEDs utilizing negative pressure |

| US10242977B2 (en) | 2014-10-31 | 2019-03-26 | eLux, Inc. | Fluid-suspended microcomponent harvest, distribution, and reclamation |

| US10381335B2 (en) | 2014-10-31 | 2019-08-13 | ehux, Inc. | Hybrid display using inorganic micro light emitting diodes (uLEDs) and organic LEDs (OLEDs) |

| US10381332B2 (en) | 2014-10-31 | 2019-08-13 | eLux Inc. | Fabrication method for emissive display with light management system |

| US9825202B2 (en) | 2014-10-31 | 2017-11-21 | eLux, Inc. | Display with surface mount emissive elements |

| US10236279B2 (en) | 2014-10-31 | 2019-03-19 | eLux, Inc. | Emissive display with light management system |

| US10543486B2 (en) | 2014-10-31 | 2020-01-28 | eLux Inc. | Microperturbation assembly system and method |

| US10446728B2 (en) | 2014-10-31 | 2019-10-15 | eLux, Inc. | Pick-and remove system and method for emissive display repair |

| US10319878B2 (en) | 2014-10-31 | 2019-06-11 | eLux, Inc. | Stratified quantum dot phosphor structure |

| TWI560905B (en) * | 2014-11-19 | 2016-12-01 | Univ Nat Sun Yat Sen | A light emitting element and manufacturing method thereof |

| US10381508B2 (en) | 2014-11-19 | 2019-08-13 | National Sun Yat-Sen University | Light emitting element with an enhanced electroluminescence effect |

| US10217729B2 (en) | 2016-09-30 | 2019-02-26 | Intel Corporation | Apparatus for micro pick and bond |

| US20180166294A1 (en) * | 2016-12-13 | 2018-06-14 | Intel Corporation | Apparatus and methods to achieve uniform package thickness |

| CN109001240B (zh) * | 2018-08-17 | 2021-04-13 | 胜科纳米(苏州)有限公司 | 制备非导电性材料样品的方法 |

| WO2020034189A1 (zh) * | 2018-08-17 | 2020-02-20 | 中国科学院半导体研究所 | 垂直金字塔结构led及其制备方法 |

| US12218275B2 (en) * | 2019-03-18 | 2025-02-04 | Hexagem Ab | Semiconductor template and fabrication method |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5788782A (en) * | 1980-11-21 | 1982-06-02 | Sharp Corp | Light emitting diode |

| JPS58130582A (ja) * | 1982-01-29 | 1983-08-04 | Toshiba Corp | デイスプレイ装置 |

| US4706041A (en) * | 1986-03-21 | 1987-11-10 | Texas Instruments Incorporated | Periodic negative resistance microwave structures and amplifier and oscillator embodiments thereof |

| JP2500615B2 (ja) * | 1993-06-23 | 1996-05-29 | 日本電気株式会社 | 埋め込み構造半導体光デバイスの製造方法 |

| JPH0794124A (ja) | 1993-09-25 | 1995-04-07 | Yamaha Corp | 表示装置 |

| JPH07142579A (ja) | 1993-11-19 | 1995-06-02 | Canon Inc | 多層配線構造及び製造方法 |

| JPH08307001A (ja) * | 1995-04-28 | 1996-11-22 | Mitsubishi Electric Corp | 半導体レ−ザダイオ−ドおよびその製造方法 |

| DE19621124A1 (de) * | 1996-05-24 | 1997-11-27 | Siemens Ag | Optoelektronischer Wandler und dessen Herstellungsverfahren |

| TW383508B (en) * | 1996-07-29 | 2000-03-01 | Nichia Kagaku Kogyo Kk | Light emitting device and display |

| TW427039B (en) * | 1997-06-16 | 2001-03-21 | Matsushita Electric Industrial Co Ltd | Manufacturing method for semiconductor, manufacturing method for semiconductor device, manufacturing method for semiconductor substrate |

| JP3641122B2 (ja) * | 1997-12-26 | 2005-04-20 | ローム株式会社 | 半導体発光素子、半導体発光モジュール、およびこれらの製造方法 |

| JPH11220180A (ja) * | 1998-01-30 | 1999-08-10 | Ricoh Co Ltd | Ledアレイヘッド |

| JP4083866B2 (ja) * | 1998-04-28 | 2008-04-30 | シャープ株式会社 | 半導体レーザ素子 |

| JP3206555B2 (ja) * | 1998-08-13 | 2001-09-10 | 日本電気株式会社 | 窒化ガリウム系半導体発光素子及びその製造方法 |

| US6410942B1 (en) * | 1999-12-03 | 2002-06-25 | Cree Lighting Company | Enhanced light extraction through the use of micro-LED arrays |

| JP3882539B2 (ja) * | 2000-07-18 | 2007-02-21 | ソニー株式会社 | 半導体発光素子およびその製造方法、並びに画像表示装置 |

| JP3906653B2 (ja) * | 2000-07-18 | 2007-04-18 | ソニー株式会社 | 画像表示装置及びその製造方法 |

| US6614103B1 (en) * | 2000-09-01 | 2003-09-02 | General Electric Company | Plastic packaging of LED arrays |

| JP4101468B2 (ja) * | 2001-04-09 | 2008-06-18 | 豊田合成株式会社 | 発光装置の製造方法 |

-

2001

- 2001-02-08 JP JP2001032688A patent/JP4724924B2/ja not_active Expired - Lifetime

-

2002

- 2002-02-07 US US10/071,909 patent/US6825499B2/en not_active Expired - Fee Related

-

2004

- 2004-09-01 US US10/931,594 patent/US7060542B2/en not_active Expired - Lifetime

-

2005

- 2005-03-30 US US11/093,444 patent/US7250314B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20050174023A1 (en) | 2005-08-11 |

| US6825499B2 (en) | 2004-11-30 |

| US20050032259A1 (en) | 2005-02-10 |

| US20020104999A1 (en) | 2002-08-08 |

| US7250314B2 (en) | 2007-07-31 |

| US7060542B2 (en) | 2006-06-13 |

| JP2002237618A (ja) | 2002-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4724924B2 (ja) | 表示装置の製造方法 | |

| JP5554792B2 (ja) | 発光素子及びその製造方法 | |

| JP6712579B2 (ja) | 発光デバイスを支持基板に取り付ける方法 | |

| US7129527B2 (en) | Light emitting diode and method of making the same | |

| TWI593145B (zh) | 發光二極體 | |

| JP2019114804A (ja) | 支持基板に接合された発光デバイス | |

| JP2010021546A (ja) | 発光素子及びその製造方法 | |

| KR20100035846A (ko) | 발광 소자 및 그 제조방법 | |

| CN102646763B (zh) | 氮化物半导体发光元件的制造方法 | |

| CN100464438C (zh) | 发光半导体元件的制造方法 | |

| KR20050066358A (ko) | 플립칩용 질화물 반도체 발광소자 및 그 제조방법 | |

| JP6193254B2 (ja) | 厚い金属層を有する半導体発光デバイス | |

| WO2015141166A1 (ja) | 半導体発光装置とその製造方法 | |

| US9306122B2 (en) | Light emitting diode and a manufacturing method thereof, a light emitting device | |

| TWI300277B (en) | Method for manufacturing gallium nitride light emitting diode devices | |

| CN120730896B (zh) | 一种改善散热与缓释应力的led芯片及其制备方法 | |

| CN103904170B (zh) | 分离基板的方法和利用其制造半导体装置的方法 | |

| TWI573293B (zh) | 具有厚金屬層之半導體發光裝置 | |

| RU2535636C2 (ru) | Отражающий контакт для полупроводникового светоизлучающего устройства | |

| TW201332149A (zh) | 於半導體發光裝置上形成厚金屬層 | |

| TWI817264B (zh) | 垂直式發光二極體及其製造方法 | |

| CN118299485A (zh) | 红光led芯片制备方法及红光led芯片 | |

| KR100646635B1 (ko) | 복수 셀의 단일 발광 소자 및 이의 제조 방법 | |

| KR20120032779A (ko) | 고효율 발광 다이오드 및 그것을 제조하는 방법 | |

| CN121368238A (zh) | 一种微发光元件及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20071027 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101025 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101102 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101227 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110315 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110328 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140422 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |