JP4680904B2 - 隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術 - Google Patents

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術 Download PDFInfo

- Publication number

- JP4680904B2 JP4680904B2 JP2006521858A JP2006521858A JP4680904B2 JP 4680904 B2 JP4680904 B2 JP 4680904B2 JP 2006521858 A JP2006521858 A JP 2006521858A JP 2006521858 A JP2006521858 A JP 2006521858A JP 4680904 B2 JP4680904 B2 JP 4680904B2

- Authority

- JP

- Japan

- Prior art keywords

- state storage

- programming

- storage element

- control line

- over

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 title claims abstract description 281

- 238000005516 engineering process Methods 0.000 title description 5

- 238000000034 method Methods 0.000 claims description 153

- 238000012795 verification Methods 0.000 claims description 83

- 230000000694 effects Effects 0.000 claims description 23

- 238000012545 processing Methods 0.000 claims description 22

- 230000005684 electric field Effects 0.000 claims description 10

- 238000012937 correction Methods 0.000 claims description 8

- 238000004891 communication Methods 0.000 claims description 3

- 238000010200 validation analysis Methods 0.000 claims 2

- 239000004065 semiconductor Substances 0.000 abstract description 6

- 238000007667 floating Methods 0.000 description 37

- 238000001514 detection method Methods 0.000 description 17

- 238000012360 testing method Methods 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 9

- 238000012790 confirmation Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 4

- 238000013459 approach Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3404—Convergence or correction of memory cell threshold voltages; Repair or recovery of overerased or overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

Landscapes

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

本発明は、一般的にメモリデバイスのために技術に関し、特に、メモリデバイスがオーバー・プログラミングされたか否かを検知する技術に関する。

データを適切に保存するためには、マルチ状態メモリセルの複数の閾電圧レベル範囲の間隔を十分にあけて、メモリセルのレベルを明確な作法でプログラミング又は消去することが要求される。

まず、ECC処理が長い処理時間を必要とするため、メモリシステムの操作の速度が極端に下がる。

また、ECCを妥当な時間内で実行するためには、付加的な専用ハードウェアが要求される。このような専用ハードウェアをメモリシステムチップ内に配置するためには、多くの空間が必要になる。より小さなホストデバイスにフィットする小さなシステムを実現するために、メモリシステムのサイズを小さくすることが現在のトレンドである。従って、新しいメモリのデザインは、ECCのために使用されるスペースを減らす傾向がある。

また、複数のエラーがある場合、ECCではそれらのエラーの全てを訂正できない可能性がある。

従って、メモリセルのオーバー・プログラミングを検知するためのより優れた手法が必要とされている。

1つの実施例では、システムは、第1マルチ状態記憶素子の閾電圧が比較値より大きいか否かを判断する。第1マルチ状態記憶素子の閾電圧が比較値より大きく、異なる論理ページのためのデータが、第1マルチ状態記憶素子の閾電圧がその比較値を超えるべきではないと示唆した場合に、システムは第1マルチ状態記憶素子がオーバー・プログラミングされたと結論づける。オーバー・プログラミングの検知は、両方の論理ページがプログラミングされた後に実行される。

別の実施形態では、1つ又は複数の読取比較点について、第1制御線に関連するマルチ状態記憶素子に対して読取操作を実行することによって、オーバー・プログラミングの判断が行なわれる。これにより、第1制御線に関連するマルチ状態記憶素子の初期状態が判断される。第1制御線に関連するマルチ状態記憶素子と初期状態のためのエラー訂正コード処理が実行される。マルチ状態記憶素子のためのエラー訂正コード処理が失敗した場合に、そのマルチ状態記憶素子がオーバー・プログラミングされたと判断される。

1つの実施形態では、管理回路は、制御装置と状態機械を含む。別の実施形態では、管理回路は、状態機械のみを含み、制御装置を含まない。管理回路は、上記した工程を実行することができる。

1つの実施形態では、記憶素子がオーバー・プログラミングされたか否かを確認するための処理は、状態機械によって実行される。実施例では、状態機械は、記憶素子のアレイと同じ集積回路チップ上に配置される。

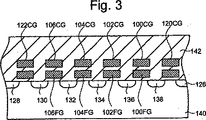

図1は、1つのNANDストリングの平面図を示す。図2は、NANDストリングの等価回路を示す。図1と図2のNANDストリングは、第1選択ゲート120と、第2選択ゲート122と、それらの間で直列に配列された4つのトランジスタ100,102,104,106を含む。

選択ゲート120は、NANDストリングをビット線126に接続する。選択ゲート122は、NANDストリングをソース線128に接続する。選択ゲート120は、制御ゲート120CGに適当な電圧を印加することによって制御される。選択ゲート122は、制御ゲート122CGに適当な電圧を印加することによって制御される。

各トランジスタ100,102,104,106は、制御ゲートと浮遊ゲートを有する。トランジスタ100は、制御ゲート100CGと浮遊ゲート100FGを有する。トランジスタ102は、制御ゲート102CGと浮遊ゲート102FGを有する。トランジスタ104は、制御ゲート104CGと浮遊ゲート104FGを有する。トランジスタ106は、制御ゲート106CGと浮遊ゲート106FGを有する。

制御ゲート100CGはワード線WL3に接続されており、制御ゲート102CGはワード線WL2に接続されており、制御ゲート104CGはワード線WL1に接続されており、制御ゲート106CGはワード線WL0に接続されている。

メモリセル群の制御ゲート群(100,102,104,106)は、ワード線を構成する。N+拡散層130,132,134,136,138は、隣接するセルによって共有される。これにより、各セルが互いに直列に接続されたNANDストリングが構成される。これらのN+拡散層は、各セルのソース及びドレインを構成する。例えば、N+拡散層130は、トランジスタ122のドレインであるとともに、トランジスタ106のソースである。N+拡散層132は、トランジスタ106のドレインであるとともに、トランジスタ104のソースである。N+拡散層134は、トランジスタ104のドレインであるとともに、トランジスタ102のソースである。N+拡散層136は、トランジスタ102のドレインであるとともに、トランジスタ100のソースである。N+拡散層138は、トランジスタ100のドレインであるとともに、トランジスタ120のソースである。N+拡散層126は、NANDストリングのビット線に接続される。N+拡散層128は、複数のNANDストリングの共有ソース線に接続される。

選択線SGSは、ソース側の選択ゲートを制御するために利用される。各NANDストリングは、選択線SGDによって制御される選択トランジスタ220,240等によって各自のビット線に接続される。他の実施形態では、選択線は必ずしも共有されていなくてよい。

ワード線WL3は、メモリセル222の制御ゲートとメモリセル242の制御ゲートに接続される。ワード線WL2は、メモリセル224の制御ゲートとメモリセル244の制御ゲートとメモリセル250の制御ゲートに接続される。ワード線WL1は、メモリセル226の制御ゲートとメモリセル246の制御ゲートに接続される。ワード線WL0は、メモリセル228の制御ゲートとメモリセル248の制御ゲートに接続される。

図示されるように、各ビット線とそのNANDストリングは、メモリセルアレイの列を構成する。ワード線(WL3,WL2,WL1,WL0)は、アレイの行を構成する。

NANDタイプのフラッシュメモリの一例では、メモリセルが消去された後の閾電圧は負であり、論理「1」と定義される。プログラミング操作後の閾電圧は正であり、論理「0」と定義される。閾電圧が負の時に読取りが行なわれると、メモリセルはターンオンし、論理「1」が保存されていることを示す。閾電圧が正の時に読取が行なわれると、メモリセルはターンオンせず、論理「0」が保存されていることを示す。

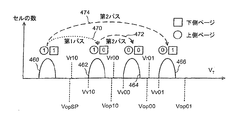

メモリセルは、複数レベルの情報(例えば複数ビットのデジタルデータ)を保存することもできる。複数レベルのデータを保存する場合、可能な閾電圧の範囲はデータのレベルの数に分けられる。例えば、4つのレベルの情報が保存される場合、閾電圧は4つの範囲に分けられ、その4つの範囲はデータ値「11」、「10」、「01」、「00」が割り当てられる。NANDタイプのメモリの一例では、消去操作後の閾電圧は負であり、「11」と定義される。状態「10」、「01」、「00」には、正の閾電圧が使用される。

他のタイプのフラッシュメモリデバイスも本発明を利用することができる。例えば、米国特許第5095344号、同第5172338号、同第5890192号、及び同第6151248号は、NORタイプのフラッシュメモリを開示する。これらの内容は、本明細書に組み込まれる。また、米国特許第6151248号は、フラッシュメモリの他の例が記載されている。この内容は、本明細書に組み込まれる。

列制御回路304は、メモリセルアレイ302のビット線に接続されている。列制御回路304は、メモリセルに保存されたデータを読取る。また、プログラミング操作中のメモリセルの状態を判断する。また、ビット線の電位レベルを制御してプログラミングを促進あるいは禁止する。

行制御回路306は、ワード線群の中から1つを選択するために各ワード線に接続されている。行制御回路306は、読取電圧、プログラミング電圧、及び消去電圧を印加することができる。

Cソース制御回路310は、メモリセルに接続された共有ソース線(図6では「Cソース」と称する)を制御する。

Pウェル制御回路308は、Pウェル電圧を制御する。

メモリシステムは、ホストシステムの一部として埋め込まれてもよい。あるいは、メモリシステムは、ホストシステムにリムーバブルに差し入れできるメモリカード(又は他のパッケージ)に含まれていてもよい。このようなリムーバブルカードは、メモリシステム全体(例えば制御装置を含む)を含んでいてもよい。あるいは、メモリアレイとそのメモリアレイに関連する周辺回路のみを含んでもよい。従って、制御装置は、ホストに埋め込まれていてもよいし、リムーバブルメモリシステムに含まれていてもよい。

1つのブロックに保存されたデータは同時に消去される。1つの実施形態では、1つのブロックは、同時に消去できるセルの最小単位である。この例では、各ブロックが、偶数列と奇数列に分けられた8512個の列を有する。ビット線は、偶数ビット線(BLe)と奇数ビット線(BLo)に分けられる。

図6は、4個のメモリセルを直列に接続することによって構成されたNANDストリングを示す。各NANDストリングに4個のセルが含まれているように示されているが、4個以上あるいは4個以下にしてもよい。NANDストリングの一端は、第1選択トランジスタSGDを介して対応するビット線に接続されている。他端は、第2選択トランジスタSGSを介してCソースに接続されている。

ソースとPウェルは0Vである。選択されたビット線(BLe)は、例えば0.7Vのレベルに予備チャージされる。閾電圧が読取レベル又は検証レベルよりも大きい場合、非導電メモリセルになるために、関連するビット線(BLe)の電位レベルは高レベルに維持される。一方において、閾電圧が読取レベル又は検証レベルよりも小さい場合、導電性メモリセル(M)になるために、関連しているビット線(BLe)の電位レベルは、例えば0.5V以下という低レベルに下がる。メモリセルの状態は、ビット線に接続されているセンス増幅器によって検知される。メモリセルが消去されるか又はプログラミングされるかは、浮遊ゲートに負電荷が帯電しているか否かに依存する。例えば、浮遊ゲートに負電荷が帯電している場合、閾電圧は上昇し、トランジスタは促進モードになることができる。

上記した消去、読取、及び検証操作は、この技術分野における公知のテクニックに基づいて実行される。従って、上記の各説明は、当業者が変更することができる。

センス増幅器は、読取操作又は検証操作中に選択されたビット線の電位レベルを検知し、検地したデータを二値データとして保存し、プログラミング操作中にビット線電圧を制御する。センス増幅器は、「evenBL」と「oddBL」の信号のいずれかを選択することによって、選択されたビット線に選択的に接続される。

データラッチ402,404,406は、読取データを出力したりプログラミングデータを保存したりするために、I/O線408に接続されている。I/O線408は、図5のデータ入出力バッファ312に接続されている。データラッチ402,404,406は、ステータス情報を入出力するために、ステータス線410にも接続されている。この実施形態では、1つのビット線のペア(偶数と奇数)に対して、センス増幅器、第1データラッチ402、第2データラッチ404、及び第3データラッチ406が備えられている。

2ビットは単一のメモリセルに保存され、この例では、各ビットは異なる論理ページの一部である。四角内に示すビットは、下側ページに対応する。丸内に示すビットは上側ページに対応する。1つの実施形態では、これらの論理状態は、グレイコードオリエンテーション(11、10、00、01)を利用して物理的状態に割り当てられる。その結果、浮遊ゲートの閾電圧が誤ってシフトしても、1ビットのみが影響を受ける。

なお、図8では4つの状態を示しているが、本発明は4つ以上あるいは4つ以下の状態を利用してもよい。

上側ページのビットが論理「0」の場合、閾電圧はシフトされる。第1パスの結果、セルの状態が閾区分460に対応する消去状態のままだった場合、第2パスでは、そのセルが矢印474で示すように閾電圧が上げられるようにプログラミングされる。具体的には、その閾電圧が閾電圧区分466内に収まるようプログラミングされる。一方、第1パスの結果、セルの状態が閾区分462に対応する状態にプログラミングされた場合、第2パスでは、そのセルが矢印472で示すように、閾電圧が上げられるようプログラミングされる。具体的には、その閾電圧が閾電圧区分464内に収まるようにプログラミングされる。第2パスでは、下側ページのデータは変更されずに、上側ページに論理「0」を保存するよう指定された状態にプログラミングされる。

なお、各区分には特定のビットパターンが割り当てられているが、これと異なるビットパターンが割り当てられてもよい。その場合、プログラミングが実行される状態は、図8に示すものと異なってよい。

1つの実施形態では、読取比較点Vr10,Vr00,Vr01のそれぞれは、閾区分の隣接する2つの状態の中間点である。検証比較点Vv10,Vv00,Vv01は、セルが十分にプログラミングされたことを確認するためにプログラミング処理の間に利用される。

例えば、状態11にあるはずのメモリセルの制御ゲートにVopSPを印加してもそのメモリセルが導通しない場合に、そのセルはオーバー・プログラミング(あるいはオーバー・ソフト・プログラミング)されたと判断できる。

状態10にあるはずのメモリセルの制御ゲートにVop10を印加してもそのセルが導通(例えばターンオン)しない場合に、そのメモリセルがオーバー・プログラミングされたと結論づけることができる。

状態00にあるはずのメモリセルの制御ゲートにVop00を印加した時にそのメモリセルが導通(例えばターンオン)しない場合に、そのセルがオーバー・プログラミングされたと判断することができる。

状態01にあるはずのメモリセルの制御ゲートにVop01を印加した時にそのメモリセルが導通(例えばターンオン)しない場合に、そのセルがオーバー・プログラミングされたと結論づけることができる。

オーバー・プログラミング検証比較点のそれぞれは、隣接する読取比較点より若干低い。例えば、1つの実施形態では、各検証比較点は、隣接する読取比較点よりも50mV低い。他の実施形態では、検証比較点と隣接する読取比較点の違いは、50mV以上あるいは50mV以下でもよい。1つの実施形態では、オーバー・プログラミング検証処理は、状態機械316によって実行される。

データが上側ページに書き込まれる場合、状態機械は、ステップ596の下側ページのデータを確認するために、下側ページ読取操作を実行する。図8を参照すると、上側ページのプログラミングは、メモリセルを状態00又は状態01にプログラミングすることを含む。下側ページのデータが論理「1」の場合、上側ページのプログラミング処理は、メモリセルを状態01にプログラミングすることを含む(図8の矢印474参照)。従って、システムは、上側ページのプログラミング処理の間に、メモリセルがどの状態にプログラミングされなければならないかを判断するために下側ページのデータを知る必要がある。

1回目のステップ600では、選択されたワード線に第1プログラミングパルスが印加される。特定の第1データラッチに論理「0」が保存されている場合、そのメモリセルに対応するビット線は接地される。一方において、特定の第1データラッチに論理「1」が保存されている場合、そのメモリセルに対応するビット線はVddに接続され、プログラミングは禁止される。プログラミングを禁止することに関するさらなる情報は、「Improved Self Boosting Technique(2003年3月5日に出願された米国特許出願第10/379608号)」に開示されている。この内容は、本明細書に組み込まれる。

ステップ604は、全ての第2データラッチ404が論理「1」を保存しているか否かを確認することを含んでいる。全ての第2データラッチ404が論理「1」を保存している場合、プログラミングの第1ステージが完了し、適当なステータスメッセージがステップ610で報告される。

プログラムカウンタが最大値より低い場合、プログラミング電圧は次のステップサイズ分だけ増加され、プログラムカウンタはインクリメントされ、プログラミング処理は次のパルスを印加するためにステップ600に進む。

これまでは、プログラミング処理が所望の状態を上回ってしまったことを確認することはなかった。例えば、メモリを状態10にプログラミングするのが目的である場合、そのメモリセルの閾電圧がVop10より高い値にプログラミングされてしまったら、そのメモリセルはオーバー・プログラミングされたことになる。ステップ620〜676は、プログラミング処理がメモリセルをオーバー・プログラミングしたか否かを判断するために利用される。

メモリセルが消去される場合、そのメモリセルの閾電圧が低すぎる場合がある。閾電圧が低すぎる問題を改善するために、ソフトプログラミング処理が実行され、その消去されたメモリセルの閾電圧を適当なレベルに上げる。ソフトプログラミング処理が閾電圧を上げすぎて、そのセルをオーバー・プログラミングしてしまう可能性がある(閾電圧がVopSPより高くなる可能性がある)。ステップ620では、このようにオーバー・プログラミングされたセルを検知する。

ステップ622では、各セルが、ソフトプログラミングに起因するオーバー・プログラミング検証処理(ステップ620)をパスしたか否かを判断する。全てのセルがパスしなかった場合、ステップ624では、ソフトプログラミングに起因するオーバー・プログラミング検証が失敗した旨を示すステータスがリターンされる。ステップ620の処理をパスした場合(ソフトプログラミングの間にオーバー・プログラミングされたセルがなかった場合)、ステップ638では、状態10のオーバー・プログラミング検証処理が実行される。

ステップ638の処理において、メモリセルがオーバー・プログラミングされたと判断されなければ、ステップ644で「パス」のステータスがリターンされる。ステップ644の他の実施形態では、状態10のオーバー・プログラミング検証がパスであった旨を示すステータスをリターンすることができる。

ステップ700では、以前にメモリセルにプログラミングされたデータが、第1データラッチ402にまだ存在している。このデータは、そのメモリセルに対応する第1データラッチ402から第2データラッチ404にロードされる。

ステップ702では、VopSPを用いて検証処理が実行される。即ち、システムは、制御ゲートが電圧VopSPを持つ読取操作を実行することができる。メモリセルが導通した場合、センス増幅器は論理「1」をリターンする。メモリセルが導通しなかった場合、センス増幅器は論理「0」をリターンする。検証データが第2データラッチ404のデータと一致した場合(ステップ704)、第2データラッチ404のデータは「1」に設定される(ステップ706)。ステップ700〜706は、各セルに対して並列に行われる。

メモリセルに対する全ての第2データラッチが「1」に設定された場合(ステップ708)、ソフトプログラミングに起因するオーバー・プログラミングの検証処理は「パス」の結果をリターンする(ステップ710)。全ての第2データラッチ404が「1」に設定されていない場合、処理は失敗する(ステップ712)。

セルが状態10にあった場合は、ステップ700で第2データラッチにロードされるデータは論理「0」となり、検証ステップ702はVopSP電圧を印加してもトランジスタは導通せず、センスデータは「0」を示す。従って、読取データは、第2データラッチ404のデータと一致し、第2データラッチ404は論理「1」に設定され、処理はパスすることになる。

図11のステップ764では、システムは、Vop10を用いて検証処理を実行する。即ち、Vop10を様々なメモリセルの制御ゲートに印加して読取操作を実行する。セルがオーバー・プログラミングされておらず状態11又は10にある場合、そのセルは導通するはずである。従って、論理「1」が受信されるはずである。

ステップ766では、検証ステップからの結果が第2データラッチ404にロードされる。全てのセルがオーバー・プログラミングされていない場合、その全てのセルは、各自の第2データラッチに論理「1」を保存しているはずである。全ての第2データラッチが論理「1」の場合(ステップ768)、処理はパスする(ステップ770)。全ての第2データラッチが論理「1」ではない場合、処理は失敗する(ステップ772)。

図12のステップ802では、Vop00を用いて検証処理が実行される。即ち、Vop00をメモリセルの制御ゲートに印加して、読取操作が実行される。1つの実施形態では、メモリセルの閾電圧がVop00より高い場合、そのメモリセルはターンオンせず、論理「0」がリターンされる。メモリセルの閾電圧がVop00より低い場合、そのメモリセルはターンオンし、論理「1」がリターンされる。

ステップ802の検証でリターンされた結果は、対応する第2データラッチ404に保存される。ステップ804では、システムは、検証ステップ802の結果と、第3データラッチ406に保存してある下側ページのデータを比較する。図12の処理は、上側ページのプログラミングの後に実行される。上述したように、上側ページのプログラミングは、まず下側ページのデータを読取り、その下側ページのデータを第3データラッチ406に保存することによって開始される(ステップ596と598を参照)。第3データラッチに保存された下側ページのデータは、検証ステップ802の結果と比較される。

上側ページのプログラミングの後に、状態機械は、メモリセルが状態00にあるはずなのか、それとも状態01にあるはずなのかを知る必要がある。下側ページのデータは、その情報を提供する。下側ページのデータが「0」の場合、上側ページのプログラミングが行われる前に、そのメモリセルが状態10にあったことを意味する。メモリセルが状態10にあった場合、上側ページのプログラミングを実行することによって、そのメモリセルは状態00に移動する(図8の矢印472を参照)。下側ページのデータが「1」の場合、上側ページのプログラミングが行われる前に、そのメモリセルが状態11にあったことを意味する。メモリセルが状態11にあった場合、上側ページのプログラミングを実行することによって、そのメモリセルは状態01に移動する(図8の矢印474を参照)。従って、下側ページのデータが論理「0」の場合、状態機械は、メモリセルがオーバー・プログラミングされたか確認する必要がある。論理ページが論理「1」の場合、メモリセルが状態00であることはない。従って、状態00のオーバー・プログラミング検証に失敗はありえない。

下側ページのデータが論理「1」の場合、又は、ステップ802の検証処理からリターンされた結果(第2データラッチ404に保存されている結果)が論理「1」である場合、そのメモリセルは状態00に対してオーバー・プログラミングされていないと判断される。

ステップ806では、状態00に対してオーバー・プログラミングされていない各セルに対応する第2データラッチ404が論理「1」に設定される。なお、上側ページのプログラミング処理が、上側ページを論理「1」に維持しようとする場合(例えば状態11あるいは状態10)、対応する第2データラッチは既に論理「1」である。

全ての第2データラッチ404が論理「1」に設定されている場合(ステップ808)、図12の処理はパスする(ステップ810)。全ての第2データラッチが論理「1」に設定されていない場合、状態00に対してオーバー・プログラミングされたメモリセルが1つ又は複数存在するために、図12の処理は失敗する(ステップ812)。

ステップ862では、比較点Vop01を用いて検証処理を実行する。セルが導通した場合(論理「1」の検証結果がリターンされた場合)、第2データラッチ404は論理「1」に設定される。セルが導通しない場合、第2データラッチは論理「0」に設定される。

全ての第2データラッチが論理「1」に設定された場合(ステップ864)、図13の処理はパスする(ステップ866)。全ての第2データラッチが論理「1」に設定されていない場合、図13の処理はパスしない(ステップ868)。

他の実施形態では、記憶ユニットの状態は、複数の異なるパラメータを用いることによって判断することができる。例えば、セルに帯電している電荷レベルの確認は、バイアスコンディションを利用して、その状態のマグニチュードが検知される電流センシングによって実行されてよい。

一方において、コンディションのオンセットが様々なステアリングゲートバイアスコンディションを利用して検知される場合、閾電圧をセンシングすることによって判断することもできる。

また、セルの電荷レベルに定められた駆動力を利用して、(例えばプリチャージされたコンデンサによって)動的にホールドされたセンスノードの放電率を制御することによって、上記の確認を動的に行うこともできる。与えられた放電レベルに達するまでの時間を検知することによって、帯電している電荷レベルが特定される。この場合、セルのコンディションを示すパラメータは時間である。この方法は、米国特許第6222762号に説明されている。この内容は、本明細書に組み込まれる。

さらに、他の技術では、記憶ユニットの状態が周波数をパラメータとして利用することによって判断される。この方法は、米国特許第6044019号に説明されている。この内容は、本明細書に組み込まれる。なお、電流センシングの方法は、米国特許第5172338号により詳しく説明されている。この内容も、本明細書に組み込まれる。

隣接するセルは、隣接するワード線あるいは隣接するビット線に存在していてもよい。例えば、図4のセル244は、セル224、242、250、及び246と隣接している。いくつかの実施例では、セル244に隣接していないメモリセルが、セル244から読取られた電荷に影響を与える電界を持つこともありえる。

図14Aのステップ902では、メモリセルのセットは、第1ワード線を用いてプログラミングされる。例えば、図4を参照すると、ワード線WL1を用いて論理ページをプログラミングすることができる。ステップ902の処理は、図9の処理を実行することを含んでおり、図10〜13に示される「オーバー・プログラミングされたメモリセルを確認すること」も含んでいる。

ステップ904では、第2ワード線(例えば図4のワード線WL2)を用いて第2セットのメモリセルにプログラミング操作を実行する。ステップ904の処理は、図9の処理を実行することを含んでおり、オーバー・プログラミングされたメモリセルを確認することも含んでいる。

ステップ906では、システムは、第1ワード線(例えばワード線WL1)に関連する論理ページのメモリセルに対して、上述のYupin効果が原因で生じたオーバー・プログラミングをチェックする。

ステップ908では、システムは、第3ワード線(例えばワード線WL3)を用いて第3セットのメモリセルをプログラミングする。ステップ908の処理は、図9の処理を実行することを含んでおり、オーバー・プログラミングされたメモリセルを確認することも含んでおり。

ステップ910では、システムは、第2ワード線(例えばワード線WL2)に関連する論理ページのメモリセルに対して、上述のYupin効果が原因で生じたオーバー・プログラミングをチェックする。

その後、処理は続行し(あるいは続行しなくてもよい)、付加的なワード線に関連する付加的なメモリセルをプログラミングし、以前にプログラミングされたワード線においてオーバー・プログラミングされたメモリセルのための確認を実行することができる。

NANDストリングは、通常(必ずとは言えないが)、ソース側からドレイン側にプログラミングされる。例えば、メモリセル228からメモリセル222(図4参照)にプログラミングされる。従って、WL0を用いてプログラミングした後に、システムは、WL1(WL0に隣接するワード線)を利用する。従って、図14Aの例では、オーバー・プログラミング検証が、直前のワード線に対して実行される。しかしながら、他の実施形態では、直前にプログラミングされたメモリセルではなくて、それより前にプログラミングされた他のメモリセルを確認するようにしてもよい。

1つの実施形態では、ビット線は奇数ビット線と偶数ビット線にグループ分けされる。この実施形態では、奇数ビット線がプログラミングされ、次いで偶数ビット線がプログラミングされ、次いで奇数ビット線がプログラミングされ、次いで偶数ビット線がプログラミングされることが続いていく。他の実施形態では、ビット線の異なるセットは、異なるプログラミング操作が使用されてよい。

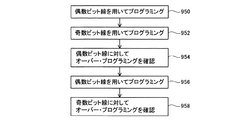

図14Bでは、一方のセットのビット線でプログラミングされた後に、その前にプログラミングされた他方のセットのビット線に対してオーバー・プログラミングの確認が行われる。ステップ950では、偶数ビット線を用いてプログラミング操作が実行される。ステップ950の処理は、図9の処理を実行することを含んでおり、図10〜13に示す「オーバー・プログラミングされたメモリセルを確認すること」を含んでいる。

ステップ952では、プログラミング操作は奇数ビット線を用いて実行される。ステップ952の処理は、図9の処理を実行することを含んでおり、オーバー・プログラミングされたメモリセルを確認することを含んでいる。

ステップ954では、システムは、以前にプログラミングされた偶数ビット線に関連する論理ページに対して、上述のYupin効果によって生じるオーバー・プログラミングを確認する。

ステップ956では、偶数ビット線を用いてプログラミングが実行される。ステップ956の処理は、図9の処理を実行することを含んでおり、オーバー・プログラミングされたメモリセルを確認することを含んでいる。

ステップ958では、システムは、以前にプログラミングされた奇数ビット線に関連する論理ページに対して、上述のYupin効果によって生じるオーバー・プログラミングを確認する。

この処理は、プログラミングと、以前にプログラミングされたビット線に対するオーバー・プログラミングの確認とを交互に行いながら続行することができる。

図14Aと14Bの処理の一部としてシステムが用いる方法は、多種多様である。以前にプログラミングされた制御線に関連する論理ページに対して、上述のYupin効果が原因で生じるオーバー・プログラミングを確認するための方法は、多種多様である。図15A〜Cは、その適切な方法を二つ説明するが、他の適切な方法も用いることもできる。

第1セルと隣接する第2セルをプログラミングした後に、第2セルからのYupin効果によって、第1セルの閾電圧が0.2Vほど上がる。技術、規模、スペース等に依存し、0.2V以上あるいは0.2V以下でもよい。

このデータは、予想通り破損しているが、完全に破損してはいない。1つのシナリオは、初めのプログラミングによって第1セルの閾電圧がオーバー・プログラミング検証電圧(例えばVop10)をわずかに下回る値になった場合に、セルが最大Yupin効果(例えば約0.2V又は上述した別の値)の影響にさらされることである。Yupin効果が原因でセルがオーバー・プログラミングされたことを示す閾電圧の範囲を象徴するオーバー・プログラミング領域が確立される。

図15Aは、3つのオーバー・プログラミング領域を示す。第1オーバー・プログラミング領域は、VopSPとVopAの間の領域を含んでいる。第2オーバー・プログラミング領域は、Vop10とVopBの間の領域を含んでいる。第3オーバー・プログラミング領域は、Vop00とVopCの間の領域を含んでいる。

なお、オーバー・プログラミング比較点とオーバー・プログラミングテスト点は、図15Aとは異なる値でもよい。

図15Aは、4つの閾区分(2ビットのデータを保存する)を示すが、本発明の実施には、4つ以上あるいは4つ以下の区分(2ビット以上あるいは2ビット以下のデータ)を利用してもよい。

ステップ1002では、各オーバー・プログラミング領域のエッジで読取操作が実行される。例えば、VopSP,VopA,Vop10,VopB,Vop00,VopCで読取操作が実行される。これらの読取操作に基づいて、いずれか1つのオーバー・プログラミング領域内にセルの閾電圧があるか否かを判断する。例えば、Vop10がワード線に印加された時にメモリセルはターンオンし、VopBがワード線に印加された時にターンオンしない場合、そのセルは第2オーバー・プログラミング領域内にあると推定される。

メモリセルの閾電圧が、いずれか1つのオーバー・プログラミング領域内にある場合(ステップ1006)、そのセルは隣接するセルの影響(Yupin効果)が原因でオーバー・プログラミングされたと結論づけられる(ステップ1008)。

ステップ1010では、オーバー・プログラミングされたデータが修正される。閾電圧を適当な区分まで下げるために、セルを部分的に消去することができる。また、セルを完全に消去して再び書き込みを行なうこともできる。また、データを別の場所に書き込むこともできる。また、セルがオーバー・プログラミングされたことを示すエラー情報を保存し、オーバー・プログラミングを考慮して以後の読取を行なうこともできる。また、他の適切な処理を実行してよい。

ステップ1060では、読取比較点Vr10,Vr00,Vr01のそれぞれで読取操作が実行される。読取操作に基づいて、メモリセルの初期状態の確認が行われる。ステップ1062では、公知の手法に基づいてECC処理が実行される。ECCエラーがない場合(ステップ1064)、メモリセルはYupin効果によってオーバー・プログラミングされなかったと推定される(ステップ1066)。ECCエラーが検知された場合(ステップ1064)、そのエラーはYupin効果によってメモリセルがオーバー・プログラミングされたことが原因で生じたものだと推定される(ステップ1070)。ステップ1072では、データが修正される(図15Bのステップ1010と同様)。

例えば、ステップ1060で行った読取操作によって、閾電圧がVr00より高くVr01より低いと判断されたものとする。メモリセルは、閾区分464にあり、論理データ00を保存していると推定される。ECCが失敗した場合、メモリセルは閾区分462にあり、論理データ10を保存していると推定される(ただし、メモリセルはオーバー・プログラミングされている)。従って、ステップ1072の1つの実施形態では、メモリセルの閾電圧が、閾区分462内に含まれるよう修正される。

比較点VopSP’は、閾電圧区分460の最高電圧を若干上回る値である。比較点Vop10’は、閾電圧区分462の最高電圧を若干上回る値である。比較点Vop00’は、閾電圧区分464の最高電圧を若干上回る値である。比較点Vop01’は、閾電圧区分466の最高電圧を若干上回る値である。

図16のVopSP’は図8のVopSPより低く、図16のVop10’は図8のVop10より低く、図16のVop00’は図8のVop00より低く、図16のVop01’は図8のVop01より低い。

他の実施形態では、比較点VopSP’,Vop10’,Vop00’,Vop01’は、個々の閾電圧区分より高い他の値が使用されてよい。

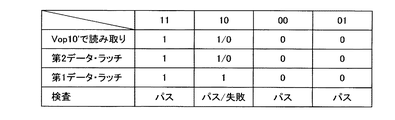

図17の真理値表は、以前の下側ページのプログラミングにおいてプログラミングされたデータが、「0」データなのか、あるいは「1」データなのかを示す2つの列を示す。真理値表の2行目(「VopSP’で読み取り」)は、オーバー・プログラミングのための検証が行なわれたメモリセルから読取られたデータに対応している。3行目は、第2データラッチ404に保存されたデータを示す。4行目は、第1データラッチ402に保存されたデータを示す。5行目は、状態11のオーバー・プログラミング検証の結果を示す。

真理値表の2行目は、メモリセルの制御ゲートにVopSP’を印加することを含んでいる読取操作の結果を示す。読取られたメモリセルの閾電圧がVopSP’より高い場合、そのメモリセルはターンオンせず、論理「0」が読取られる。メモリセルの閾電圧がVopSP’より低い場合、そのメモリセルはターンオンし、論理「1」が読取られる。

メモリセルに論理「1」がプログラミングされることに対応する列では、読取ステップで論理「1」(正常にプログラミングされた)、又は、論理「0」(オーバー・プログラミングされた)が読取られる。セルが状態10にプログラミングされた場合、プログラミング中の検証ステップで、電圧が少なくともVv10より高いことが検証されるので、読取ステップは論理「0」を読取る。読取られたデータは第2データラッチ404に保存される。第1データラッチ402は、以前に下側ページにプログラミングされたデータを保存している。状態機械は、第1データラッチ402と第2データラッチ404の内容を確認する。第1データラッチ402が論理「1」を保存しており、第2データラッチ404が論理「0」を保存している場合、オーバー・プログラミングテストは失敗である。即ち、状態機械は、メモリセルがオーバー・プログラミングされたと判断する。

真理値表の2行目は、制御ゲートにVopSP’を印加して読取られたデータを示す。セルが状態11を目的としていた場合、読取操作は、セルがオーバー・プログラミングされていなければ「1」をリターンし、オーバー・プログラミングされていたら「0」をリターンする。セルが他の3つの状態のいずれかにある場合は、「0」がリターンされるはずである。プログラミング処理の間に行われた以前の検証ステップが、そのセルの閾電圧が適当な検証点より十分に高いことを保証したからである。

真理値表の3行目は、上述の読取操作の結果を保存している第2データラッチ404のコンテンツを示す。4行目は、第3データラッチのコンテンツを示す。第3データラッチは、上述したように、下側ページのデータを保存する。5行目は、状態11のオーバー・プログラミング検証の結果を示す。

状態機械は、第3データラッチ406が論理「1」を保存しているとともに第2データラッチが論理「0」を保存しているか否かを確認する。そのように保存している場合、メモリセルがオーバー・プログラミングされたことを意味するために、オーバー・プログラミングテストは失敗する。そのように保存していなければ、テストはパスする。

真理値表には2つの列があり、一方の列は下側ページに論理「0」がプログラミングされた場合に対応し、他方の列は下側ページに論理「1」がプログラミングされた場合に対応する。2行目は、制御ゲートにVop10’を印加した場合の読取操作から得たデータを示す。メモリセルを状態11に維持することが目的だった場合、あるいはメモリセルが正常に状態10にプログラミングされた場合、Vop10’での読取操作は、メモリセルがターンオンし、論理「1」が報告される。この読取操作の結果は、第2データラッチ404に保存される(真理値表の3行目参照)。メモリセルを状態10にプログラミングすることが目的であったのにそのセルがオーバー・プログラミングされた場合、Vop10’での読取操作は、メモリセルはターンオンせず、それが原因で論理「0」が報告される。この読取操作の結果は、第1データラッチ402に保存される(4行目を参照)。

論理「1」がプログラミングされた場合(例えばプログラミングが実行されなかった場合)、第2データラッチ404と第1データラッチ402は両方とも論理「1」を保存し、テストはパスする(5行目を参照)。

論理「0」が適切にプログラミングされた場合、第1データラッチ404は論理「0」を保存し、第2データラッチは論理「1」を保存し、テストはパスする。第2データラッチ404が論理「0」であって第1データラッチ402が論理「1」の場合は、セルがオーバー・プログラミングされたことを意味するために、テストは失敗である。

2行目は、制御ゲートにVop10’を印加した読取操作から得られたデータを示す。この読取操作の結果は、第2データラッチ404(3行目)に保存される。メモリセルが状態11の維持される場合、あるいは、状態10に正常にプログラミングされた場合、メモリセルはターンオンして論理「1」が読取られる。メモリセルを状態10にプログラミングすることが目的だったことにもかかわらず、そのセルをオーバー・プログラミングしてしまった場合、セルはターンオンせず、論理「0」がリターンされる。上側ページのプログラミングの間にセルが状態00又は状態01にプログラミングされた場合、セルはターンオンせず、論理「0」が読取られる。

第1データラッチ402は、直前に実行された上側ページのプログラミング操作から得られたデータを保存する(4行目)。例えば、セルが状態11又は10の場合、第1データラッチは論理「1」を保存する。セルが状態00又は01の場合、第1データラッチは論理「0」を保存する。その後、システムはテストを実行し、第1データラッチ402が論理「1」を保存していて第2データラッチ404が論理「0」を保存していることを確認する。もしそうであれば、セルがオーバー・プログラミングされたことを意味するために、検証処理は失敗である。そうでなければ、検証処理はパスする(5行目)。

まず、制御ゲートにVop00’を印加することを含む読取操作が実行される(真理値表の2行目を参照)。メモリセルが正常に状態11,10,00にプログラミングされた場合、メモリセルはターンオンし、論理「1」がリターンされる。メモリセルが状態01にプログラミングされた場合、セルはターンオンせず、論理「0」がリターンされる。メモリセルを状態00にプログラミングすることが目的だったことにもかかわらずセルをオーバー・プログラミングしてしまった場合、セルはターンオンせず、論理「0」がリターンされる。この読取操作からリターンされたデータは、第2データラッチ404に保存される(真理値表の3行目参照)。

4行目は、第3データラッチ402のコンテンツを示す。第3データラッチは、上述したように、下側ページのデータを保存する。5行目は、状態00に対するオーバー・プログラミング検証の結果を示す。

状態機械は、第3データラッチ406が論理「0」を保存しているとともに第2データラッチ404が論理「0」を保存しているか否かを判断するためにチェックする。そのように保存されていれば、それはメモリセルがオーバー・プログラミングされたことを意味するために、オーバー・プログラミングテストは失敗である。そうでなければ、テストはパスする。

図22の2行目は、制御ゲートにVop01’を印加することを含む読取操作から得られた結果を示す。この読取操作から得られたデータは、第2データラッチ404に保存される(3行目)。この読取操作から得られたデータは、セルの状態を問わずに必ず論理「1」であるべきである。従って、論理「0」がリターンされた場合、検証ステップは失敗である。論理「0」がリターンされなかった場合、検証ステップはパスする(4行目)。

別の手法では、下側ページと上側ページの両方が書き込まれた後に、図18,20,21,22の真理値表を用いて説明した処理を用いて、全てのオーバー・プログラミング検証を実行することができる。

さらに別の手法では、下側ページのプログラミング処理が実行された後に、図17を用いて説明した検証処理を実行することができる。上側ページがプログラミングされた時に、システムは、図20,21,22の真理値表を用いて、状態10,00,01のオーバー・プログラミング検証を実行することもできる。

Claims (33)

- オーバー・プログラミングを検知する方法であり、

第1制御線に関連する1つ又は複数のマルチ状態記憶素子をプログラミングする工程と、

前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程の後に、第1制御線に隣接する第2制御線に関連する1つ又は複数のマルチ状態記憶素子をプログラミングする工程と、

前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程の後に、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」がオーバー・プログラミングされたか否かを判断する判断工程と、

を連続して実行し、

前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」を検証する工程を含み、

前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」のための前記検証が成功する場合に、開始され、

前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」を検証する工程を含み、

前記判断工程は、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」のための前記検証が成功する場合に、開始されることを特徴とする方法。 - 第1制御線は、第1ビット線であり、

第2制御線は、第1ビット線に隣接する第2ビット線であることを特徴とする請求項1の方法。 - 第1制御線は、第1ワード線であり、

第2制御線は、第1ワード線に隣接する第2ワード線であることを特徴とする請求項1の方法。 - オーバー・プログラミングされたと判断された記憶素子に対してデータを修正する工程をさらに備えることを特徴とする請求項1の方法。

- 前記修正工程は、所定の記憶素子の閾電圧を次に低い閾区分まで下げることを含んでいることを特徴とする請求項4の方法。

- 前記判断工程は、所定の記憶素子に隣接する記憶素子の電荷から生じる電界の存在を原因として前記所定の記憶素子がオーバー・プログラミングされたか否かを検知することを含んでいることを特徴とする請求項1の方法。

- 前記判断工程は、1つ又は複数のオーバー・プログラミング範囲のいずれかに含まれる閾電圧を所定の記憶素子が有するか否かを検知することを含んでいることを特徴とする請求項1の方法。

- 前記判断工程は、1つ又は複数のオーバー・プログラミング範囲のいずれかに含まれる閾電圧を所定の記憶素子が有するか否かを検知することを含んでおり、

オーバー・プログラミング範囲は、前記所定の記憶素子に隣接する記憶素子の電荷から生じる電界の影響を推定することによって決定されることを特徴とする請求項1の方法。 - 前記判断工程は、

1つ又は複数のオーバー・プログラミング範囲のエッジについて、前記の「第1制御線に関連するマルチ状態記憶素子」に対して読取操作を実行する工程と、

第1制御線に関連する所定のマルチ状態記憶素子が前記の「1つ又は複数のオーバー・プログラミング範囲」のいずれかに含まれる閾電圧を有する場合に、前記所定のマルチ状態記憶素子がオーバー・プログラミングされたと判断する工程

を有する方法を実行することを含んでおり、

前記所定のマルチ状態記憶素子は、前記の「第2制御線に関連するマルチ状態記憶素子」の少なくとも1つに隣接することを特徴とする請求項1の方法。 - 第1制御線は、第1ワード線であり、

第2制御線は、第2ワード線であることを特徴とする請求項9の方法。 - 前記判断工程は、

前記の「第1制御線に関連するマルチ状態記憶素子」の初期状態を判断するために、1つ又は複数の読取比較点について、前記の「第1制御線に関連するマルチ状態記憶素子」に対して読取操作を実行する工程と、

前記の「第1制御線に関連するマルチ状態記憶素子」と前記初期状態のためのエラー訂正コード処理を実行する工程と、

第1制御線に関連する所定のマルチ状態記憶素子のためのエラー訂正コード処理が失敗した場合に、前記所定のマルチ状態記憶素子がオーバー・プログラミングされたと判断する工程

を有する方法を実行することを含んでおり、

前記所定のマルチ状態記憶素子は、前記の「第2制御線に関連するマルチ状態記憶素子」の少なくとも1つに隣接することを特徴とする請求項1の方法。 - 第1制御線は、第1ワード線であり、

第2制御線は、第2ワード線であることを特徴とする請求項11の方法。 - 前記所定のマルチ状態記憶素子がオーバー・プログラミングされた場合に、前記所定のマルチ状態記憶素子に対してデータを修正する工程をさらに備えることを特徴とする請求項10の方法。

- 前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」と、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」は、NANDフラッシュメモリ素子であることを特徴とする請求項1の方法。

- 前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」は、記憶素子のアレイの一部であり、

記憶素子のアレイは、集積回路チップ上にあり、

前記判断工程は、集積回路チップ上にある1つ又は複数の回路によって実行されることを特徴とする請求項1の方法。 - オーバー・プログラミングを検知する方法であり、

第1マルチ状態記憶素子をプログラミングする工程と、

第1マルチ状態記憶素子をプログラミングする工程の後に、第1マルチ状態記憶素子に隣接する第2マルチ状態記憶素子であって、第1マルチ状態記憶素子に対して影響を及ぼすことができる電界を有する第2マルチ状態記憶素子をプログラミングする工程と、

第2マルチ状態記憶素子をプログラミングする工程の後に、第1マルチ状態記憶素子がオーバー・プログラミングされたか否かを判断する判断工程と、

を連続して実行し、

前記第1マルチ状態記憶素子をプログラミングする工程は、前記第1マルチ状態記憶素子を検証する工程を含み、

前記第2マルチ状態記憶素子をプログラミングする工程は、前記第1マルチ状態記憶素子のための前記検証が成功する場合に、開始され、

前記第2マルチ状態記憶素子をプログラミングする工程は、前記第2マルチ状態記憶素子を検証する工程を含み、

前記判断工程は、前記第2マルチ状態記憶素子のための前記検証が成功する場合に、開始されることを特徴とする方法。 - 第1マルチ状態記憶素子は、第1ワード線に接続されており、

第2マルチ状態記憶素子は、第2ワード線に接続されていることを特徴とする請求項16の方法。 - 第1マルチ状態記憶素子は、第1ビット線に接続されている第1NANDチェーンの一部であり、

第2マルチ状態記憶素子は、第2ビット線に接続されている第2NANDチェーンの一部であることを特徴とする請求項16の方法。 - 前記判断工程は、第2マルチ状態記憶素子の電荷から生じる電界の存在を原因として第1マルチ状態記憶素子がオーバー・プログラミングされたか否かを検知することを含んでいることを特徴とする請求項16の方法。

- 前記判断工程は、

1つ又は複数のオーバー・プログラミング範囲のエッジについて、第1マルチ状態記憶素子に対して読取操作を実行する工程と、

第1マルチ状態記憶素子が前記の「1つ又は複数のオーバー・プログラミング範囲」のいずれかに含まれる閾電圧を有する場合に、第1マルチ状態記憶素子がオーバー・プログラミングされたと判断する工程

を有する方法を実行することを含んでいることを特徴とする請求項16の方法。 - 前記判断工程は、

第1マルチ状態記憶素子の初期状態を判断するために、1つ又は複数の読取比較点について、第1マルチ状態記憶素子に対して読取操作を実行する工程と、

第1マルチ状態記憶素子と前記初期状態のためのエラー訂正コード処理を実行する工程と、

エラー訂正コード処理が失敗した場合に、第1マルチ状態記憶素子がオーバー・プログラミングされたと判断する工程

を有する方法を実行することを含んでいることを特徴とする請求項16の方法。 - マルチ状態記憶素子のアレイと、マルチ状態記憶素子のアレイと通信する管理回路を備えるメモリシステムであり、

管理回路は、第1制御線に関連する1つ又は複数のマルチ状態記憶素子をプログラミングする工程と、その後に連続して、第2制御線に関連する1つ又は複数のマルチ状態記憶素子をプログラミングする工程と、を含むプログラミング操作を実行し、

管理回路は、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングした後に、連続して、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」がオーバー・プログラミングされたか否かを判断する判断工程を実行し、

前記の「第2制御線に関連するマルチ状態記憶素子」の少なくとも一部は、前記の「第1制御線に関連するマルチ状態記憶素子」に隣接しており、

前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」を検証する工程を含み、

前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」のための前記検証が成功する場合に、開始され、

前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」をプログラミングする工程は、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」を検証する工程を含み、

前記判断工程は、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」のための前記検証が成功する場合に、開始されることを特徴とするメモリシステム。 - 第1制御線は、第1ビット線であり、

第2制御線は、第1ビット線に隣接する第2ビット線であることを特徴とする請求項22のメモリシステム。 - 第1制御線は、第1ワード線であり、

第2制御線は、第1ワード線に隣接する第2ワード線であることを特徴とする請求項22のメモリシステム。 - 前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」と、前記の「第2制御線に関連する1つ又は複数のマルチ状態記憶素子」は、NANDフラッシュメモリ素子であることを特徴とする請求項22のメモリシステム。

- 前記の「1つ又は複数のマルチ状態記憶素子」は、記憶素子のアレイの一部であり、

記憶素子のアレイは、集積回路チップ上にあり、

管理回路は、状態機械を含んでおり、

状態機械は、集積回路チップ上にあり、

状態機械は、前記の「第1制御線に関連する1つ又は複数のマルチ状態記憶素子」がオーバー・プログラミングされたか否かの判断を実行することを特徴とする請求項22のメモリシステム。 - 管理回路は、オーバー・プログラミングされたと判断された記憶素子に対してデータを修正することを特徴とする請求項22のメモリシステム。

- 管理回路は、所定の記憶素子に隣接する記憶素子の電荷から生じる電界の存在を原因として前記所定の記憶素子がオーバー・プログラミングされたか否かを検知することを特徴とする請求項22のメモリシステム。

- 管理回路は、所定の記憶素子が1つ又は複数のオーバー・プログラミング範囲のいずれかに含まれる閾電圧を有するか否かを検知し、

オーバー・プログラミング範囲は、前記所定の記憶素子に隣接する記憶素子の電荷から生じる電界の影響を推定することによって決定されることを特徴とする請求項22のメモリシステム。 - 管理回路は、1つ又は複数のオーバー・プログラミング範囲のエッジについて、前記の「第1制御線に関連するマルチ状態記憶素子」に対して読取操作を実行し、

第1制御線に関連する所定のマルチ状態記憶素子が前記の「1つ又は複数のオーバー・プログラミング範囲」のいずれかに含まれる閾電圧を有する場合に、前記所定のマルチ状態記憶素子はオーバー・プログラミングされたと判断することを特徴とする請求項22のメモリシステム。 - 第1制御線は、第1ワード線であり、

第2制御線は、第1ワード線に隣接する第2ワード線であることを特徴とする請求項30のメモリシステム。 - 管理回路は、

前記の「第1制御線に関連するマルチ状態記憶素子」の初期状態を判断するために、1つ又は複数の読取比較点について、前記の「第1制御線に関連するマルチ状態記憶素子」に対して読取操作を実行し、

前記の「第1制御線に関連するマルチ状態記憶素子」のためのエラー訂正コード処理を実行し、

第1制御線に関連する所定のマルチ状態記憶素子のためのエラー訂正コード処理が失敗した場合に、前記所定のマルチ状態記憶素子がオーバー・プログラミングされたと判断することを特徴とする請求項22のメモリシステム。 - 第1制御線は、第1ワード線であり、

第2制御線は、第1ワード線に隣接する第2ワード線であることを特徴とする請求項32のメモリシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/628,962 US6914823B2 (en) | 2003-07-29 | 2003-07-29 | Detecting over programmed memory after further programming |

| PCT/US2004/021699 WO2005013283A1 (en) | 2003-07-29 | 2004-07-07 | Detecting over programmed memory cells after programming of adjacent memory cells |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007500412A JP2007500412A (ja) | 2007-01-11 |

| JP2007500412A5 JP2007500412A5 (ja) | 2007-05-24 |

| JP4680904B2 true JP4680904B2 (ja) | 2011-05-11 |

Family

ID=34103497

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006521858A Expired - Fee Related JP4680904B2 (ja) | 2003-07-29 | 2004-07-07 | 隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US6914823B2 (ja) |

| EP (1) | EP1652191B1 (ja) |

| JP (1) | JP4680904B2 (ja) |

| KR (1) | KR101049582B1 (ja) |

| CN (1) | CN100474453C (ja) |

| AT (1) | ATE356410T1 (ja) |

| DE (1) | DE602004005211T8 (ja) |

| TW (1) | TWI264012B (ja) |

| WO (1) | WO2005013283A1 (ja) |

Families Citing this family (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4084922B2 (ja) * | 2000-12-22 | 2008-04-30 | 株式会社ルネサステクノロジ | 不揮発性記憶装置の書込み方法 |

| JP3935139B2 (ja) | 2002-11-29 | 2007-06-20 | 株式会社東芝 | 半導体記憶装置 |

| US6996004B1 (en) * | 2003-11-04 | 2006-02-07 | Advanced Micro Devices, Inc. | Minimization of FG-FG coupling in flash memory |

| JP4170952B2 (ja) * | 2004-01-30 | 2008-10-22 | 株式会社東芝 | 半導体記憶装置 |

| US7042766B1 (en) * | 2004-07-22 | 2006-05-09 | Spansion, Llc | Method of programming a flash memory device using multilevel charge storage |

| US7230854B2 (en) * | 2005-08-01 | 2007-06-12 | Sandisk Corporation | Method for programming non-volatile memory with self-adjusting maximum program loop |

| US7307887B2 (en) * | 2005-12-29 | 2007-12-11 | Sandisk Corporation | Continued verification in non-volatile memory write operations |

| US7352629B2 (en) * | 2005-12-29 | 2008-04-01 | Sandisk Corporation | Systems for continued verification in non-volatile memory write operations |

| US7450425B2 (en) * | 2006-08-30 | 2008-11-11 | Micron Technology, Inc. | Non-volatile memory cell read failure reduction |

| US7593259B2 (en) * | 2006-09-13 | 2009-09-22 | Mosaid Technologies Incorporated | Flash multi-level threshold distribution scheme |

| KR100921949B1 (ko) * | 2007-05-02 | 2009-10-15 | 충북대학교 산학협력단 | 표시장치용 구동 집적회로 |

| US7619920B2 (en) * | 2007-07-05 | 2009-11-17 | Kabushiki Kaisha Toshiba | NAND type flash memory and write method of the same |

| KR101411976B1 (ko) * | 2007-07-09 | 2014-06-27 | 삼성전자주식회사 | 플래시 메모리 시스템 및 그것의 에러 정정 방법 |

| KR101397549B1 (ko) * | 2007-08-16 | 2014-05-26 | 삼성전자주식회사 | 고속 프로그램이 가능한 불휘발성 반도체 메모리 시스템 및그것의 독출 방법 |

| JP4510060B2 (ja) * | 2007-09-14 | 2010-07-21 | 株式会社東芝 | 不揮発性半導体記憶装置の読み出し/書き込み制御方法 |

| KR101414494B1 (ko) * | 2008-03-17 | 2014-07-04 | 삼성전자주식회사 | 메모리 장치 및 메모리 데이터 읽기 방법 |

| US8014209B2 (en) | 2008-07-02 | 2011-09-06 | Sandisk Technologies Inc. | Programming and selectively erasing non-volatile storage |

| KR101069004B1 (ko) * | 2008-08-01 | 2011-09-29 | 주식회사 하이닉스반도체 | 플래시 메모리 소자의 프로그램 방법 |

| KR101124126B1 (ko) * | 2009-06-29 | 2012-03-22 | 주식회사 하이닉스반도체 | 불휘발성 메모리 소자의 프로그램 방법 |

| US8422305B2 (en) * | 2009-06-29 | 2013-04-16 | Hynix Semiconductor Inc. | Method of programming nonvolatile memory device |

| US8214700B2 (en) * | 2009-10-28 | 2012-07-03 | Sandisk Technologies Inc. | Non-volatile memory and method with post-write read and adaptive re-write to manage errors |

| US8423866B2 (en) | 2009-10-28 | 2013-04-16 | SanDisk Technologies, Inc. | Non-volatile memory and method with post-write read and adaptive re-write to manage errors |

| US8634240B2 (en) | 2009-10-28 | 2014-01-21 | SanDisk Technologies, Inc. | Non-volatile memory and method with accelerated post-write read to manage errors |

| KR101082692B1 (ko) * | 2009-12-31 | 2011-11-15 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 이의 프로그램 방법 |

| US8514630B2 (en) | 2010-07-09 | 2013-08-20 | Sandisk Technologies Inc. | Detection of word-line leakage in memory arrays: current based approach |

| US8305807B2 (en) | 2010-07-09 | 2012-11-06 | Sandisk Technologies Inc. | Detection of broken word-lines in memory arrays |

| US8432732B2 (en) | 2010-07-09 | 2013-04-30 | Sandisk Technologies Inc. | Detection of word-line leakage in memory arrays |

| US8379454B2 (en) | 2011-05-05 | 2013-02-19 | Sandisk Technologies Inc. | Detection of broken word-lines in memory arrays |

| KR20130008300A (ko) * | 2011-07-12 | 2013-01-22 | 삼성전자주식회사 | 오버 프로그램을 이용하여 소거 동작을 수행하는 플래시 메모리 장치 및 그 동작방법 |

| US8874994B2 (en) | 2011-07-22 | 2014-10-28 | Sandisk Technologies Inc. | Systems and methods of storing data |

| US8750042B2 (en) | 2011-07-28 | 2014-06-10 | Sandisk Technologies Inc. | Combined simultaneous sensing of multiple wordlines in a post-write read (PWR) and detection of NAND failures |

| US20130031431A1 (en) | 2011-07-28 | 2013-01-31 | Eran Sharon | Post-Write Read in Non-Volatile Memories Using Comparison of Data as Written in Binary and Multi-State Formats |

| US8775901B2 (en) | 2011-07-28 | 2014-07-08 | SanDisk Technologies, Inc. | Data recovery for defective word lines during programming of non-volatile memory arrays |

| US8726104B2 (en) | 2011-07-28 | 2014-05-13 | Sandisk Technologies Inc. | Non-volatile memory and method with accelerated post-write read using combined verification of multiple pages |

| US8842476B2 (en) | 2011-11-09 | 2014-09-23 | Sandisk Technologies Inc. | Erratic program detection for non-volatile storage |

| US8630118B2 (en) | 2011-11-09 | 2014-01-14 | Sandisk Technologies Inc. | Defective word line detection |

| US8566671B1 (en) | 2012-06-29 | 2013-10-22 | Sandisk Technologies Inc. | Configurable accelerated post-write read to manage errors |

| US9135989B2 (en) | 2012-09-06 | 2015-09-15 | Sandisk Technologies Inc. | Write data preservation for non-volatile storage |

| US9053810B2 (en) | 2013-03-08 | 2015-06-09 | Sandisk Technologies Inc. | Defect or program disturb detection with full data recovery capability |

| US9213601B2 (en) | 2013-12-03 | 2015-12-15 | Sandisk Technologies Inc. | Adaptive data re-compaction after post-write read verification operations |

| KR102356072B1 (ko) * | 2015-09-10 | 2022-01-27 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그 동작 방법 |

| US10249382B2 (en) | 2017-08-22 | 2019-04-02 | Sandisk Technologies Llc | Determination of fast to program word lines in non-volatile memory |

| KR102612891B1 (ko) * | 2018-05-31 | 2023-12-13 | 에스케이하이닉스 주식회사 | 메모리 장치, 그것의 동작방법 및 메모리 시스템 |

| US11545221B2 (en) | 2018-06-29 | 2023-01-03 | Sandisk Technologies Llc | Concurrent programming of multiple cells for non-volatile memory devices |

| US10978156B2 (en) | 2018-06-29 | 2021-04-13 | Sandisk Technologies Llc | Concurrent programming of multiple cells for non-volatile memory devices |

| US11081198B2 (en) | 2019-05-16 | 2021-08-03 | Sandisk Technologies Llc | Non-volatile memory with countermeasure for over programming |

| US10839928B1 (en) | 2019-05-16 | 2020-11-17 | Sandisk Technologies Llc | Non-volatile memory with countermeasure for over programming |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002279788A (ja) * | 2001-03-16 | 2002-09-27 | Toshiba Corp | 不揮発性半導体メモリ |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5602789A (en) * | 1991-03-12 | 1997-02-11 | Kabushiki Kaisha Toshiba | Electrically erasable and programmable non-volatile and multi-level memory systemn with write-verify controller |

| JPH08249893A (ja) * | 1995-03-07 | 1996-09-27 | Toshiba Corp | 半導体記憶装置 |

| KR960002006B1 (ko) * | 1991-03-12 | 1996-02-09 | 가부시끼가이샤 도시바 | 2개의 기준 레벨을 사용하는 기록 검증 제어기를 갖는 전기적으로 소거 가능하고 프로그램 가능한 불휘발성 메모리 장치 |

| JP3152720B2 (ja) * | 1991-03-12 | 2001-04-03 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US6222762B1 (en) * | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| US5532962A (en) * | 1992-05-20 | 1996-07-02 | Sandisk Corporation | Soft errors handling in EEPROM devices |

| US5422580A (en) * | 1993-10-14 | 1995-06-06 | Aps Technologies | Switchable active termination for SCSI peripheral devices |

| US6131140A (en) * | 1995-12-22 | 2000-10-10 | Cypress Semiconductor Corp. | Integrated cache memory with system control logic and adaptation of RAM bus to a cache pinout |

| US5771346A (en) * | 1996-10-24 | 1998-06-23 | Micron Quantum Devices, Inc. | Apparatus and method for detecting over-programming condition in multistate memory device |

| US5764568A (en) * | 1996-10-24 | 1998-06-09 | Micron Quantum Devices, Inc. | Method for performing analog over-program and under-program detection for a multistate memory cell |

| JP3517081B2 (ja) * | 1997-05-22 | 2004-04-05 | 株式会社東芝 | 多値不揮発性半導体記憶装置 |

| JP3246420B2 (ja) * | 1997-11-06 | 2002-01-15 | 日本電気株式会社 | 電気的書込可能な半導体記憶装置 |

| US5867429A (en) * | 1997-11-19 | 1999-02-02 | Sandisk Corporation | High density non-volatile flash memory without adverse effects of electric field coupling between adjacent floating gates |

| US6147547A (en) * | 1998-05-25 | 2000-11-14 | Mitsubishi Denki Kabushiki Kaisha | Charge pump circuit capable of generating positive and negative voltages and nonvolatile semiconductor memory device comprising the same |

| JP2000173289A (ja) * | 1998-12-10 | 2000-06-23 | Toshiba Corp | エラー訂正可能なフラッシュメモリシステム |

| KR100391404B1 (ko) * | 1999-07-13 | 2003-07-12 | 가부시끼가이샤 도시바 | 반도체 메모리 |

| JPWO2002050843A1 (ja) * | 2000-12-21 | 2004-04-22 | 富士通株式会社 | 不揮発性半導体記憶装置及びデータ消去方法 |

| US6493266B1 (en) * | 2001-04-09 | 2002-12-10 | Advanced Micro Devices, Inc. | Soft program and soft program verify of the core cells in flash memory array |

| US6522580B2 (en) * | 2001-06-27 | 2003-02-18 | Sandisk Corporation | Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states |

| US6456528B1 (en) * | 2001-09-17 | 2002-09-24 | Sandisk Corporation | Selective operation of a multi-state non-volatile memory system in a binary mode |

| US6542407B1 (en) * | 2002-01-18 | 2003-04-01 | Sandisk Corporation | Techniques of recovering data from memory cells affected by field coupling with adjacent memory cells |

| US6799256B2 (en) * | 2002-04-12 | 2004-09-28 | Advanced Micro Devices, Inc. | System and method for multi-bit flash reads using dual dynamic references |

| KR101110191B1 (ko) | 2002-06-19 | 2012-02-15 | 쌘디스크 코포레이션 | 스케일 낸드용 인접셀들 사이의 크로스 커플링을 실드하기위한 딥 워드라인 트렌치 |

-

2003

- 2003-07-29 US US10/628,962 patent/US6914823B2/en not_active Expired - Lifetime

-

2004

- 2004-07-07 JP JP2006521858A patent/JP4680904B2/ja not_active Expired - Fee Related

- 2004-07-07 CN CNB2004800264428A patent/CN100474453C/zh not_active Expired - Lifetime

- 2004-07-07 AT AT04756719T patent/ATE356410T1/de not_active IP Right Cessation

- 2004-07-07 KR KR1020067002056A patent/KR101049582B1/ko active IP Right Grant

- 2004-07-07 EP EP04756719A patent/EP1652191B1/en not_active Expired - Lifetime

- 2004-07-07 WO PCT/US2004/021699 patent/WO2005013283A1/en active IP Right Grant

- 2004-07-07 DE DE602004005211T patent/DE602004005211T8/de active Active

- 2004-07-20 TW TW093121649A patent/TWI264012B/zh not_active IP Right Cessation

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002279788A (ja) * | 2001-03-16 | 2002-09-27 | Toshiba Corp | 不揮発性半導体メモリ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100474453C (zh) | 2009-04-01 |

| CN1853240A (zh) | 2006-10-25 |

| TW200518104A (en) | 2005-06-01 |

| KR20060114319A (ko) | 2006-11-06 |

| DE602004005211T8 (de) | 2008-05-15 |

| US20050024943A1 (en) | 2005-02-03 |

| KR101049582B1 (ko) | 2011-07-15 |

| TWI264012B (en) | 2006-10-11 |

| EP1652191B1 (en) | 2007-03-07 |

| ATE356410T1 (de) | 2007-03-15 |

| JP2007500412A (ja) | 2007-01-11 |

| WO2005013283A1 (en) | 2005-02-10 |

| EP1652191A1 (en) | 2006-05-03 |

| DE602004005211T2 (de) | 2007-11-08 |

| DE602004005211D1 (de) | 2007-04-19 |

| US6914823B2 (en) | 2005-07-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4680904B2 (ja) | 隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術 | |

| JP4754486B2 (ja) | オーバー・プログラミングされたメモリを検出する技術 | |

| US7616499B2 (en) | Retention margin program verification | |

| JP4490977B2 (ja) | 不揮発性メモリのプログラミング方法 | |

| EP1751773B1 (en) | Erase verification for non-volatile memory by testing the conduction of the memory elements in a first and a second direction | |

| TWI451422B (zh) | 非揮發性記憶體中改良讀取操作之程式化不同大小邊限及在選擇狀態補償感測之方法和系統 | |

| JP4954223B2 (ja) | フローティングゲート結合に対する補償を伴う不揮発性記憶装置に対する読み出し動作 | |

| TWI389124B (zh) | 於非揮發性記憶體中使用不同參考位準以改良感測之粗略/精細程式化確認方法及系統 | |

| JP2011170964A (ja) | 不揮発性メモリ消去オペレーションにおけるワード・ライン補正 | |

| US20050024948A1 (en) | Semiconductor device and data processing system | |

| KR20120120221A (ko) | 패스트 비트 감지 및 확인 생략을 구비한 비휘발성 저장소의 프로그래밍 | |

| US7652918B2 (en) | Retention margin program verification | |

| JP2008535145A (ja) | マルチレベルセル型フラッシュメモリに高位レベル状態をより迅速にプログラミングする方法 | |

| JP5114621B2 (ja) | 不揮発性メモリのソフトプログラミングにおける制御されたブースト | |

| KR20090007298A (ko) | 임계 전압의 치밀한 분배가 가능한 비활성 메모리의 비 실시간 재 프로그래밍 방법 | |

| JP2009522703A (ja) | 不揮発性メモリの書込動作における継続的な検証 | |

| JP2010511263A (ja) | プログラミング検証のためのセグメント化されたビットスキャン | |

| JP4960378B2 (ja) | 不揮発性メモリの読み出し外乱を低減する方法 | |

| TWI386939B (zh) | 保留餘裕程式驗證 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070329 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070329 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091028 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091117 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100216 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100223 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100315 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100323 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100416 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100423 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100517 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100914 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110203 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4680904 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 3 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 3 |

|

| R370 | Written measure of declining of transfer procedure |

Free format text: JAPANESE INTERMEDIATE CODE: R370 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |