JP4649047B2 - ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 - Google Patents

ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 Download PDFInfo

- Publication number

- JP4649047B2 JP4649047B2 JP2001019268A JP2001019268A JP4649047B2 JP 4649047 B2 JP4649047 B2 JP 4649047B2 JP 2001019268 A JP2001019268 A JP 2001019268A JP 2001019268 A JP2001019268 A JP 2001019268A JP 4649047 B2 JP4649047 B2 JP 4649047B2

- Authority

- JP

- Japan

- Prior art keywords

- pin

- component

- order

- unit

- power supply

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は、プリント配線基板設計を支援する設計支援装置(CAD(Computer Aided Design)装置)に関し、特にノイズ低減に適した部品配置およびその確認に関する。

【0002】

【従来の技術】

プリント配線基板の配線設計においては、動作時のノイズを抑制するための対策が重要であり、特に高い周波数で動作する電子回路はノイズが発生しやすいので、十分な対策を講じる必要がある。従来から動作時のノイズを抑制するための対策の1つとして、基板上にバイパスコンデンサを配置する方法が採られている。

【0003】

特に、高周波信号線が配されるプリント配線基板において、高周波信号の変化時点に生じる高周波電源リプルの吸収、つまりICに対する高周波電流の供給は、主にコンデンサが担っている。したがって、配線基板における電磁放射ノイズを低減させ品質を向上させるためには、これらコンデンサはICの電源ピンにできる限り近くに配置したほうが良い。このような技術に関する文献としては、Mark I Montrose,"Printed Circuit Board Design Techniques for EMI Compliance",IEEE Order No.PC5595 や、Howard W.Johnson,Martin Graham "HIGH-SPEED DIGITAL DESIGN A Handbook of Black Magic",PTR Prentice-Hall などが挙げられる。

【0004】

また、配線基板の配置/配線CADにおいては、従来部品種類や、ネットの接続状況に応じ、IC、コネクタなどの主要な大物部品に、コンデンサ素子、コイル素子(インダクタ素子)、抵抗素子、フィルタ素子などの小さな部品を割付けて、割り付けられた相互の部品を一つの部品として扱うことにより、配線基板全体の顧慮すべき部品点数を減少させ、部品の配置を行うものなどが挙げられる。

このような技術に関する文献としては、谷本真一 他、“クリティカルネットの長さを制限した部品自動配置によるプリント回路基板からのEMI低減方法”、信学技報、EMCJ99-92,pp.17-22,1999などが挙げられる。

【0005】

【発明が解決しようとする課題】

しかしながら、部品種類を基に部品の割付けを行った場合、主要な大物部品(IC)に対し、低周波電流を供給するための容量の大きな電解コンデンサや、タンタルコンデンサと、高周波電流を供給するための容量の小さなセラミックコンデンサが、区別されることなく同じキャパシタ素子として認識されてしまう。そのため、図1に示すコンデンサ素子C6〜C8(C1〜C3より容量が小さい)などのように、コンデンサ素子が偏って割り当てられ、適切な部品の割付けが実施されず、ユーザによる修正が必要であった。また、コンデンサの配置は、高周波電流を供給すためのコンデンサほど、ICの電源ピンに近づけて最短距離で配置すべきであるが、近年のICは電源ピンを複数所有しているケースも多く、ICの電源ピンと複数のコンデンサの電源ピンとのピンペアの組み合わせも多くあり、最適なピンペアを選択し、配線することは困難であった。

【0006】

また、バイパスコンデンサの配置が適切であるかを確認することができるCAD装置としては、特開平10−97560号(コンピュータ支援設計システム)に開示されたものがある。

このCAD装置は、配置したバイパスコンデンサ毎にノイズ除去の有効範囲を基板上に表示することによって、バイパスコンデンサの配置を確認できるようにしたものである。

【0007】

図2は、特開平10−97560号において開示されたCAD装置のモニター上に表示された、設計中の配線基板の表示例を示す図である。

図2に示す配線基板2101には、この時点でバイパスコンデンサ2110、IC2120、IC2130が配置されている。

さらに、バイパスコンデンサ2110によるノイズ除去の有効範囲、楕円2141及び楕円2142が表示されている。ここで楕円2141はバイパスコンデンサ2110によるノイズ除去の効力が高い範囲を示し、楕円2142はバイパスコンデンサ2110によるノイズ除去の効力が中程度の範囲を示す。

【0008】

設計者は、これらの有効範囲の表示を参照して、配線基板上に配置された各部品の個々のピンが、バイパスコンデンサによるノイズ除去の有効範囲に入っているか否かを判断する事により、バイパスコンデンサの配置を確認する事ができる。

ここでは、IC2120の左側にある4本のピンは楕円2141の範囲内に存在するのでノイズ除去の効力が高いと推測され、IC2120の右側にある4本のピンは楕円2142の範囲内に存在するのでノイズ除去の効力が中程度であると推測される。また、IC2130のいずれのピンも、楕円2141及び楕円2142範囲内に存在しないので、ノイズ除去の効力が中程度以下であると推測される。

【0009】

しかしながら上記のような表示では、配線基板上に配置されたバイパスコンデンサの数が多くなるに伴ない楕円の数が多くなり、また楕円が相互に重なり合うので、バイパスコンデンサの数がある程度上になると表示が極端に見にくくなる。

また、部品の出力ピン毎の動作周波数等の動作特性の違いによって、それぞれ適合するバイパスコンデンサが異なる場合があり、このような場合には、上記のような表示ではそれぞれのバイパスコンデンサがどの部品のどのピンに有効であるのかがわからないので、かえって判断ミスを招く事になりかねない。

【0010】

また、コンデンサには容量があり、たとえ特性が一致したとしても、容量が不足すればノイズ除去の効果が不十分となるのであるが、上記のような表示ではバイパスコンデンサの容量を考慮していないので、容量不足を発見できない。

さらに上記のような表示による判断方法は、基板上におけるバイパスコンデンサと部品のピンとの平面上の直線距離のみによって、バイパスコンデンサが有効かどうかを判定するものであり、正確さに欠ける。なぜなら、バイパスコンデンサが有効かどうかは、平面上の直線距離に依存するのではなく、配線パターンにより決定される過渡電流の高調波成分が流れる経路長に依存するからである。

【0011】

本発明の第1の目的は、電磁放射ノイズの低減に適した部品配置を行なうCAD装置を提供することにある。

本発明の第2の目的は、バイパスコンデンサの配置が適切であるかを容易に確認することができるCAD装置を提供することにある。

【0012】

【課題を解決するための手段】

本発明のCAD装置は、プリント配線基板に配置すべき部品のうち、受動部品に対して、部品のインピーダンス値の小さい順に部品順位を決定する決定部と、決定された部品順位の順に受動部品を配置する配置部とを備える。

この構成によれば、受動部品は、インピーダンス値の小さい部品から順に配置されていく。インピーダンスが小さいほど周波数の高いノイズを低減するので、より高い周波数のノイズから低い周波数のノイズの順に受動部品が配置されることになる。先に配置される程、配置の自由度が大きいので、周波数の高いノイズほど効率良く低減される位置に、受動部品を配置することができる。

【0013】

ここで、前記配置部は、受動部品以外の配置済み部品の電源ピンの近傍に受動部品配置する。

ここで、前記決定部は、受動部品の等価直列インダクタンスの小さい順をインピーダンスの小さい順として前記部品順位を決定するようにしてもよい。

また、本発明の設計支援装置は、配線基板の部品配置を表示して、配置位置によって効果が異なる部品である位置依存部品の配置が適切か否かのユーザによる評価を支援する設計支援装置であって、

配線基板上の各部品の位置を示す位置情報を記憶する設計情報記憶部と、

位置依存部品と、その位置依存部品によって効果を及ぼされる被効果部品とを関係づけた関係情報を記憶する関係情報記憶部と、

位置情報に従って、前記関係情報により関係づけられた位置依存部品と被効果部品とを、ユーザが認識可能な態様で対応づけて表示する表示部とを備える。

【0014】

【発明の実施の形態】

(実施の形態1)

<概要>

本実施の形態におけるCAD装置は、プリント配線基板の設計を支援する装置であって、特定種類の部品について配置順を示す部品優先順位を設定して、優先部品優先順位に従って配置するように構成される。ここで、特定種類とは、キャパシタ素子、抵抗素子、インダクタ素子、フィルタ素子などプリント配線基板のノイズを低減させる受動部品であって、ノイズ対策用の部品種類をいう。

【0015】

本CAD装置は、部品のインピーダンスの小さい順、特に部品の高周波信号に対するインピーダンスの小さい順に部品優先順位を設定する。具体的には、キャパシタ素子等受動部品のインダクタンス(等価直列インダクタンス(Equivalent Series Inductance:ESLとも呼ばれる。)が小さい部品(あるいは小さいと看做すことができる部品)ほど高い部品優先順位を付ける。この部品優先順位は配置の順位であるので、部品優先順位の高い部品から順番にプリント配線基板に配置される。この場合、部品優先順位の高い部品ほど配置の自由度が大きい、つまり他の部品が配置されていない空きスペースが広いので、電源ピンの直近の最適な位置に配置されることになる。その結果、ESLが小さい部品ほど高周波ノイズに対するインピーダンス値が小さいので、本CAD装置は、より高周波のノイズ信号を低減する部品ほどが電源ピンの直近に配置することができる。

<構成>

図3は、本発明の実施の形態1におけるCAD装置1000の構成を示すブロック図である。CAD装置1000は、図4に示すワークステーションなどのコンピュータ・ハードウェア上で、図3に示した各ブロックの機能を実現するソフトウェアを実行することにより実現している。このコンピュータ・ハードウェアは、マイクロプロセッサ、RAM、ROM、ハードディスク装置、ディスプレイ装置、キーボード、マウスなどから構成される。

【0016】

図3においてCAD装置1000は、コマンド入力部1101、データ入力部1102、コマンド入力解析部1104、制御部1103、部品検出部1105、部品優先順位設定部1106、配置部1107、設計情報記憶部1108、表示部1109から構成される。説明の便宜上、1101、1102、1109、1104、1103、1108、1105、1106、1107の順に説明する。

【0017】

コマンド入力部1101は、キーボード、マウスなどに対するユーザ操作による各種コマンドを受け付ける。

データ入力部1102は、回路図設計CAD装置(図外)などにより作成された回路図情報の入力を受け付ける。受け付けられた回路図情報は設計情報として設計情報記憶部1108に格納される。

【0018】

表示部1109は、プリント配線基板を設計過程に応じてプリント配線基板上の部品の配置図、配線図、ユーザ操作入力ボックスなどを表示する。

コマンド入力解析部1104は、コマンド入力部1101により受け付けられたコマンドを解析して、そのコマンドの種別を判定し、種別に応じてCAD装置1000を構成する各部に対してコマンドを出力する。コマンドの種別には、回路図情報の入力コマンド、プリント配線基板への部品配置を指示する配置コマンド、配置された部品間を配線する配線コマンド等がある。

【0019】

本実施例では配置コマンドとして第1、第2配置コマンドの2種類あるものとする。第1配置コマンドは大物部品(IC等の能動部品、コネクタなど)の配置を指示する。第2配置コマンドは大物部品以外の小物部品(キャパシタ素子、インダクタ素子、抵抗素子等受動素子など)の配置を指示する。第2配置コマンドは第1配置コマンドより後にコマンド入力部1101において入力される。

【0020】

制御部1103は、コマンド入力部1101、データ入力部1102、コマンド入力解析部1104、CAD装置1000全体を制御する。特に、制御部1103は、コマンド入力解析部1104より第2配置コマンドを受け取った場合、部品検出部1105および部品優先順位設定部1106をこの順に起動する。これにより、部品優先順位設定部1106によって特定種類の部品に対して上記部品優先順位が設定される。さらに、制御部1103は部品優先順位に従い部品を選択し、選択した部品を配置部1107に配置させる。

【0021】

設計情報記憶部1108は、データ入力部1102に受け付けられた回路図情報に基づいて作成されるプリント配線基板の設計情報を記憶する。設計情報は、(1)部品情報リスト、(2)部品マスタ情報リスト1301、(3)有効周波数域情報リスト、(4)部品形状情報リスト1701とを含む。

(1)部品情報リスト

部品情報リストは、回路情報が示す回路を構成する部品毎のプリント配線基板上の配置に関する情報からなるリストである。

【0022】

図5は、部品情報リストの具体的な一例を示す図である。同図において部品情報リスト1201は、各部品についての部品番号1202、部品名1203、部品形状1204、配置面1205、基準点座標1206、優先順位1207、主部品番号1208、付随部品番号1209、部品グループ1210の各欄を含む。部品情報リスト1201の各行は1部品についての部品情報を表す。

【0023】

このうち、部品番号1202、部品名1203、部品形状1204は、データ入力部1102によって受付けられた回路情報から直接部品情報リスト1201に設定される。残りはCAD装置1000の設計段階に応じて順次設定される。本実施形態では、主部品番号1208、付随部品番号1209、部品グループ名1210は、ユーザによりコマンド入力部1101から入力されたものとし、部品グループ名1210は設定されていなくてもよい。

【0024】

部品番号1202は、回路中の各部品を識別する番号を示す。

部品名1203は、部品に対応する部品マスタ情報を識別する名称を示す。

部品形状1204は、部品形状を識別する識別子である。

配置面1205は、部品の配置されるプリント配線基板の面を識別する識別子を示す。配置面はプリント配線基板の一方の面をA面と他方をB面とする。

【0025】

基準点座標1206は、部品の配置される(X,Y)座標を示す。

優先順位1207は、部品配置の優先順位を示す番号を示す。優先順位1207は全ての部品について設定されるとは限らず、ノイズ対策用の部品に対して部品優先順位設定部1106によって設定される。

主部品番号1208は、部品が付随部品である場合に、対応する主部品の部品番号を示す。ここで、主部品はIC、コネクタ等の部品を、付随部品は、キャパシタ素子、インダクタ素子、抵抗素子、フィルタ素子等などの部品をいう。主部品、付属部品という用語は、プリント基板上のできるだけ直近に配置することが望ましい関係にある部品を区別するために用られる。主部品はノイズ発生源となりノイズ対策を必要とする部品、付属部品はノイズ対策用の部品を示す。配置部1107によって、主部品は付属部品よりも先に配置され、付属部品は主部品のできるだけ直近に配置される。

【0026】

付随部品番号1209は、当該部品(主部品)に割付けられた付随部品をの部品番号を示す。本実施形態では、ユーザによって主部品に対して付属部品が割り当てられているものとする。つまりユーザによって、主部品番号1208、付随部品番号1209が設定されたものとする。

部品グループ1210は当該部品の所属するグループを識別する識別子を示す。本実施形態では設定されてなくてもよい。

【0027】

なお、リスト中の「−」はその項目が設定されていないことを示す。

(2)部品マスタ情報

部品マスタ情報リストは、個々の部品の特性を示す部品マスタ情報からなるリストを示す。

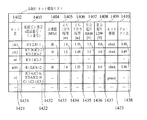

図6は、部品マスタ情報リスト1301の具体的な一例を示す。同図において部品マスタ情報リスト1301は、各部品マスタについての部品名1302、部品種類1303、ピン数1304、L値1305、C値1306、R値1307、内部クロック−電源ネット名1308、有効周波数MIN1309、有効周波数MAX1310の各欄を含む。本実施形態では1307〜1310の各欄は設定されていなくてもよい。

【0028】

部品マスタ情報リスト1301中の各行は1つの部品マスタ情報を表す。

部品名1302は、部品名を識別する識別子を示す。

部品種類1303は部品種類を識別する識別子を示す。部品種類には、集積回路部品を示すIC,キャパシタ素子を示すC,抵抗素子を示すR、インダクタ素子を示すL,コネクタ部品を示すCNなどがある。

【0029】

ピン数1304は、部品のピン数を示す。

L値1305、C値1306、R値1307は、それぞれ部品のインダクタンス値、容量値、抵抗値を示す。これらは、部品種類に応じて設定される。

内部クロック−電源ネット名1308は、部品の内部クロックとその内部クロックの使用する電源ネット名とを示す。全ての部品に内部クロック−電源ネット名が示されているとは限らない。例えば「33MHz−vcc2」は、内部クロックの周波数が33MHzであり、その内部クロック用の電源ネット名がvcc2であることを示している。

【0030】

有効周波数MIN1309、有効周波数MAX1310は、それぞれ当該部品が有効に動作する最低周波数、最高周波数を示す。

(3)有効周波数域情報リスト

有効周波数域情報リストは、キャパシタ素子や、抵抗素子などの受動素子における等価直列インダクタンス(ESL)の値や、有効周波数域を記憶しておくリストである。有効周波数域情報リストは、インダクタ素子以外のノイズ対策用部品のピン間距離を、等価直列インダクタンス及び有効周波数域に換算するためのリストである。

【0031】

図9は、有効周波数域情報リストの具体的な一例を示す図である。同図において有効周波数域情報リスト1601は、ピン間距離1602、インダクタンス値1603、有効周波数域1604の各欄を含む。有効周波数域情報リスト1601中の各行は1つの有効周波数域情報を示す。

ピン間距離1602は、キャパシタ素子や、抵抗素子、インダクタ素子などの受動素子における第1ピンと第2ピンの距離を示す。レジスタアレイなどの部品の場合、内部で接続している第1のピンと第2のピンの距離を、3端子フィルタなどでは、グランドピン以外の第1のピンと第2のピンの距離を示す。

【0032】

インダクタンス値1603は、ピン間距離1602に対応する等価直列インダクタンス(ESL)を示す。インダクタ素子以外のキャパシタ素子及び抵抗素子については、ピン間距離が短いほどESLも小さいと考えられる。

有効周波数域1604は、ピン間距離1602に対応する有効周波数域を示す。有効周波数域は、ESLが小さいほど高くなると考えられる。ESLによるインピーダンスが小さいほど、インピーダンス値も小さくなり、有効周波数域が高くなると考えられる。

【0033】

インダクタンス値1603及び有効周波数域1604の値は、予めユーザにより設定される。これらの値は実験により求めた値や経験的に見出した値であってもよい。

(4)部品形状情報リスト1701

部品形状情報リストは部品毎の形状を示す部品形状情報のリストである。

【0034】

図10は、部品形状情報リストの具体的は一例を示す図である。同図において、部品形状情報リスト1701は、部品形状1702、最小最大領域1703、ピン番号1704、ピン座標1705、ピン間距離1706の各欄から構成される。

部品形状1702は、部品形状を識別する識別子を示す。

【0035】

最小最大領域1703は、部品の外形を示す座標の組であり、部品外形の左上座標と右下座標の組である。同図では左上座標を(0、0)とする相対座標になっている。各座標は(X、Y)座標である。

ピン座標1705は、ピン番号1704が示すピン毎に、部品情報に示した部品の基準点座標1206に対する、ピンの相対座標を示している。

【0036】

ピン間距離1706は、部品の第1のピンと第2のピンの基準座標間の距離を示している。

図3において、部品検出部1105は、制御部1103の制御の下で、設計情報記憶部1108に記憶されている部品情報リスト1201、部品マスタ情報リスト1301、部品形状情報リスト1701から、各部品についての部品情報、部品マスタ情報、部品形状情報を読み出し、部品優先順位設定部1106又は配置部1107に渡す。また、部品検出部1105は、部品優先順位を設定すべき部品の種類(上記特定種類)を記憶している。本実施例では記憶されている特定種類は、(A)キャパシタ素子、(B)キャパシタ素子およびインダクタ素子、(C)キャパシタ素子、インダクタ素子および抵抗素子などがユーザにより設定される。

【0037】

部品優先順位設定部1106は、部品検出部1105によって読み出された情報を参照して、上記特定種類の部品に対して部品優先順位を部品情報中に設定する。その際、部品検出部1105に記憶されている特定種類が上記(A)(B)(C)の何れであるかにより設定する処理が若干異なる。

すなわち、部品検出部1105に記憶されている特定種類が(A)キャパシタ素子である場合には、部品優先順位設定部1106は、特定種類の部品に対して容量の小さい順に部品優先順位を設定する。ここでは、部品優先順位設定部1106は、容量の小さい部品ほどESLが小さいとみなしている。また、特定種類が(B)キャパシタ素子およびインダクタ素子である場合には、部品優先順位設定部1106は、特定種類の部品に対して、図9の有効周波数域情報リスト1601に従って部品のピン間距離をESL値に換算し、そのESL値の小さい順に部品優先順位を設定する。特定種類が(C)キャパシタ素子、インダクタ素子及び抵抗素子である場合には、部品優先順位設定部1106は、特定種類の部品に対して、図9の有効周波数域情報リスト1601に従って部品のピン間距離を有効周波数域に換算し、その有効周波数域の高い順に部品優先順位を設定する。

【0038】

配置部1107は、制御部1103より部品番号1230を受け取り、部品を配置し配置処理を終了する。通常、部品優先順が設定された部品には主部品番号が付与されている。配置部1107は、主部品番号が付与されている場合には、当該部品を主部品番号のできるだけ近くに配置する。

<部品優先順位設定部1106の詳細>

部品検出部1105に記憶された特定種類が(A)キャパシタ素子の場合、(B)キャパシタ素子およびインダクタ素子の場合、(C)キャパシタ素子、インダクタ素子および抵抗素子の場合に分けて、部品優先順位設定部1106における部品優先順位設定処理を説明する。

(A)の場合、

図11は、部品優先順位設定部1106における部品優先順位設定処理(A)の詳細を示すフローチャートである。

【0039】

同図において、部品優先順位設定部1106は、部品検出部1105により読み出された全ての部品情報(図5参照)に対してループ1の処理(S101〜S106)を行なう。すなわち、部品優先順位設定部1106は、1部品に対応する部品情報から部品番号と部品名とを読み出し(S102)、読み出された部品名に対応する部品マスタ情報(図6参照)からC値と部品種類を読み出し(S103)、その部品種類が部品検出部1105に記憶されている特定種類(ここではキャパシタ素子)に該当する場合には(S104:Yes)、メモリ(図外)中の作業領域に部品番号とC値とを登録する(S105)。

【0040】

部品情報毎にS102〜S105を繰り返すことにより、ループ1の処理終了後には、作業リストは特定種類に該当する全ての品について部品番号とC値との組みをループ1処理にて登録された順に保持することになる。

さらに、部品優先順位設定部1106は、作業リストの組をC値の小さい順に並び替え(S107)、並び替え後の順に同順の部品優先順位を部品情報リスト1201に対して設定する(S108)。その結果、部品情報リスト1201中のキャパシタ素子に対してC値の小さい順に部品優先順位が設定される。

【0041】

なお、図11ではC値の小さい順をESLの小さい順と看做しているが、C値の代わりにキャパシタ素子のピン間距離を用いてもよい。つまり、ピン間距離の小さい順をESLの小さい順と看做してもよい。一般にピン間距離が小さいほど、ESLも小さいからである。その場合、上記S103において、C値の代わりにピン間距離を部品形状情報リスト1701から読み出す構成とすればよい。その結果、作業リストはピン間距離の小さい順に並び替えられた上記組を保持することになり、ピン間距離の小さい順に部品優先順位が設定されることになる。

(B)の場合

図12は、部品優先順位設定部1106における部品優先順位設定処理(B)の詳細を示すフローチャートである。同図は、図11と同じステップには同じステップ番号を付与しているので説明を省略し、異なるステップを中心に説明する。

【0042】

図12のフローチャートは、図11におけるS102、S103、S105、S107の代わりにS102a、S103a、S105a〜c、S107aを有する点が異なっている。もちろん、部品検出部1105に記憶される特定種類は上記(B)になっている。

S102a、S103aでは、部品優先順位設定部1106は、S102の処理に加えて、図5の部品形状1204欄から部品形状の識別子も読み出し、S103におけるC値を読まない点が異なる。

【0043】

S104にて特定種類と判定された後、部品優先順位設定部1106は、S102aにおいて読み出された部品形状の識別子に対応する部品形状情報(図10参照)からピン間距離を読み出し(S105a)、そのピン間距離に対応するインダクタンス値を有効周波数域情報リスト1601から読み出し(S105b)、部品番号とインダクタンス値とを作業リストに登録する(S105c)。

【0044】

部品情報毎にS102a〜S105cを繰り返すことにより、ループ1の処理終了後には、作業リストは特定種類に該当する全ての品について部品番号とインダクタンス値との組をループ1処理にて登録された順に保持することになる。

さらに、S107aにおいて、部品優先順位設定部1106は、作業リストの組をインダクタンス値の小さい順に並び替える。

【0045】

その結果、部品情報リスト1201中のキャパシタ素子及びインダクタ素子に対してインダクタンス値(ESL)の小さい順に部品優先順位が設定される。

なお、S105bにおいて有効周波数域情報リスト1601のインダクタンス値ではなく部品マスタ情報リスト1301のL値を読み出すようにしてもよい。

(C)特定種類がキャパシタ素子、インダクタ素子および抵抗素子である場合

図13は、部品優先順位設定部1106における部品優先順位設定処理(C)の詳細を示すフローチャートである。同図は、図12と同じステップには同じステップ番号を付与しているので説明を省略し、異なるステップを中心に説明する。

【0046】

図13のフローチャートは、図12におけるS105b、S105c、S107aの代わりにS105p、S105q、S107pを有する点が異なっている。もちろん、部品検出部1105に記憶される特定種類は上記(C)になっている。S105p、S105q、S107pの処理では、インダクタンス値の代わりに有効周波数域を用いる点が異なっている。

【0047】

さらに、S107aにおいて、部品優先順位設定部1106は、作業リストの組をインダクタンス値の小さい順に並び替える。

その結果、部品情報リスト1201中のキャパシタ素子、インダクタ素子及び抵抗素子に対してインダクタンス値(ESL)の小さい順に部品優先順位が設定される。

<制御部1103による制御動作>

制御部1103がコマンド入力解析部1104より第2配置コマンドを受け取って、制御部1103の制御により小物部品の配置が終わるまでの処理について説明する。

【0048】

図14は、第2配置コマンドを受け取ってから小物部品の配置が終わるまでのCAD装置1000の動作を示すフローチャートである。既に第1配置コマンドに従って大物部品の配置が完了しているものとする。

制御部1103は、コマンド入力解析部1104より第2配置コマンドを受け取ると、部品検出部1105を起動する(S1101)。部品検出部1105は設計情報記憶部1108から部品情報を読み出す。次に、制御部1103は、部品優先順位設定部1106を起動する(S1102)。起動された部品優先順位設定部1106は、部品検出部1105に読み出された部品情報を参照して部品情報リスト1201中に部品優先順位を設定する(図11〜図13参照)。

【0049】

次に制御部1103は、部品優先順位設定部1106にて設定された部品優先順位を読み出し、読み出しが終了していなければ(S1103)、部品優先順位に従い部品を配置部1107に配置させる(S1104)。この配置では、付属部品は主部品のできるだけ近くに配置される。部品優先順位の読み出しが終了するまで、この処理を繰り返す。

【0050】

このように、部品優先順位の高い部品は低い部品と比べて、プリント基板上の配置スペースが広いので配置の自由度が大きく、より最適な位置に配置されることになる。

以上説明したように、本実施の形態におけるCAD装置によれば、特定種類の部品について、容量またはピン間距離が小さいほど、ESLまたはインピーダンス値が小さい(または有効周波数域が高い)部品であると看做して、ESLが小さい順に部品優先順位を設定し、部品優先順位の順に配置を行う。

【0051】

その結果、ノイズ対策用部品の配置順序はインピーダンスの小さい順(ESLの小さい順)になるので、インピーダンスの小さいノイズ対策用部品ほど配置の自由度を大きくなる。その結果、ノイズ特性の良好な配置を行うことができる。なぜなら、インピーダンスの小さい(ESLの小さい)部品ほど高い周波数のノイズを低減するが、周波数が高いノイズ対策部品ほど配置の制約が大きいつまり主部品のできるだけ近くに配置しなければならないからである。

【0052】

また、部品形状情報リスト1701はピン間距離をインダクタンス値または有効周波数域に換算する表であるので、部品優先順位設定部1106は異なる種類のノイズ対策用部品(キャパシタ素子、インダクタ素子、抵抗素子、フィルタ素子など)を同列に部品優先順位を設定することができる。

なお、上記実施形態では部品検出部1105に記憶されている特定種類として(A)(B)(C)の3例を挙げているが、(B)(C)については、キャパシタ素子、インダクタ素子、抵抗素子、フィルタ素子などの一般にノイズ対策用部品種類の任意の組み合わせとしてよい。また、部品優先順位設定部1106は、(B)(C)の場合にインダクタンス値の小さい順、有効周波数域の高い順のいずれを部品優先順位としてもよい。

(実施の形態2)

<概要>

実施の形態1におけるCAD装置では、有効周波数域は、図9に示した有効周波数域情報リスト1601によりピン間距離から換算された値を利用しているが、本実施の形態におけるCAD装置は、部品の容量値やインダクタンス値からf−Z特性(周波数対インピーダンス値特性)を算出して、f−Z特性から有効周波数域を算出し、部品マスタ情報リスト1301に設定する点が異なっている。

<構成>

図15は、本実施の形態におけるCAD装置2000の構成を示すブロック図である。

【0053】

同図のCAD装置2000の構成要素のうち、CAD装置1000の構成要素と同じ符号を付した構成要素はCAD装置1000と同じであるので説明を省略し、異なる構成要素を中心に説明する。

CAD装置2000は、図3に示したCAD装置1000と比べて、制御部1103の代わりに制御部2101を、部品優先順位設定部1106の代わりに部品優先順位設定部2103を備える点と、新たに有効周波数域設定部2102を備える点とが異なっている。

【0054】

制御部2101は、コマンド入力解析部1104より第2配置コマンドを受け取ると、部品検出部1105を起動して部品情報を取り出させた後、有効周波数域設定部2102、部品優先順位設定部2103をこの順で起動する。これ以外は制御部1103と同様である。

部品優先順位設定部2103は、図11、図12に示した部品優先順位設定処理(A)(B)については制御部1103と同じであるが、図13に示した部品優先順位設定処理(C)については、一部分異なっている。

【0055】

図16は、特定種類が(C)キャパシタ素子、インダクタ素子、抵抗素子である場合の部品優先順位設定部2103における部品優先順位設定処理(C’とする)を示すフローチャートである。

同図は、図13のS105a及びS105p(ピン間距離から有効周波数域への換算)の代わりに、S105tを有する点が異なっている。

【0056】

S105tにおいて部品優先順位設定部2103は、有効周波数域設定部2102によって部品マスタ情報に設定された有効周波数MAX1310を読み出す。その結果、部品優先順位は、図13のS105q以降の処理において、有効周波数域設定部2102に算出された有効周波数MAX1310の高い順に設定される。

【0057】

有効周波数域設定部2102は、制御部2101から特定種類の部品についてC値、L値又はその両方の値が通知されると、その値に基づいて当該部品がどの周波数範囲においてノイズ対策(EMI対策)に有効であるかを算出する。具体的には、有効周波数域設定部2102は、あらかじめ定められた閾値Thを記憶しており、制御部2101より部品番号1230のC値1323とL値1322のうちどちらか一方、または両方の値を受け取り、C値1323とL値1322のうち、どの値を受け取ったか判定し、受け取った値に応じて、f−Z特性(例えば、ある間隔の周波数ごとの各インピーダンス値)を次のように算出し、インピーダンス値が上記の閾値Thよりも小さくなる周波数範囲を有効周波数範囲として求める。

【0058】

C値1323のみを受け取った場合のインピーダンス値Z(f)を(数1)に示す。

(数1)

Z(f)=|1/(2πfC)|

L値1322のみを受け取った場合のインピーダンス値Z(f)を(数2)に示す。

(数2)

Z(f)=|2πfL|

C値1323、L値1322の両方を受け取った場合のインピーダンス値Z(f)を(数3)に示す。

(数3)

Z(f)=|2πfL-(1/(2πfC))|

有効周波数域設定部2102は、f−Z特性におけるインピーダンス値と閾値とを比較し、閾値よりインピーダンス値が小さい部分(Th>Z(f))を有効周波数域として求めて、部品マスタ情報リスト1301の有効周波数MIN1309および有効周波数MAX1310に設定する。

【0059】

図17は、有効周波数域設定部2102が、制御部2101からL値1322のみを受け取った場合に算出されたf−Z特性の一例を示す。同図では、有効周波数域設定部2102は、インピーダンス2201(Z(f))と前記閾値2202(Th)を比較し、閾値2202よりインピーダンス2201が小さい部分(交点2205より左側)を有効周波数域として、部品マスタ情報リスト1301に設定する。

【0060】

図18は、有効周波数域設定部2102が、制御部2101からC値1323のみを受け取った場合に算出されたf−Z特性の一例を示す。同図では、有効周波数域設定部2102は、閾値2202よりインピーダンス2201が小さい部分(交点2204より右側)を有効周波数域として部品マスタ情報リスト1301に設定する。

【0061】

図19は、有効周波数域設定部2102は、制御部2101からL値1322とC値1323の両方を受け取った場合に算出されたf−Z特性の一例を示す。

同図では、閾値2202よりインピーダンス2201が小さい部分(交点2204と交点2205との間の部分)を有効周波数域として設定する。

上記の図17から図19では閾値Thを1Ωとしている。ここでは、有効周波数域は、当該部品が1Ωより小さいインピーダンスで高周波電流を流す(又はICの電源ピンに供給する)ことができる周波数の範囲を意味する。なお、閾値Thは1Ωでなくても当該部品が流す必要がある(又はICの電源ピンに供給する必要がある)高周波電流の容量に応じて値を定めれば良い。また、閾値は、デフォルト値として1[Ω]などの値を記憶しておくか、ユーザにより入力させても良い。

【0062】

有効周波数域の算出結果として、有効周波数域設定部2102は、部品マスタ情報リスト1301に、有効周波数域の下限を示す有効周波数MIN1309に周波数2204と、有効周波数域の上限を示す有効周波数MAX1310に周波数2205とを記す。

部品優先順位設定部2103は、部品マスタ情報の有効周波数MAX1310を読み出し、有効周波数MAX1326の高い周波数の順に部品優先順位1233を設定する。その結果、特定種類の部品(付属部品)は部品優先順位と同順で、主部品のできるだけ近くに配置される。その結果、有効周波数MAX1326の高い部品ほど配置の自由度が高いので、ノイズ特性の良好な配置を可能にしている。

<制御部2101による制御動作>

制御部2101がコマンド入力解析部1104より第2配置コマンドを受け取って、制御部2101の制御により小物部品の配置が終わるまでCAD装置2000の処理について説明する。

【0063】

図20は、第2配置コマンドを受け取ってから小物部品の配置が終わるまでのCAD装置2000の動作を示すフローチャートである。既に第1配置コマンドに従って大物部品の配置が完了しているものとする。

同図は、図14に示したフロチャートに対して、S1101とS1102の間にS2102およびS2103を追加している点が異なり、これ以外は同様である。

【0064】

制御部2101は、コマンド入力解析部1104より第2配置コマンドを受け取ると、部品検出部1105を起動する(S1101)。これにより部品検出部1105は設計情報記憶部1108から部品情報を読み出す。次に、制御部2101は、読み出された部品情報から、部品番号1230を読み出し、特定種類の部品全てについて有効周波数域の設定が完了していなければ(S2102)、部品情報の部品名に対応する部品マスタ情報からL値、C値を読み出し、有効周波数域設定部2102にこれらのL値、C値から有効周波数域を設定させる(S2103)。これにより、有効周波数域設定部2102は有効周波数MIN1309と有効周波数MAX1310を部品マスタ情報リストに書き込む。

【0065】

制御部2101は、S2102にてすべての部品情報(部品番号)の読み出しが終了していれば、部品優先順位設定部2103を起動する(S1102)。起動された部品優先順位設定部2103は、特定種類が(C)キャパシタ素子、インダクタ素子、抵抗素子の場合に、図16に示したように、ピン間距離を有効周波数域に換算するのではなく、部品マスタ情報に設定された有効周波数MAXを読み出す点以外は図14のS1101と同様に部品優先順位を設定する(S2103)。これ以降の処理は実施の形態1と同様である。

【0066】

以上説明してきたように本実施の形態におけるCAD装置によれば、特定種類の部品の優先順位つまり配置順位を部品マスタ情報に設定された有効周波数MAX1310の高い順番に設定する。

このように、部品優先順位設定部2103は、有効周波数域情報リスト1601を用いてピン間距離を有効周波数域に換算することなく、L値、C値から有効周波数域MAXを算出する。

【0067】

なお、有効周波数を、実施の形態1のようにピン間距離から換算するか、本実施の形態のようにL値、C値から算出するかは、ユーザ操作により選択するようにCAD装置2000を構成してもよい。

また、本実施の形態では、有効周波数域設定部2102は、部品マスタ情報リスト1301に含まれるL値を用いて有効周波数域を算出しているが、このL値の代わりに、部品形状情報リスト1701のピン間距離を読み出し、有効周波数域情報リスト1601を参照してピン間距離に対応するインダクタンス値1611を用いて有効周波数域を算出するように構成してもよい。

【0068】

なお、本実施の形態では、部品情報リスト1201に設定される有効周波数MIN1325と有効周波数MAX1326は、部品マスタ情報リスト1301中のL値とC値を基に算出されているが、L値とC値が不明な場合などには、ピン間距離1713を読み出しから有効周波数域情報リスト1601を参照し、有効周波数域1612を用いても良い。

(実施の形態3)

本実施の形態のCAD装置3000は、実施の形態1のCAD装置1000の機能に加えて、主部品(IC、コネクタ等)と付随部品(キャパシタ素子、インダクタ素子、抵抗素子、フィルタ素子等)との割り付けを次のように行なう。

【0069】

すなわち、CAD装置3000は、主部品の電源ピンのうち、電源ピンを流れる電流に発生すると推定されるノイズの深刻さが大きい電源ピンほど高いピン優先順位を付与し、ピン優先順位の高い電源ピンから順次、部品優先順位の高い付随部品を割り当てていく。ここでノイズの深刻さとは、ノイズ周波数の高さやノイズ電力の強さ等をいう。その結果、深刻なノイズを発生させる電流を流す電源ピンのから優先的に、部品優先順位の高い付随部品が割り当てられることになる。

【0070】

図21は、本実施の形態におけるCAD装置3000の構成を示すブロック図である。同図において、図3と同じ符号の構成要素は同じ機能を有するので説明を省略し、異なる構成を中心に説明する。

図21のCAD装置3000は、図3と比較して、設計情報記憶部1108の代わりに設計情報記憶部3107を備える点と、ネット検出部3102、ピン検出部3103、部品グループ設定部3104、ピン優先順位設定部3105、部品割付け部3106を新たに追加している点と、制御部1103の代わりに制御部3101を備える点とが異なっている。

【0071】

設計情報記憶部3107は、部品情報リスト1201、部品マスタ情報リスト1301、有効周波数域情報リスト1601、部品形状情報リスト1701を記憶する点では図3の設計情報記憶部1108と同じであるが、さらに、ネット情報リスト1401およびピン情報リスト1501を記憶する。

(1)ネット情報リスト1401

図7はネット情報リスト1401の一例を示す図である。ネット情報リスト1401は、部品のピンを接続するネット(つまりどのピンとどのピンとが接続(配線)されるか)を示すネット情報のリストである。

【0072】

図25にネットの説明図を示す。同図では、部品3501、3601、3605、3606、3610とがプリント配線基板のA面に配置される。ネット3701は、部品3501のピンと、部品3601のピンと、部品3605のピンと、部品3606のピンとの接続関係を示す。ネット3705は、部品3501のピンと、部品3610のピンとの接続関係を示す。

【0073】

図7に示すように、ネット情報リスト1401は、ネット毎のネット情報を載せたリストである。ネット情報は、ネット名1402、接続ピン番号1403、周波数1404、立ち上がり時間1405、立ち下がり時間1406、出力電圧HIGH1407、出力電圧LOW1408、ネット種類1409、デューティ比1410からなる。

【0074】

ネット名1402は、ネットを識別する識別子である。

接続ピン番号1403は、ネットに接続すべき部品のピン(接続ピン)を示す。接続ピンは(部品を識別する部品番号)−(当該部品のピンを識別するピン番号)と表記される。例えば"IC1-2"は、部品番号がIC1のIC部品におけるピン番号1のピンを示す。また"R1-1"は部品番号がR1の抵抗素子におけるピン番号1のピンを示す。また接続ピン番号1403には、部品を識別する部品番号と、前記部品上のピンを識別するピン番号とが、「−」により結合されたものが、少なくとも1つ含まれる。

【0075】

周波数1404は、ネットに流される信号の周波数を示す。

立ち上がり時間1405、立ち下がり時間1406は、それぞれネットに流される信号の立ち上がり時間、立下り時間を示す。

出力電圧HIGH1407、出力電圧LOW1408は、それぞれネットに流される信号の出力がHIGH、LOWの時に流される電圧を示す。

【0076】

ネット種類1409は、ネットの種類を識別する識別名である。ネットの種類には、電源供給用の「power」、0V用の「ground」、クロック信号等高速な信号用の「clock」、これら以外の一般的な信号用の「normal」などがある。

デューティ比1410は、ネットに流される信号のデューティ比を示している。

【0077】

上記周波数1405からデューティ比1410は、全てのネットに示されているとは限らない。同図において「−」は、その項目が示されていないことを示す。

(2)ピン情報リスト1501

図8はピン情報リスト1501の一例を示す図である。同図に示すように、ピン情報リスト1501は、ピン情報からなるリストであり、ピン情報は、部品番号1502、ピン番号1503、ピン名1504、電源ネット名1505、電源ピン番号1506、周波数1507、立ち上がり時間1508、立ち下がり時間1509、出力電圧HIGH1510、出力電圧LOW1511、優先順位1512、使用周波数MIN1513、使用周波数MAX1514、ピン種類1515、消費電流1516、デューティ比1517からなる。

【0078】

部品番号1502は、ピンの属する部品を識別する識別子であり。ピン番号1503は、ピンを識別する識別子である。ピン名1504はピンの名前を識別する識別子である。

電源ネット名1505は、ピンに接続されるIC内部回路に流れる電流を供給している電源ネット名の識別子である。

【0079】

電源ピン番号1506は、ピンに接続されるIC内部回路に流れる電流を供給している電源ピンの番号を識別する識別子である。

周波数1507は、ピンを接続するネットに流されている信号の周波数を示す。

立ち上がり時間1508、立ち下がり時間1509は、それぞれピンに接続するネットに流されている信号の立ち上がり時間、立ち下がり時間を示す。

【0080】

出力電圧HIGH1510、出力電圧LOW1511は、それぞれピンに接続するネットに流されている信号の出力がHIGH、LOWの時に流される電圧を示す。

優先順位1512は、そのピンの優先順位を示す。

使用周波数MIN1513、使用周波数MAX1514は、それぞれピンに接続するネットに流れる信号の周波数成分のうち、最も低い周波数、もっとも高い周波数を示す。

【0081】

ピン種類1515は、ピンに接続するネットの種類を示す。ネットの種類は「normal」、「power」「ground」、「clock」などがある。

消費電流1516は、ピンに接続するネットに流れる信号の成分の消費電流を示す。

【0082】

デューティ比1517は、ピンに接続するネットに流れる信号のデューティ比を示している。

上記周波数1507〜デューティ比1517は、当然ながら電源ピンにはもともと設定されてはいないが、本実施形態では電源ピンに対しても優先順位設定部3105により設定される。また、同図において「−」は、その項目が示されていないことを示す。

【0083】

ネット検出部3102は、制御部3101の制御の下で、全てのネット情報を順に読み出す。読み出されたネット情報は、主に部品グループ設定部3104に用いられる。

ピン検出部3103は、制御部3101の制御の下で、設計情報記憶部3107に記憶されているピン情報リスト1501から、全てのピン情報を順に読み出す。読み出されたピン情報リスト1501は、主にピン優先順位設定部3105、部品割付け部3106に用いられる。

【0084】

部品グループ設定部3104は、部品検出部1105により読み出された部品情報リスト1201(図5参照)に対して部品情報毎に部品グループ名1210を設定する。部品グループ名は第1の部品グループを”1”、第2の部品グループを”2”とする。第1の部品グループ名”1”は、IC部品及びコネクタ部品を第1の部品グループに属する部品(主部品)であることを示す。第2の部品グループ”2”は、抵抗素子、キャパシタ素子、インダクタ素子及びフィルタ素子を第2の部品グループに属する部品(付随部品)であることを示す。部品グループ設定部3104は、部品検出部1105により読み出された部品情報リスト1201(図5参照)中の部品名1221をキーにして、部品検出部1105に読み出された部品マスタ情報リスト1301(図6参照)中の部品マスタ情報13からキーに対応する部品種類1331を取り出し、取り出した前記部品種類が第1の部品グループに含まれていれば”1”を、第2の部品グループに含まれていれば”2”を、部品グループ1210に書き込む。

【0085】

たとえば、図5における部品番号1220”IC1”の部品は、部品名1221が”MN1”であり、さらに図6における部品マスタ情報リスト1301によれば部品名1330”MN1”の部品種類はICであるので、部品グループ設定部3104は、図5における部品番号1220”IC1”に対して部品グループ1222を”1”に設定する。なお、部品グループは2つよりも多くてもよい。部品グループ設定部3104は、部品情報リスト1201中の全ての部品について部品グループ1210の設定が終了すれば、処理を終了する。ただし、どのグループに属さない部品には「−」を設定する。

【0086】

ピン優先順位設定部3105は、電源ピンに対して、ピン優先順位を設定する。ピン優先順位は、1つの電源ネットに接続される電源ピンについて、当該電源ピンから供給される電流により駆動される信号の周波数が高い順に(又は立ち上がり時間/立ち下がり時間の速い順に)設定される。

電源ピンには供給される電源はそもそも論理的には直流なので、周波数に関する情報が存在しないが、ピン優先順位設定部3105は、電源ピンの近くの高周波信号用ピン(「clock」)であって当該電源ピンからIC内部で電流の供給を受けている場合には、当該「clock」信号用のピンの周波数に関する情報を、電源ピンの周波数に関する情報として、利用する。この利用は、実質的に、各電源ピンが供給すべき電流の高周波成分を検出していることになる。

【0087】

図22は、ピン優先順位設定部3105による詳細なピン優先順位設定処理を示すフローチャートを示す。

同図のようにピン優先順位設定部3105は、図8に示したピン情報リスト1501における全ての高周波信号(ピン種類が「clock」)のピンについて、以下を繰り返す(ループ1:S3105a〜S3105d)。すなわち、ループ1においてピン優先順位設定部3105は、高周波信号ピンに対して電源ピン番号1506が設定されているか否かを判定し(S3105b)、設定されていると判定した場合にはピン情報リスト1501における高周波信号ピンのデータを設定されていた電源ピンのデータとしてコピーする(S3105c)。ここでいうデータは、周波数1507、立ち上がり時間1508、立ち下がり時間1509、出力電圧HIGH1510、出力電圧LOW1511をいう。

【0088】

例えば、図8における高周波信号線のピンclk1(ピン名1531)については、ピン優先順位設定部3105はそのデータ(周波数1535、立ち上がり時間1536、立ち下がり時間1537、出力電圧HIGH1538、出力電圧LOW1539)を、電源ピン4(ピン番号1551)のデータ欄(周波数1555、立ち上がり時間1556、立ち下がり時間1557、出力電圧HIGH1558、出力電圧LOW1559)にコピーする。図8ではコピー後のデータを記してある。

【0089】

同様にして、ピン優先順位設定部3105は、他の高周波信号線のピンに対して設定された電源ピン番号1506の電源ピンにデータをコピーし、全ての高周波信号線のピンに対して処理を終えればループ1の処理を終える。

次に、ピン優先順位設定部3105は、全電源ネットに対して以下を繰り返す(ループ2:S3105e〜S3105i)。すなわち、ピン優先順位設定部3105は、図7のネット情報リスト1401におけるネット種類「power」のネット名を読み出し(例えばVcc1)、そのネットに接続される接続ピン番号1403を全て読み出し(S3105f)、読み出された各接続ピン番号に対応する周波数に関する情報(周波数1507、立ち上がり時間1508、立ち下がり時間1509)を図8のピン情報リスト1501から読み出し(S3105g)、当該ネットに接続される接続ピンに対して、周波数の高い順に(又は立ち上がり時間、立ち下がり時間の速い順に)ピン優先順位1512をピン情報リスト1501に設定する(S3105h)。このようにして、ネット種類「power」のネット毎に、当該ネットに接続されるピンに対してピン優先順位が設定される。

【0090】

部品割付け部3106は、ピン優先順位の高い順に第1の部品グループに属する部品の電源ピンに、部品優先順位の高い第2の部品を割付ける、つまり、図5に示した部品情報リスト1201に対して主部品番号1208、付随部品番号1209を設定する。

図23は、部品割付け部3106における割り付け処理の具体例を示すフローチャートである。

【0091】

同図において、ループ1は全ての電源ネットに対する電源ネット毎の処理を、ループ2は1つの電源ネット内の接続ピン毎の処理を示す。

ループ1において、部品割付け部3106は、図7に示したネット情報のネット種類が「power」である1つのネットについて、接続ピン番号1422欄から全てのピン番号を読み出し(S3106b)、読み出したピン番号毎にループ2処理を行なう。

【0092】

ループ2において、部品割付け部3106は、読み出されたピン番号の1つの属する部品の部品グループ名1210を図5に示した部品情報より参照し、参照した部品グループ名が”1”である場合には、ピン情報内のピン優先順位1512を参照し、メモリ中の作業用領域(以下第1リストと呼ぶ)にそのピン番号とピン優先順位との組を登録する(S3106d、e、f)。また、参照した部品グループ名が”2”である場合には、部品情報から部品優先順位を読み出し、ピン番号と部品優先順位との組みをメモリ中の作業用領域(以下第2リストと呼ぶ)に登録する(S3106d、g、h)。ループ1により、第1リストは第1の部品グループに属する部品のピン番号とピン優先順位の組みを、第2リストは第2の部品グループに属する部品のピン番号と部品優先順位の組みを保持することになる。

【0093】

ループ2完了後、部品割付け部3106は、第1リストに保持された組をピン優先順位の高い順に並び替え(S3106j)、第2リストに保持された組を部品優先順位の高い順に並び替える(S3106k)。この後、部品割付け部3106は、第1及び第2リストを参照して、ピン優先順位の高い第1の部品グループ内の部品に部品優先順位の高い第2の部品グループ内の部品を割り付ける(S3106m)。その際、第1の部品グループの部品数と第2の部品グループの部品数とが異なる場合、第1の部品グループの複数の部品には、各部品の電源ピンの数に比例分配することが望ましい。

【0094】

なお、部品割付け部3106は、第1リストの組と第2リストの組とが同数である場合は、第1、第2リストの並び順に1対1で割り付けてもよい。第1リストの組が第2リストの組よりも多い場合は、同じ部品に属する座標が近い電源ピンを1グループとしグループに対して割り付けれてもよい。また、第1リストの組が第2リストの組よりも少ない場合は、第1、第2リストの先頭から1対1で割当て、第2リストの残りを再度第1リストの先頭から1対1で割り付けれてもよい。

【0095】

この割付け結果、部品割付け部3106は、第1の部品グループ内の部品に割付けられた第2の部品部品グループ内の部品の部品番号を、付随部品として、部品情報の付随部品番号1223に書き込み、第2の部品1230が割付けられた第1の部品1220を主部品番号1234に書き込む。

<制御部3101による制御動作>

制御部3101がコマンド入力解析部1104より第2配置コマンドを受け取って、制御部3101の制御により小物部品の配置が終わるまでCAD装置3000の処理について説明する。

【0096】

図24は、第2配置コマンドを受け取ってから小物部品の配置が終わるまでのCAD装置3000の動作を示すフローチャートである。既に第1配置コマンドに従って大物部品の配置が完了しているものとする。

同図のように、制御部3101は、コマンド入力解析部1104より第2配置コマンドを受け取ると、部品検出部1105に設計情報記憶部3107から部品情報を読み出させ(S3101)、ネット検出部3102に設計情報記憶部3107からネット情報を読み出させ(S3102)、ピン検出部3103に設計情報記憶部3107からピン情報を読み出させる(S3103)。

【0097】

次に、制御部3101は部品グループ設定部3104を起動する(S3104)。起動された部品グループ設定部3104は、部品検出部1105によって詠み出された部品情報と部品マスタ情報を参照し、部品種類1303より部品グループ1210を設定する。さらに、制御部3101は、部品優先順位設定部1106を起動する(S3105)。起動された部品優先順位設定部1106は、部品情報より部品優先順位1207を設定する。次いで、制御部3101は、ピン優先順位設定部3105を起動する(S3106)。起動されたピン優先順位設定部3105は、図22に示したようにピン優先順位1512を設定する。

【0098】

さらに、制御部3101は、部品割付け部3106を起動する(S3107)。部品割付け部3106は、ピン優先順位1512と部品優先順位1207を参照し、図23に示したように第1の部品に第2の部品を割付ける。次に制御部3101は、部品優先順位設定部1106にて部品優先順位の設定された第2の部品を読み出し、読み出しが終了していなければ(S3109)、部品優先順位に従い第2の部品を配置部1107により配置する(S3110)。部品優先順位の読み出しが終了するまで、この処理を繰り返す。

【0099】

上記処理により部品配置された一例を、図27を示す。図27では、第1の部品グループとして部品3501〜3504(IC1〜IC4)が、第2の部品グループとして部品3601〜3609(C1〜C9)がグループ分けされている。部品3501(IC1)には、部品3601、3605、3606(C1、C5、C6)が割り付けられている。部品3502(IC2)には部品3602、3607(C2、C7)が、部品3503(IC3)には部品3603、3608(C3、C8)が、部品3504(IC4)には、部品3604、3609(C4、C9)がそれぞれ割り付けられている。

【0100】

図27と、従来技術で示した図1とを比較すると、容量が小さい(高周波に対してインピーダンスが小さい)キャパシタ素子C6〜C9が、IC1〜IC4に偏ることなく満遍なく割り付けられていることがわかる。

なお、実施の形態3では、ピン優先順位設定部3105は、ピン情報リスト1501における周波数1507の高い順に電源ピンに対してピン優先順位1512を設定していたが、(a)立ち上がり時間1508の速い順、(b)立下り時間1509の速い順、(c)消費電流1516の多い順、(d)消費電力の多い順のいずれかによりピン優先順位1512を設定しても良い。消費電力は、ピン情報リストに新たにユーザ設定可能な項目を追加しても良いし、消費電流1516と出力電圧HIGH1510、出力電圧LOW1511より求めても良い。

【0101】

また、実施の形態3では、ピン優先順位設定部3105は、高周波ピンの内部回路へ電流を供給する電源ピンの特定に電源ピン番号1506を使用していたが、図8の出力電圧HIGH1510が一致する電源ピン(例えばピン番号1531の出力電圧HIGH1538とピン番号1551の出力電圧HIGH1558)のうち、図26に示すように近い電源ピンを選択しても良い。

【0102】

実施の形態3では、ピン優先順位設定部3105は、高周波ピンの内部回路へ電流を供給する電源ピンの特定に電源ピン番号1506を使用していたが、ピン番号1531の電源ネット名1533とピン番号1551のネット名1421が一致する電源ピンのうち、図26に示すように近い電源ピンを選択しても良い。

また、実施の形態3では、ピン優先順位設定部3105は、高周波ピンの内部回路へ電流を供給する電源ピンの特定に電源ピン番号1506を使用していたが、図26に示すようにピン番号3801に近いピン番号3802を電源ピンを選択しても良い。

【0103】

さらに、実施の形態3では、部品割付け部3106は、ピン優先順位1512の高いピンを持つ第1の部品から優先的に、部品優先順位1207の高い第2の部品を割り付けていたが、ピン優先順位1512が示されているピンの数が多い第1の部品から優先的に、部品優先順位1207の高い第2の部品を割り付けても良い。

(実施の形態4)

実施の形態3のCAD装置3000では、ピン情報リスト1501中の周波数1507の高い順に電源ピンに対してピン優先順位1512を設定したが、本実施の形態では、ピン情報リスト1501中の周波数1507ではなく使用周波数MAX1514の高い順にピン優先順位1512を設定する場合について説明する。

【0104】

図28は、本実施の形態におけるCAD装置4000の構成を示すブロック図である。同図において、図21と同じ符号の構成要素は同じ機能を有するので説明を省略し、異なる構成を中心に説明する。

図28のCAD装置4000は、図21と比較して、有効周波数域設定部2102を追加し、部品優先順位設定部1106の代わりに部品優先順位設定部2103を備え、ピン使用周波数域設定部4102を追加し、ピン優先順位設定部3105の代わりにピン優先順位設定部4103を備え、制御部3101の代わりに制御部4101を備える点が異なっている。

【0105】

有効周波数域設定部2102、部品優先順位設定部2103は、実施の形態2の同符号の構成要素と同じなので説明を省略する。

ピン使用周波数域設定部4102は、図8に示したピン情報リスト1501に対して電源ピン毎に使用周波数MAX1514に設定する。

図29は、ピン使用周波数域設定部4102の詳細なピン処理内容を示すフローチャートを示す。

【0106】

同図のようにピン使用周波数域設定部4102は、図8に示したピン情報リスト1501における全ての高周波信号(ピン種類が「clock」)のピンについて、以下を繰り返す(ループ1:S4102a〜S4102e)。すなわち、ループ1においてピン使用周波数域設定部4102は、高周波信号ピンに対して電源ピン番号1506が設定されているか否かを判定し(S4102b)、設定されていると判定した場合にはピン情報リスト1501における高周波信号ピンのデータ(周波数1507、立ち上がり時間1508、立ち下がり時間1509、出力電圧HIGH1510、出力電圧LOW1511)に基づいて(数4)に従って、信号電圧波形を算出し(S4102c)、図32に示すような周波数成分(f−V特性)に分解し、電圧がしきい値(図32の4201の電圧)を上回る最高周波数を、S4102bにて判定された電源ピンの使用周波数MAX1514に設定する(S4102d)。

【0107】

(数4)

V(f)=2・V0・τ・f0・P・Q(f)

ここで、P=(sin(n・π・τ・f0)/(n・π・τ・f0))

Q(f)=(sin(n・π・tf・f0)/(n・π・tf・f0))

V0:出力電位の電位差(出力電圧HIGH−出力電圧LOW)、τ:デューティ比

f0:基本周波数、tf:立ち下がり時間、f:周波数、n:正の整数

なお、(数4)には、立ち下がり時間1537のみを用いるように示されているが、立ち上がり時間1536、立ち下がり時間1537のうち、短い方を採用しても良い。

【0108】

ピン優先順位設定部4103は、電源ピンに対してピン優先順位を設定する。

図30は、ピン優先順位設定部4103におけるピン優先順位設定処理を示すフローチャートである。同図において、図22と同じステップ番号のステップは同じ処理なので説明を省略する。同図は、図22のS3105e〜S3105iにおいて、S3105gの代わりにS4103gを有する。

【0109】

S4103gにおいて、ピン優先順位設定部4103は、S3105fにおいて読み出された各接続ピン番号に対応する使用周波数MAX1514を図8のピン情報リスト1501から読み出す(S3105g)。これにより、ピン優先順位設定部4103は、電源ネット毎に使用周波数MAX1514の高い順にピン優先順位を設定することになる。

<制御部4101による制御動作>

図33は、制御部4101の制御による、第2配置コマンドを受け取ってから小物部品の配置が終わるまでのCAD装置4000の動作を示すフローチャートである。既に第1配置コマンドに従って大物部品の配置が完了しているものとする。

【0110】

同図は、図24、図20と同じステップ番号のステップは同じ処理なので説明を省略し異なる点を説明する。異なる点は、図24のS3106の代わりにS4110を有し、その直前にS4108及びS4109を有する点である。

S2102において部品優先順位が設定された後、制御部4101は、ピン使用周波数域設定部4102にピン使用周波数域ピン優先順位1512を設定させる(S4108、S4109)。S4108及びS4109の詳細は図30に示した。これにより、ノイズの原因となる電圧がしきい値(図32の4201に示した電圧)を越える周波数域の最大値が求められる。

【0111】

さらに、制御部4101は、ピン優先順位設定部4103を起動する(S4110)。起動されたピン優先順位設定部4103は、ピン情報リスト1501中の周波数1507ではなく使用周波数MAX1514の高い順にピン優先順位1512を設定するピン優先順位1512を設定する。

その結果、ピン優先順位の高いつまりピン使用周波数域MAXの高い電流を流す電源ピンに対して、優先的に部品順位の高いノイズ対策部品から順に配置される。

【0112】

尚、実施の形態4では、ピン情報のピン番号1531の電気特性を参照して、信号電圧の周波数成分を算出していたが、部品番号1530とピン番号1531よりネット情報の接続ピン番号1403を検索し、ネット名1431を特定し、その周波数1433、立ち上がり時間1434、立ち下がり時間1435、出力電圧HIGH1436、出力電圧LOW1437、デューティー比1438を参照し、その周波数成分を算出しても良い。

【0113】

尚、実施の形態4では、ピン使用周波数域設定部4102は、ピン情報のピン番号1531のデータに基づいて信号電圧の周波数成分を算出していたが、部品マスタ情報の内部クロック−電源ネット名1308に基づいて信号電圧の周波数成分を算出しても良い。この場合、立ち上がり時間、立ち下がり時間、出力電圧HIGH、出力電圧LOW、デューティー比は部品マスタ情報リスト1301に含まれていないが、これらの項目を部品マスタ情報リスト1301に追加しユーザに入力させても良いし、それらのデフォルト値をCAD装置4000が保持していても良い。

(実施の形態5)

本実施の形態では、上記の何れかのCAD装置によってノイズ対策用部品が配置された後、1つの電源ネットを複数の第1の階層ネットと1つの第2の階層のネットとに分割し、第1の階層ネット間でのノイズ伝播を防止するよう配線するCAD装置について説明する。ここで、第1の階層ネットとは1つの主部品とその付随部品からなる各グループ内の電源ネットをいい、第2の階層ネットとは各グループ間を接続するネットをいう。

【0114】

図34は、本実施の形態におけるCAD装置5000の構成を示すブロック図である。同図は、図21に示した第3実施形態におけるCAD装置3000に対して、設計情報記憶部3107の代わりに設計情報記憶部5106を、制御部3101の代わりに制御部5101を備え、階層ネット設定部5102、代表ピン選択部5103、未結線表示部5104、配線部5105を新たに追加した構成となっている。図21と同じ構成は説明を省略し、異なる点を中心に説明する。

【0115】

設計情報記憶部5106は、図21の設計情報記憶部3107の記憶内容に加えて、階層ネット設定部5102によって設定される階層ネット情報リスト1801を記憶する。

図36は、階層ネット情報リスト1801の具体例を示す図である。同図において、ネット名1802は、ネット情報と同様に、ネットを識別するための識別子であり、ネット情報リスト1401に属するネット種類が「power」であるネット名をからなる。

【0116】

接続ピン番号1803は、ネット名1802のネットに接続するピン番号を示す。

階層ネット番号1804は、ネット名1802の電源ネットが分割されてできた第1の階層ネットを識別する識別番号である。

代表ピン番号1805は、第1の階層ネットに属するピンのうち、他の第1の階層のネットとの接続に用いられる代表ピンを示す。複数の第1の階層ネットにおける代表ピンを接続するネットが上記第2の階層ネットである。

【0117】

階層ネット接続ピン番号1806は、第1の階層ネットに接続される接続ピン番号を示す。階層ネット接続ピン番号1806には、少なくとも一つ以上のピン番号が記入されている。

階層ネット設定部5102は、設計情報記憶部5106よりネット情報を参照し、ネット種類1409が「power」であるネット名1421を読み出し、前記ネット名1421を階層ネット情報のネット名1822に書き込む。次に接続ピン番号1403を参照し、前記ネット名1421の接続ピン番号1422を読み出し、前記接続ピン番号1422を階層ネット情報の接続ピン番号1823に書き込む。次に、部品情報を参照し、前記接続ピン番号1823に属する部品の主部品番号1208と付随部品番号1209を読み出し、主部品番号ごとに階層ネット番号を付与し、前記接続ピン番号1823のうち、前記主部品1220のピン番号と当該付随部品1230のピン番号を階層ネット接続ピン番号1826に書き込む。これにより、電源ネットは、1つの主部品とその付随部品からなる各グループ内のネットに分割される。

【0118】

代表ピン選択部5103は、第1の階層ネットに対応するグループ毎に、グループ内の付随部品の内最も容量の大きい部品を選択し、その部品のピンの内第1の階層ネットに接続するピンを代表ピンに選択する。具体的には、階層ネット情報リスト1801を参照し、階層ネット接続ピン1806に記載された部品番号を読み出し、部品情報を参照し、付随部品に設定されている部品番号1223を読み出す。さらに、付随部品に設定されている部品番号1223の部品マスタ情報を参照し、当該付随部品のC値1323を読み出す。次に、付随部品に設定されている部品番号1223内のC値を比較し、最も大きな値を持つ部品番号1230を判定し、代表ピンとして選択し、階層ネット情報リスト1801の代表ピン番号1825に書き込む。

【0119】

未結線表示部5104は、データ入力部1102におけるユーザの対話操作に従って、第1、第2の階層ネット毎の未結線を表示部1109に表示する。その際、第1の階層ネットと第2の階層ネットとは、ユーザの区別を可能にするため異なる色で表示する。

配線部5105は、データ入力部1102におけるユーザの対話操作に従って、電源ネットを1つのネットとして配線ないで、第1、第2の階層ネットをそれぞれ独立したネットとして配線する。さらに、未結線表示部5104により表示された未結線に対して配線を行なう。

<制御部5101>

制御部5101が第2配置コマンドによる配置コマンドを受け取った場合の制御動作は、図24と同じなので省略する。ここでは、制御部5101がコマンド入力解析部1104から配線コマンドを受け取った場合の制御動作について説明する。

【0120】

図35は、配線コマンドを受け取ってから第1の階層ネット、第2の階層ネットの配線を行なう処理を示すフローチャートである。

制御部5101は、コマンド入力解析部1104より配線コマンドを受け取ると、階層ネット設定部5102を起動する(S5104)。第1の階層ネット設定部5102は部品情報を参照し、階層ネット情報リスト1801に書き込む。

【0121】

次に、制御部5101は、代表ピン選択部5103を起動する(S5105)代表ピン選択部5103は、階層ネット情報リスト1801を参照し、階層ネット接続ピン1806に記載された部品番号を読み出し、部品情報を参照し、付随部品に設定されている部品番号1223を読み出す。代表ピン選択部は、付随部品に設定されている部品番号1223の部品マスタ情報を参照し、当該付随部品のC値1323を読み出す。次に、付随部品に設定されている部品番号1223内のC値を比較し、最も大きな値を持つ部品番号1230を判定し、代表ピンとして選択し、階層ネット情報リスト1801の代表ピン番号1825に書き込み処理を終了する。代表ピンの選択例を図31に示す。図31において、代表ピンは、それぞれ、部品3601−ピン3901、部品3602−ピン3902、部品3603−ピン3903、部品3604−ピン3904に設定されている。

【0122】

次に、制御部5101は、未結線表示部5104を起動する(S5106)。

未結線表示部5104は、第1の階層ネットと第2の階層ネットを未結線表示する。第一の階層ネットの未結線の表示例を図37示す。同図では、IC1〜IC4のグループに対応する4つの第1の階層ネットの未結線(図中部品のピンとピンとを接続する実線)が表示されている。第2の階層ネットの未結線の表示例を図31に示す。同図では代表ピン間を接続する実線が未結線に当る。図37と図31とでは未結線部分を異なる表示態様(異なる色など)で表示される。

【0123】

制御部5101は、配線部5105を起動する(S5107)。配線部5105は未結線表示部5104によって表示された未結線に従い配線を実施する。なお、S5106、S5107はユーザと対話的に行われる。

以上説明してきたように、本実施の形態では、複数の第1の階層ネットが代表ピンを介して第2の階層ネットにより接続される。代表ピンは容量が大きいので、第1の階層ネット内のノイズ信号は他の第1の階層ネットには伝播しにくくなる。つまり第1の階層ネットは他の第1の階層ネットにノイズを与えにくくなる。

【0124】

なお、代表ピン選択部5103は、さらに、インピーダンスが2番目に大きい第2代表ピン、3番目に大きい第3代表ピンなど複数の代表ピンを順位を付けて選択し、配線部5105は、第2の階層ネットの配線に(第1)代表ピンを用いた場合に未結線が発生する(つまり配線できない)場合に、第2代表ピンを用いて配線するようにしてもよい。

【0125】

さらに、代表ピン選択部5103は、第2の階層ネットの配線が最短となるように第2又は第3代表ピンなどを選択してもよい。この場合も、代表ピン選択部5103は第2の階層ネットの配線を短くしながらも、できるだけインピーダンスの大きい部品のピンを選択することが望ましい。

なお、実施の形態5では、代表ピン選択部5103は部品マスタ情報リスト1301のC値1306の最も大きな部品のピンを代表ピンとして選択しているが、ノイズに対するインピーダンスが大きければよいので、L値1305の大きな部品のピンを選択してもよい。

【0126】

また、実施の形態5では、代表ピン選択部5103は部品マスタ情報リスト1301のC値1306の最も大きな部品のピンを代表ピンとして選択しているが、部品情報リスト1201の部品番号1230に対応する部品形状1232を取り出し、部品形状情報リスト1701を参照し、部品形状1710に対応するピン間距離1713を参照し、ピン間距離1713の大きな部品のピンを選択してもよい。

【0127】

なお、実施の形態5では、代表ピン選択部5103は部品マスタ情報リスト1301のC値1306の最も大きな部品のピンを代表ピンとして選択しているが、部品優先順位1207の優先順位の低い部品のピンを選択してもよい。

また、実施の形態5では、未結線表示部5104において未結線のピンペアの選択法を特定していないが、(a)〜(e)のようにおこなっても良い。(a)第1の階層ネットに接続する部品のうち、最もC値の小さな付随部品のピンと主部品のピンとを選択し、その後、C値の小さな順にピンペアを選択し、順に未結線表示を行っても良い。(b)第1の階層ネットに接続する部品のうち、最もL値の小さな付随部品のピンと主部品のピンとを選択し、未結線表示を行っても良い。(c)第1の階層ネットに接続する部品のうち、最もL値の小さな付随部品のピンと主部品のピンとを選択し、その後、L値の小さな順にピンペアを選択し、未結線表示を行っても良い。(d)第1の階層ネットに接続する部品のうち、最もピン間距離の小さな付随部品のピンと主部品のピンとを選択し、未結線表示を行っても良い。(e)第1の階層ネットに接続する部品のうち、最もピン間距離の小さな付随部品のピンと主部品のピンとを選択し、その後、ピン間距離の小さな順にピンペアを選択し、未結線表示を行っても良い。

【0128】

尚、実施の形態5では、配線部5105において特に配線の方法を指定していないが、第1の階層ネットの配線は、できる限り太く短く配線し、第2の階層ネットの配線は、細く、長い配線を行ってもよい。あるいは、第1の階層ネットと第2の階層ネットにグループ分けされたネットは、それぞれ異なるネット名を持つネットと同様に扱い、それぞれのネットが代表ピンのみで結合されるように配線しても良い。

(実施の形態6)

<概要>

本実施の形態は、バイパスコンデンサのように、配置位置によって効果が異なる部品の配置が適切か否かのユーザによる評価を支援する装置であり、効果を及ぼされる可能性がある部品との対応関係を、ユーザが評価しやすいような表示態様で表示するものである。ここでは、予め記憶された対応関係に基づいて、CAD装置のモニタ上で、バイパスコンデンサ又はそのピンと、そのバイパスコンデンサによってノイズ除去されるであろうスイッチング素子(以下、代表して「IC」と言う)又はそのピンとを線で結んで表示することによって、対応関係を認識しやすくする。

【0129】

また、バイパスコンデンサ又はそのピンと、IC又はそのピンとの距離等に基づいて対応関係を作成する。

また、対応関係毎に有効性の度合いを数値化し、ユーザが評価しやすいような表示態様で表示を区別する。ここでは、線の太さ等を変えて表示する。

さらに、距離だけではなく、現実に則して、動作周波数の一致やバイパスコンデンサの容量も考慮して対応関係を作成し、評価精度を向上させる。

【0130】

<構成>

図38は、本実施の形態に係るCAD装置の構成を示す図である。

図38に示すCAD装置10は、設計情報入手部11、設計情報記憶部12、バイパスコンデンサ評価部13、バイパスコンデンサグループ化部14、バイパスコンデンサグループ情報記憶部15、コマンド入手部16、コマンド解析部17、実装部品表示部18、バイパスコンデンサグループ表示部19、モニタ20、及び、設計情報出力部21を備える。

【0131】

設計情報入手部11は、設計情報を入手する。

設計情報記憶部12は、入手された設計情報を記憶する。

図39(a)〜図39(c)は、設計情報入手部11により入手され、設計情報記憶部12に記憶される設計情報の一例を示す図である。

設計情報は、部品情報とピン情報とネット情報に区別される。

【0132】

図39(a)に示すように部品情報は、部品番号、部品名、部品種類、部品特性、代表点座標、及び、最小最大領域等の各項目の情報から構成される。

ここで、部品番号とは部品の個々を特定する情報である。

部品名とは一般的な部品の名称である。部品種類とは例えばICやコンデンサ等と示される部品の種類を示す情報である。

【0133】

部品特性とは部品の電気的特性等を示し、例えばコンデンサでは、容量(単位[μF])とリード及びビアのインダクタンス(単位[nH])と有効ピン数(単位[個])とである。有効ピン数とは当該コンデンサをパスコンとして同時に効果をもたらすことが可能なICの電源ピンの数をいう。

代表点座標とは配線基板において配置された当該部品の代表点の座標であり、例えば配線基板の左上を基準とした時の第1ピンの相対座標である。

【0134】

最小最大領域とは配線基板において配置された当該部品の外形を示す座標であり例えば配線基板の左上を基準とした時の左上端と右下端の相対座標である。

図39(b)に示すようにピン情報は、部品番号、ピン番号、ネット名、ネット種類、動作周波数、ピン特性、及び、代表点座標等の各項目の情報から構成される。

【0135】

ここで、部品番号とは部品の個々を特定する情報である。

ピン番号とはピンを特定する情報である。

ネット名とはCAD装置内で便宜的に取り決められ電気的に独立した接続ラインのそれぞれを区別する為のネットの名称であって同一の名称が記載されたピン同士は電気的に接続されるものである。

【0136】

ネット種類とは当該ピンが属するネットが電源及びグランドのどちらかに接続されているかもしくはどちらにも接続されていない一般であるかを示す。

動作周波数とは当該ピンに流れる信号の最大周波数である。

ピン特性とはピンの電気的特性等を示し、例えばICのピンでは必要容量(単位[μF])である。必要容量とはICピンに負荷されるべき容量をいう。

【0137】

代表点座標とは配線基板において配置された当該ピンの代表点の座標である。

図39(c)に示すようにネット情報は、ネット名、部品番号、及び、ピン番号の各項目の情報から構成され、ネット名から部品番号、及び、ピン番号を特定する為の情報である。

バイパスコンデンサ評価部13は、各バイパスコンデンサが有効に作用するICを特定する評価を行う。ここでは、各バイパスコンデンサが備える電源ピンから、所定の距離以内に電源ピンを備えるICを特定することにより有効であると評価し、さらに、バイパスコンデンサの電源ピンとICの電源ピンとの間の距離に応じて、有効性の度合いを数値化した有効度を決定する。

【0138】

また、ここでいう距離は、直線距離、マンハッタン距離、実際の配線距離、及び、ループ面積が最小になるような経路距離等がある。ここで、直線距離は、電源ピン間を直線で結んだ最短の距離をいう。マンハッタン距離は、電源ピン間をX軸方向の線分とY軸方向の線分とで順次結んだ距離をいう。実際の配線距離は、配線された箔の長さをいう。経路距離は、電源とグランドの一方がベタパターン(面状又は線幅の太い箔)の場合に電流ループの面積を最小にする距離をいう。

【0139】

バイパスコンデンサ評価部13は、これらの距離を、グランドや電源の配線パターンの違いによってバイパスコンデンサ評価部13は例えば次のように使い分ける。

例えば、グランド、電源の双方がベタパターン(面状または太い線幅の箔)である場合には、直線距離を使う。グランド、電源の一方がベタパターンであって、配線がなされていない場合は、マンハッタン距離を使う。グランド、電源の一方がベタパターンであって、配線がなされている場合は、経路距離を使う。グランド、電源の両方ともベタパターンでない場合は、実際の配線距離を使う。

バイパスコンデンサ評価部13により算出される距離は、配線が完了している場合は実際の配線距離でよい。グランド、電源の双方がベタパターン(面状または太い線幅の箔)である場合は直線距離でよい。グランド及び電源何れか一方をベタパターンとする場合はループ面積が最小になるような経路距離でよい。

グランド及び電源のいずれか又は両方がベタパターンでなく実際の配線を考慮できない場合は一般的な配線ルールに従うと配線が基板の縦及び横方向に限定されると予想される事とループ面積が最小になるような経路距離となる事によりマンハッタン距離となり、

実際の配線を考慮できるが一部にベタパターンが存在する場合はループ面積が最小になるような経路距離となる。

【0140】

バイパスコンデンサグループ化部14は、バイパスコンデンサ評価部13による評価結果に基づいて、バイパスコンデンサのピンと有効であると判定されたICのピンとをそれぞれグループ化しそれぞれに有効度を付加したグループ情報を作成し、そのグループ情報をバイパスコンデンサグループ情報記憶部15に記憶させる。

【0141】

バイパスコンデンサグループ情報記憶部15は、バイパスコンデンサグループ化部14により作成されたグループ情報を記憶する。

図40は、バイパスコンデンサグループ化部14により作成され、バイパスコンデンサグループ情報記憶部15に記憶されるグループ情報の一例を示す図である。

【0142】

図40に示すグループ情報は、グループ番号、IC番号、ICピン番号、バイパスコンデンサ番号、バイパスコンデンサピン番号、及び、有効度の各項目の情報から構成される。

ここで、グループ番号とはグループの個々を特定する情報であり、IC番号とはICの個々を特定する情報であり、ICピン番号とはICのピンの個々を特定する情報であり、バイパスコンデンサ番号はバイパスコンデンサの個々を特定する情報であり、バイパスコンデンサピン番号とはバイパスコンデンサのピンの個々を特定する情報であり、有効度とは評価した有効性の度合いを数値化したものであり例えば十分な有効性をもつものを“有効度80〜100”とし、比較的高い有効性をもつものを“有効度60〜79”、中程度の有効性をもつものを“有効度40〜59”、有効性の低いものを“有効度0〜39”とする。

【0143】

なお、図40の例は1つのICピンと1つのバイパスコンデンサピンとで1つのグループを構成しているが、複数のICピンと1つのバイパスコンデンサピンとで1つのグループを構成してもよいし、1つのICピンと複数のバイパスコンデンサピンとで1つのグループを構成してもよいし、複数のICピンと複数のバイパスコンデンサピンとで1つのグループを構成してもよい。

【0144】

コマンド入手部16は、ユーザがキーボードやポインティングデバイズを用いて入力したコマンドを入手する。

コマンド解析部17は、コマンド入手部16により入手されたコマンドを解析する。

実装部品表示部18は、設計情報記憶部12に記憶された設計情報に基づいて、モニタ20に表示する為の、各実装部品を実装基板上に配置した画像データを作成する。

【0145】

バイパスコンデンサグループ表示部19は、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に基づいて、同一グループのICピンとバイパスコンデンサピンとがユーザが認識可能な態様で対応づけて表示されるように、実装部品表示部18により作成された画像データを変更する。例えば、線で結ぶ、表示の太さを対応づける、表示の形状(破線、波線等)を対応づける、表示色を対応づける、表示の濃淡を対応づける、及び、表示の模様を対応づける等である。

【0146】

モニタ20は、実装部品表示部18及びバイパスコンデンサグループ表示部19により作成、変更された画像データに基づいて、画像を表示する。

設計情報出力部21は、例えば、プリンタ、プロッタ、着脱可能な記憶媒体、及び、所定のネットワークに接続されたドライバ等であり、設計情報記憶部12に記憶された設計情報を出力する。

【0147】

<表示の動作>

ここで、本実施の形態に係るCAD装置10が備える実装部品表示部18が、設計情報記憶部12に記憶された設計情報に基づいて、モニタ20に表示する為の、各実装部品を実装基板上に配置した画像データを作成した後において、バイパスコンデンサグループ表示部19が、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に基づいて、実装部品表示部18により作成された画像データを、同一グループのICとバイパスコンデンサのピンとを、ユーザが認識可能な態様で対応づけて表示されるように変更してモニタ20に画像を表示する動作を説明する。

【0148】

図41は、本実施の形態のCAD装置10の動作の一例を示す図である。

以下に、図41を用いてCAD装置10が画像データを変更して、画像を表示する動作を説明する。

(1)バイパスコンデンサグループ情報記憶部15に、まだ処理の対象となっていないグループが存在するか否かを判断する(ステップS1)。存在しない場合は表示処理(ステップS6)へ行く。

【0149】

(2)まだ処理の対象となっていないグループが存在する場合は、バイパスコンデンサグループ情報記憶部15から、順に1つのグループを選択する(ステップS2)。

(3)バイパスコンデンサグループ情報記憶部15から、選択したグループに属するICの部品番号、又は、ICの部品番号とICピンのピン番号とを抽出し、バイパスコンデンサの部品番号、又は、バイパスコンデンサの部品番号とバイパスコンデンサピンのピン番号とを抽出する(ステップS3)。

【0150】

(4)設計情報記憶部12から、抽出したICの部品番号に基づいて当該ICの部品情報を検索するか、又は、抽出したICの部品番号とICピンのピン番号とに基づいて当該ICピンのピン情報を検索し、抽出したバイパスコンデンサの部品番号に基づいて当該バイパスコンデンサの部品情報を検索するか、又は、抽出したバイパスコンデンサの部品情報とバイパスコンデンサピンのピン番号とに基づいて当該バイパスコンデンサピンのピン情報を検索する(ステップS4)。

【0151】

(5)検索したICの部品情報中の代表点座標、又は、検索したICピンのピン情報中の代表点座標と、検索したバイパスコンデンサの部品情報中の代表点座標、又は、検索したバイパスコンデンサピンのピン情報中の代表点座標とが、ユーザが認識可能な態様で、対応づけて表示されるように、実装部品表示部18により作成された画像データを変更し、次のグループを処理する為に最初に戻る(ステップS5)。例えばここでは、これらの座標点を線で結ぶ。また、グループ情報に添付された有効度に応じて、有効度80〜100の場合には太線、有効度60〜79の場合には普通の線、有効度40〜59以下は細線、有効度39以下は点線、という様に、線の太さや線の形状(破線、波線等)を変える。

【0152】

(6)全てのグループの処理が終了したら、モニタ20が変更された画像データを受けて画像を表示する(ステップS6)。

以下に、表示例を示す。

図42(a)は、ICピンとバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC510の電源ピン511と、バイパスコンデンサ520の電源ピン521とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0153】

図42(a)に示すようにICの電源ピン511とバイパスコンデンサの電源ピン521とが線531で結ばれる。

図42(b)は、ICピンとバイパスコンデンサの中心とを線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC510の電源ピン511と、バイパスコンデンサ520とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0154】

図42(b)に示すようにICの電源ピン511とバイパスコンデンサ520の中心とが線532で結ばれる。

図42(c)は、ICの中心とバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC510と、バイパスコンデンサ520の電源ピン521とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0155】

図42(c)に示すようにIC510の中心とバイパスコンデンサの電源ピン521とが線533で結ばれる。

図42(d)は、ICの中心とバイパスコンデンサの中心とを線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC510と、バイパスコンデンサ520とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0156】

図42(d)に示すようにIC510とバイパスコンデンサ520とが線534で結ばれる。

なお、図42(a)〜図42(d)の各表示例においては、1つのICと1つのバイパスコンデンサとが対応していたが、複数のICと1つのバイパスコンデンサとが対応してもよいし、1つのICと複数のバイパスコンデンサとが対応してもよいし、複数のICと複数のバイパスコンデンサとが対応してもよい。

【0157】

また、複数のピンは、同じ部品のピンであってもよいし、異なる部品のピンであってもよい。

図43(a)は、複数のICピンと1つのバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例を示す図である。

図43(b)は、1つのICピンと複数のバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例を示す図である。

【0158】

図43(c)は、2つのICのそれぞれピンと1つのバイパスコンデンサピンとを、有効度を考慮して実線又は破線で結ぶ場合に、モニタ20に表示される画像の表示例を示す図である。ここでは十分な有効性を持つ(有効度80〜100)グループに基づく表示を実線601で表示し、比較的高い有効性を持つ(有効度が60〜79)グループに基づく表示を点線602で表示している。有効度に応じて表示態様を区別することで、ICに対してバイパスコンデンサの配置が適切か否かを容易に判断できる。

【0159】

図44(a)は、有効度を考慮して、ICピンとバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC710の電源ピン711と、バイパスコンデンサ720の電源ピン721と、バイパスコンデンサ730の電源ピン731とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶され、IC710のグランドピン712と、バイパスコンデンサ720のグランドピン722と、バイパスコンデンサ730のグランドピン732とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0160】

図44(a)に示すように、ICの電源ピン711とバイパスコンデンサの電源ピン721との間、及び、ICのグランドピン712とバイパスコンデンサのグランドピン722との間が、十分な有効性を持つ(有効度80〜100)グループに基づく表示である実線741で結ばれ、ICの電源ピン711とバイパスコンデンサの電源ピン731との間、及び、ICのグランドピン712とバイパスコンデンサのグランドピン732との間が、比較的高い有効性を持つ(有効度が60〜79)グループに基づく表示である実線741で結ばれる。

【0161】

図44(b)は、ICピンとバイパスコンデンサピンとを有効度に応じた太さの違う線で結ぶ場合に、モニタ20に表示される画像の表示例である。ここでは、IC750の電源ピン751と、バイパスコンデンサ760の電源ピン761と、バイパスコンデンサ770の電源ピン771と、バイパスコンデンサ780の電源ピン781とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとする。

【0162】

図44(b)に示すように、ICの電源ピン751とバイパスコンデンサの電源ピン761とが太線791で結ばれ、ICの電源ピン751とバイパスコンデンサの電源ピン771とが普通の太さの線792で結ばれ、ICの電源ピン751とバイパスコンデンサの電源ピン781とが細線793で結ばれる。

ここでは、ICピンとバイパスコンデンサピン間の距離をd[mm]、dmin = 2[mm] として、有効度αを次式のように定義する。

・d> dminの場合は、

α=(dmin / d )× 100

・d≦dminの場合は、

α= 100

例えば、電源ピン751と電源ピン761間の距離を4mm、電源ピン751と電源ピン771間の距離を6mm、電源ピン751と電源ピン781間の距離を8mmとすると、有効度はそれぞれ50、33、25となる。

【0163】

なお、ここでは有効度をICピンとバイパスコンデンサピン間の距離に基づいた特定の数式によって求めたが、バイパスコンデンサが有効であることを示すいかなる指標に基づいて有効度を求めてもかまわない。

また、ここでは有効度を100までの数値で定義したが、例えばA,B,Cの様な3段階表現や、1〜5の様の5段階表現など、比較判定できるものであればどのように定義してもよい。

【0164】

また、ここでは有効度の違いを実線と点線で区別して表示したり、有効度に応じて線の太さを変えたりしたが、有効度の違いを区別できるならばどのような表示方法であってもよい。例えば、線の色、線の濃淡、及び、線の模様等の違いで区別してもよいし、線で結ぶのではなくピン自体の表示態様を変えて区別してもよい。

【0165】

このように、有効度に応じて表示態様を区別することで、ICに対してバイパスコンデンサの配置が適切か否かを容易に判断できる。

また、ここでは、対応するICピンとバイパスコンデンサピンを線で結んで表示しているが、対応するICピンとバイパスコンデンサピンが視覚的に確認できるような表示方法であれば、いかなる表示方法であってもよい。例えば、対応するICピンとバイパスコンデンサピンとを同一の表示態様(太さ、形状、色、濃淡、模様、強調表示、等)で表示してもよいし、対応の一覧を表示してもよい。

さらに上記表示態様として、基板の表面であるか裏面であるかに応じて異なる表示にしてもよいし、一時的に表示するようにしてもよいし、ユーザ指示があれば消去または表示開始するようにしてもよい。

【0166】

<グループ化の動作>

ここで、本実施の形態に係るCAD装置10が備えるバイパスコンデンサ評価部13が、各バイパスコンデンサが有効に作用するICを特定する為に評価を行い、バイパスコンデンサグループ化部14が、バイパスコンデンサ評価部13による評価結果に基づいて、バイパスコンデンサのピンと有効であると判定されたICのピンとをそれぞれグループ化し、それぞれに有効度を付加したグループ情報を作成し、そのグループ情報をバイパスコンデンサグループ情報記憶部15に記憶させる動作を説明する。

【0167】

図45は、本実施の形態のCAD装置10の動作の一例を示す図である。

以下に、図45を用いてCAD装置10が各バイパスコンデンサを評価してグループ情報を作成し記憶する動作を説明する。

(1)設計情報記憶部12に記憶されたネット情報中に、まだ処理の対象となっていない電源ネットが存在するか否かを判断する(ステップS11)。存在しない場合は処理を終了する。

【0168】

(2)まだ処理の対象となっていない電源ネットが存在する場合は、設計情報記憶部12に記憶されたネット情報中から順に1つの電源ネットを選択する(ステップS12)。

(3)設計情報記憶部12に記憶されたピン情報から、選択した電源ネットに属する全てのICピンのピン情報中の代表点座標と周波数と必要容量とを抽出する(ステップS13)。

【0169】

(4)選択した電源ネットに接続されるコンデンサピン中に、まだ処理の対象となっていないコンデンサピンが存在するか否かを判断する(ステップS14)。存在しない場合は、次の電源ネットの処理(ステップS11)へ行く。

(5)まだ処理の対象となっていないコンデンサピンが存在する場合は、設計情報記憶部12に記憶されたネット情報中から順に、1つのコンデンサピンのピン番号と当該コンデンサピンが属するコンデンサの部品番号とを選択する(ステップS15)。

【0170】

(6)選択したコンデンサが備えるピンのうち電源ネットに属していないもう一方がグランドネットに属するか否かを、設計情報記憶部12に記憶されたピン情報を参照して判断する(ステップS16)。グランドネットに属さない場合は、当該コンデンサはバイパスコンデンサとして使われていないと判断して、次のコンデンサピンの処理(ステップS14)へ行く。グランドネットに属する場合は、当該コンデンサはバイパスコンデンサとして使われていると判断して処理を継続する。

【0171】

(7)選択したバイパスコンデンサピンのピン番号とバイパスコンデンサの部品情報とに基づいて、設計情報記憶部12に記憶されたピン情報から当該バイパスコンデンサピンのピン情報中の代表点座標を検索し、設計情報記憶部12に記憶されたバイパスコンデンサの部品情報中から容量とリード及びビアのインダクタンスと有効ピン数とを抽出する(ステップS17)。

【0172】

(8)バイパスコンデンサピンの代表点座標と所定の距離以内にある代表点座標を、ステップS13において抽出した代表点座標から検索し、検索された代表点座標を持つICピンを特定する(ステップS18)。

またここで有効ピン数を考慮して、コンデンサの有効ピン数を越える場合は、越える分のICのICピンは特定しない事とする。

【0173】

ここでバイパスコンデンサとICとの周波数特性を考慮して、周波数特性が一致しないICのICピンは特定しない事とする。

またここで容量を考慮して、コンデンサの容量が不足する場合は、不足する分のICのICピンは特定しない事とする。

(9)バイパスコンデンサピンの代表点座標と、所定の距離以内のあるICピンの代表点座標との、距離に応じて有効度を決定する(ステップS19)。

【0174】

(10)バイパスコンデンサのピン情報と、有効であると判定されたICのピン情報とをそれぞれグループ化し、それぞれに有効度を付加したグループ情報を作成し、バイパスコンデンサグループ情報記憶部15に記憶させ、次のコンデンサピンの処理(ステップS14)へ行く(ステップS20)。

図44(a)は、周波数特性を考慮した場合に、モニタ20に表示される画像の表示例を示す図である。ここでは、IC910の電源ピン911と、バイパスコンデンサ920の電源ピン921とバイパスコンデンサ930の電源ピン931とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとし、電源ピン921の有効周波数範囲をfA、電源ピン931の有効周波数範囲をfBとし、電源ピン911のピン周波数f1が有効周波数範囲fAには含まれるが有効周波数範囲fBには含まれないものとする。

【0175】

図46(a)に示すように、電源ピン931よりも電源ピン921の方が、電源ピン911と距離的には近いのであるが、周波数特性が異なるためグループ化されず、その結果、電源ピン911と電源ピン931とが線941で結ばれている。

図46(b)は、容量を考慮した場合に、モニタ20に表示される画像の表示例を示す図である。ここでは、IC950の電源ピン951と、IC950の電源ピン952と、IC960の電源ピン961と、バイパスコンデンサ970の電源ピン971とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されているものとし、電源ピン951の必要容量を0.03[μF]、電源ピン952の必要容量を0.05[μF]、電源ピン961の必要容量を0.04[μF」、バイパスコンデンサ970の容量を0.1[μF]とする。

【0176】

図46(b)に示すように、ICの電源ピン951とバイパスコンデンサの電源ピン971との間が線981で結ばれ、ICの電源ピン952とバイパスコンデンサの電源ピン971との間が線982で結ばれるが、ICの電源ピン961とバイパスコンデンサ971との間は結ばれていない。これは、電源ピン951と電源ピン952との必要容量の合計が0.03+0.05=0.08[μF]であり、バイパスコンデンサ970の容量0.1[μF]を越えないので容量が足りているが、さらに電源ピン961の必要容量を合計すると0.08+0.04=0.12[μF]となり、バイパスコンデンサ970の容量0.1[μF]を越えてしまい容量が不足するからである。

【0177】

なお、本実施の形態では、電源ネットのみに基づいて、バイパスコンデンサピンから所定の距離以内であるか否かを判定してICピンを特定したが、電源ネットのみに基づくのではなくグランドネットのみに基づいてもよいし、電源ネット及びグランドネットの両方に基づいてもよい。

また、所定の距離以内であるか否かではなく、距離が一番近いICピンを特定してもよいし、距離が近い順に所定の順番までのICピンを特定して、順に有効度を付与してもよい。

【0178】

また、先にICピンを検索してICピンからバイパスコンデンサピンを特定してもよい。

また、本実施の形態では各座標値は2次元であって配線基板の厚さを考慮していないが、各座標値を3次元化し、配線基板の厚さをも考慮して、より正確に距離を算定してもよい。

【0179】

図47は、配線基板の厚さをも考慮してより正確に距離を算定する方法の概略を説明する為の、配線基板の断面を示す図である。

ここでは説明を簡単にするために、電源ネットのみに基づいて、バイパスコンデンサピンと距離が一番近いICピンを特定することとする。

図47に示す配線基板1003の部品面1001(上の面)には、IC1010とバイパスコンデンサ1020が配置され、半田面1002(下の面)にはバイパスコンデンサ1030が配置されている。

【0180】

ここで、IC1010が備えるピン1011と、バイパスコンデンサ1020が備えるピン1021と、バイパスコンデンサ1030が備えるピン1031とが同じ電源ネットに属するものとし、ピン1011とピン1021とは部品面1001上の配線1030で図上に示した距離で接続されるものとすると、ピン1011からの距離が最短になるバイパスコンデンサのピンは、配線基板の厚さを考慮しなければピン1031となるが、配線基板の厚さを考慮すればピン1021となる。

【0181】

次に、ループ面積が最小になるような経路距離について補足説明する。

図48は、多層基板においてループ面積が最小になるような経路距離を算定する方法の一例を説明する為の、配線基板を側面及び上面から見た図である。

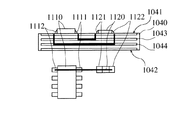

図48に示す配線基板1040の部品面1041(上の面)には、IC1110とバイパスコンデンサ1120が配置されている。また、内層1043は電源層、内層1044はグランド層であり、両方共ベタパターンであるものとする。

【0182】

ここで、IC1110が備えるピン1111と、バイパスコンデンサ1120が備えるピン1121とが内層1103と同じ電源ネットに属し、IC1110が備えるピン1112と、バイパスコンデンサ1120が備えるピン1122とが内層1104と同じグランドネットに属するものとすると、ループの面積が最小になる電流の経路は、図48に示した経路1131及び経路1132のようになる。従って、この様な場合の経路距離は、厚さを考慮せずに決定した経路距離に、各部品が配置されている面から各内層までの厚さに相当する距離を往復分加算したものとなる。

【0183】

図49は、ループ面積が最小になるような経路距離を算定する方法の一例を説明する為の、配線基板を上面から見た図である。

ここでは、グランド層がほぼ全体にわたってベタパターンであるものとし、電源層には図49に示すようにスリット1151があるとすると、電源層を流れる電流はスリット1151を回り込むような経路1152をとらざるを得ない事になる。

【0184】

ここで、グランド層がほぼ全体にわたってベタパターンであるので、グランド層を流れる電流は直線距離となる経路も取り得るが、それではループ面積が最小にならないので、結局、電源層の経路1152と同様の経路を取ることになる。

また、各座標値を3次元化してより正確に距離を算定しようとすると、ループ面積が最小になるような経路にはねじれが発生する場合があるが、このような場合には、あくまで厳密に計算やシミュレーションによってもとめてもよいが、適切な特定の平面に投影した図形の面積が最小になる経路を求めて代用してもよい。

【0185】

次に、周波数特性を考慮してグループ情報を作成する方法について補足説明する。

(1)図45のステップS18に示したICピンの特定に際して、周波数特性を考慮する場合には、まず、ステップS17で得たバイパスコンデンサの容量(以下、「C」)とリード及びビアのインダクタンス(以下、「L」)から、当該バイパスコンデンサの共振周波数(以下、「f0」)を、以下の式で算出する。

【0186】

f0=1/(2π√(LC))

図50は、バイパスコンデンサのインピーダンスZと周波数fとの関係を示す図である。

図50に示すように、バイパスコンデンサのインピーダンスZは、周波数f=f0のときに最小値を取る。

【0187】

ここで、バイパスコンデンサは、特定値Z0以下のインピーダンスを取る周波数の範囲に対して有効であるとすると、その有効周波数範囲fは、

f=f0−ΔfL 〜 f0+ΔfH

と表記される。

【0188】

(2)図45のステップS18で検索されるICピンは電源ネット又はグランドネットに属するので、一般的にはピン自体が周波数を持つわけではないが、そのICピンを電源又はグランドとする内部回路の動作周波数によって、スイッチング電流などの高周波成分を含む電流がピンに発生する。

図51(a)は、電源ネット又はグランドネットに属するICピンの周波数を算出する為の、デバイスモデルを示す図である。

【0189】

図51(a)に示す回路のシミュレーションを行ない、電源ピンに流れる電流又はグランドピンに流れる電流をピン電流I(t)として、その波形を求める。

図51(b)は、ピン電流I(t)と時間tとの関係を示す図である。

図51(b)に示す波形を、周波数領域の電流をI(f)としてフーリエ変換する。

【0190】

図51(c)は、周波数領域の電流I(f)と周波数fとの関係を示す図である。

図51(c)に示すように、I(f)が最大値を取る周波数をfMとし、これをICピンの周波数とする。

ICピンの周波数は予め設計情報記憶部12にピン情報として記憶しておき、図45のステップS13で抽出される。

【0191】

(3)図45のステップS18において、ステップS13で抽出された周波数が、有効周波数範囲fに含まれる場合にのみ、ICピンが特定される事とする。

なお、ICピンの周波数は1つではなく、複数であってもよい。

また、バイパスコンデンサの有効周波数範囲fを、L、C、Z0等から数式によって求めるのではなく、有効周波数範囲fを予め記憶させておいてもよい。

【0192】

また、ICピンの周波数はデバイスモデルから導出するのではなく、実測によって求めてもよいし、ICの最大内部周波数と定義してもよいし、その他の如何なる方法で導出してもよいし、予め与えておいてもよい。

また、周波数領域の電流I(f)が最大値を取る周波数をピン周波数とするのではなく、I(f)が所定の値より大きい周波数をすべてピン周波数としてもよい。

【0193】

次に、容量を考慮してグループ情報を作成する方法について補足説明する。

図45のステップS18に示したICピンの特定に際して、容量を考慮する場合には、ステップS13で抽出したICピンの必要容量と、ステップS17で得たバイパスコンデンサの容量とを比較して、ICピンの必要容量がバイパスコンデンサの容量よりも小さい時にのみ、ICピンが特定される事とする。

【0194】

また、複数のICピンの必要容量の合計が、バイパスコンデンサの容量を越えない範囲で、1つのバイパスコンデンサを複数のICピンと対応させてグループ化してもよい。

また、1つのバイパスコンデンサを複数のICピンと対応させてグループ化する場合には、実際にはそれぞれのICピンに対応する出力が同時にスイッチングされることはまれであるので、複数のICピンの必要容量の合計をそのまま用いるのではなく、同時にスイッチングされる比率を設定して、必要容量の合計にこの比率を掛けて補正した値を用いてもよい。例えば、図46(b)に示した例において、同時にスイッチングされる比率を“0.8”とすると、3つのICピンの必要容量の合計“0.12μF”が、比率を“0.8”を掛けた値“(0.12x0.8=)0.096μF”となり、バイパスコンデンサの容量“0.1μF”よりも小さくなるので、これら3つのICピンはグループ化できるようになる。

【0195】

以下に、ICピンの必要容量Cを算出する例を説明する。

ここで、ピンの過渡電流ΔI、ピンに許容されるノイズマージンΔVが与えられているものとする。

このとき、インピーダンスXは次式で求められる。

X=ΔV/ΔI

ICの内部動作周波数をfとすると、必要容量Ciは次式で求められる。

Ci=1/(2πfX)

なお、ここでは過渡電流ΔI、ノイズマージンΔVがあらかじめ与えられている状態から、インピーダンスX、必要容量Ciを計算式で算出したが、過度電流ΔI、ノイズマージンΔV自体も計算式で算出可能である。

【0196】

また、ここでは簡易的な数式を用いて必要容量を求めているが、ICピンの周波数の場合と同様にデバイスモデルから導出してもよいし、その他の如何なる方法で導出してもよいし、あらかじめ与えておいてもよい。

以上のように、本実施の形態のCAD装置10によれば、動作周波数の一致やバイパスコンデンサの容量も考慮して、実際により近いであろうと推測されるピン間の距離に基づいて対応関係を作成し、対応関係のあるバイパスコンデンサとスイッチング素子とを、有効性の度合別の線で結んで表示することができる。

(実施の形態7)

<概要>

本実施の形態は、いずれのバイパスコンデンサにも関係づけられていないスイッチング素子又はスイッチング素子のピンを検索して強調表示することによって、バイパスコンデンサの配置漏れを容易に発見する。

【0197】

<構成>

図52は、本実施の形態に係るCAD装置の構成を示す図である。

図52に示すCAD装置30は、設計情報入手部11、設計情報記憶部12、バイパスコンデンサ評価部13、バイパスコンデンサグループ化部14、バイパスコンデンサグループ情報記憶部15、コマンド入手部16、コマンド解析部17、実装部品表示部18、バイパスコンデンサグループ表示部19、モニタ20、設計情報出力部21、未対応ピン検索部31、及び、未対応ピン表示部32を備える。

【0198】

ここで、実施の形態1における図38に示したCAD装置10の構成要素と同一の機能を有するものは同一の番号とし、その説明を省略する。

未対応ピン検索部31は、設計情報記憶部12に記憶されたピン情報中のICの電源ピン及びグランドピンの中から、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に含まれていないピンを全て検索して、バイパスコンデンサ未対応ピンと認定する。

【0199】

未対応ピン表示部32は、未対応ピン検索部31によりバイパスコンデンサ未対応ピンと認識されたICピンを、ユーザが認識可能な態様で表示する。

<動作>

ここで、本実施の形態に係るCAD装置30が備える実装部品表示部18が、設計情報記憶部12に記憶された設計情報に基づいて、モニタ20に表示する為の、各実装部品を実装基板上に配置した画像データを作成し、バイパスコンデンサグループ表示部19が、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に基づいて、実装部品表示部18により作成された画像データを、同一グループのICとバイパスコンデンサのピンとを、ユーザが認識可能な態様で対応づけて表示されるように変更した後において、未対応ピン検索部31がバイパスコンデンサ未対応ピンを認定して、未対応ピン表示部32がモニタ20に表示する動作を説明する。

【0200】

図53は、本実施の形態のCAD装置30の動作の一例を示す図である。

以下に、図53を用いてCAD装置30が各バイパスコンデンサを評価してグループ情報を作成し記憶する動作を説明する。

(1)設計情報記憶部12に記憶されたピン情報中のICの電源ピン及びグランドピンを全て抽出する(ステップS31)。

【0201】

(2)抽出した電源ピン及びグランドピンから、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に含まれているピンを全て削除して、残りをバイパスコンデンサ未対応ピンと認定する(ステップS32)。

(3)まだ処理の対象となっていないバイパスコンデンサ未対応ピンが存在するか否かを判断する(ステップS33)。存在しない場合は処理を終了する。

【0202】

(4)まだ処理の対象となっていないバイパスコンデンサ未対応ピンが存在する場合は、順にバイパスコンデンサ未対応ピンの1つを選択する(ステップS34)。

(5)設計情報記憶部12に記憶されたピン情報から、選択したバイパスコンデンサ未対応ピンのピン情報中の代表点座標を抽出する(ステップS35)。

【0203】

(6)抽出した代表点座標のピンをユーザが認識可能な態様で表示し、次のバイパスコンデンサ未対応ピンの処理(ステップS33)へ行く(ステップS36)。例えば、ピン外形を太線化したり、ピンに対応する領域を塗り潰したり、ピンの表示色をかえたりして、強調表示する。

図54は、バイパスコンデンサ未対応ピンをユーザが認識可能な態様で表示する場合に、モニタ20に表示される画像の表示例である。ここでは、IC1710の電源ピン1711と、バイパスコンデンサ1720の電源ピン1721とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されており、IC1710の電源ピン1712はバイパスコンデンサグループ情報記憶部15に記憶されていないものとする。

【0204】

図54に示すようにICの電源ピン1711とバイパスコンデンサの電源ピン1721とが線1731で結ばれるが、電源ピン1712はどことも結ばれることがなく、さらにここでは、ピン外形が太線化され、領域が塗り潰されることによって強調表示されている。

以上のように、本実施の形態のCAD装置30によれば、バイパスコンデンサが対応づけられていないICピンを強調表示することができる。

【0205】

なお、ここではICピンを強調表示したが、ICを強調表示してもよい。

(実施の形態8)

<概要>

本実施の形態は、いずれのスイッチング素子にも関係づけられていないバイパスコンデンサ又はバイパスコンデンサのピンを検索して強調表示することによって、過剰なバイパスコンデンサを容易に発見する。

【0206】

<構成>

図55は、本実施の形態に係るCAD装置の構成を示す図である。

図55に示すCAD装置40は、設計情報入手部11、設計情報記憶部12、バイパスコンデンサ評価部13、バイパスコンデンサグループ化部14、バイパスコンデンサグループ情報記憶部15、コマンド入手部16、コマンド解析部17、実装部品表示部18、バイパスコンデンサグループ表示部19、モニタ20、設計情報出力部21、未使用コンデンサ検索部41、及び、未使用コンデンサ表示部42を備える。

【0207】

ここで、実施の形態6における図38に示したCAD装置10の構成要素と同一の機能を有するものは同一の番号とし、その説明を省略する。

未使用コンデンサ検索部41は、設計情報記憶部12に記憶されたピン情報中のコンデンサの電源ピン及びグランドピンの中から、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に含まれていないピンを全て検索して、当該ピンを備えるコンデンサを未使用コンデンサと認定する。

【0208】

未使用コンデンサ表示部42は、未使用コンデンサ検索部41により未使用コンデンサと認識されたコンデンサを、ユーザが認識可能な態様で表示する。

<動作>

ここで、本実施の形態に係るCAD装置40が備える実装部品表示部18が、設計情報記憶部12に記憶された設計情報に基づいて、モニタ20に表示する為の、各実装部品を実装基板上に配置した画像データを作成し、バイパスコンデンサグループ表示部19が、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に基づいて、実装部品表示部18により作成された画像データを、同一グループのICとバイパスコンデンサのピンとを、ユーザが認識可能な態様で対応づけて表示されるように変更した後において、未使用コンデンサ検索部41が未使用コンデンサを認定して、未使用コンデンサ表示部42がモニタ20に表示する動作を説明する。

【0209】

図56は、本実施の形態のCAD装置40の動作の一例を示す図である。

以下に、図56を用いてCAD装置40が各バイパスコンデンサを評価してグループ情報を作成し記憶する動作を説明する。

(1)設計情報記憶部12に記憶されたピン情報中のバイパスコンデンサの電源ピン及びグランドピンを全て抽出する(ステップS41)。

【0210】

(2)抽出した電源ピン及びグランドピンから、バイパスコンデンサグループ情報記憶部15に記憶されたグループ情報に含まれているピンを全て削除して、残りのピンを備えるコンデンサを未使用コンデンサと認定する(ステップS42)。

(3)まだ処理の対象となっていない未使用コンデンサが存在するか否かを判断する(ステップS43)。存在しない場合は処理を終了する。

【0211】

(4)まだ処理の対象となっていない未使用コンデンサが存在する場合は、順に未使用コンデンサの1つを選択する(ステップS44)。

(5)設計情報記憶部12に記憶された部品情報から、選択した未使用コンデンサの部品情報中の代表点座標を抽出する(ステップS45)。

(6)抽出した代表点座標のコンデンサをユーザが認識可能な態様で表示し、次の未使用コンデンサの処理(ステップS43)へ行く(ステップS46)。例えば、コンデンサ外形を太線化したり、コンデンサに対応する領域を塗り潰したり、コンデンサの表示色をかえたりして、強調表示する。

【0212】

図57は、未使用コンデンサをユーザが認識可能な態様で表示する場合に、モニタ20に表示される画像の表示例である。ここでは、IC2010の電源ピン2011と、バイパスコンデンサ2020の電源ピン2021とが同一グループとしてバイパスコンデンサグループ情報記憶部15に記憶されており、バイパスコンデンサ2030の電源ピン2031はバイパスコンデンサグループ情報記憶部15に記憶されていないものとする。

【0213】

図57に示すようにICの電源ピン2011とバイパスコンデンサの電源ピン2021とが線2041で結ばれるが、電源ピン2031はどことも結ばれることがなく、さらにここでは、バイパスコンデンサ2030の外形が太線化され、領域が塗り潰されることによって強調表示されている。

以上のように、本実施の形態のCAD装置40によれば、ICピンが対応づけられていないバイパスコンデンサを強調表示することができる。

【0214】

なお、実施の形態6〜8においては、配置位置によって効果が異なる部品としてバイパスコンデンサを例にとって説明したが、バイパスコンデンサに限られるものではない。例えば、ダンピング抵抗、終端抵抗、フェライトコア、及び、EMI対策部品等であってもよい。

上記各実施の形態では、プリント配線基板の設計を支援するCAD装置を説明したが、IC内の回路チップ(ベアチップ)の設計を支援するCAD装置にも本発明を当然適用することができる。

【0215】

また、コンピュータに実施の形態1〜3のような動作を実行させることができるプログラムが、コンピュータ読み取り可能な記録媒体に記録され、この記録媒体が流通し、取り引きの対象となりうる。

ここでコンピュータ読み取り可能な記録媒体とは、例えば、フロッピーディスク、CD、MO、DVD、メモリーカード等の着脱可能な記録媒体、ハードディスク、半導体メモリ等の固定記録媒体等であり、特に限定されるものではない。

【0216】

【発明の効果】

本発明のCAD装置は、プリント配線基板に配置すべき部品のうち、受動部品に対して、部品のインピーダンス値の小さい順に部品順位を決定する決定部と、決定された部品順位の順に受動部品を配置する配置部とを備える。

この構成によれば、受動部品は、インピーダンス値の小さい部品から順に配置されていく。インピーダンスが小さいほど周波数の高いノイズを低減するので、より高い周波数のノイズから低い周波数のノイズの順に受動部品が配置されることになる。先に配置される程、配置の自由度が大きいので、周波数の高いノイズほど効率良く低減される位置に、受動部品を配置することができる。

【0217】

ここで、前記配置部は、受動部品以外の配置済み部品の電源ピンの近傍に受動部品配置する。

この構成によれば、電源ピンの電流に起因する高周波ノイズを効率良く低減することができる。

ここで、前記決定部は、受動部品の等価直列インダクタンスの小さい順をインピーダンスの小さい順として前記部品順位を決定するようにしてもよい。

【0218】

この構成によれば、受動部品のインピーダンスの代わりに等価直列インダクタンスを用いるので、種類が異なる受動部品を同列に取り扱う事ができる。

ここで、前記決定部は、受動部品のとりうる複数のピン間距離とそれに対応する等価直列インダクタンス値とを保持するテーブル部と、受動部品毎に、そのピン間距離をテーブル部に保持された等価直列インダクタンス値に換算する換算部と、受動部品毎に換算されたインダクタンス値を、小さい順に並び替えて前記部品順位とする並び替え部とを備える構成としてもよい。

【0219】

この構成によれば、ピン間距離が小さいほど等価直列インダクタンス値が小さいという性質を利用して、換算部はテーブル部を参照することによりピン間距離を等価直列インダクタンス値に換算するので、電気的特性がわかっていなくても受動部品のピン間距離さえわかっていれば、種類が異なる受動部品に対して容易に部品順位を定することができる。

【0220】

ここで、前記決定部は、受動部品のインピーダンスがしきい値以下となる周波数域である有効周波数域の高い順を、前記インピーダンスの小さい順として前記部品順位を決定するようにしてもよい。

この構成によれば、受動部品がノイズ対策に有効な周波数の高い順に部品順位を決定するので、部品順位は有効周波数の高い順になるので、周波数の高いノイズから受動部品を有効に配置をすることができる。

【0221】

ここで、前記決定部は、受動部品のとりうる複数のピン間距離とそれに対応する前記有効周波数とを保持するテーブル部と、受動部品毎に、そのピン間距離をテーブル部に保持された有効周波数域に換算する換算部と、受動部品毎に換算された有効周波数域を、高い順に並び替えて前記部品順位とする並び替え部とを備える構成としてもよい。

【0222】

この構成によれば、換算部はテーブル部を参照することによりピン間距離を有効周波数に換算するので、電気的特性がわかっていなくても受動部品のピン間距離さえわかっていれば、種類が異なる受動部品に対して容易に部品順位を定することができる。

ここで、前記決定部は、受動部品毎に、その部品のキャパシタンスおよびインダクタンスの少なくとも一方から、前記有効周波数域を算出する算出部と、受動部品毎に算出された有効周波数域を、高い順に並び替えて前記部品順位とする並び替え部とを備える構成としてもよい。

【0223】

この構成によれば、受動部品毎に、キャパシタンスおよびインダクタンスから有効周波数域を直接算出するので、精度よく有効周波数域の高い順に部品順位を決定することができる。

ここで、前記算出部は、受動部品がキャパシタ素子、抵抗素子、フィルタ素子の何れかである場合に、少なくともそのインダクタンスを用いて前記有効周波数を算出するようにしてもよい。

【0224】

この構成によれば、受動部品がキャパシタ素子、抵抗素子、フィルタ素子の何れかである場合でも、そのインダクタンスから有効周波数域を算出するので、精度よく有効周波数域の高い順に部品順位を決定することができる。

ここで、前記受動部品はキャパシタ素子であり、

前記決定部は、キャパシタ素子の等価直列インダクタンスの小さい順をインピーダンスの小さい順として前記部品順位を決定するようにしてもよい。

【0225】

この構成によれば、キャパシタ素子の等価直列インダクタンスの小さい順つまりノイズ低減に有効な周波数の高いを順を、部品順位として、この順に受動部品を配置するので、ノイズ特性の良い配線基板設計を効率よく行うことができる。

ここで、前記決定部は、キャパシタ素子の容量の小さい順を等価直列インダクタンスの小さい順として前記部品順位を決定するようにしてもよい。

【0226】

この構成によれば、キャパシタ素子の容量の小さい部品ほど等価直列インダクタンスも小さいという性質を利用するので、簡易に部品順位を設定することができる。

ここで、前記決定部は、キャパシタ素子の端子間距離の小さい順を等価直列インダクタンスの小さい順と看做して前記部品順位を決定するようにしてもよい。

【0227】

この構成によれば、端子間距離の小さい部品ほど等価直列インダクタンスも小さいという性質を利用するので、簡易に部品順位を設定することができる。

ここで、前記決定部は、キャパシタ素子のとりうり複数のピン間距離とそれに対応する等価直列インダクタンス値とを対応させて保持するテーブル部と、キャパシタ素子毎に、そのピン間距離をテーブル部に保持された等価直列インダクタンス値に換算する換算部と、キャパシタ素子毎に換算されたインダクタンス値を、小さい順に並び替えて前記部品順位とする並び替え部とを備える構成としてもよい。

【0228】

この構成によれば、換算部はテーブル部を参照することによりピン間距離を有効周波数に換算するので、ピン間距離さえわかっていれば、キャパシタ素子の有効周波数に容易に換算することができる。

ここで、前記受動部品は、キャパシタ素子であり、

前記決定部は、キャパシタ素子のインピーダンスがしきい値以下となる周波数域である有効周波数域の高い順を、前記インピーダンスの小さい順として前記部品順位を決定するようにしてもよい。

【0229】

この構成によれば、キャパシタ素子のノイズ低減に有効な周波数が高い順に部品順位を決定するので、周波数の高いノイズから低いノイズの順により適切なキャパシタ素子を配置することができる。

ここで、設計支援装置は、さらに、受動部品以外の部品の電源ピンに対して、電源ピンを流れる電流に発生し得るノイズの重大な順にピン順位を設定するピン順位決定部と、電源ピンをもつ部品に対する受動部品の割付けを、ピン順位及び部品順位の高い順に行なう割付部とを備え、前記配置部は、部品順位の高い順に受動部品を、それが割り付けられた電源ピンの近傍に配置するように構成してもよい。

【0230】

この構成によれば、割付部はピン優先順位の高い順に、部品順位の高い受動部品を割り付けるので、配置部は電源ピンのうち発生し得るノイズの重大な順に、部品順位の高い受動部品を配置していくので、ノイズ特性のよい部品配置をおこなうことができる。

ここで、前記ピン順位決定部は、電源ピンを流れる電流によって駆動される信号周波数の高い順を前記重大な順として前記ピン順位を設定するようにしてもよい。

【0231】

この構成によれば、周波数の高いノイズ源となる電源ピンに対して、インピーダンスの低い受動部品を配置することができる。

ここで、前記ピン順位決定部は、電源ピンを流れる電流によって駆動される信号の立ち上がり時間及び立ち下がり時間の何れかについて、その短い順を前記重大な順として前記ピン順位を決定するようにしてもよい。

【0232】

ここで、前記ピン順位決定部は、電源ピンを流れる電流によって駆動される信号の立ち上がり時間及び立ち下がり時間の短い方について、その短い順を前記重大な順として前記ピン順位を決定するようにしてもよい。

この構成によれば、電源ピンを流れる電流に起因するノイズの電源ピンに対して、そのノイズの重大さの順にピン順位を決定することができる。

【0233】

ここで、前記ピン順位決定部は、電源ピンを流れる電流によって駆動される信号の消費電流の多い順を前記重大な順として前記ピン順位を決定するようにしてもよい。

この構成によれば、消費電流の多い電源ピンほど、その電源ピンに起因するノイズが重大であるという性質を利用して、ピン順位を決定することができる。

【0234】

ここで、前記ピン順位決定部は、電源ピンを流れる電流によって駆動される信号の電圧、周波数、立ち上がりまたは立下り時間、デューティ比に基づいて、当該信号の電圧波形を算出し、電圧波形において電圧しきい値を上回る電圧の最高周波数の高い順を前記重大な順として前記ピン順位を決定するようにしてもよい。

【0235】

この構成によれば、ピン順位決定部は、電源ピンを流れる電流によって駆動される信号の電圧波形から得られる最高周波数の順を前記重大な順として前記ピン順位を決定することができる。

ここで、前記ピン順位設定部は、電源ネット毎に、そのネットに接続される電源ピンに対して前記ピン優先順位を決定し、前記割付部は、電源ネット毎に、ネットに接続される部品を対象に前記割付を行うようにしてもよい。

【0236】

この構成によれば、電源ネット毎に独立して、ノイズを生じさせる電源ピンに対して受動部品を割り付けることができる。

また、本発明の設計支援装置は、能動部品を含む前記第1種の部品と、ノイズ対策用の受動部品である第2種の部品とに対して、第1種に属する部品の近傍に第2種に属する部品を配置するプリント配線基板の設計支援装置であって、

第1種に属する部品の電源ピンに対して、電源ピンを流れる電流に発生し得るノイズの重大な順にピン順位を決定する第1決定部と、

第2種に属する部品に対して、そのインピーダンス値の小さい順に部品順位を決定する第2決定部と、

部品順位の高い第2種の部品ほど、ピン順位の高い電源ピンを持つ第1種の部品に割付ける割付部と、

割り付けられた電源ピンをもつ第1種に属する部品の近傍に第2種に属する部品を部品順位の順に配置する配置部と、

接続されるべき複数の部品ピンからなるネットを示すネット情報を記憶する記憶部と、

ネット情報に基づいて、電源ピンが接続されるべき電源ネットを、1個の第1種の部品とそれに割り付けられた第2種の部品とからなる部品群に対応する部分ネットに分割する分割部と、

部分ネット毎に、部分ネットに接続される第2種の部品のうち最もインピーダンスの大きい部品の電源ピンを代表ピンとして選択する選択部と、

部分ネットをそれぞれ独立に配線するとともに、複数の前記代表ピンを接続するよう配線する配線部とを備える。

【0237】

この構成によれば、電源ネットを部分ネットに分割し、複数の部分ネットを接続する代表ピンからなるネットと、独立に配線するので、部分ネット間のノイズの伝播を低減することができる。

また、本発明の設計支援装置は、配線基板の部品配置を表示して、配置位置によって効果が異なる部品である位置依存部品の配置が適切か否かのユーザによる評価を支援する設計支援装置であって、

配線基板上の各部品の位置を示す位置情報を記憶する設計情報記憶部と、

位置依存部品と、その位置依存部品によって効果を及ぼされる被効果部品とを関係づけた関係情報を記憶する関係情報記憶部と、

位置情報に従って、前記関係情報により関係づけられた位置依存部品と被効果部品とを、ユーザが認識可能な態様で対応づけて表示する表示部とを備える。

【0238】

この構成によれば、対応する被効果部品と位置依存部品とを対応づけて表示することができる。従って、位置依存部品の配置が適切か否かの評価をユーザが容易に行うことができる。

ここで、前記表示部は、関係づけられている位置依存部品と被効果部品とを線で結ぶことにより対応づけて表示するようにしてもよい。

【0239】

ここで、 前記表示部は、前記位置情報に従って位置依存部品のピン及び位置依存部品の本体の一方と、被効果部品のピン及び被効果部品の本体の一方とを線で結ぶようにしてもよい。

この構成によれば、対応する被効果部品と位置依存部品とを線で結んて表示するので、被効果部品や位置依存部品の数が多くなろうとも表示が見にくくならず、位置依存部品の配置が適切か否かの評価をユーザが容易に行うことができる。

63 ここで、前記関係情報記憶部は、さらに、及ぼされる効果の度合いを示す有効度を記憶し、前記表示部は、さらに、関係情報記憶部に記憶された有効度をユーザが認識可能な態様で表示するように構成してもよい。

【0240】

この構成によれば、有効度をユーザに認識させることができるので、位置依存部品の配置が適切か否かの評価を、ユーザが有効度まで考慮して行うことができる。

ここで、前記表示部は、関係づけられている位置依存部品と被効果部品とを、有効度の違いに応じて異なる表示態様の線を用いて結ぶようにしてもよい。

【0241】

この構成によれば、有効度の違いを、線の違いによって表示することができる。従って、被効果部品や位置依存部品の数が多くなろうとも有効度まで考慮した表示が見にくくならず、位置依存部品の配置が適切か否かの評価を、ユーザが有効度まで考慮して行うことができる。

ここで、前記表示部は、有効度の違いを、線の太さ、線の形状、線の色、線の濃淡、又は、線の模様の違いで区別するようにしてもよい。

【0242】

この構成によれば、有効度の違いを、線の太さ、線の形状、線の色、線の濃淡、又は、線の模様の違いで区別して表示することができる。

ここで、設計支援装置はさらに、位置情報記憶部に記憶された位置情報に基づいて、位置依存部品と、その位置依存部品によって効果を及ぼされる被効果部品とを検索する検索部を備え、

前記関係情報記憶部は、検索部によって検索された位置依存部品と被効果部品とを関連づけて記憶するようにしてもよい。

【0243】

この構成によれば、設計情報から位置依存部品と、その位置依存部品によって効果を及ぼされる被効果部品とを検索することができる。

ここで、前記検索部は、予め定めた距離以内にある位置依存部品と被効果部品とを検索するようにしてもよい。

これによって、位置依存部品との距離が予め定めた距離以内にある被効果部品を関係づけて記憶することができる。

【0244】

ここで、前記検索部は、位置依存部品毎に、当該位置依存部品からの距離が近い方から予め定めた順番までの部品であって被効果部品を検索するようにしてもよい。

これによって、位置依存部品毎に、被効果部品まで距離が近い方から予め定めた順番までの被効果部品を関係づけて記憶することができる。

【0245】

ここで、前記検索部は、さらに、距離又は順番に応じて、及ぼされる効果の度合いを示す有効度を設定するようにしてもよい。

これによって、距離又は順番に応じて有効度を設定するので、有効度まで考慮したより正確な関係情報を生成することができる。

ここで、前記位置依存部品はコンデンサであり、

前記被効果部品は、コンデンサによりノイズ除去の効果を及ぼされる可能性があるスイッチング素子であり、

前記検索部は、さらに、スイッチング素子のノイズ除去に必要な容量が、コンデンサの容量を越えない範囲で検索するようにしてもよい。

【0246】

この構成によれば、コンデンサの容量を越えない範囲で、スイッチング素子を関係づけることができる。

ここで 前記検索部は、さらに、複数のスイッチング素子のノイズ除去に必要な容量を合計した値が、コンデンサの容量を越えない範囲で検索するようにしてもよい。

【0247】

この構成によれば、コンデンサの容量を越えない範囲で、複数のスイッチング素子を関係づけることができる。

ここで、前記検索部は、さらに、複数のスイッチング素子のノイズ除去に必要な容量を合計した値に、同時にスイッチングされる比率を掛けて補正した値が、コンデンサの容量を越えない範囲で検索するようにしてもよい

この構成によれば、コンデンサの容量を越えない範囲で、複数のスイッチング素子を、より正確により多く関係づけることができる。

【0248】

ここで、前記検索部は、さらに、前記位置依存部品と前記被効果部品との周波数特性が一致する場合にのみ、検索するようにしてもよい。

この構成によれば、周波数特性まで考慮したより正確な関係情報を生成することができる。

ここで、前記検索部における距離は、直線距離、マンハッタン距離、実際の配線距離、及び、ループ面積が最小になる経路距離のいずれかとしてもよい。

【0249】

この構成によれば、配線の態様に応じて、直線距離、マンハッタン距離、実際の配線距離、及び、ループ面積が最小になる経路距離のいずれかの距離を選択することができる。

ここで、前記設計支援装置は、さらに、前記位置情報記憶部に記憶された被効果部品又は当該被効果部品が備えるピンの中から、前記関係情報記憶部により記憶された関係情報によって何れの位置依存部品又は位置依存部品が備えるピンにも関係づけられていない被効果部品又は被効果部品が備えるピンを抽出する抽出部と、 抽出部により抽出された被効果部品又は被効果部品が備えるピンを、ユーザが認識可能な態様で表示する表示部とを備える構成としてもよい。

【0250】

この構成によれば、いずれの位置依存部品にも関係づけられていない被効果部品又は被効果部品のピンを表示することができる。従って、位置依存部品の配置漏れを容易に発見することができる。

ここで、前記設計支援装置は、さらに、

前記位置情報記憶部に記憶された位置依存部品又は当該位置依存部品が備えるピンの中から、前記関係情報記憶部により記憶された関係情報によって何れの被効果部品又は被効果部品が備えるピンにも関係づけられていない位置依存部品又は位置依存部品が備えるピンを抽出する抽出部と、

抽出部により抽出された位置依存部品又は位置依存部品が備えるピンを、ユーザが認識可能な態様で表示する表示部とを備える構成としてもよい。

【0251】

この構成によれば、いずれの位置依存部品にも関係づけられていない被効果部品又は被効果部品のピンを表示することができる。従って、位置依存部品の配置漏れを容易に発見することができる。

また、本発明のプログラムは、上記の各部をコンピュータに実現させるプログラムである。

【図面の簡単な説明】

【図1】部品種類による部品の割付け結果を示す概念図である。

【図2】従来技術におけるCAD装置のモニター上に表示された、設計中の配線基板を示す図である。

【図3】本発明の実施の形態1におけるCAD装置の構成を示すブロック図である。

【図4】CAD装置の外観図である。

【図5】部品情報リスト1201の一例を示す図である。

【図6】部品マスタ情報リスト1301の一例を示す図である。

【図7】ネット情報リスト1401の一例を示す図である。

【図8】ピン情報リスト1501の一例を示す図である。

【図9】有効周波数リスト1601の一例を示す図である。

【図10】部品形状情報リスト1701の一例を示す図である。

【図11】部品優先順位設定部1106における部品優先順位設定処理(A)の詳細を示すフローチャートである。

【図12】部品優先順位設定部1106における部品優先順位設定処理(B)の詳細を示すフローチャートである。

【図13】部品優先順位設定部1106における部品優先順位設定処理(C)の詳細を示すフローチャートである。

【図14】CAD装置1000の概要動作を示すフローチャートである。

【図15】実施の形態2におけるCAD装置2000の構成を示すブロック図である。

【図16】部品優先順位設定部1106における部品優先順位設定処理(C’)の詳細を示すフローチャートである。

【図17】L値から算出されたf−Z特性における有効周波数域を決定する際の概念図である。

【図18】C値から算出されたf−Z特性における有効周波数域を決定する際の概念図である。

【図19】L値及びC値から算出されたf−Z特性における有効周波数域を決定する際の概念図である。

【図20】CAD装置2000の概要動作を示すフローチャートである。

【図21】実施の形態3におけるCAD装置3000の構成を示すブロック図である。

【図22】ピン優先順位設定部3105による詳細なピン優先順位設定処理を示すフローチャートを示す。

【図23】部品割付け部3106における割り付け処理の具体例を示すフローチャートである。

【図24】CAD装置3000の概要動作を示すフローチャートである。

【図25】部品番号3501と部品番号3501に割付けられた部品の概念図である。

【図26】部品番号3501のピンから電源ピンを検出する際の概念図である。

【図27】本発明による部品の割付け結果を示す概念図である。

【図28】実施の形態4におけるCAD装置4000の構成を示すブロック図である。

【図29】ピン使用周波数域設定部4102の詳細なピン処理内容を示すフローチャートを示す。

【図30】ピン優先順位設定部4103におけるピン優先順位設定処理を示すフローチャートである。

【図31】第2の階層ネットを示した概念図である。

【図32】信号電圧を周波数成分に分割した概念図である。

【図33】CAD装置4000の概要動作を示すフローチャートである。

【図34】実施の形態5におけるCAD装置5000の構成を示すブロック図である。

【図35】CAD装置5000の概要動作を示すフローチャートである。

【図36】CAD装置5000の設計情報記憶部1108に記憶されている階層ネット情報リスト1801の一例を示す図である。

【図37】第1の階層ネットを示した概念図である。

【図38】実施の形態6に係るCAD装置の構成を示す図である。

【図39】(a)設計情報に含まれる部品情報の一例を示す。

(b)設計情報に含まれるピン情報の一例を示す。

(c)設計情報に含まれるネット情報の一例を示す。

【図40】バイパスコンデンサグループ化部14により作成され、バイパスコンデンサグループ情報記憶部15に記憶されるグループ情報の一例を示す図である。

【図41】本実施の形態のCAD装置10の動作の一例を示す図である。

【図42】ICピンとバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例である。

【図43】(a)〜(c)複数のICピンと1つのバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例を示す図である。

【図44】(a)(b) 有効度を考慮して、ICピンとバイパスコンデンサピンとを線で結ぶ場合に、モニタ20に表示される画像の表示例である。

【図45】本実施の形態のCAD装置10の動作の一例を示す図である。

【図46】(a)周波数特性を考慮した場合に、モニタ20に表示される画像の表示例を示す図である。

(b)容量を考慮した場合に、モニタ20に表示される画像の表示例を示す図である。

【図47】配線基板の厚さをも考慮してより正確に距離を算定する方法の概略を説明する為の、配線基板の断面を示す図である。

【図48】多層基板においてループ面積が最小になるような経路距離を算定する方法の一例を説明する為の、配線基板を側面及び上面から見た図である。

【図49】ループ面積が最小になるような経路距離を算定する方法の一例を説明する為の、配線基板を上面から見た図である。

【図50】バイパスコンデンサのインピーダンスZと周波数fとの関係を示す図である。

【図51】(a)電源ネット又はグランドネットに属するICピンの周波数を算出する為の、デバイスモデルを示す図である。

(b)ピン電流I(t)と時間tとの関係を示す図である。

(c)周波数領域の電流I(f)と周波数fとの関係を示す図である。

【図52】実施の形態7に係るCAD装置の構成を示す図である。

【図53】本実施の形態のCAD装置30の動作の一例を示す図である。

【図54】バイパスコンデンサ未対応ピンをユーザが認識可能な態様で表示する場合に、モニタ20に表示される画像の表示例である。

【図55】実施の形態8に係るCAD装置の構成を示す図である。

【図56】本実施の形態のCAD装置40の動作の一例を示す図である。

【図57】未使用コンデンサをユーザが認識可能な態様で表示する場合に、モニタ20に表示される画像の表示例である。

【符号の説明】

10 CAD装置

11 設計情報入手部

12 設計情報記憶部

13 バイパスコンデンサ評価部

14 バイパスコンデンサグループ化部

15 バイパスコンデンサグループ情報記憶部

16 コマンド入手部

17 コマンド解析部

18 実装部品表示部

19 バイパスコンデンサグループ表示部

20 モニタ

21 設計情報出力部

30 CAD装置

31 未対応ピン検索部

32 未対応ピン表示部

39 有効度

40 CAD装置

41 未使用コンデンサ検索部

42 未使用コンデンサ表示部

1000 CAD装置

1101 コマンド入力部

1102 データ入力部

1103 制御部

1104 コマンド入力解析部

1105 部品検出部

1106 部品優先順位設定部

1107 配置部

1108 設計情報記憶部

1109 表示部

1201 部品情報リスト

1202 部品番号

1203 部品名

1204 部品形状

1205 配置面

1206 基準点座標

1207 部品優先順位

1207 優先順位

1208 主部品番号

1209 付随部品番号

1210 部品グループ

1210 部品グループ名

1220 主部品

1220 部品

1220 部品番号

1221 部品名

1222 部品グループ

1223 付随部品番号

1223 部品番号

1230 当該付随部品

1230 部品

1230 部品番号

1232 部品形状

1233 部品優先順位

1234 主部品番号

1301 部品マスタ情報リスト

1401 ネット情報リスト

1501 ピン情報リスト

1601 有効周波数域情報リスト

1701 部品形状情報リスト

1801 階層ネット情報リスト

2000 CAD装置

2101 制御部

2101 配線基板

2102 有効周波数域設定部

2103 部品優先順位設定部

3000 CAD装置

3101 制御部

3102 ネット検出部

3103 ピン検出部

3104 部品グループ設定部

3105 ピン優先順位設定部

3105 優先順位設定部

3107 設計情報記憶部

4000 CAD装置

4101 制御部

4102 ピン使用周波数域設定部

4103 ピン優先順位設定部

5000 CAD装置

5101 制御部

5102 階層ネット設定部

5103 代表ピン選択部

5104 未結線表示部

5105 配線部

5106 設計情報記憶部

Claims (11)

- プリント配線基板の設計を支援する設計支援装置であって、

プリント配線基板に配置すべき部品のうち、受動部品に対して、部品の等価直列インダクタンスに応じたインピーダンス値の小さい順に部品順位を決定する決定手段と、

部品順位の高い順に受動部品を、それが割り付けられた電源ピンの近傍に配置する配置手段と、

受動部品以外の部品の電源ピンに対して、電源ピンを流れる電流によって駆動される信号から推定されるノイズの重大な順にピン順位を設定するピン順位決定手段と、

電源ピンをもつ部品に対する受動部品の割付けを、ピン順位及び部品順位の高い順に行なう割付手段と

を備えることを特徴とする設計支援装置。 - 請求項1記載の設計支援装置において

前記配置手段は、受動部品以外の配置済み部品の電源ピンの近傍に受動部品を配置することを特徴とする設計支援装置。 - 請求項2記載の設計支援装置において

前記受動部品は、キャパシタ素子であり、

前記決定手段は、キャパシタ素子の等価直列インダクタンスの小さい順をインピーダンスの小さい順として前記部品順位を決定する

ことを特徴とする設計支援装置。 - 請求項2記載の設計支援装置において

前記受動部品は、キャパシタ素子であり、

前記決定手段は、キャパシタ素子のインピーダンスがしきい値以下となる周波数域である有効周波数域の高い順を、前記インピーダンスの小さい順として前記部品順位を決定する

ことを特徴とする設計支援装置。 - 請求項1記載の設計支援装置において、

前記ピン順位設定手段は、電源ネット毎に、そのネットに接続される電源ピンに対して前記ピン優先順位を決定し、

前記割付手段は、電源ネット毎に、ネットに接続される部品を対象に前記割付を行うことを特徴とする設計支援装置。 - 第1種に属する部品の近傍に第2種に属する部品を配置するプリント配線基板の設計支援装置であって、

第1種に属する部品の電源ピンに対して、電源ピンを流れる電流によって駆動される信号から推定されるノイズの重大な順にピン順位を設定する第1決定手段と、

第2種に属する部品に対して、その等価直列インダクタンスに応じたインピーダンス値の小さい順に部品順位を決定する第2決定手段と、

部品順位の高い第2種の部品ほど、ピン順位の高い電源ピンを持つ第1種の部品に割付ける割付手段と、

を備えることを特徴とする設計支援装置。 - 請求項6記載の設計支援装置は、さらに

割り付けられた電源ピンをもつ第1種に属する部品の近傍に第2種に属する部品を部品順位の順に配置する配置手段を備えることを特徴とする設計支援装置。 - 請求項7記載の設計支援装置において、

前記第1決定手段は、電源ピンを流れる電流によって駆動される信号周波数の高い順を前記重大な順として前記ピン順位を設定する

ことを特徴とする設計支援装置。 - 請求項7記載の設計支援装置において、

前記ピン順位決定手段は、電源ピンを流れる電流によって駆動される信号の立ち上がり時間及び立ち下がり時間の何れかについて、その短い順を前記重大な順として前記ピン順位を決定する

ことを特徴とする設計支援装置。 - 請求項9に記載の設計支援装置において、

前記第2決定手段は、受動部品の等価直列インダクタンスの小さい順をインピーダンスの小さい順として前記部品順位を決定する

ことを特徴とする設計支援装置。 - 請求項7記載の設計支援装置は、さらに

接続されるべき複数の部品ピンからなるネットを示すネット情報を記憶する記憶手段と、

ネット情報に基づいて、電源ピンが接続されるべき電源ネットを、1個の第1種の部品とそれに割り付けられた第2種の部品とからなる部品群に対応する部分ネットに分割する分割手段と、

部分ネット毎に、部分ネットに接続される第2種の部品のうち最もインピーダンスの大きい部品の電源ピンを代表ピンとして選択する選択手段と、

部分ネットをそれぞれ独立に配線するとともに、複数の前記代表ピンを接続するよう配線する配線手段と

を備えることを特徴とする設計支援装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001019268A JP4649047B2 (ja) | 2000-01-27 | 2001-01-26 | ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000018405 | 2000-01-27 | ||

| JP2000-20843 | 2000-01-28 | ||

| JP2000020843 | 2000-01-28 | ||

| JP2000-18405 | 2000-01-28 | ||

| JP2001019268A JP4649047B2 (ja) | 2000-01-27 | 2001-01-26 | ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001282882A JP2001282882A (ja) | 2001-10-12 |

| JP2001282882A5 JP2001282882A5 (ja) | 2008-02-28 |

| JP4649047B2 true JP4649047B2 (ja) | 2011-03-09 |

Family

ID=27342150

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001019268A Expired - Fee Related JP4649047B2 (ja) | 2000-01-27 | 2001-01-26 | ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4649047B2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7117459B2 (en) | 2002-11-26 | 2006-10-03 | Matsushita Electric Industrial Co., Ltd. | Layout check system |

| WO2005038675A1 (ja) | 2003-10-15 | 2005-04-28 | Zuken Inc. | プリント基板設計指示支援方法およびその装置 |

| JP2009151363A (ja) * | 2007-12-18 | 2009-07-09 | Ydc Corp | 基板設計装置 |

| US7957150B2 (en) * | 2008-02-21 | 2011-06-07 | Hitachi, Ltd. | Support method and apparatus for printed circuit board |

| JP2010098162A (ja) * | 2008-10-17 | 2010-04-30 | Hitachi Ltd | プリント配線基板および設計支援システム |

| JP5253244B2 (ja) * | 2009-03-12 | 2013-07-31 | キヤノン株式会社 | プリント基板設計支援プログラム、方法及び装置 |

| JP5668394B2 (ja) * | 2010-09-30 | 2015-02-12 | 富士通株式会社 | 設計チェックプログラム、設計チェック装置及び設計チェック方法 |

| JP5640712B2 (ja) * | 2010-12-10 | 2014-12-17 | 日本電気株式会社 | 半導体装置の設計支援装置、キャパシタ配置方法、及びプログラム |

| JP6421467B2 (ja) * | 2014-06-11 | 2018-11-14 | 株式会社リコー | Emi対策用コンデンサの実装方法 |

| CN114239451B (zh) * | 2021-12-06 | 2024-10-29 | 成都海光集成电路设计有限公司 | 一种电源开关单元的连接关系优化方法和装置 |

-

2001

- 2001-01-26 JP JP2001019268A patent/JP4649047B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001282882A (ja) | 2001-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7120885B2 (en) | Computer aided design apparatus for aiding design of a printed wiring board to effectively reduce noise | |

| JP4649047B2 (ja) | ノイズ低減に適したプリント配線基板の設計を支援する設計支援装置 | |

| US8104003B2 (en) | Technique for creating analysis model and technique for creating circuit board model | |

| US7412683B2 (en) | Printed wiring board design method, program therefor, recording medium storing the program recorded therein, printed wiring board design device using them and CAD system | |

| US5729467A (en) | Method of and system for routing | |

| JPH0444983B2 (ja) | ||

| US20040250230A1 (en) | Wiring design method and system for electronic wiring boards | |

| WO2005045711A2 (en) | Elastic assembly floor plan design tool | |

| US7093220B2 (en) | Method for generating constrained component placement for integrated circuits and packages | |

| CN1199273C (zh) | 半导体装置及其设计方法和设计装置 | |

| EP1083502A1 (en) | Noise checking method and device | |

| US7975253B2 (en) | Power supply noise analysis model generating method and power supply noise analysis model generating apparatus | |

| JP3339531B2 (ja) | プリント基板設計方法およびシステム | |

| JP2004334654A (ja) | 電源ノイズ解析モデル生成装置、電源ノイズ解析モデル生成方法、電源ノイズ解析モデル生成プログラム | |

| US7340710B1 (en) | Integrated circuit binning and layout design system | |

| CN117291140B (zh) | 自动布线工具的绕线违例减少方法、装置、存储介质及电子终端 | |

| US20010032222A1 (en) | System, method and computer accessible storage medium, for creating and editing structured parts list | |

| US6505336B1 (en) | Channel router with buffer insertion | |

| JPH1049568A (ja) | 回路基板設計方法及び記録媒体 | |

| JP2020017211A (ja) | ノイズ経路算出プログラム、ノイズ経路算出方法、及び情報処理装置 | |

| Li et al. | A gridless routing system with nonslicing floorplanning-based crosstalk reduction on gridless track assignment | |

| CN100458771C (zh) | 辅助布线系统及方法 | |

| JP4071351B2 (ja) | プリント基板設計cadシステム | |

| JPWO2014111969A1 (ja) | 設計方法、プログラム、メモリ媒体および設計装置 | |

| JPH07192038A (ja) | レイアウト中の回路のルート指示及び再区分用図形表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080108 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080108 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100223 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100406 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100713 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100819 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101116 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101213 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131217 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |