JP4583776B2 - 表示装置の作製方法 - Google Patents

表示装置の作製方法 Download PDFInfo

- Publication number

- JP4583776B2 JP4583776B2 JP2004037405A JP2004037405A JP4583776B2 JP 4583776 B2 JP4583776 B2 JP 4583776B2 JP 2004037405 A JP2004037405 A JP 2004037405A JP 2004037405 A JP2004037405 A JP 2004037405A JP 4583776 B2 JP4583776 B2 JP 4583776B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- transistor

- tft

- pixel

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 266

- 238000004519 manufacturing process Methods 0.000 title claims description 28

- 239000004065 semiconductor Substances 0.000 claims description 158

- 239000000758 substrate Substances 0.000 claims description 73

- 238000007639 printing Methods 0.000 claims description 39

- 239000004020 conductor Substances 0.000 claims description 24

- 238000005530 etching Methods 0.000 claims description 23

- 230000001681 protective effect Effects 0.000 claims description 15

- 238000005192 partition Methods 0.000 claims description 13

- 238000000576 coating method Methods 0.000 claims description 4

- 238000007599 discharging Methods 0.000 claims description 3

- 239000010408 film Substances 0.000 description 250

- 239000010410 layer Substances 0.000 description 121

- 239000003990 capacitor Substances 0.000 description 118

- 239000000463 material Substances 0.000 description 48

- 239000011229 interlayer Substances 0.000 description 30

- 239000007789 gas Substances 0.000 description 28

- 238000003860 storage Methods 0.000 description 27

- 238000010586 diagram Methods 0.000 description 26

- 235000019557 luminance Nutrition 0.000 description 24

- 230000002829 reductive effect Effects 0.000 description 21

- 229910052751 metal Inorganic materials 0.000 description 19

- 239000002184 metal Substances 0.000 description 19

- 229910052581 Si3N4 Inorganic materials 0.000 description 18

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 18

- 238000005070 sampling Methods 0.000 description 18

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 18

- 238000002347 injection Methods 0.000 description 17

- 239000007924 injection Substances 0.000 description 17

- 102100029768 Histone-lysine N-methyltransferase SETD1A Human genes 0.000 description 15

- 101000865038 Homo sapiens Histone-lysine N-methyltransferase SETD1A Proteins 0.000 description 15

- 239000012535 impurity Substances 0.000 description 14

- 150000002736 metal compounds Chemical class 0.000 description 14

- 238000000059 patterning Methods 0.000 description 14

- 101100218322 Arabidopsis thaliana ATXR3 gene Proteins 0.000 description 12

- 102100032742 Histone-lysine N-methyltransferase SETD2 Human genes 0.000 description 12

- 101100149326 Homo sapiens SETD2 gene Proteins 0.000 description 12

- LZHSWRWIMQRTOP-UHFFFAOYSA-N N-(furan-2-ylmethyl)-3-[4-[methyl(propyl)amino]-6-(trifluoromethyl)pyrimidin-2-yl]sulfanylpropanamide Chemical compound CCCN(C)C1=NC(=NC(=C1)C(F)(F)F)SCCC(=O)NCC2=CC=CO2 LZHSWRWIMQRTOP-UHFFFAOYSA-N 0.000 description 12

- 101100533304 Plasmodium falciparum (isolate 3D7) SETVS gene Proteins 0.000 description 12

- 101150117538 Set2 gene Proteins 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 12

- 238000001459 lithography Methods 0.000 description 12

- 239000000203 mixture Substances 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 230000006870 function Effects 0.000 description 11

- 229910021332 silicide Inorganic materials 0.000 description 11

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 11

- 229910052814 silicon oxide Inorganic materials 0.000 description 11

- 239000012298 atmosphere Substances 0.000 description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 10

- 239000013078 crystal Substances 0.000 description 10

- 239000011159 matrix material Substances 0.000 description 10

- 150000002894 organic compounds Chemical class 0.000 description 10

- 229910052760 oxygen Inorganic materials 0.000 description 10

- 239000001301 oxygen Substances 0.000 description 10

- 239000002904 solvent Substances 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 10

- 238000002161 passivation Methods 0.000 description 9

- BCMCBBGGLRIHSE-UHFFFAOYSA-N 1,3-benzoxazole Chemical class C1=CC=C2OC=NC2=C1 BCMCBBGGLRIHSE-UHFFFAOYSA-N 0.000 description 8

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 8

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 8

- 230000008859 change Effects 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- 230000006866 deterioration Effects 0.000 description 8

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 8

- 229910052709 silver Inorganic materials 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 8

- -1 Li and Cs Chemical class 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 7

- 230000005525 hole transport Effects 0.000 description 7

- 229910044991 metal oxide Inorganic materials 0.000 description 7

- 150000004706 metal oxides Chemical class 0.000 description 7

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 7

- 239000011368 organic material Substances 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 239000011787 zinc oxide Substances 0.000 description 7

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical group C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 239000011521 glass Substances 0.000 description 6

- 239000001257 hydrogen Substances 0.000 description 6

- 229910052739 hydrogen Inorganic materials 0.000 description 6

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- 229910052783 alkali metal Inorganic materials 0.000 description 5

- 150000001340 alkali metals Chemical class 0.000 description 5

- 125000004429 atom Chemical group 0.000 description 5

- 229910052796 boron Inorganic materials 0.000 description 5

- 239000003086 colorant Substances 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 5

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 5

- 239000000243 solution Substances 0.000 description 5

- 229910001935 vanadium oxide Inorganic materials 0.000 description 5

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 4

- 150000001342 alkaline earth metals Chemical class 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 229910052744 lithium Inorganic materials 0.000 description 4

- 150000002739 metals Chemical class 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 239000003960 organic solvent Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 239000011701 zinc Substances 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 239000004372 Polyvinyl alcohol Substances 0.000 description 3

- 229910010413 TiO 2 Inorganic materials 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000000354 decomposition reaction Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229920002451 polyvinyl alcohol Polymers 0.000 description 3

- 230000000717 retained effect Effects 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 229910052723 transition metal Inorganic materials 0.000 description 3

- 150000003624 transition metals Chemical class 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 2

- STTGYIUESPWXOW-UHFFFAOYSA-N 2,9-dimethyl-4,7-diphenyl-1,10-phenanthroline Chemical compound C=12C=CC3=C(C=4C=CC=CC=4)C=C(C)N=C3C2=NC(C)=CC=1C1=CC=CC=C1 STTGYIUESPWXOW-UHFFFAOYSA-N 0.000 description 2

- UOCMXZLNHQBBOS-UHFFFAOYSA-N 2-(1,3-benzoxazol-2-yl)phenol zinc Chemical compound [Zn].Oc1ccccc1-c1nc2ccccc2o1.Oc1ccccc1-c1nc2ccccc2o1 UOCMXZLNHQBBOS-UHFFFAOYSA-N 0.000 description 2

- ZVFQEOPUXVPSLB-UHFFFAOYSA-N 3-(4-tert-butylphenyl)-4-phenyl-5-(4-phenylphenyl)-1,2,4-triazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C(N1C=2C=CC=CC=2)=NN=C1C1=CC=C(C=2C=CC=CC=2)C=C1 ZVFQEOPUXVPSLB-UHFFFAOYSA-N 0.000 description 2

- DHDHJYNTEFLIHY-UHFFFAOYSA-N 4,7-diphenyl-1,10-phenanthroline Chemical compound C1=CC=CC=C1C1=CC=NC2=C1C=CC1=C(C=3C=CC=CC=3)C=CN=C21 DHDHJYNTEFLIHY-UHFFFAOYSA-N 0.000 description 2

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- 101100043929 Arabidopsis thaliana SUVH2 gene Proteins 0.000 description 2

- NLZUEZXRPGMBCV-UHFFFAOYSA-N Butylhydroxytoluene Chemical compound CC1=CC(C(C)(C)C)=C(O)C(C(C)(C)C)=C1 NLZUEZXRPGMBCV-UHFFFAOYSA-N 0.000 description 2

- 229910004261 CaF 2 Inorganic materials 0.000 description 2

- 101100043931 Chlamydomonas reinhardtii SUVH3 gene Proteins 0.000 description 2

- 241000284156 Clerodendrum quadriloculare Species 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- 101150057295 SET3 gene Proteins 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 239000007983 Tris buffer Substances 0.000 description 2

- 230000002776 aggregation Effects 0.000 description 2

- 238000004220 aggregation Methods 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- VREFGVBLTWBCJP-UHFFFAOYSA-N alprazolam Chemical compound C12=CC(Cl)=CC=C2N2C(C)=NN=C2CN=C1C1=CC=CC=C1 VREFGVBLTWBCJP-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- UFVXQDWNSAGPHN-UHFFFAOYSA-K bis[(2-methylquinolin-8-yl)oxy]-(4-phenylphenoxy)alumane Chemical compound [Al+3].C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC([O-])=CC=C1C1=CC=CC=C1 UFVXQDWNSAGPHN-UHFFFAOYSA-K 0.000 description 2

- QDWJUBJKEHXSMT-UHFFFAOYSA-N boranylidynenickel Chemical compound [Ni]#B QDWJUBJKEHXSMT-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 230000018109 developmental process Effects 0.000 description 2

- ZUOUZKKEUPVFJK-UHFFFAOYSA-N diphenyl Chemical compound C1=CC=CC=C1C1=CC=CC=C1 ZUOUZKKEUPVFJK-UHFFFAOYSA-N 0.000 description 2

- 239000002270 dispersing agent Substances 0.000 description 2

- 230000007613 environmental effect Effects 0.000 description 2

- 235000019441 ethanol Nutrition 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- 229910001867 inorganic solvent Inorganic materials 0.000 description 2

- 239000003049 inorganic solvent Substances 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 238000012423 maintenance Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical group C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- JMANVNJQNLATNU-UHFFFAOYSA-N oxalonitrile Chemical compound N#CC#N JMANVNJQNLATNU-UHFFFAOYSA-N 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920000123 polythiophene Polymers 0.000 description 2

- 238000010248 power generation Methods 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 238000003980 solgel method Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- BGHCVCJVXZWKCC-UHFFFAOYSA-N tetradecane Chemical compound CCCCCCCCCCCCCC BGHCVCJVXZWKCC-UHFFFAOYSA-N 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- POILWHVDKZOXJZ-ARJAWSKDSA-M (z)-4-oxopent-2-en-2-olate Chemical compound C\C([O-])=C\C(C)=O POILWHVDKZOXJZ-ARJAWSKDSA-M 0.000 description 1

- VFMUXPQZKOKPOF-UHFFFAOYSA-N 2,3,7,8,12,13,17,18-octaethyl-21,23-dihydroporphyrin platinum Chemical compound [Pt].CCc1c(CC)c2cc3[nH]c(cc4nc(cc5[nH]c(cc1n2)c(CC)c5CC)c(CC)c4CC)c(CC)c3CC VFMUXPQZKOKPOF-UHFFFAOYSA-N 0.000 description 1

- SNTWKPAKVQFCCF-UHFFFAOYSA-N 2,3-dihydro-1h-triazole Chemical compound N1NC=CN1 SNTWKPAKVQFCCF-UHFFFAOYSA-N 0.000 description 1

- FQJQNLKWTRGIEB-UHFFFAOYSA-N 2-(4-tert-butylphenyl)-5-[3-[5-(4-tert-butylphenyl)-1,3,4-oxadiazol-2-yl]phenyl]-1,3,4-oxadiazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=C(C=CC=2)C=2OC(=NN=2)C=2C=CC(=CC=2)C(C)(C)C)O1 FQJQNLKWTRGIEB-UHFFFAOYSA-N 0.000 description 1

- GEQBRULPNIVQPP-UHFFFAOYSA-N 2-[3,5-bis(1-phenylbenzimidazol-2-yl)phenyl]-1-phenylbenzimidazole Chemical compound C1=CC=CC=C1N1C2=CC=CC=C2N=C1C1=CC(C=2N(C3=CC=CC=C3N=2)C=2C=CC=CC=2)=CC(C=2N(C3=CC=CC=C3N=2)C=2C=CC=CC=2)=C1 GEQBRULPNIVQPP-UHFFFAOYSA-N 0.000 description 1

- AWXGSYPUMWKTBR-UHFFFAOYSA-N 4-carbazol-9-yl-n,n-bis(4-carbazol-9-ylphenyl)aniline Chemical compound C12=CC=CC=C2C2=CC=CC=C2N1C1=CC=C(N(C=2C=CC(=CC=2)N2C3=CC=CC=C3C3=CC=CC=C32)C=2C=CC(=CC=2)N2C3=CC=CC=C3C3=CC=CC=C32)C=C1 AWXGSYPUMWKTBR-UHFFFAOYSA-N 0.000 description 1

- 125000004860 4-ethylphenyl group Chemical group [H]C1=C([H])C(=C([H])C([H])=C1*)C([H])([H])C([H])([H])[H] 0.000 description 1

- DIVZFUBWFAOMCW-UHFFFAOYSA-N 4-n-(3-methylphenyl)-1-n,1-n-bis[4-(n-(3-methylphenyl)anilino)phenyl]-4-n-phenylbenzene-1,4-diamine Chemical compound CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)N(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 DIVZFUBWFAOMCW-UHFFFAOYSA-N 0.000 description 1

- 229920001621 AMOLED Polymers 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 241001609030 Brosme brosme Species 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 101000837344 Homo sapiens T-cell leukemia translocation-altered gene protein Proteins 0.000 description 1

- 229910018068 Li 2 O Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 101100154789 Mus musculus Tulp4 gene Proteins 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- NRCMAYZCPIVABH-UHFFFAOYSA-N Quinacridone Chemical class N1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3NC1=C2 NRCMAYZCPIVABH-UHFFFAOYSA-N 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 102100028692 T-cell leukemia translocation-altered gene protein Human genes 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- 229910008322 ZrN Inorganic materials 0.000 description 1

- DDRUQPGRDYOZHB-UHFFFAOYSA-N [Eu].c1ccc2c(c1)ccc1ccccc21 Chemical compound [Eu].c1ccc2c(c1)ccc1ccccc21 DDRUQPGRDYOZHB-UHFFFAOYSA-N 0.000 description 1

- CUJRVFIICFDLGR-UHFFFAOYSA-N acetylacetonate Chemical compound CC(=O)[CH-]C(C)=O CUJRVFIICFDLGR-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 229910001508 alkali metal halide Inorganic materials 0.000 description 1

- 150000008045 alkali metal halides Chemical class 0.000 description 1

- 229910000272 alkali metal oxide Inorganic materials 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 150000001412 amines Chemical class 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 150000004982 aromatic amines Chemical class 0.000 description 1

- 150000001491 aromatic compounds Chemical class 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- WZJYKHNJTSNBHV-UHFFFAOYSA-N benzo[h]quinoline Chemical group C1=CN=C2C3=CC=CC=C3C=CC2=C1 WZJYKHNJTSNBHV-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 235000010290 biphenyl Nutrition 0.000 description 1

- 239000004305 biphenyl Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- XZCJVWCMJYNSQO-UHFFFAOYSA-N butyl pbd Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=CC(=CC=2)C=2C=CC=CC=2)O1 XZCJVWCMJYNSQO-UHFFFAOYSA-N 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 150000004696 coordination complex Chemical class 0.000 description 1

- 150000001893 coumarin derivatives Chemical class 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000007850 fluorescent dye Substances 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 150000004820 halides Chemical class 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 150000002460 imidazoles Chemical class 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229940079865 intestinal antiinfectives imidazole derivative Drugs 0.000 description 1

- UEEXRMUCXBPYOV-UHFFFAOYSA-N iridium;2-phenylpyridine Chemical compound [Ir].C1=CC=CC=C1C1=CC=CC=N1.C1=CC=CC=C1C1=CC=CC=N1.C1=CC=CC=C1C1=CC=CC=N1 UEEXRMUCXBPYOV-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 239000005001 laminate film Substances 0.000 description 1

- 239000003446 ligand Substances 0.000 description 1

- 125000000040 m-tolyl group Chemical group [H]C1=C([H])C(*)=C([H])C(=C1[H])C([H])([H])[H] 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 230000003472 neutralizing effect Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000010943 off-gassing Methods 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 150000004866 oxadiazoles Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000011941 photocatalyst Substances 0.000 description 1

- 238000013032 photocatalytic reaction Methods 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 1

- 229920003223 poly(pyromellitimide-1,4-diphenyl ether) Polymers 0.000 description 1

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 229940005642 polystyrene sulfonic acid Drugs 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 125000002943 quinolinyl group Chemical group N1=C(C=CC2=CC=CC=C12)* 0.000 description 1

- 238000001552 radio frequency sputter deposition Methods 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 150000002910 rare earth metals Chemical class 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 239000005871 repellent Substances 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- PJANXHGTPQOBST-UHFFFAOYSA-N stilbene Chemical class C=1C=CC=CC=1C=CC1=CC=CC=C1 PJANXHGTPQOBST-UHFFFAOYSA-N 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 230000001502 supplementing effect Effects 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229940042055 systemic antimycotics triazole derivative Drugs 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- TVIVIEFSHFOWTE-UHFFFAOYSA-K tri(quinolin-8-yloxy)alumane Chemical compound [Al+3].C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1 TVIVIEFSHFOWTE-UHFFFAOYSA-K 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- GWDUZCIBPDVBJM-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzothiazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1 GWDUZCIBPDVBJM-UHFFFAOYSA-L 0.000 description 1

- QEPMORHSGFRDLW-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzoxazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1 QEPMORHSGFRDLW-UHFFFAOYSA-L 0.000 description 1

Images

Description

前記保持された前記電圧を第2の電流に変換する手段は、前記第1の電流と電流値の等しい第2の電流、又は、前記第1の電流と電流値が比例する第2の電流へ変換する手段であることを含む。

この発明に依る表示装置は、前記デジタルの映像信号とは別の信号によって、前記第2の電流を前記発光素子に流さないようにする手段を有することを含むことを特徴としている。

また、前記表示装置は、デジタルの映像信号とは別の信号によって、第2のトランジスタのドレイン電流を発光素子に流さないようにする手段を有することを特徴としている。

前記表示装置は、さらに、トランジスタのゲート電極とドレイン端子を電気的に接続する手段を有することを含むと共に、前記デジタルの映像信号とは別の信号によって、トランジスタのドレイン電流を発光素子に流さないようにする手段を有することを含むことを特徴としている。

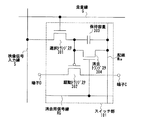

各画素100において、スイッチ部101は端子C及び端子Dを有する。発光素子106の画素電極106aは、スイッチ部の端子Dと接続される。スイッチ部の端子Cは、電流源回路102の端子Bと接続される。電流源回路102の端子Aは電源線Wと接続されている。電流源回路102は、円の中に矢印を配置した記号によって模式的に示す。電流源回路102はこの記号の矢印の方向、つまり端子Aから端子Bの方向に、正の一定電流を流す回路であるとする。端子A又は端子Bの一方を電流源回路102の入力端子、他方を電流源回路102の出力端子と呼ぶ。

発光素子106は、画素電極106aから対向電極106bへ、又はその逆の方向に電流を流し、その電流に応じて輝度が変化する素子を示す。

なお、本発明におけるトランジスタとしては、薄膜トランジスタ(TFT)でも、単結晶トランジスタ等のトランジスタでもどちらでも良い。また、有機物を利用したトランジスタでもよい。

例えば、単結晶トランジスタとしては、SOI技術を用いて形成されたトランジスタとすることができる。薄膜トランジスタとしては、活性層として多結晶半導体、セミアモルファス半導体(微結晶半導体)または非晶質半導体を用いたものでもよい。例えば、ポリシリコンを用いたTFT、セミアモルファスシリコンを用いたTFTまたはアモルファスシリコンを用いたTFTとすることができる。

図4〜図7では、第1の半導体膜と第2の半導体膜を別々の工程でパターニングしているが、本発明の表示装置はこの作製方法に限定されない。本実施の形態では図8を用いて、第1の半導体膜と第2の半導体膜を同一のマスクを用いてパターニングする例について説明する。

本発明の表示装置の画素構成の一例を示す。

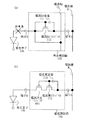

電流源トランジスタ112とカレントトランジスタ1405は一対でカレントミラー回路を構成するので、極性は等しくなくてはならない。また、同一画素内のこれら2つのトランジスタの電流特性は等しいことが望まれる。ここで本実施の形態2では、簡単のため、電流源トランジスタ112とカレントトランジスタ1405の電流特性は等しいものとする。

また、電流入力トランジスタ1403、電流保持トランジスタ1404はnチャネル型トランジスタとするが、単なるスイッチとして動作するため、pチャネル型トランジスタでもかまわない。

カレントトランジスタ1405のゲート電極とドレイン端子は、電流保持トランジスタ1404のソース・ドレイン端子間を介して、接続されている。電流保持トランジスタ1404のゲート電極は、信号線GHに接続されている。カレントトランジスタ1405のドレイン端子と電流線CLは、電流入力トランジスタ1403のソース・ドレイン端子間を介して接続されている。電流入力トランジスタ1403のゲート電極は、信号線GNに接続されている。また、電流源トランジスタ112のドレイン端子は、端子Bに接続されている。

第1の手法について図16を用いて説明する。図16は、図7に示す各画素に配置された電流源回路102の設定動作(画素の設定動作)を示すタイミングチャートである。ここでは、表示装置の電源を入れた後の最初の画素の設定動作について説明する。

量111は、カレントトランジスタ1405が基準電流I0を流す際のゲート電圧を保持する。

本実施の形態では、同一トランジスタ方式の電流源回路の構成例を図18に示す。なお、ここでは実施の形態1と異なる部分について主に説明し、重複する部分は説明を省略する。従って、図18において図1と同じ部分は同じ符号を用いて示す。

スイッチ部の構成としては、実施の形態2において説明したものと同様であり、様々な構成を用いることができる。一例としては、図3に示したものと同様の構成とし説明は省略する。

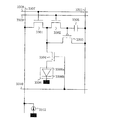

また図19において、駆動トランジスタ302は、単なるスイッチとして機能するので、nチャネル型でもpチャネル型でもどちらでも良い。ただし、駆動トランジスタ302は、そのソース端子の電位が固定された状態で動作するのが好ましい。そのため、図19に示すような発光素子106の画素電極を陽極とし、対向電極を陰極とした構成では、駆動トランジスタ302はpチャネル型のほうが好ましい。なお、第19図において、各画素の配線WCOと電源線Wとは、同じ電位に保たれていてもよいため、共用することができる。また、異なる画素間の配線WCO同士、電源線W同士、配線WCOと電源線Wも共用することができる。

また、電流停止トランジスタ205と消去トランジスタ304を1つにまとめて、どちらか1つを省いてもよい。画素の設定動作のときには、駆動トランジスタ302や発光素子106に電流がもれてしまうと、正しく設定ができない。よって、画素の設定動作のときは、電流停止トランジスタ205を非導通状態とするか、駆動トランジスタ302が非導通状態となるように消去トランジスタ304を導通状態とするかどちらか1つを行えばよい。もちろん両方行っても良い。一方、非表示期間においても同様に、電流停止トランジスタ205を非導通状態とするか、消去トランジスタ304を導通状態とすればよい。以上にことから、電流停止トランジスタ205か消去トランジスタ304のどちらかを省略することができる。

まず画像表示動作については、実施の形態2において、図17を用いて説明したものと同様である。異なるのは、電流停止トランジスタ205についての動作である。もし、電流停止トランジスタ205が存在する場合、点灯期間中には、電流停止トランジスタ205は導通状態になっていなければならない。もし、電流停止トランジスタ205が非導通状態になっていたら、たとえ駆動トランジスタ302が導通状態であっても発光素子に電流が流れなくなってしまうからである。従って点灯期間中は、電流停止トランジスタ205は導通状態にしておく必要がある。非点灯期間中はどちらでもよい。以上の点を除けば実施の形態の2と同様である。従って詳しい説明は省略する。

各画素において画素の設定動作を行う際、電流源容量111に画素対応基準電圧を保持するため、電流線CLを流れる基準電流が、電流源トランジスタ112のドレイン電流をとなる状態を設定する必要があった。従って、もし、画素の設定動作を行っている間に、電流源トランジスタ112を流れる電流の一部が電流源回路102から発光素子106に流れると、電流源トランジスタ112のドレイン電流が電流線CLを流れる基準電流とは異なる値となり、正しく電流源容量111に画素対応基準電圧を保持することができない。これを防ぐため、画素の設定動作を行っている間は、その画素の発光素子に電流を流さないようにする必要がある。

図20(A)において、第1のサブフレーム期間SF1及び第2のサブフレーム期間SF2においては、非表示期間Tusが設けられていないので、画素の設定動作は行われない。一方、第3のサブフレーム期間SF3のリセット期間Tr3が始まると同時に、第1行の画素の設定動作が行われる。なお、k行目の画素の設定動作を行う期間をSETkと表すことにする。そして、SET1が終了するとSET2が始まり、第2行の画素の設定動作が行われる。SET1〜SETyが終了すると、画素の設定動作が全ての画素に関して終了する。こうして、SET1〜SETyの動作がリセット期間Tr3中に行われる。以降のフレーム期間でも、同様の動作を繰り返していけばよい。ただし、毎フレーム期間ごとに画素の設定動作を行う必要はない。画素の電流源容量の保持能力に応じて決定すればよい。

図21(A)において、第1のサブフレーム期間SF1及び第2のサブフレーム期間SF2においては、非表示期間Tusが設けられていないので、画素の設定動作は行われない。一方、第3のサブフレーム期間SF3のリセット期間Tr3が始まると同時に、SET1が始まり、第1行の画素の設定動作が行われる。こうして、SET1の動作が第1行の画素の非表示期間Tus1中にTus1の期間の全てを使って行われる。次に第2のフレーム期間F2が始まり、第2行の画素の設定動作が行われる。以後、同様の動作が行われる。

全ての画素の設定動作が一旦完了した後の、画素の設定動作を繰り返すタイミングは、画素の電流源回路の有する電流源容量の電荷保持能力によって、任意に定めることができる。つまり、数フレーム期間の間、設定動作を全く行わない期間があってもよい。

本実施の形態ではマルチゲート方式の電流源回路について説明する。なお、ここでは実施の形態2や実施の形態3と異なる部分について主に説明し共通する部分の説明は省略する。

なお、図22(A)において、電流保持トランジスタ804の配置を変え、図22(B)に示すような回路構成としてもよい。図22(B)では、電流保持トランジスタ804は、電流源トランジスタ112のゲート電極とドレイン端子の間に接続されている。

図22(D)に示す期間TD2において、保持された電荷によって電流源トランジスタ112のゲート・ソース間電圧が閾値電圧以上となる。すると、電流源トランジスタ112にドレイン電流が流れる。

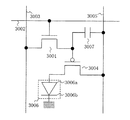

マルチゲート方式1において、電流源回路の部分は画素の設定動作時には、図23(a)のようになり、発光時には図23(b)のようになっていればよい。つまり、そのように、配線やスイッチが接続されていればよい。

ここでは、ヘッドを複数有する液滴吐出装置を示したが、この形態に限られない。一つのヘッドを有しており、そのヘッドをX−Y軸方向に走査して吐出してもよい。この場合、さらに装置の小型・軽量化が可能となる。

また、複数のヘッドにそれぞれ異なる材料を充填することによって、複数の材料を同時に吐出することができる。さらにヘッドによってそれぞれ異なったノズルの径を設定しておけば、用途によって、様々な線幅の配線等を容易に形成することができる。

リセット期間において、各画素行を順に選択し非表示期間が始まる。ここで、走査線を順に選択する周波数と同じ周波数で、各画素行の設定動作を行うことができる。例えば、図3に示した構成のスイッチ部を用いる場合に注目する。走査線Gや消去用信号線RGを順に選択する周波数と同じ周波数で、各画素行を選択し画素の設定動作を行うことが出来る。ただし、1行分の選択期間の長さでは、画素の設定動作を十分に行うことが難しい場合がある。そのときは、複数行分の選択期間を用いて、ゆっくりと画素の設定動作を行ってもよい。ゆっくりと画素の設定動作を行うとは、電流減回路が有する電流容量に、所定の電荷を蓄積する動作を長い時間をかけて行うことを示す。

まず、第1のフレーム期間にF1の期間Aにおいて、GN1、GN11、GN21、・・・ととびとびに選択される。こうして、1行目、11行目、21行目、・・・のGその設定動作が行われる(期間1)。次いで、第1のフレーム期間F1の期間Bにおいて、GN2、GN12、GN22、・・・が選択される。こうして、2行目、12行目、22行目、・・・のがその設定動作が行われる(期間2)。上記動作を5フレーム期間繰り返すことによって、全ての画素の設定動作が一通り行われる。

表示システムの例を図29に示す。表示システムは、表示装置の他に、A/D変換回路、メモリ選択スイッチA、メモリ選択スイッチB、フレームメモリ1、フレームメモリ2、コントローラ、クロック信号発生回路、電源発生回路を有する。

本実施例は、他の実施の形態や実施例と自由に組み合わせて実施することが可能である。

Claims (2)

- 基板上に、第1のTFTのゲート電極、第2のTFTのゲート電極、及び第3のTFTのゲート電極を液滴吐出法または印刷法により形成し、

前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極を覆うゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の半導体膜を形成し、

前記第1の半導体膜を介して、前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極上に、それぞれ保護膜を形成し、

液滴吐出法または印刷法によりレジストを形成し、

前記レジストを用いて前記第1の半導体膜をエッチングして、前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜を形成し、

前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜上に第2の半導体膜を形成し、

前記第2の半導体膜上に、前記第1のTFTのソース電極及びドレイン電極、前記第2のTFTのソース電極及びドレイン電極の一方、前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方、及び前記第3のTFTのソース電極及びドレイン電極の一方を液滴吐出法または印刷法により形成し、

前記第1乃至第3のTFTのソース電極及びドレイン電極をマスクとして前記第2の半導体膜をエッチングして、

前記第1のTFTのソース電極及びドレイン電極の一方の下に第3の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の下に第4の半導体膜を形成し、

前記第2のTFTのソース電極及びドレイン電極の一方の下に第5の半導体膜を形成し、

前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方の下に第6の半導体膜を形成し、

前記第3のTFTのソース電極及びドレイン電極の一方の下に第7の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の上に、液滴吐出法により複数回導電材料を滴下してピラーを形成し、

前記第1のTFTを覆う絶縁膜を塗布法により形成し、

前記絶縁膜表面をエッチングして前記ピラーを露出させ、

前記絶縁膜上に、前記ピラーと電気的に接続する第1の電極を形成し、

前記第1の電極の端部を覆って隔壁を形成し、

前記第1の電極及び前記隔壁上に電界発光層を形成し、

前記電界発光層上に第2の電極を形成することを特徴とする表示装置の作製方法。 - 基板上に、第1のTFTのゲート電極、第2のTFTのゲート電極、及び第3のTFTのゲート電極を液滴吐出法または印刷法により形成し、

前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極を覆うゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の半導体膜を形成し、

前記第1の半導体膜を介して、前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極上に、それぞれ保護膜を形成し、

液滴吐出法または印刷法によりレジストを形成し、

前記レジストを用いて前記第1の半導体膜をエッチングして、前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜を形成し、

前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜上に第2の半導体膜を形成し、

前記第2の半導体膜上に、前記第1のTFTのソース電極及びドレイン電極、前記第2のTFTのソース電極及びドレイン電極の一方、前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方、及び前記第3のTFTのソース電極及びドレイン電極の一方を液滴吐出法または印刷法により形成し、

前記第1乃至第3のTFTのソース電極及びドレイン電極をマスクとして前記第2の半導体膜をエッチングして、

前記第1のTFTのソース電極及びドレイン電極の一方の下に第3の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の下に第4の半導体膜を形成し、

前記第2のTFTのソース電極及びドレイン電極の一方の下に第5の半導体膜を形成し、

前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方の下に第6の半導体膜を形成し、

前記第3のTFTのソース電極及びドレイン電極の一方の下に第7の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の上に、液滴吐出法により複数回導電材料を滴下してピラーを形成し、

前記第1乃至第3のTFTを覆う絶縁膜を塗布法により形成し、

前記絶縁膜表面をエッチングして前記ピラーを露出させ、

前記絶縁膜上に、前記ピラーと電気的に接続する第1の電極を形成し、

前記第1の電極の端部を覆って隔壁を形成し、

前記第1の電極及び前記隔壁上に電界発光層を形成し、

前記電界発光層上に第2の電極を形成することを特徴とする表示装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004037405A JP4583776B2 (ja) | 2004-02-13 | 2004-02-13 | 表示装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004037405A JP4583776B2 (ja) | 2004-02-13 | 2004-02-13 | 表示装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005227625A JP2005227625A (ja) | 2005-08-25 |

| JP2005227625A5 JP2005227625A5 (ja) | 2007-03-15 |

| JP4583776B2 true JP4583776B2 (ja) | 2010-11-17 |

Family

ID=35002375

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004037405A Expired - Fee Related JP4583776B2 (ja) | 2004-02-13 | 2004-02-13 | 表示装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4583776B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008134625A (ja) * | 2006-10-26 | 2008-06-12 | Semiconductor Energy Lab Co Ltd | 半導体装置、表示装置及び電子機器 |

| TWI442368B (zh) | 2006-10-26 | 2014-06-21 | Semiconductor Energy Lab | 電子裝置,顯示裝置,和半導體裝置,以及其驅動方法 |

| US7812348B2 (en) * | 2008-02-29 | 2010-10-12 | Semiconductor Energy Laboratory Co., Ltd. | Thin-film transistor and display device |

| JP2010225781A (ja) * | 2009-03-23 | 2010-10-07 | Casio Computer Co Ltd | 薄膜トランジスタ及び薄膜トランジスタの製造方法 |

| JP6050054B2 (ja) | 2011-09-09 | 2016-12-21 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5909729B2 (ja) * | 2011-10-17 | 2016-04-27 | 株式会社Joled | 表示装置及びその制御方法 |

| JP2013104908A (ja) * | 2011-11-10 | 2013-05-30 | Panasonic Corp | 表示装置及びその制御方法 |

| US10043794B2 (en) | 2012-03-22 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06216258A (ja) * | 1993-01-15 | 1994-08-05 | Toshiba Corp | 半導体装置の製造方法 |

| JPH11284198A (ja) * | 1998-03-27 | 1999-10-15 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2001024340A (ja) * | 1999-07-07 | 2001-01-26 | Toshiba Corp | プリント配線基板の製造方法及びプリント配線基板 |

| JP2002189427A (ja) * | 2000-12-21 | 2002-07-05 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2002203675A (ja) * | 2000-10-31 | 2002-07-19 | Canon Inc | 有機発光素子の製造方法及び有機発光表示体の製造方法、有機発光素子及び有機発光表示体 |

| JP2002251166A (ja) * | 2001-02-26 | 2002-09-06 | Semiconductor Energy Lab Co Ltd | 発光装置及び電子機器 |

| JP2002318555A (ja) * | 2000-12-21 | 2002-10-31 | Semiconductor Energy Lab Co Ltd | 発光装置及びその作製方法 |

| JP2003086370A (ja) * | 2001-09-10 | 2003-03-20 | Brother Ind Ltd | 表示用組成物形成用塗布液、有機el素子、表示装置、及び表示装置の製造方法 |

| WO2003027997A1 (fr) * | 2001-09-21 | 2003-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Ecran et procede de fonctionnement associe |

| WO2003083960A1 (en) * | 2002-03-27 | 2003-10-09 | Cambridge Display Technology Limited | Method of preparation of organic optoelectronic and electronic devices and devices thereby obtained |

| JP2004000927A (ja) * | 2002-04-16 | 2004-01-08 | Seiko Epson Corp | パターンの形成方法、パターン形成装置、導電膜配線、デバイスの製造方法、電気光学装置、並びに電子機器 |

| JP2004031201A (ja) * | 2002-06-27 | 2004-01-29 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005535120A (ja) * | 2002-08-06 | 2005-11-17 | アベシア・リミテッド | 有機電子デバイス |

-

2004

- 2004-02-13 JP JP2004037405A patent/JP4583776B2/ja not_active Expired - Fee Related

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06216258A (ja) * | 1993-01-15 | 1994-08-05 | Toshiba Corp | 半導体装置の製造方法 |

| JPH11284198A (ja) * | 1998-03-27 | 1999-10-15 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2001024340A (ja) * | 1999-07-07 | 2001-01-26 | Toshiba Corp | プリント配線基板の製造方法及びプリント配線基板 |

| JP2002203675A (ja) * | 2000-10-31 | 2002-07-19 | Canon Inc | 有機発光素子の製造方法及び有機発光表示体の製造方法、有機発光素子及び有機発光表示体 |

| JP2002189427A (ja) * | 2000-12-21 | 2002-07-05 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2002318555A (ja) * | 2000-12-21 | 2002-10-31 | Semiconductor Energy Lab Co Ltd | 発光装置及びその作製方法 |

| JP2002251166A (ja) * | 2001-02-26 | 2002-09-06 | Semiconductor Energy Lab Co Ltd | 発光装置及び電子機器 |

| JP2003086370A (ja) * | 2001-09-10 | 2003-03-20 | Brother Ind Ltd | 表示用組成物形成用塗布液、有機el素子、表示装置、及び表示装置の製造方法 |

| WO2003027997A1 (fr) * | 2001-09-21 | 2003-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Ecran et procede de fonctionnement associe |

| WO2003083960A1 (en) * | 2002-03-27 | 2003-10-09 | Cambridge Display Technology Limited | Method of preparation of organic optoelectronic and electronic devices and devices thereby obtained |

| JP2004000927A (ja) * | 2002-04-16 | 2004-01-08 | Seiko Epson Corp | パターンの形成方法、パターン形成装置、導電膜配線、デバイスの製造方法、電気光学装置、並びに電子機器 |

| JP2004031201A (ja) * | 2002-06-27 | 2004-01-29 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005227625A (ja) | 2005-08-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7295313B2 (ja) | 発光装置 | |

| KR101080351B1 (ko) | 표시 장치 및 그 구동 방법 | |

| JP4728849B2 (ja) | 表示装置及びその駆動方法 | |

| JP5764604B2 (ja) | El表示装置 | |

| JP5078236B2 (ja) | 表示装置及びその駆動方法 | |

| JP5080733B2 (ja) | 表示装置及びその駆動方法 | |

| JP5613360B2 (ja) | 表示装置、表示モジュール及び電子機器 | |

| JP4854177B2 (ja) | 有機電界発光駆動素子とこれを有する有機電界発光表示パネル | |

| US8384701B2 (en) | Organic light emitting display apparatus and method of driving the same | |

| US20060007072A1 (en) | Display device and driving method thereof | |

| JP2006243740A (ja) | 表示装置及びその駆動方法 | |

| JP4583776B2 (ja) | 表示装置の作製方法 | |

| JP4588312B2 (ja) | 発光装置の作製方法 | |

| JP4566575B2 (ja) | 発光装置の作製方法 | |

| JP5825740B2 (ja) | 表示装置 | |

| JP4637472B2 (ja) | 発光装置の作製方法 | |

| KR20100029811A (ko) | 유기 발광 표시장치 및 그 구동방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070130 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070130 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100329 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100601 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100706 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100901 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |