JP4554292B2 - 薄膜トランジスタの作製方法 - Google Patents

薄膜トランジスタの作製方法 Download PDFInfo

- Publication number

- JP4554292B2 JP4554292B2 JP2004211354A JP2004211354A JP4554292B2 JP 4554292 B2 JP4554292 B2 JP 4554292B2 JP 2004211354 A JP2004211354 A JP 2004211354A JP 2004211354 A JP2004211354 A JP 2004211354A JP 4554292 B2 JP4554292 B2 JP 4554292B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- semi

- amorphous semiconductor

- manufacturing

- thin film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 247

- 238000004519 manufacturing process Methods 0.000 title claims description 99

- 239000010409 thin film Substances 0.000 title claims description 72

- 239000010410 layer Substances 0.000 claims description 503

- 239000004065 semiconductor Substances 0.000 claims description 257

- 239000004020 conductor Substances 0.000 claims description 168

- 239000000758 substrate Substances 0.000 claims description 132

- 239000012212 insulator Substances 0.000 claims description 84

- 239000007789 gas Substances 0.000 claims description 83

- 239000012535 impurity Substances 0.000 claims description 65

- 239000000463 material Substances 0.000 claims description 45

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 30

- 229910021332 silicide Inorganic materials 0.000 claims description 30

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 30

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 29

- 239000001301 oxygen Substances 0.000 claims description 27

- 229910052760 oxygen Inorganic materials 0.000 claims description 27

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 24

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 24

- 238000005530 etching Methods 0.000 claims description 22

- 238000005268 plasma chemical vapour deposition Methods 0.000 claims description 19

- 239000013078 crystal Substances 0.000 claims description 18

- 229910052786 argon Inorganic materials 0.000 claims description 15

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 14

- 125000004429 atom Chemical group 0.000 claims description 13

- 239000010949 copper Substances 0.000 claims description 13

- 239000010931 gold Substances 0.000 claims description 13

- 239000001257 hydrogen Substances 0.000 claims description 12

- 229910052739 hydrogen Inorganic materials 0.000 claims description 12

- 229910052709 silver Inorganic materials 0.000 claims description 12

- 239000004332 silver Substances 0.000 claims description 12

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 11

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 claims description 11

- 229910052802 copper Inorganic materials 0.000 claims description 11

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 10

- 239000011241 protective layer Substances 0.000 claims description 9

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 8

- 229910052737 gold Inorganic materials 0.000 claims description 8

- 239000001307 helium Substances 0.000 claims description 8

- 229910052734 helium Inorganic materials 0.000 claims description 8

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims description 8

- 229910052743 krypton Inorganic materials 0.000 claims description 8

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 claims description 8

- 229910052754 neon Inorganic materials 0.000 claims description 8

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 claims description 8

- 238000007865 diluting Methods 0.000 claims description 7

- 229910052732 germanium Inorganic materials 0.000 claims description 5

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 5

- 238000010030 laminating Methods 0.000 claims description 5

- 229910003902 SiCl 4 Inorganic materials 0.000 claims description 3

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 claims description 3

- 125000004435 hydrogen atom Chemical class [H]* 0.000 claims 1

- 239000010408 film Substances 0.000 description 109

- 239000000203 mixture Substances 0.000 description 66

- 239000004973 liquid crystal related substance Substances 0.000 description 36

- 230000008569 process Effects 0.000 description 29

- 230000015572 biosynthetic process Effects 0.000 description 28

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 21

- 230000002829 reductive effect Effects 0.000 description 21

- 239000002904 solvent Substances 0.000 description 21

- 238000007599 discharging Methods 0.000 description 19

- 229920005989 resin Polymers 0.000 description 18

- 239000011347 resin Substances 0.000 description 18

- 239000000565 sealant Substances 0.000 description 15

- 238000010438 heat treatment Methods 0.000 description 13

- 230000001681 protective effect Effects 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- 239000012298 atmosphere Substances 0.000 description 11

- 238000000354 decomposition reaction Methods 0.000 description 11

- 230000004888 barrier function Effects 0.000 description 10

- 230000018109 developmental process Effects 0.000 description 10

- 229910052757 nitrogen Inorganic materials 0.000 description 10

- 239000002245 particle Substances 0.000 description 10

- 239000000243 solution Substances 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 10

- 239000011521 glass Substances 0.000 description 9

- 239000011368 organic material Substances 0.000 description 9

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 8

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 8

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 7

- -1 aluminum (Al) Chemical class 0.000 description 7

- 238000001035 drying Methods 0.000 description 7

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 7

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 239000011248 coating agent Substances 0.000 description 6

- 238000002425 crystallisation Methods 0.000 description 6

- 230000008025 crystallization Effects 0.000 description 6

- 230000005669 field effect Effects 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 5

- 238000006243 chemical reaction Methods 0.000 description 5

- 239000000945 filler Substances 0.000 description 5

- 238000007667 floating Methods 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- 229910017855 NH 4 F Inorganic materials 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 230000006378 damage Effects 0.000 description 4

- 235000019441 ethanol Nutrition 0.000 description 4

- 238000010304 firing Methods 0.000 description 4

- 229910052736 halogen Inorganic materials 0.000 description 4

- 150000002367 halogens Chemical class 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 239000011147 inorganic material Substances 0.000 description 4

- 239000010955 niobium Substances 0.000 description 4

- KDLHZDBZIXYQEI-UHFFFAOYSA-N palladium Substances [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- 239000003504 photosensitizing agent Substances 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000010453 quartz Substances 0.000 description 4

- 239000010948 rhodium Substances 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 239000003566 sealing material Substances 0.000 description 4

- 229910000077 silane Inorganic materials 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 239000002253 acid Substances 0.000 description 3

- 229910052788 barium Inorganic materials 0.000 description 3

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- 239000003795 chemical substances by application Substances 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 230000003472 neutralizing effect Effects 0.000 description 3

- 229910052756 noble gas Inorganic materials 0.000 description 3

- 229920003986 novolac Polymers 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 238000009832 plasma treatment Methods 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- 229920000915 polyvinyl chloride Polymers 0.000 description 3

- 239000004800 polyvinyl chloride Substances 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 2

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910008486 TiSix Inorganic materials 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 150000001298 alcohols Chemical class 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 229910052793 cadmium Inorganic materials 0.000 description 2

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000000356 contaminant Substances 0.000 description 2

- 239000002178 crystalline material Substances 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000000280 densification Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- OLLFKUHHDPMQFR-UHFFFAOYSA-N dihydroxy(diphenyl)silane Chemical compound C=1C=CC=CC=1[Si](O)(O)C1=CC=CC=C1 OLLFKUHHDPMQFR-UHFFFAOYSA-N 0.000 description 2

- 238000010790 dilution Methods 0.000 description 2

- 239000012895 dilution Substances 0.000 description 2

- 229910001882 dioxygen Inorganic materials 0.000 description 2

- 239000002270 dispersing agent Substances 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 150000002148 esters Chemical class 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 230000004927 fusion Effects 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000002105 nanoparticle Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 239000003960 organic solvent Substances 0.000 description 2

- 230000010355 oscillation Effects 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920000052 poly(p-xylylene) Polymers 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 238000009751 slip forming Methods 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 239000004094 surface-active agent Substances 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 238000005406 washing Methods 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 239000004640 Melamine resin Substances 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 238000003848 UV Light-Curing Methods 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 1

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 description 1

- 238000009835 boiling Methods 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 125000000484 butyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical compound FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 229920001519 homopolymer Polymers 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 238000004020 luminiscence type Methods 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 1

- 229910021344 molybdenum silicide Inorganic materials 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000010943 off-gassing Methods 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 239000011135 tin Substances 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Description

T.Shimoda、Ink−jet Technology for Fabrication Processes of Flat Panel Displays、SID 03 DIGEST、p1178−1181

なお本発明では、SASは、少なくともチャネル形成領域に用いていれば良い。またチャネル形成領域は、その膜厚方向において全てセミアモルファス半導体である必要はなく、少なくとも一部にセミアモルファス半導体を含んでいれば良い。

本発明は、前記第1の半導体素子のチャネル部としてセミアモルファス半導体層を形成し、前記第1の半導体素子を構成する導電体層は、導電性材料を含む組成物を選択的に吐出して形成することを特徴とする。この表示装置の作製方法については、形態3に詳述する。

また、本発明は、液滴吐出法を用いることにより、レジストによるマスクを全く用いない、又は数枚のみを用いるだけで、薄膜トランジスタを形成することが可能となる。従って、レジストの塗布、レジストの焼成、露光、現像、現像後の焼成、レジスト剥離等の工程を省略することができるため、工程の簡略化によるコストの大幅な低減や信頼性の向上が実現される。

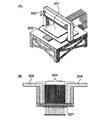

(実施の形態1)

ガラス、石英、プラスチック材料、ステンレスやアルミニウムなどの金属材料の上に絶縁膜を形成した基板10上にゲート電極及びゲート配線(走査線)を形成するための導電体層51、52を形成する(図2(A))。この導電体層51、52は、液滴吐出法を用いて、導電性材料を含む組成物を基板10上に描画することで形成される。より詳しくは、導電体材料を含む組成物を選択的に吐出することで形成される。なお、図示しないが、この際、ゲート電極と接続する配線も同時に形成される。

溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等に相当する。

本発明は、このような半導体をセミアモルファス半導体(以下、SASと表記)と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なSASが得られる。

また、SASは、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いN型の電気伝導性を示す。これは、SAS中に含まれる不純物によるもので、代表的には酸素がN型の伝導性を付与するものとして考えられている。SASに含まれる酸素は、成膜時の高周波電力密度に応じても変化する。

従って、弱N型の電気伝導性を持つ第1の半導体層55に対して、同じ導電型で一導電型を有する第3の半導体層57を形成する場合には必ずしも必要ない。しきい値制御をする目的において、P型を付与する不純物元素を添加する場合には、第2の半導体層56は段階的に不純物濃度を変化させる効果を持ち、接合形成を良好にする上で好ましい形態となる。すなわち、形成されるトランジスタにおいては、チャネル形成領域とソースまたはドレイン領域の間に形成される低濃度不純物領域(LDD領域)としての機能を持たせることが可能となる。

このようにして形成されるトランジスタは、チャネル形成領域がソースとドレインの間、およびLDD領域の間に挟まれて形成されず、電界集中や電流集中を緩和できる構造を有している。

続いて、導電体層66〜69をマスクとして、第2の半導体層61、64、第3の半導体層62、65及び導電体層58、59をパターン加工する。この際、第1の半導体層60、63も少しエッチングされ、第1の半導体層70、74、第2の半導体層71、75、第3の半導体層72、76、導電体層73、77、88、89が形成される。この導電体層73及び77と、導電体層88及び89は、一方がソース配線であり、他方はドレイン配線に相当する。

以上の工程を経て、チャネルエッチ型のトランジスタが形成される。このトランジスタは、SASでチャネル形成領域を構成することにより2〜10cm2/V・secの電界効果移動度を得ることができる。従って、このTFTを画素のスイッチング用素子として利用することができる。さらに画素のスイッチング素子だけではなく、走査線(ゲート線)側の駆動回路を形成する素子として利用することができる。従って、システムオンパネル化を実現した表示装置を作製することができる。

また、特筆すべき点として、本工程では、レジストによるマスクを用いていない点が挙げられる。これは、液滴吐出法を用いているために可能となっており、より詳しくは、第1乃至第3の半導体層55〜57は、導電体層58、59、又は導電体層66〜69を用いてパターニングを行っている。そのために、レジストの塗布、レジストの焼成、露光、現像、現像後の焼成、レジスト剥離等の工程を省略することができる。従って、工程の簡略化によるコストの大幅な低減や信頼性の向上が実現される。

そうすると、反応温度が60℃以上85℃未満と低温で作製することができる。上記条件で作製した薄膜は、0.3atomic%以上の希ガスを有し、HFが4.7%、NH4Fが36.3%含まれたバッファードフッ酸における室温でのエッチングレートが30.0nm/min以下の特性、又は0.3atomic%以上の希ガスと25atomic%未満の水素を有し、HFが4.7%、NH4Fが36.3%含まれたバッファードフッ酸における室温でのエッチングレートが30.0nm/min以下の特性、又は0.3atomic%以上の希ガスと4.0atomic%以上の酸素を有し、HFが4.7%、NH4Fが36.3%含まれたバッファードフッ酸における室温でのエッチングレートが30.0nm/min以下の特性、又は0.3atomic%以上の希ガスと4.0atomic%以上の酸素と25atomic%未満の水素を有し、HFが4.7%、NH4Fが36.3%含まれたバッファードフッ酸における室温でのエッチングレートが30.0nm/min以下の特性を有する。このように、80度以下という低温で作製したにも関わらず、上記のようなエッチングレートを有する窒化珪素膜は、バリア性が高く、緻密で質のよい膜であることが分かる。

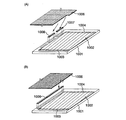

続いて、液晶を封止するためのシール材87を形成する。また、透明導電膜からなる対向電極83と、ラビング処理が施された配向膜82とが形成された第2の基板(対向基板)84を準備する。そして、シール材87で囲まれた領域に液晶81を滴下し、別途用意しておいた第2の基板84を、対向電極83と画素電極として機能する導電体層80とが向かい合うように、シール材87を用いて貼り合わせる。

なおシール材87にはフィラーが混入されていても良く、また、第2の基板84には、カラーフィルタや、ディスクリネーションを防ぐための遮蔽膜(ブラックマトリクス)などが形成されていても良い。また、偏光板85、偏光板86を各基板10、84に貼り合わせておく。

(実施の形態2)

本発明は、第1の半導体層15中の酸素濃度は5×1019atoms/cm3以下、好ましくは1×1019atoms/cm3以下とすることが望ましい。また、チャネル形成領域を具備する第1の半導体層15に対しては、P型を付与する不純物元素を、この成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。P型を付与する不純物元素としては、代表的には硼素であり、B2H6、BF3などの不純物気体を1ppm〜1000ppmの割合で珪化物気体に混入させると良い。そしてボロンの濃度を1×1014〜6×1016atoms/cm3とすると良い。

また、マスクパターン21、22を形成せずに、導電体層11、12を用いて裏面露光することで、チャネル保護膜を形成してもよい。

また、特筆すべき点として、本工程では、レジストによるマスクを液滴吐出法により形成する点が挙げられる。より詳しくは、第1の半導体層15は、液滴吐出法により形成されたマスクパターン16、17を用いてパターニングを行っており、絶縁体層20はマスクパターン21、22を用いてパターニングを行っており、第2及び第3の半導体層25、26は導電体層27〜30を用いてパターニングを行っている。そのために、レジストの塗布、レジストの焼成、露光、現像、現像後の焼成等の工程を省略することができる。従って、工程の簡略化によるコストの大幅な低減や信頼性の向上が実現される。

次に、全面に絶縁体層41を形成し、続いて、導電体層40が露出するように、所定の箇所に開口部を設ける(図1(B))。

次に、液滴吐出法又は蒸着法等により、電界発光層42を形成する。電界発光層42は、無機材料や有機材料等の広汎に渡る材料により形成され、単層で形成されていても、複数の層が積層され形成されていてもどちらでもよい。次に、電界発光層42上に、対向電極となる導電体層43を液滴吐出法により形成する。この導電体層40、電界発光層42及び導電体層43の積層体が発光素子44に相当する。

(実施の形態3)

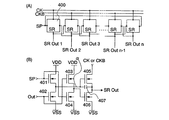

その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにすることが好適である。例えば、走査線側のドライバICを構成するトランジスタには30V程度の耐圧が要求されるものの、駆動周波数は100kHz以下であり、比較的高速動作は要求されない。従って、走査線側のドライバを構成するトランジスタのチャネル長(L)は十分大きく設定することが好適である。一方、信号線側のドライバICのトランジスタには、12V程度の耐圧があれば十分であるが、駆動周波数は3Vにて65MHz程度であり、高速動作が要求される。そのため、ドライバを構成するトランジスタのチャネル長などはミクロンルールで設定することが好適である。

(実施の形態4)

溶媒は、酢酸ブチル等のエステル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

ここで、ディスペンサ方式を採用した場合、つまり、液晶滴下プロセスについて、図26を用いて説明する。基板8001上に、TFT等の素子が完成したら、まず、シール材として機能する閉ループ8002を形成する(図26(A)参照)。次に、閉ループ8002の中にディスペンサにより液晶8003を滴下する(図26(B)参照)。続いて、真空中で基板8001と基板8004とを貼り合わせる(図26(C)参照)。その後、UV硬化を行うと、液晶8005が充填された状態となり(図26(D)参照)、続いてパネル毎に分断する(図26(E)参照)。

次に、開口部641を充填するように、導電性材料を含む組成物を選択的に吐出して、画素電極として機能する導電体層643を形成する。続いて、配向膜として機能する絶縁体層644を形成する(図31(B)参照)。その後、図30(B)(C)に示す工程と同様に、シール材を形成し、対向基板を貼り合わせて、液晶を注入すれば、表示機能を有する表示装置が完成する(図27(B)参照)。上記工程を経て、図27(A)とは異なる構成のチャネル保護型のスイッチング用TFT632と容量素子633を含む表示装置が完成する。

本工程では、レジストによるマスクを用いていない点を特徴とし、本特徴により、レジストの塗布、レジストの焼成、露光、現像、現像後の焼成、レジスト剥離等の工程を省略することができる。従って、工程の簡略化による作製時間の短縮や作製費用の低減を実現する。

(実施の形態5)

本工程では、レジストによるマスクを用いていない点を特徴とし、これは、液滴吐出法を用いているために可能となっている。従って、レジストの塗布、レジストの焼成、露光、現像、現像後の焼成、レジスト剥離等の工程を省略することができる。従って、工程の簡略化による作製時間の短縮や作製費用の低減を実現する。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

(実施の形態6)

また図12では、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施例はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

また、液晶素子4011aが有する画素電極4030は、トランジスタ4010と配線4040、配線4041を介して電気的に接続されている。そして液晶素子4011aの対向電極4031は第2の基板4006上に形成される。画素電極4030、対向電極4031及び液晶4007aが重なっている部分が、液晶素子4011aに相当する。

4035は球状のスペーサであり、画素電極4030と対向電極4031との間の距離(セルギャップ)を制御するために設けられている。なお絶縁膜をパターニングすることで得られるスペーサを用いていても良い。

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、図12(B)に示す断面図では図示されていないが、引き回し配線4014及び4015を介して、接続端子4016から供給されている。

図25(C)に示す保護回路は、P型TFT7220、P型TFT7230を、TFT7350、TFT7360、TFT7370、TFT7380で代用した等価回路図である。

また、上記とは別の構成の保護回路として、図25(D)に示す保護回路は、抵抗素子7280、抵抗素子7290と、N型TFT7300を有する。

図25(E)に示す保護回路は、抵抗素子7280、7290、P型TFT7310及びN型TFT7320を有する。図25(D)(E)の両構成とも、端子7330には配線などが接続され、この配線などの電位が急激に変化した場合に、N型TFT7300、又はP型TFT7310及びN型TFT7320がオンすることで、電流を端子7330から7340の方向に流す。そうすると、端子7330に接続された電位の急激な変動を緩和し、素子の損傷又は破壊を防止することができる。なお、上記保護回路を構成する素子は、耐圧に優れた非晶質半導体層により構成することが好ましい。本実施例は、上記の実施の形態と自由に組み合わせることが可能である。

Claims (27)

- 絶縁表面を有する基板上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極上に、ゲート絶縁層、セミアモルファス半導体層、一導電型の不純物を含有するセミアモルファス半導体層を積層形成し、

前記ゲート電極と重なる位置に、液滴吐出法で第1の導電体層を形成し、

前記第1の導電体層をマスクとして、前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層とをエッチングし、

前記第1の導電体層上に、液滴吐出法でソース配線又はドレイン配線として機能する第2の導電体層を形成し、

前記第2の導電体層をマスクとして、前記第1の導電体層と、前記一導電型の不純物を含有するセミアモルファス半導体層とをエッチングし、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、プラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 絶縁表面を有する基板上に、液滴吐出法でゲート電極を形成し、

前記ゲート電極上に、ゲート絶縁層、第1のセミアモルファス半導体層を積層形成し、

前記ゲート電極と重なる位置に、液滴吐出法で第1のマスクを形成し、

前記第1のマスクを用いて、前記第1のセミアモルファス半導体層をエッチングして第2のセミアモルファス半導体層を形成し、

前記第2のセミアモルファス半導体層上に絶縁体層を形成し、

前記絶縁体層上に、液滴吐出法で第2のマスクを形成し、

前記第2のマスクを用いて、前記絶縁体層をエッチングしてチャネル保護層を形成し、

前記第2のセミアモルファス半導体層上に、一導電型の不純物を含有するセミアモルファス半導体層を形成し、

前記一導電型の不純物を含有するセミアモルファス半導体層上に、液滴吐出法でソース配線又はドレイン配線として機能する導電体層を形成し、

前記導電体層をマスクとして、前記一導電型の不純物を含有するセミアモルファス半導体層をエッチングし、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、プラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1において、

前記第1の導電体層と前記第2の導電層は、それぞれ、銀、金、又は銅を含む材料を用いて液滴吐出法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1又は請求項3において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、酸素濃度が5×1019atoms/cm3以下であることを特徴とする薄膜トランジスタの作製方法。 - 請求項1又は請求項3において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、酸素濃度が1×10 19 atoms/cm 3 以下であることを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項5のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、結晶粒が分散した非晶質半導体層であることを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項5のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、0.5〜20nmの結晶粒が分散した非晶質半導体層であることを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項7のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項7のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体を希ガス元素で希釈した気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項7のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体に炭化物気体を混入させた気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項3乃至請求項7のいずれか一項において、

前記セミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体にゲルマニウム化気体を混入させた気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2において、

前記導電体層は、銀、金、又は銅を含む材料を用いて液滴吐出法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2又は請求項12において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、酸素濃度が5×1019atoms/cm3以下であることを特徴とする薄膜トランジスタの作製方法。 - 請求項2又は請求項12において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、酸素濃度が1×10 19 atoms/cm 3 以下であることを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項14のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、結晶粒が分散した非晶質半導体層であることを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項14のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層は、0.5〜20nmの結晶粒が分散した非晶質半導体層であることを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項16のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項16のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体を希ガス元素で希釈した気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項16のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体に炭化物気体を混入させた気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2、請求項12乃至請求項16のいずれか一項において、

前記第1のセミアモルファス半導体層と、前記一導電型の不純物を含有するセミアモルファス半導体層はそれぞれ、珪化物気体にゲルマニウム化気体を混入させた気体を用いてプラズマCVD法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項8乃至請求項11、請求項17乃至請求項20のいずれか一項において、

前記珪化物気体は、SiH 4 、Si 2 H 6 、SiH 2 Cl 2 、SiHCl 3 、SiCl 4 、又はSiF 4 であることを特徴とする薄膜トランジスタの作製方法。 - 請求項9又は請求項18において、

前記希ガス元素は、水素、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた1種または複数種であることを特徴とする薄膜トランジスタの作製方法。 - 請求項10又は請求項19において、

前記ゲルマニウム化気体は、GeH 4 又はGeF 4 であることを特徴とする薄膜トランジスタの作製方法。 - 請求項11又は請求項20において、

前記炭化物気体は、CH 4 又はC 2 H 6 であることを特徴とする薄膜トランジスタの作製方法。 - 請求項1乃至請求項24のいずれか一項において、

前記ゲート電極は、銀、金、又は銅を含む材料を用いて液滴吐出法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1乃至請求項25のいずれか一項において、

前記ゲート絶縁層は、窒化珪素層と、酸化珪素層とを順次積層して形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1乃至請求項25のいずれか一項において、

前記ゲート絶縁層は、第1の窒化珪素層と、酸化珪素層と、第2の窒化珪素層とを順次積層して形成することを特徴とする薄膜トランジスタの作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004211354A JP4554292B2 (ja) | 2003-07-18 | 2004-07-20 | 薄膜トランジスタの作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003277144 | 2003-07-18 | ||

| JP2003361289 | 2003-10-21 | ||

| JP2004211354A JP4554292B2 (ja) | 2003-07-18 | 2004-07-20 | 薄膜トランジスタの作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005150685A JP2005150685A (ja) | 2005-06-09 |

| JP2005150685A5 JP2005150685A5 (ja) | 2007-06-14 |

| JP4554292B2 true JP4554292B2 (ja) | 2010-09-29 |

Family

ID=34704840

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004211354A Expired - Fee Related JP4554292B2 (ja) | 2003-07-18 | 2004-07-20 | 薄膜トランジスタの作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4554292B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8900970B2 (en) | 2006-04-28 | 2014-12-02 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device using a flexible substrate |

| JP5117001B2 (ja) * | 2006-07-07 | 2013-01-09 | 株式会社ジャパンディスプレイイースト | 有機el表示装置 |

| US8330887B2 (en) * | 2007-07-27 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device |

| US8101444B2 (en) * | 2007-08-17 | 2012-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2009071289A (ja) * | 2007-08-17 | 2009-04-02 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| KR101484297B1 (ko) * | 2007-08-31 | 2015-01-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 표시장치의 제작방법 |

| US20090141004A1 (en) | 2007-12-03 | 2009-06-04 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| JP5498711B2 (ja) * | 2008-03-01 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| JP5602389B2 (ja) * | 2008-05-16 | 2014-10-08 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| JP5518366B2 (ja) * | 2008-05-16 | 2014-06-11 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| CN102197490B (zh) | 2008-10-24 | 2013-11-06 | 株式会社半导体能源研究所 | 半导体器件和用于制造该半导体器件的方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6151878A (ja) * | 1984-08-21 | 1986-03-14 | Seiko Instr & Electronics Ltd | 表示用パネルの製造方法 |

| JPH0887033A (ja) * | 1994-09-16 | 1996-04-02 | Toshiba Corp | アクティブマトリクス表示装置の製造方法 |

| JPH09321315A (ja) * | 1995-12-11 | 1997-12-12 | Hyundai Electron Ind Co Ltd | 露光装置及び薄膜トランジスタの形成方法 |

| JPH11330472A (ja) * | 1998-05-01 | 1999-11-30 | Internatl Business Mach Corp <Ibm> | バックチャネル効果を防止する薄膜トランジスタおよびその製造方法 |

| JP2000357797A (ja) * | 1999-06-15 | 2000-12-26 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JP2003318192A (ja) * | 2002-04-22 | 2003-11-07 | Seiko Epson Corp | デバイスの製造方法、デバイス、電気光学装置及び電子機器 |

-

2004

- 2004-07-20 JP JP2004211354A patent/JP4554292B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6151878A (ja) * | 1984-08-21 | 1986-03-14 | Seiko Instr & Electronics Ltd | 表示用パネルの製造方法 |

| JPH0887033A (ja) * | 1994-09-16 | 1996-04-02 | Toshiba Corp | アクティブマトリクス表示装置の製造方法 |

| JPH09321315A (ja) * | 1995-12-11 | 1997-12-12 | Hyundai Electron Ind Co Ltd | 露光装置及び薄膜トランジスタの形成方法 |

| JPH11330472A (ja) * | 1998-05-01 | 1999-11-30 | Internatl Business Mach Corp <Ibm> | バックチャネル効果を防止する薄膜トランジスタおよびその製造方法 |

| JP2000357797A (ja) * | 1999-06-15 | 2000-12-26 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JP2003318192A (ja) * | 2002-04-22 | 2003-11-07 | Seiko Epson Corp | デバイスの製造方法、デバイス、電気光学装置及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005150685A (ja) | 2005-06-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101030698B1 (ko) | 반도체 장치 제조방법 | |

| US7510905B2 (en) | Forming method of contact hole, and manufacturing method of semiconductor device, liquid crystal display device and EL display device | |

| US9287343B2 (en) | Display device and method for manufacturing the same | |

| US9245922B2 (en) | Light-emitting device and method for manufacturing the same | |

| US7955907B2 (en) | Semiconductor device, television set, and method for manufacturing the same | |

| US9237657B2 (en) | Wiring substrate, semiconductor device, and method for manufacturing thereof | |

| JP4939756B2 (ja) | 半導体装置の作製方法 | |

| US7439086B2 (en) | Method for manufacturing liquid crystal display device | |

| JP4619060B2 (ja) | 半導体装置の作製方法 | |

| JP4554292B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4498715B2 (ja) | 半導体装置の作製方法 | |

| US7446054B2 (en) | Method for manufacturing semiconductor device | |

| JP4877866B2 (ja) | 半導体装置の作製方法 | |

| JP4737971B2 (ja) | 液晶表示装置および液晶表示装置の作製方法 | |

| JP4741218B2 (ja) | 液晶表示装置及びその作製方法、並びに液晶テレビ受像機 | |

| JP4877868B2 (ja) | 表示装置の作製方法 | |

| JP4718818B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4986391B2 (ja) | 表示装置の作製方法 | |

| JP4817627B2 (ja) | 表示装置の作製方法 | |

| JP4683898B2 (ja) | 半導体装置の作製方法 | |

| JP2005165305A (ja) | 液晶表示装置及びその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070419 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070419 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100709 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100713 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100714 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130723 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130723 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130723 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |