JP4718818B2 - 薄膜トランジスタの作製方法 - Google Patents

薄膜トランジスタの作製方法 Download PDFInfo

- Publication number

- JP4718818B2 JP4718818B2 JP2004297094A JP2004297094A JP4718818B2 JP 4718818 B2 JP4718818 B2 JP 4718818B2 JP 2004297094 A JP2004297094 A JP 2004297094A JP 2004297094 A JP2004297094 A JP 2004297094A JP 4718818 B2 JP4718818 B2 JP 4718818B2

- Authority

- JP

- Japan

- Prior art keywords

- mask

- conductive layer

- layer

- semiconductor layer

- droplet discharge

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

Description

また、本発明は、液滴吐出法を用いた半導体装置の作製方法に関する。半導体装置とは、基板上に薄膜トランジスタが形成されたTFT基板、基板上に薄膜トランジスタ及び液晶が形成された液晶パネル用基板又は液晶モジュール用基板、基板上に薄膜トランジスタ及び発光素子が形成されたEL(エレクトロルミネッセンス)パネル用基板又はELモジュール用基板、基板上の薄膜トランジスタ及び液晶が封止材により封止された液晶パネル、基板上の薄膜トランジスタ及び発光素子が封止材により封止されたELパネル、これらパネルにFPC等が取り付けられたモジュール、FPC等の先にドライバICが接続されたモジュール、パネルにCOG方式等によりドライバICが実装されたモジュールに相当する。

T.Shimoda,Ink-jet Technology for Fabrication Processes of Flat Panel Displays,SID 03 DIGEST,p1178-p1181

本発明は、第1の導電層に接するマスクを形成するステップ、前記マスクを用いて第1の導電層をエッチングして、第2の導電層を形成するステップを有し、前記マスクは液滴吐出法により形成し、さらに除去しないことを特徴とする。なお、第1の導電層は、スパッタリング法、蒸着法又は液滴吐出法等を用いて全面に形成するか、又は液滴吐出法を用いて一部に形成する。

また、本発明の必須の構成要件として、マスクとして用いる絶縁層を液滴吐出法で形成することが挙げられるが、液滴吐出法で形成された絶縁層をそのままマスクとして用いるか、又は液滴吐出法で形成された絶縁層に露光処理と現像処理を行った絶縁層をマスクとして用いるかのどちらかの方法を採用する。上記をふまえると、第2の導電層の作製方法には、以下のように、大別して4通りの方法があり、本発明はいずれの方法を用いてもよい。

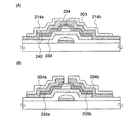

第2の方法は、基板50上に液滴吐出手段53により、導電層54を一部の領域に形成し、その後、マスクとなる絶縁層52を液滴吐出手段53により形成する(図1(B)参照)。次に、絶縁層52をマスクとして、導電層54をエッチングして、導電層55を形成する(図1(C)参照)。その後、絶縁層52は除去しない。

第4の方法は、基板50上に液滴吐出手段53により、導電層54を一部の領域に形成し、その後、マスクとなる絶縁層52を液滴吐出手段53により形成する(図2(D)参照)。次に、フォトマスク56を用いて露光し(図2(E)参照)、現像処理を行って、絶縁層57を形成する(図2(F)参照)。最後に、絶縁層57をマスクとして、導電層54をエッチングして、導電層58を形成する(図2(G)参照)。その後、絶縁層57は除去しない。

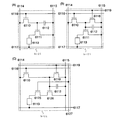

次に、第1のマスク上に、絶縁層、第1の半導体層及び一導電型が付与された第2の半導体層を積層形成するステップ、前記第2の半導体層に接する第2のマスクを液滴吐出法により形成するステップ、前記第2のマスクを用いて、前記第1及び前記第2の半導体層を同時にエッチングして、第3の半導体層及び一導電型が付与された第4の半導体層を形成するステップを有する。上記ステップを経て、ゲート絶縁膜として機能する絶縁層、活性層として機能する第3の半導体層が完成する。

次に、第4の半導体層に接する第3の導電層を形成するステップ、前記第3の導電層に接する第3のマスクを液滴吐出法により形成するステップ、前記第3のマスクを用いて、前記第4の半導体層及び前記第3の導電層を同時にエッチングするステップを有する。上記ステップを経て、第3の導電層がエッチングされ、ソース・ドレイン配線が完成する。また、第4の半導体層がエッチングされ、ソース・ドレイン配線と活性層(第3の半導体層)を電気的に接続し、一導電型が付与された半導体層が完成する。また、上記ステップを経て、チャネルエッチ型の薄膜トランジスタが完成する。

なお、本発明では、上記ステップにおいて、第1乃至第3のマスクから選択された1つ又は複数は除去しないことを特徴とする。上記特徴により、作製時間の短縮及び作製費用の低減を実現する。

次に、第1のマスク上に、第1の絶縁層、第1の半導体層及び第2の絶縁層を積層形成するステップ、前記第2の絶縁層に接する第2のマスクを液滴吐出法により形成するステップ、前記第2のマスクを用いて、前記第2の絶縁層をエッチングして、第3の絶縁層を形成するステップを有する。上記ステップを経て、ゲート絶縁膜として機能する第1の絶縁層が完成する。また、チャネル保護層として機能する第3の絶縁層が完成する。

次に、第2のマスク上に、一導電型が付与された第2の半導体層を形成するステップ、前記第2の半導体層に接する第3のマスクを液滴吐出法により形成するステップ、前記第3のマスクを用いて、前記第1及び前記第2の半導体層を同時にエッチングして、第3の半導体層及び一導電型が付与された第4の半導体層を形成するステップを有する。上記ステップを経て、活性層として機能する第3の半導体層が完成する。

次に、第4の半導体層と接する第3の導電層を形成するステップ、前記第3の導電層に接する第4のマスクを液滴吐出法により形成するステップ、前記第4のマスクを用いて、前記第4の半導体層及び前記第3の導電層を同時にエッチングするステップを有する。上記ステップを経て、第3の導電層がエッチングされ、ソース・ドレイン配線が完成する。また、第4の半導体層がエッチングされ、ソース・ドレイン配線と活性層(第3の半導体層)を電気的に接続し、一導電型が付与された半導体層が完成する。また、上記ステップを経て、チャネル保護型の薄膜トランジスタが完成する。

なお、本発明では、上記ステップにおいて、第1乃至第4のマスクから選択された1つ又は複数は除去しないことを特徴とする。上記特徴により、作製時間の短縮及び作製費用の低減を実現する。

次に、第1のマスク上に、導電層を形成するステップ、前記導電層に接する第2のマスクを液滴吐出法により形成するステップ、前記第2のマスクを用いて、前記導電層をエッチングするステップを有する。上記ステップを経て、前記導電層がエッチングされ、ゲート電極が完成する。また、上記ステップを経て、順スタガ型の薄膜トランジスタが完成する。

なお、本発明では、上記ステップにおいて、第1及び第2のマスクから選択された1つ又は複数は除去しないことを特徴とする。上記特徴により、作製時間の短縮及び作製費用の低減を実現する。

次に、前記第2の半導体層に接する第3の半導体層を形成するステップ、前記第3の半導体層に接する第2のマスクを液滴吐出法により形成するステップ、前記第2のマスクを用いて、前記第2及び前記第3の半導体層をエッチングして、一導電型が付与された第4の半導体層と、第5の半導体層を形成するステップを有する。上記のステップを経て、活性層となる第5の半導体層が完成する。また、ソース・ドレイン配線と、活性層(第5の半導体層)とを電気的に接続する、一導電型が付与された第4の半導体層が完成する。

次に、前記第2のマスク上に、絶縁層、第2の導電層を積層形成するステップ、前記第2の導電層に接する第3のマスクを液滴吐出法により形成するステップ、前記第3のマスクを用いて、前記第2の導電層をエッチングするステップを有する。上記ステップを経て、ゲート絶縁膜として機能する絶縁層が完成し、また、前記第2の導電層をエッチングして、ゲート電極が完成する。

なお、本発明では、上記ステップにおいて、第1乃至第3のマスクから選択された1つ又は複数は除去しないことを特徴とする。上記特徴により、作製時間の短縮及び作製費用の低減を実現する。

次に、第2の半導体層上に、一導電型が付与された第3の半導体層、第1の導電層を積層形成するステップ、前記第1の導電層に接する第2のマスクを液滴吐出法により形成するステップ、前記第2のマスクを用いて、前記第3の半導体層及び前記第1の導電層をエッチングして、一導電型が付与された第4の半導体層と第2の導電層を形成するステップを有する。上記ステップを経て、ソース・ドレイン配線となる第2の導電層、ソース・ドレイン配線と活性層(第2の半導体層)を電気的に接続する、一導電型が付与された第4の半導体層が完成する。

次に、前記第2のマスク上に、絶縁層、第3の導電層を積層形成するステップ、前記第3の導電層に接する第3のマスクを液滴吐出法により形成するステップ、前記第3のマスクを用いて、前記第3の導電層をエッチングするステップを有することを特徴とする。上記ステップを経て、ゲート絶縁膜として機能する絶縁層が完成する。また、第3の導電層をエッチングして、ゲート電極が完成する。

なお、本発明では、上記ステップにおいて、第1乃至第3のマスクから選択された1つ又は複数は除去しないことを特徴とする。上記特徴により、作製時間の短縮及び作製費用の低減を実現する。

(実施の形態1)

(実施の形態2)

(実施の形態3)

(実施の形態4)

(実施の形態5)

(実施の形態6)

53・・・液滴吐出手段、54・・・導電層、55・・・導電層

56・・・フォトマスク、57・・・絶縁層、58・・・導電層

Claims (19)

- 基板上に第1の導電層を形成し、

前記第1の導電層に接する第1のマスクを液滴吐出法により形成し、

前記第1のマスクを用いて、前記第1の導電層をエッチングして、ゲート電極としての機能を有する第2の導電層を形成し、

前記第1のマスク上に、ゲート絶縁膜としての機能を有する絶縁層と、第1の半導体層及び一導電型が付与された第2の半導体層を積層形成し、

前記第2の半導体層に接する第2のマスクを液滴吐出法により形成し、

前記第2のマスクを用いて、前記第1の半導体層及び前記第2の半導体層を同時にエッチングして、活性層としての機能を有する第3の半導体層及び一導電型が付与された第4の半導体層を形成し、

前記第4の半導体層に接する第3の導電層を形成し、

前記第3の導電層に接する第3のマスクを液滴吐出法により形成し、

前記第3のマスクを用いて、前記第4の半導体層及び前記第3の導電層を同時にエッチングして、第5の半導体層及びソース・ドレイン配線としての機能を有する第4の導電層を形成し、

前記第1乃至前記第3のマスクのうち、少なくとも1つは除去しないことを特徴とする薄膜トランジスタの作製方法。 - 基板上に第1の導電層を形成し、

前記第1の導電層に接する第1のマスクを液滴吐出法により形成し、

前記第1のマスクを用いて、前記第1の導電層をエッチングして、ゲート電極としての機能を有する第2の導電層を形成し、

前記第1のマスク上に、ゲート絶縁膜としての機能を有する第1の絶縁層と、第1の半導体層と、第2の絶縁層とを積層形成し、

前記第2の絶縁層に接する第2のマスクを液滴吐出法により形成し、

前記第2のマスクを用いて、前記第2の絶縁層をエッチングして、チャネル保護層としての機能を有する第3の絶縁層を形成し、

前記第2のマスク上に、一導電型が付与された第2の半導体層を形成し、

前記第2の半導体層に接する第3のマスクを液滴吐出法により形成し、

前記第3のマスクを用いて、前記第1の半導体層及び前記第2の半導体層を同時にエッチングして、活性層としての機能を有する第3の半導体層及び一導電型が付与された第4の半導体層を形成し、

前記第4の半導体層と接する第3の導電層を形成し、

前記第3の導電層に接する第4のマスクを液滴吐出法により形成し、

前記第4のマスクを用いて、前記第4の半導体層及び前記第3の導電層を同時にエッチングして、第5の半導体層及びソース・ドレイン配線としての機能を有する第4の導電層を形成し、

前記第1乃至前記第4のマスクのうち、少なくとも1つは除去しないことを特徴とする薄膜トランジスタの作製方法。 - 基板上に第1の半導体層を形成し、

前記第1の半導体層に接する、ゲート絶縁膜としての機能を有する第1のマスクを液滴吐出法により形成し、

前記第1のマスクを用いて、前記第1の半導体層をエッチングして、活性層としての機能を有する第2の半導体層を形成し、

前記第1のマスク上に、第1の導電層を形成し、

前記第1の導電層に接する第2のマスクを液滴吐出法により形成し、

前記第2のマスクを用いて、前記第1の導電層をエッチングして、ゲート電極としての機能を有する第2の導電層を形成し、

前記第1のマスクと前記第2のマスクのうち、少なくとも1つは除去しないことを特徴とする薄膜トランジスタの作製方法。 - 基板上に、ソース・ドレイン配線としての機能を有する第1の導電層と、一導電型が付与された第1の半導体層を積層形成し、

前記第1の半導体層に接する第1のマスクを液滴吐出法により形成し、

前記第1のマスクを用いて、前記第1の半導体層をエッチングして、一導電型が付与された第2の半導体層を形成し、

前記第2の半導体層に接する第3の半導体層を形成し、

前記第3の半導体層に接する第2のマスクを液滴吐出法により形成し、

前記第2のマスクを用いて、前記第2の半導体層及び前記第3の半導体層をエッチングして、一導電型が付与された第4の半導体層と、活性層としての機能を有する第5の半導体層を形成し、

前記第2のマスク上に、ゲート絶縁膜としての機能を有する絶縁層と、第2の導電層を積層形成し、

前記第2の導電層に接する第3のマスクを液滴吐出法により形成し、

前記第3のマスクを用いて、前記第2の導電層をエッチングして、ゲート電極としての機能を有する第3の導電層を形成し、

前記第1乃至前記第3のマスクのうち、少なくとも1つは除去しないことを特徴とする薄膜トランジスタの作製方法。 - 基板上に第1の半導体層を形成し、

前記第1の半導体層に接する第1のマスクを液滴吐出法により形成し、

前記第1のマスクを用いて、前記第1の半導体層をエッチングして、活性層としての機能を有する第2の半導体層を形成し、

前記第2の半導体層上に、一導電型が付与された第3の半導体層と、第1の導電層を積層形成し、

前記第1の導電層に接する第2のマスクを液滴吐出法により形成し、

前記第2のマスクを用いて、前記第3の半導体層及び前記第1の導電層をエッチングして、一導電型が付与された第4の半導体層と、ソース・ドレイン配線としての機能を有する第2の導電層を形成し、

前記第2のマスク上に、ゲート絶縁膜としての機能を有する絶縁層と、第3の導電層を積層形成し、

前記第3の導電層に接する第3のマスクを液滴吐出法により形成し、

前記第3のマスクを用いて、前記第3の導電層をエッチングして、ゲート電極としての機能を有する第4の導電層を形成し、

前記第1乃至前記第3のマスクのうち、少なくとも1つは除去しないことを特徴とする薄膜トランジスタの作製方法。 - 請求項1又は請求項2において、

前記第1の導電層と前記第3の導電層は、液滴吐出法、スパッタリング法又は蒸着法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1又は請求項2において、

前記第1の導電層と前記第3の導電層は、銀、金、銅又はインジウム錫酸化物により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項3において、

前記第1の導電層は、液滴吐出法、スパッタリング法又は蒸着法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項3において、

前記第1の導電層は、銀、金、銅又はインジウム錫酸化物により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項4において、

前記第1の導電層と前記第2の導電層は、液滴吐出法、スパッタリング法又は蒸着法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項4において、

前記第1の導電層と前記第2の導電層は、銀、金、銅又はインジウム錫酸化物により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項5において、

前記第1の導電層と前記第3の導電層は、液滴吐出法、スパッタリング法又は蒸着法により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項5において、

前記第1の導電層と前記第3の導電層は、銀、金、銅又はインジウム錫酸化物により形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項4又は請求項5のいずれか一項において、

前記第1乃至前記第3のマスクは、液滴吐出法により形成された絶縁層に、フォトマスクを用いた露光処理及び現像処理を行って形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項1、請求項4又は請求項5のいずれか一項において、

前記第1乃至前記第3のマスクは、有機材料又は珪素と酸素との結合で骨格構造が形成された材料で形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2において、

前記第1乃至前記第4のマスクは、液滴吐出法により形成された絶縁層に、フォトマスクを用いた露光処理及び現像処理を行って形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項2において、

前記第1乃至前記第4のマスクは、有機材料又は珪素と酸素との結合で骨格構造が形成された材料で形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項3において、

前記第1のマスク及び前記第2のマスクは、液滴吐出法により形成された絶縁層に、フォトマスクを用いた露光処理及び現像処理を行って形成することを特徴とする薄膜トランジスタの作製方法。 - 請求項3において、

前記第1のマスク及び前記第2のマスクは、有機材料又は珪素と酸素との結合で骨格構造が形成された材料で形成することを特徴とする薄膜トランジスタの作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004297094A JP4718818B2 (ja) | 2003-10-10 | 2004-10-12 | 薄膜トランジスタの作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003351974 | 2003-10-10 | ||

| JP2003351974 | 2003-10-10 | ||

| JP2004297094A JP4718818B2 (ja) | 2003-10-10 | 2004-10-12 | 薄膜トランジスタの作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005136403A JP2005136403A (ja) | 2005-05-26 |

| JP2005136403A5 JP2005136403A5 (ja) | 2007-08-30 |

| JP4718818B2 true JP4718818B2 (ja) | 2011-07-06 |

Family

ID=34656092

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004297094A Expired - Fee Related JP4718818B2 (ja) | 2003-10-10 | 2004-10-12 | 薄膜トランジスタの作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4718818B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008226993A (ja) * | 2007-03-09 | 2008-09-25 | Advanced Lcd Technologies Development Center Co Ltd | 半導体装置及びその製造方法 |

| KR20180077332A (ko) * | 2009-12-04 | 2018-07-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| JP2012164876A (ja) * | 2011-02-08 | 2012-08-30 | Mitsubishi Chemicals Corp | 配線又は電極の形成方法、電子デバイス及びその製造方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003179234A (ja) * | 2001-09-05 | 2003-06-27 | Konica Corp | 有機半導体素子およびその製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62140466A (ja) * | 1985-12-16 | 1987-06-24 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ回路の製造方法 |

| JPS62263676A (ja) * | 1986-05-09 | 1987-11-16 | Seiko Instr & Electronics Ltd | 薄膜トランジスタの製造方法 |

| JPH11340129A (ja) * | 1998-05-28 | 1999-12-10 | Seiko Epson Corp | パターン製造方法およびパターン製造装置 |

-

2004

- 2004-10-12 JP JP2004297094A patent/JP4718818B2/ja not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003179234A (ja) * | 2001-09-05 | 2003-06-27 | Konica Corp | 有機半導体素子およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005136403A (ja) | 2005-05-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101030698B1 (ko) | 반도체 장치 제조방법 | |

| US7365805B2 (en) | Display device, manufacturing method thereof, and television receiver | |

| US7247529B2 (en) | Method for manufacturing display device | |

| US9237657B2 (en) | Wiring substrate, semiconductor device, and method for manufacturing thereof | |

| US7795730B2 (en) | Wiring substrate and method of manufacturing thereof, and thin film transistor and method of manufacturing thereof | |

| JP4731970B2 (ja) | 発光装置及びその作製方法 | |

| US7955907B2 (en) | Semiconductor device, television set, and method for manufacturing the same | |

| JP4498715B2 (ja) | 半導体装置の作製方法 | |

| JP4554292B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4737971B2 (ja) | 液晶表示装置および液晶表示装置の作製方法 | |

| JP4877866B2 (ja) | 半導体装置の作製方法 | |

| JP4718818B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4877868B2 (ja) | 表示装置の作製方法 | |

| JP4741218B2 (ja) | 液晶表示装置及びその作製方法、並びに液晶テレビ受像機 | |

| JP4884675B2 (ja) | 半導体装置の作製方法 | |

| JP4817627B2 (ja) | 表示装置の作製方法 | |

| JP4597627B2 (ja) | 配線基板の作製方法 | |

| JP4712332B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4916653B2 (ja) | 配線基板の作製方法及び半導体装置の作製方法 | |

| JP4683898B2 (ja) | 半導体装置の作製方法 | |

| JP4624078B2 (ja) | 液晶表示装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070712 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070712 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101022 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110222 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110308 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110329 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110401 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140408 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140408 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |