JP4541200B2 - 電源制御回路及び電源制御回路の制御方法。 - Google Patents

電源制御回路及び電源制御回路の制御方法。 Download PDFInfo

- Publication number

- JP4541200B2 JP4541200B2 JP2005080668A JP2005080668A JP4541200B2 JP 4541200 B2 JP4541200 B2 JP 4541200B2 JP 2005080668 A JP2005080668 A JP 2005080668A JP 2005080668 A JP2005080668 A JP 2005080668A JP 4541200 B2 JP4541200 B2 JP 4541200B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- current

- circuit

- change rate

- control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B41/00—Circuit arrangements or apparatus for igniting or operating discharge lamps

- H05B41/14—Circuit arrangements

- H05B41/26—Circuit arrangements in which the lamp is fed by power derived from dc by means of a converter, e.g. by high-voltage dc

- H05B41/28—Circuit arrangements in which the lamp is fed by power derived from dc by means of a converter, e.g. by high-voltage dc using static converters

- H05B41/282—Circuit arrangements in which the lamp is fed by power derived from dc by means of a converter, e.g. by high-voltage dc using static converters with semiconductor devices

- H05B41/285—Arrangements for protecting lamps or circuits against abnormal operating conditions

- H05B41/2851—Arrangements for protecting lamps or circuits against abnormal operating conditions for protecting the circuit against abnormal operating conditions

- H05B41/2856—Arrangements for protecting lamps or circuits against abnormal operating conditions for protecting the circuit against abnormal operating conditions against internal abnormal circuit conditions

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S323/00—Electricity: power supply or regulation systems

- Y10S323/908—Inrush current limiters

Description

このように実施例4では、例えば図6に示す実施例3の構成中、電源電流検出用抵抗R21、これに並列に接続されたトランジスタTr43及び電源電流可変手段としてのトランジスタTr27を除く回路構成がマイクロプロセッサMP71に置き換えられている。

(付記1)

導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段と、

負荷回路に供給される電源電流の変化率を検出する電流変化率検出手段と、

電流変化率検出手段により検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御手段とを備え、

前記制御手段は、前記電源電流変化率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施することを特徴とする電源制御回路。

(付記2)

負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段と、

前記負荷回路に供給される前記電源電流の変化率を検出する電流変化率検出手段と、

前記電流変化率検出手段により検出された前記電源電流の前記変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御手段とを備え、

前記制御手段は、前記電源電流変化率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施することを特徴とする電源制御回路。

(付記3)

前記電流変化率検出手段は前記負荷回路に供給される電源電流量に対応する電圧量を微分する微分回路を有し、

前記制御手段は前記微分回路の出力量を基準量と比較する比較手段と、その出力量を積分する積分回路とを有する付記1又は2に記載の電源制御回路。

(付記4)

前記電流変化率検出手段は前記負荷回路に供給される電源電流量を電圧量に変換する電流電圧変換手段と、

前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出手段と、

前記起動検出手段により電源起動作完了を検出した際に前記電流電圧変換手段をバイパスするバイパス手段とを有する付記1乃至3のうちの何れかに記載の電源制御回路。

(付記5)

導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段を有する電源制御回路において前記導通手段の導通量を制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出手段により検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御段階とを備え、

前記制御段階は、前記電源電流変化率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施する段階を有する電源制御回路の制御方法。

(付記6)

インピーダンスが制御可能な構成とされ、負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段を有する電源制御回路において、前記インピーダンス挿入手段のインピーダンスを制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出手段により検出された電源電流の変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御段階とを備え、

前記制御手段は、前記電源電流変化率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施する段階を有する電源制御回路の制御方法。

(付記7)

当該電源制御回路は、前記電流変化率検出段階にて電源電流の変化率を検出するための手段として前記負荷回路に供給される電源電流を電圧に変換する電流電圧変換手段と、

当該電流電圧変換手段をバイパスする手段とを含み、

更に、前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出段階と、

前記起動検出段階において電源起動作完了が検出された際に前記電流電圧変換手段をバイパスする手段を導通させる段階とを有する付記5又は6に記載の電源制御回路の制御方法。

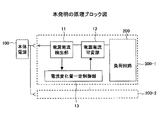

12 電源電流可変部

13 電源増加量一定制御部

R21 電源電流検出用抵抗

22 電圧シフト回路

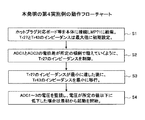

23 微分回路

B24 基準電圧源回路

25 差動増幅回路

26 時定数回路

Tr27 電源電流可変回路

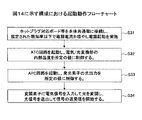

T31 電源電流変化量検出回路

Tr32 電源電流可変回路

A33 差動増幅回路

34 電流電圧変換回路

B35 基準電圧源回路

36 時定数回路

41 電圧シフト回路

42 ヒステリシス付コンパレータ回路

Tr43 スイッチ回路

A53 差動増幅器

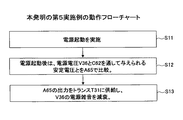

61 定電圧発生回路

C62 交流結合回路

C63、R63 交流結合回路

64 帰還回路

A65 差動増幅器

71 マイクロプロセッサ回路

100 本体電源

200 負荷回路

300−1,...、300−N 光モジュール

Claims (10)

- 導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段と、

負荷回路に供給される電源電流の変化率を検出する電流変化率検出手段と、

電流変化率検出手段により検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施することによって、前記導通手段の導通量の増加率を零より大きい値で一定に保つ制御を実施することを特徴とする電源制御回路。 - 負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段と、

前記負荷回路に供給される前記電源電流の変化率を検出する電流変化率検出手段と、

前記電流変化率検出手段により検出された前記電源電流の前記変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施することによって、前記インピーダンスの減少率を零より大きい値で一定に保つ制御を実施することを特徴とする電源制御回路。 - 導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段と、

負荷回路に供給される電源電流の変化率を検出する電流変化率検出手段と、

電流変化率検出手段により検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施し、

前記電流変化率検出手段は前記負荷回路に供給される電源電流量に対応する電圧量を微分する微分回路を有し、

前記制御手段は前記微分回路の出力量を基準量と比較する比較手段と、その出力量を積分する積分回路とを有する、請求項1に記載の電源制御回路。 - 負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段と、

前記負荷回路に供給される前記電源電流の変化率を検出する電流変化率検出手段と、

前記電流変化率検出手段により検出された前記電源電流の前記変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施し、

前記電流変化率検出手段は前記負荷回路に供給される電源電流量に対応する電圧量を微分する微分回路を有し、

前記制御手段は前記微分回路の出力量を基準量と比較する比較手段と、その出力量を積分する積分回路とを有する、請求項2に記載の電源制御回路。 - 導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段と、

負荷回路に供給される電源電流の変化率を検出する電流変化率検出手段と、

電流変化率検出手段により検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施し、

前記電流変化率検出手段は前記負荷回路に供給される電源電流量を電圧量に変換する電流電圧変換手段と、

前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出手段と、

前記起動検出手段により電源起動作完了を検出した際に前記電流電圧変換手段をバイパスするバイパス手段とを有する電源制御回路。 - 負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段と、

前記負荷回路に供給される前記電源電流の変化率を検出する電流変化率検出手段と、

前記電流変化率検出手段により検出された前記電源電流の前記変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御手段とを備え、

前記制御手段は、前記電源電流の増加率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施し、

前記電流変化率検出手段は前記負荷回路に供給される電源電流量を電圧量に変換する電流電圧変換手段と、

前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出手段と、

前記起動検出手段により電源起動作完了を検出した際に前記電流電圧変換手段をバイパスするバイパス手段とを有する電源制御回路。 - 導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段を有する電源制御回路において前記導通手段の導通量を制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出段階で検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御段階とを有し、

前記制御段階は、前記電源電流の増加率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施することによって、前記導通手段の導通量の増加率を零より大きい値で一定に保つ制御を実施する段階を有する電源制御回路の制御方法。 - インピーダンスが制御可能な構成とされ、負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段を有する電源制御回路において、前記インピーダンス挿入手段のインピーダンスを制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出段階で検出された電源電流の変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御段階とを有し、

前記制御段階は、前記電源電流の増加率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施することによって、前記インピーダンスの減少率を零より大きい値で一定に保つ制御を実施する段階を有する電源制御回路の制御方法。 - 導通量が制御可能な構成とされ、負荷回路に電源電流を導通する導通手段を有する電源制御回路において前記導通手段の導通量を制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出段階で検出された電源電流の変化率に応じて前記導通手段の導通量を制御する制御段階とを有し、

前記制御段階は、前記電源電流の増加率が大きいほど前記導通手段の導通量の増加率を減少させるフィードバック制御を実施する段階を有し、

当該電源制御回路は、前記電流変化率検出段階にて電源電流の変化率を検出するための手段として前記負荷回路に供給される電源電流を電圧に変換する電流電圧変換手段と、

当該電流電圧変換手段をバイパスする手段とを含み、

更に、前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出段階と、

前記起動検出段階において電源起動作完了が検出された際に前記電流電圧変換手段をバイパスする手段を導通させる段階とを有する電源制御回路の制御方法。 - インピーダンスが制御可能な構成とされ、負荷回路に電源電流を供給する回路に挿入されたインピーダンス挿入手段を有する電源制御回路において、前記インピーダンス挿入手段のインピーダンスを制御する方法であって、

前記負荷回路に供給される電源電流の変化率を検出する電流変化率検出段階と、

前記電流変化率検出段階で検出された電源電流の変化率に応じて前記インピーダンス挿入手段のインピーダンスを制御する制御段階とを有し、

前記制御段階は、前記電源電流の増加率が大きいほど前記インピーダンス挿入手段のインピーダンスの減少率を減少させるフィードバック制御を実施する段階を有し、

当該電源制御回路は、前記電流変化率検出段階にて電源電流の変化率を検出するための手段として前記負荷回路に供給される電源電流を電圧に変換する電流電圧変換手段と、

当該電流電圧変換手段をバイパスする手段とを含み、

更に、前記負荷回路に印加される電源電圧を検出することで前記負荷回路に対する電源起動動作の完了を検出する起動検出段階と、

前記起動検出段階において電源起動作完了が検出された際に前記電流電圧変換手段をバイパスする手段を導通させる段階とを有する電源制御回路の制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005080668A JP4541200B2 (ja) | 2005-03-18 | 2005-03-18 | 電源制御回路及び電源制御回路の制御方法。 |

| US11/209,644 US7358712B2 (en) | 2005-03-18 | 2005-08-24 | Power supply control circuit and control method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005080668A JP4541200B2 (ja) | 2005-03-18 | 2005-03-18 | 電源制御回路及び電源制御回路の制御方法。 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006262682A JP2006262682A (ja) | 2006-09-28 |

| JP2006262682A5 JP2006262682A5 (ja) | 2008-04-10 |

| JP4541200B2 true JP4541200B2 (ja) | 2010-09-08 |

Family

ID=37009608

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005080668A Expired - Fee Related JP4541200B2 (ja) | 2005-03-18 | 2005-03-18 | 電源制御回路及び電源制御回路の制御方法。 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7358712B2 (ja) |

| JP (1) | JP4541200B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010182229A (ja) * | 2009-02-09 | 2010-08-19 | Nec Infrontia Corp | 情報処理装置および給電制御方法 |

| DE102010022302A1 (de) * | 2010-06-01 | 2011-12-01 | Infineon Technologies Austria Ag | Spannungsregler |

| CN103970079B (zh) * | 2013-01-30 | 2016-12-28 | 华为技术有限公司 | 供电系统、电子设备以及电子设备的电力分配方法 |

| CN105162329A (zh) * | 2014-06-11 | 2015-12-16 | 华硕电脑股份有限公司 | 电子装置及其电源供应器的输出功率的识别方法 |

| US9819174B2 (en) | 2015-01-29 | 2017-11-14 | Lattice Semiconductor Corporation | Hotswap operations for programmable logic devices |

| WO2017183243A1 (ja) * | 2016-04-22 | 2017-10-26 | 株式会社オートネットワーク技術研究所 | 電源装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000175439A (ja) * | 1998-12-08 | 2000-06-23 | Nec Corp | 突入電流防止回路 |

| JP2004280452A (ja) * | 2003-03-14 | 2004-10-07 | Tdk Corp | 電流制御回路 |

| JP2005137060A (ja) * | 2003-10-28 | 2005-05-26 | Kyocera Mita Corp | 突入電流防止装置およびそれを用いる画像形成装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4777409A (en) * | 1984-03-23 | 1988-10-11 | Tracy Stanley J | Fluorescent lamp energizing circuit |

| JPS63200614A (ja) | 1987-02-16 | 1988-08-18 | Fujitsu Ltd | 突入電流抑制回路 |

| JPH07143736A (ja) | 1993-11-18 | 1995-06-02 | Sumitomo Metal Ind Ltd | 容量性負荷の突入電流抑制回路 |

| JPH07302142A (ja) | 1994-05-09 | 1995-11-14 | Fujitsu Ltd | 電源システム |

| JPH0830341A (ja) | 1994-07-13 | 1996-02-02 | Oki Electric Ind Co Ltd | 電流検出方法及び電源装置 |

| KR100208803B1 (ko) * | 1995-11-10 | 1999-07-15 | 윤종용 | 전자 안정기 회로 |

| JP2923873B2 (ja) * | 1996-12-03 | 1999-07-26 | 日本電気株式会社 | 圧電トランスの制御方法及び駆動回路 |

-

2005

- 2005-03-18 JP JP2005080668A patent/JP4541200B2/ja not_active Expired - Fee Related

- 2005-08-24 US US11/209,644 patent/US7358712B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000175439A (ja) * | 1998-12-08 | 2000-06-23 | Nec Corp | 突入電流防止回路 |

| JP2004280452A (ja) * | 2003-03-14 | 2004-10-07 | Tdk Corp | 電流制御回路 |

| JP2005137060A (ja) * | 2003-10-28 | 2005-05-26 | Kyocera Mita Corp | 突入電流防止装置およびそれを用いる画像形成装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20060208668A1 (en) | 2006-09-21 |

| US7358712B2 (en) | 2008-04-15 |

| JP2006262682A (ja) | 2006-09-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4541200B2 (ja) | 電源制御回路及び電源制御回路の制御方法。 | |

| US7548043B2 (en) | Power supply apparatus and method for providing voltage | |

| EP2887174B1 (en) | CC-CV method to control the startup current for LDO | |

| CN110299819B (zh) | 一种数字化电源控制电路及方法 | |

| JP2000341059A (ja) | 無線周波数電力制御器に使用するオフセット電圧キャンセレーションシステム | |

| US9237614B2 (en) | Capacitance amplifying circuit applied to a controller of a power convertor and operation method thereof | |

| US9882069B2 (en) | Biasing voltage generating circuit for avalanche photodiode and related control circuit | |

| CN109428487B (zh) | 开关调整器 | |

| CN108432112B (zh) | Dc-dc变换器以及负载驱动用半导体集成电路 | |

| CN105978301B (zh) | 用于开关电源的控制装置 | |

| JP2006121694A (ja) | 光変換器の可変雑音制御 | |

| CN113746318A (zh) | 直流电源装置、电流稳定化电路及电源线的噪声抑制方法 | |

| CN103795363A (zh) | 具有用于在自动增益控制回路中衰减放大器的至少一个输入信号的单元的电子电路 | |

| JP2006229224A (ja) | レーザダイオードのレーザ閾値を決定する方法 | |

| US10476610B2 (en) | Semiconductor integrated circuit, semiconductor system, and electric source voltage control method | |

| JPH0774562A (ja) | 時分割多重信号伝送用の伝送システムおよび送信機ならびに制御ループ | |

| KR20190029896A (ko) | 온도 센싱 회로 | |

| US20200153268A1 (en) | Power supply circuit, power supply system, and control method | |

| JP2008011585A (ja) | スイッチングレギュレータ | |

| US20100090666A1 (en) | Method for regulating supply voltage | |

| US6734746B1 (en) | Mute circuit | |

| WO2002080356A2 (en) | Current sense automatic level control system with pre-bias | |

| JP2012044456A (ja) | 可変利得増幅器の利得制御装置及びその利得制御方法 | |

| KR101380243B1 (ko) | Pwm을 이용하여 직류 오프셋을 보상하는 고 이득 차동 증폭기 회로 | |

| JP2006238064A (ja) | 送信出力制御装置及びその方法並びにそれを用いた送信機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080227 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090910 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090929 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091125 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100118 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100622 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100623 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130702 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |