JP4527552B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP4527552B2 JP4527552B2 JP2005008855A JP2005008855A JP4527552B2 JP 4527552 B2 JP4527552 B2 JP 4527552B2 JP 2005008855 A JP2005008855 A JP 2005008855A JP 2005008855 A JP2005008855 A JP 2005008855A JP 4527552 B2 JP4527552 B2 JP 4527552B2

- Authority

- JP

- Japan

- Prior art keywords

- fin

- type semiconductor

- source

- insulating film

- semiconductor region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

- H10D30/6219—Fin field-effect transistors [FinFET] characterised by the source or drain electrodes

Landscapes

- Thin Film Transistor (AREA)

Description

Fu-Liang Yang et al.; 2002 Symposium onVLSI Technology Digest of Technical Papers, p.104, 2002 Bin Yu et al.; IEDM Tech. Dig., p251, 2002 Fin−FETのチャネルは、ゲート絶縁膜を介してゲート電極と対向する側面に形成される。チャネル長は、ゲート電極(ポリシリコン層)の幅で決定される。チャネル幅はフィンの高さで決定される。フィンの長さはプロセス精度などによって決定されるが、幅狭のソース/ドレインの引き出し部は、ソース/ドレインの抵抗を高くする。フィンの端部を拡げず、フィンを切断して金属層を埋め込み、ショットキコンタクトを形成する提案もある。

絶縁性表面を有する支持基板と、

前記支持基板上に形成され、支持基板表面に対してほぼ垂直な一対の側面および前記両側面を接続する上面を有し、第1導電型を有するフィン型半導体領域と、

前記フィン型半導体領域の中間部を横断して形成され、ゲート絶縁膜とその上に形成された導電性ゲート電極とを含む絶縁ゲート電極構造と、

前記導電性ゲート電極両側の前記フィン型半導体領域に第2導電型不純物を添加して形成された、第2導電型を有するソース/ドレイン領域と、

前記導電性ゲート電極の側壁上に形成された第1サイドウォール絶縁膜と、前記フィン型半導体領域の側壁上に形成され、前記ソース/ドレイン領域上において、前記フィン型半導体領域の側面の上端から下端に達する開口を有する第2サイドウォール絶縁膜と、を含むサイドウォール絶縁膜と、

前記サイドウォール絶縁膜の開口内に露出された前記ソース/ドレイン領域の表面に形成されたシリサイド層と、

前記シリサイド層にコンタクトするソース/ドレイン電極と、

前記フィン型半導体領域、前記絶縁ゲート電極構造を埋め込み、前記サイドウォール絶縁膜の開口を露出するコンタクトホールを有する層間絶縁膜と、

を有し、前記シリサイド層は前記コンタクトホール内に形成されている半導体装置

が提供される。

(a)SOI基板の半導体層をパターニングし、絶縁表面を有する支持基板上に、支持基板表面に対しほぼ垂直な一対の側面および前記両側面を接続する上面を有するフィン型半導体領域を形成する工程と、

(b)前記フィン型半導体領域の中間部を横断し、ゲート絶縁膜とその上の導電性ゲート電極とを含む絶縁ゲート電極構造を形成する工程と、

(c)前記フィン型半導体領域および前記絶縁ゲート電極構造の側面上にサイドウォール絶縁膜を形成する工程と、

(d)前記絶縁ゲート電極構造両側の前記フィン型半導体領域にソース/ドレイン領域を形成する工程と、

(e)前記サイドウォール絶縁膜を覆って、層間絶縁膜を堆積する工程と、

(f)前記層間絶縁膜を貫通して前記ソース/ドレイン領域に達するコンタクトホールを開口すると共に、前記コンタクトホール内の前記サイドウォール絶縁膜を除去し、前記ソース/ドレイン領域を露出する工程と、

(g)前記コンタクトホール内に露出した前記ソース/ドレイン領域にシリサイド層を形成する工程と、

を含む半導体装置の製造方法

が提供される。

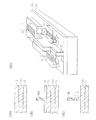

図1Dに示すように、シリコン層13の上に酸化シリコン層15を例えば厚さ10nm〜20nmCVDにより堆積し、ハードマスク層を形成する。酸化シリコン層15の上に、レジストマスクRM1を形成する。このレジストマスクRM1は、シリコン層13をエッチしてフィンを形成するためのマスクである。フィンの幅は、例えば約20nmである。レジストマスクRM1をエッチングマスクとし、ハードマスク層15をエッチングする。続いて、レジストマスクRM1及びハードマスク層15をマスクとしてシリコン層13をエッチングする。

このようにして、シリコン層13の上面及び側面に酸窒化膜のゲート絶縁膜15が形成される。

図1J、1Kに示すように、フィン型半導体領域13の中間部を横断するポリシリコンのゲート電極16が形成される。図1Jはゲート電極を通る断面図であり、図1Kは、ゲート電極16を形成した状態の平面図である。幅約20nmのフィン型半導体領域13の中間部を横断して、幅約50nmのポリシリコンゲート電極16が形成されている。

レジストマスクRM3は、フィン型半導体領域13のソース/ドレインに対するコンタクトを形成する領域に窓W1、W2を有する。このレジストマスクRM3をエッチングマスクとし、RIEにより層間絶縁膜22をエッチングする。酸化シリコンの層間絶縁膜22がエッチングされる際に、酸化シリコンのサイドウォール絶縁膜21も同時にエッチングされる。

図1Uは、層間絶縁膜を貫通してコンタクトホールCHがエッチされ、サイドウォール絶縁膜も除去されてシリコンのフィン型半導体領域13が露出した状態を示す。なお、コンタクトホールCHをエッチングする反応性ガスとしてはフッ素を含むガス、例えばCF4、CHF3、C2F6、C4F8等を圧力1Pa〜100Paとし、13.56MHzの高周波電力を印加したRIEにより行なうことができる。酸化シリコンのエッチングは、窒化シリコン層14でストップされる。エッチング終了後、希フッ酸水溶液でウエットエッチングを行なうことにより、シリコン層13表面の酸化膜を完全に除去する。

図1Vは、コンタクトホールCH1、CH2を形成した状態の平面図を示す。コンタクトホール内においては酸化シリコンのサイドウォール絶縁膜が除去され、フィン型シリコン領域13の上面及び側面が露出する。

12 埋め込み酸化シリコン層(BOX層)

12x 窒化シリコン(酸化窒化シリコン)層

13 シリコン層(フィン型半導体領域)

14 窒化シリコン層

15、17 CVD酸化シリコン層

16 ポリシリコン層

18 ソース/ドレイン領域

RM レジストマスク

CL キャップ層

21 サイドウォール酸化膜(絶縁層)

22 層間絶縁層

23 金属(Co,Ni)層

24 シリサイド層

CH コンタクトホール

Claims (9)

- 絶縁性表面を有する支持基板と、

前記支持基板上に形成され、支持基板表面に対してほぼ垂直な一対の側面および前記両側面を接続する上面を有し、第1導電型を有するフィン型半導体領域と、

前記フィン型半導体領域の中間部を横断して形成され、ゲート絶縁膜とその上に形成された導電性ゲート電極とを含む絶縁ゲート電極構造と、

前記導電性ゲート電極両側の前記フィン型半導体領域に第2導電型不純物を添加して形成された、第2導電型を有するソース/ドレイン領域と、

前記導電性ゲート電極の側壁上に形成された第1サイドウォール絶縁膜と、前記フィン型半導体領域の側壁上に形成され、前記ソース/ドレイン領域上において、前記フィン型半導体領域の側面の上端から下端に達する開口を有する第2サイドウォール絶縁膜と、を含むサイドウォール絶縁膜と、

前記サイドウォール絶縁膜の開口内に露出された前記ソース/ドレイン領域の表面に形成されたシリサイド層と、

前記シリサイド層にコンタクトするソース/ドレイン電極と、

前記フィン型半導体領域、前記絶縁ゲート電極構造を埋め込み、前記サイドウォール絶縁膜の開口を露出するコンタクトホールを有する層間絶縁膜と、

を有し、前記シリサイド層は前記コンタクトホール内に形成されている半導体装置。 - 前記ソース/ドレイン領域は、前記フィン型半導体領域の側面および上面に形成され、前記シリサイド層は前記フィン型半導体領域の側面および上面上に形成されている請求項1記載の半導体装置。

- さらに、前記フィン型半導体領域の上面上に形成されている絶縁性保護膜を有し、

前記ゲート絶縁膜は前記フィン型半導体層の側面上に形成され、前記シリサイド層は前記フィン型半導体領域の側面上に形成されている請求項1記載の半導体装置。 - 前記ソース/ドレイン電極は、前記コンタクトホールを埋め込んで形成されている請求項1記載の半導体装置。

- (a)SOI基板の半導体層をパターニングし、絶縁表面を有する支持基板上に、支持基板表面に対しほぼ垂直な一対の側面および前記両側面を接続する上面を有するフィン型半導体領域を形成する工程と、

(b)前記フィン型半導体領域の中間部を横断し、ゲート絶縁膜とその上の導電性ゲート電極とを含む絶縁ゲート電極構造を形成する工程と、

(c)前記フィン型半導体領域および前記絶縁ゲート電極構造の側面上にサイドウォール絶縁膜を形成する工程と、

(d)前記絶縁ゲート電極構造両側の前記フィン型半導体領域にソース/ドレイン領域を形成する工程と、

(e)前記サイドウォール絶縁膜を覆って、層間絶縁膜を堆積する工程と、

(f)前記層間絶縁膜を貫通して前記ソース/ドレイン領域に達するコンタクトホールを開口すると共に、前記コンタクトホール内の前記サイドウォール絶縁膜を除去し、前記ソース/ドレイン領域を露出する工程と、

(g)前記コンタクトホール内に露出した前記ソース/ドレイン領域にシリサイド層を形成する工程と、

を含む半導体装置の製造方法。 - 前記工程(a)が、上面および側面を露出した構造のフィン型半導体領域を形成し、前記工程(d)が、前記フィン型半導体領域の上面および側面に前記ソース/ドレイン領域を形成し、前記工程(f)が、前記フィン型半導体領域のソース/ドレイン領域の上面および側面を露出し、前記工程(g)が、露出された前記ソース/ドレイン領域の上面および側面上にシリサイド層を形成する請求項5記載の半導体装置の製造方法。

- 前記工程(a)が、フィン型半導体領域上に絶縁保護膜を備えたフィン型構造を形成し、前記工程(d)が、前記フィン型半導体領域の側面に前記ソース/ドレイン領域を形成し、前記工程(f)が、前記フィン型半導体領域側面のソース/ドレイン領域を露出し、前記工程(g)が、露出された前記フィン型半導体領域側面のソース/ドレイン領域上にシリサイド層を形成する請求項5記載の半導体装置の製造方法。

- さらに、(h)前記コンタクトホール内にソース/ドレイン電極を埋め込む工程を含む請求項5〜7のいずれか1項記載の半導体装置の製造方法。

- さらに、(i)前記SOI基板に窒化処理を行い、半導体層と埋め込み絶縁膜との界面に窒化膜を形成する工程を含む請求項5〜8のいずれか1項記載の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005008855A JP4527552B2 (ja) | 2005-01-17 | 2005-01-17 | 半導体装置とその製造方法 |

| US11/123,145 US7282766B2 (en) | 2005-01-17 | 2005-05-06 | Fin-type semiconductor device with low contact resistance |

| US11/896,826 US7396710B2 (en) | 2005-01-17 | 2007-09-06 | Fin-type semiconductor device with low contact resistance and its manufacture method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005008855A JP4527552B2 (ja) | 2005-01-17 | 2005-01-17 | 半導体装置とその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006196822A JP2006196822A (ja) | 2006-07-27 |

| JP4527552B2 true JP4527552B2 (ja) | 2010-08-18 |

Family

ID=36802631

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005008855A Expired - Fee Related JP4527552B2 (ja) | 2005-01-17 | 2005-01-17 | 半導体装置とその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4527552B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8258585B2 (en) * | 2008-05-29 | 2012-09-04 | Panasonic Corporation | Semiconductor device |

| JP5305969B2 (ja) * | 2009-02-17 | 2013-10-02 | 株式会社東芝 | 半導体装置 |

| US9887192B2 (en) * | 2016-06-30 | 2018-02-06 | Globalfoundries Inc. | Interconnects for vertical-transport field-effect transistors |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002118255A (ja) * | 2000-07-31 | 2002-04-19 | Toshiba Corp | 半導体装置およびその製造方法 |

| US7358121B2 (en) * | 2002-08-23 | 2008-04-15 | Intel Corporation | Tri-gate devices and methods of fabrication |

-

2005

- 2005-01-17 JP JP2005008855A patent/JP4527552B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006196822A (ja) | 2006-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7282766B2 (en) | Fin-type semiconductor device with low contact resistance | |

| US9887274B2 (en) | FinFETs and methods for forming the same | |

| CN106098775B (zh) | 半导体器件 | |

| US7648883B2 (en) | Phosphorous doping methods of manufacturing field effect transistors having multiple stacked channels | |

| US7229884B2 (en) | Phosphorous doping methods of manufacturing field effect transistors having multiple stacked channels | |

| US20040132236A1 (en) | Mos transistor | |

| CN103050407B (zh) | 嵌入式晶体管 | |

| JP2006294995A (ja) | 電界効果トランジスタ及びその製造方法 | |

| TWI807067B (zh) | 半導體結構與其形成方法、鰭狀場效電晶體裝置、與閘極結構 | |

| TW202207461A (zh) | 電晶體及其製造方法 | |

| WO2006132172A1 (ja) | フィン型電界効果型トランジスタ、半導体装置及びその製造方法 | |

| TWI854640B (zh) | 奈米結構場效電晶體及其製造方法 | |

| TWI860699B (zh) | 半導體裝置以及其形成之方法 | |

| JP5224769B2 (ja) | 立体的形状の活性領域を含むcmos構造体 | |

| TW202133271A (zh) | 半導體裝置 | |

| US8378395B2 (en) | Methods of fabricating field effect transistors having protruded active regions | |

| JP4950064B2 (ja) | サドル型mos素子 | |

| JP2006196821A (ja) | 半導体装置とその製造方法 | |

| TW202207468A (zh) | 半導體裝置及方法 | |

| JP2006054423A (ja) | 半導体装置及びその製造方法 | |

| CN115881771A (zh) | 晶体管、半导体器件及其形成方法 | |

| JP4527552B2 (ja) | 半導体装置とその製造方法 | |

| JP2013235880A (ja) | 半導体装置とその製造方法 | |

| CN113206089A (zh) | 半导体器件和方法 | |

| CN100550424C (zh) | 半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080729 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100601 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100603 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130611 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |