JP4494031B2 - ストレージ制御装置、及びストレージ制御装置の制御方法 - Google Patents

ストレージ制御装置、及びストレージ制御装置の制御方法 Download PDFInfo

- Publication number

- JP4494031B2 JP4494031B2 JP2004030825A JP2004030825A JP4494031B2 JP 4494031 B2 JP4494031 B2 JP 4494031B2 JP 2004030825 A JP2004030825 A JP 2004030825A JP 2004030825 A JP2004030825 A JP 2004030825A JP 4494031 B2 JP4494031 B2 JP 4494031B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- circuit board

- memory

- nonvolatile memory

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

Description

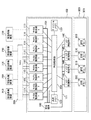

まず、本実施の形態に係るストレージ制御装置100を含むストレージ装置600の全体構成を示すブロック図を図1に示す。

ストレージ装置600は、ストレージ制御装置100とストレージ駆動装置300とを備える。ストレージ制御装置100は、情報処理装置200からデータ入出力要求を受信し、データ入出力要求に応じてストレージ駆動装置300が備えるデータを記憶するハードディスクドライブに対してデータの読み書きを行う。

ストレージ駆動装置300は多数のハードディスクドライブを備えている。そしてストレージ駆動装置300は、これらのハードディスクドライブにより提供される物理的な記憶領域である物理ボリュームと、物理ボリューム上に論理的に設定される記憶領域である論理ボリュームとを含む、データを記憶するための記憶領域である記憶ボリューム310に対してデータの読み書きを行う。

ストレージ制御装置100はチャネル制御部110、共有メモリ120、キャッシュメモリ130、ディスク制御部140、管理端末160、内部接続部150を備える。

また、チャネル制御部110にディスク制御部140の機能を持たせることにより、チャネル制御部110がストレージ駆動装置300に記憶されたデータの読み書きを行うようにすることもできる。

管理端末160はストレージ装置600を保守・管理するためのコンピュータ等の情報機器である。オペレータは、管理端末160を操作することにより、例えばストレージ駆動装置300内のハードディスクドライブの構成の設定や、情報処理装置200とチャネル制御部110との間の通信路であるパスの設定、記憶ボリューム310の設定、チャネル制御部110やディスク制御部140において実行されるマイクロプログラムのインストール等を行うことができる。これらの設定や制御は、管理端末160が備えるユーザインタフェース、あるいは管理端末160で動作するWebサーバにより提供されるWebページを表示する情報処理装置200等のユーザインタフェースから行うようにすることができる。

管理端末160は、CPU161、メモリ162、ポート163、記録媒体読取装置164、入力装置165、出力装置166、記憶装置168を備える。

次に、本実施の形態に係るストレージ装置600の外観構成を図2に示す。また、ストレージ制御装置100の外観構成を図3に示す。

図2に示すように、本実施の形態に係るストレージ装置600はストレージ制御装置100及びストレージ駆動装置300がそれぞれの筐体に納められた形態をしている。図2に示す例では、ストレージ制御装置100の筐体の両側にストレージ駆動装置300の筐体が配置されている。ストレージ駆動装置300には多数のハードディスクドライブが整列して装着されている。

末160を使用することができる。なお図3に示した管理端末160はいわゆるノート型パーソナルコンピュータの形態をしているが、どのような形態とすることも可能である。

チャネル制御部110の構成を図5に示す。

チャネル制御部110を有する回路基板は一つのユニット化されたボードとして構成される。つまりチャネル制御部110を有する回路基板は、一枚もしくは複数枚の回路基板を含んで一つのユニット化されたボードとして構成される。回路基板には、インタフェース部111、メモリ113、CPU112、NVRAM(NonVolatile Random Access Memory)114、コネクタ115が形成される。

CPU112は、チャネル制御部110全体の制御を司る。CPU112によりメモリ113に記憶された各種の動作を行うためのコードから構成されるチャネル制御プログラム810やNVRAM114に記憶された各種プログラムが実行されることにより本実施の形態に係るチャネル制御部110の機能が実現される。

NVRAM114はCPU112の制御を司るプログラムを格納する不揮発性メモリである。NVRAM114に記憶されるプログラムの内容は、管理端末160からの指示により書き込みや書き換えを行うことができる。

チャネル制御部110はコネクタ115を備えている。コネクタ115が論理基板180のコネクタ181と嵌合することにより、チャネル制御部110はストレージ制御装置100の内部接続部150や管理端末160等と電気的に接続される。

次にディスク制御部140の構成を示す図を図6に示す。

ディスク制御部140を有する回路基板は一つのユニット化されたボードとして構成される。つまりディスク制御部140を有する回路基板は、一枚もしくは複数枚の回路基板を含んで一つのユニット化されたボードとして構成される。回路基板には、インタフェース部141、メモリ143、CPU142、NVRAM144、コネクタ145が形成される。

CPU142は、ディスク制御部140全体の制御を司る。CPU142によりメモリ143に記憶された各種の動作を行うためのコードから構成されるディスク制御プログラム820やNVRAM144に記憶された各種プログラムが実行されることにより本実施の形態に係るディスク制御部140の機能が実現される。

NVRAM144はCPU142の制御を司るプログラムを格納する不揮発性メモリである。NVRAM144に記憶されるプログラムの内容は、管理端末160からの指示により書き込みや書き換えを行うことができる。

またディスク制御部140はコネクタ145を備えている。コネクタ145が論理基板180のコネクタ181と嵌合することにより、ディスク制御部140はストレージ制御装置100の内部接続部150や管理端末160等と電気的に接続される。

次に、本実施の形態に係る情報処理装置200の構成を示すブロック図を図7に示す。

情報処理装置200は、CPU210、メモリ220、ポート230、記録媒体読取装置240、入力装置250、出力装置260、記憶装置280を備える。

次に本実施の形態に係るキャッシュメモリ130の構成について、図9、図10、及び図14に示す。

まず、本実施の形態に係るストレージ制御装置100におけるキャッシュメモリ130の構成を図9に示す。またキャッシュメモリ130の詳細な構成を図10に示す。

まず、情報処理装置200からデータ書き込み要求を受信したチャネル制御部110から、内部接続部150を経由して書き込みコマンドが送信されてくると、その書き込みコマンドはパス側セレクタ回路720を介してパケットバッファ2(740)に記憶される。またパケットバッファ2(740)には、書き込みコマンドに続いて送信されてくる書き込みデータが次々と記憶されてゆく。その間、コマンド/アドレス解析部710は、パケットバッファ2(740)に記憶された書き込みコマンドをデコードしてコマンドの種類を書き込みコマンドであると特定すると共に、不揮発性メモリ131において書き込みデータが書き込まれるアドレスや書き込みデータのデータ量についても特定する。そして、コマンド/アドレス解析部710からメモリ制御部700に対して、書き込みデータが書き込まれるアドレスや書き込みデータのデータ量等の情報が送られる。そうするとメモリ制御部700は、不揮発性メモリ131に対して書き込みデータが書き込まれるアドレスとライトイネーブル信号を入力すると共に、メモリ側セレクタ回路730を介して、パケットバッファ2(740)に記憶されている書き込みデータを不揮発性メモリ131に転送する。メモリ制御部700は、全ての書き込みデータが不揮発性メモリ131に書き込まれるまで、順次書き込みデータが書き込まれるアドレスを更新しながら、上記書き込みデータの転送を行う。全ての書き込みデータが不揮発性メモリ131に書き込まれたら、終了ステータス情報をスタータスレジスタ750に書き込むと共に、その終了ステータス情報を、メモリ側セレクタ回路730を介してパケットバッファ1(740)に転送し、内部接続部150を介してチャネル制御部110に送信する。これにより、チャネル制御部110から送信されたキャッシュメモリ130への書き込みコマンドに応じて、書き込みデータを不揮発性メモリ131へ書き込むことができる。

まず情報処理装置200からデータ読み出し要求を受信したチャネル制御部110から、内部接続部150を経由して読み出しコマンドが送信されてくると、その読み出しコマンドはパス側セレクタ回路720を介してパケットバッファ2(740)に記憶される。そうすると、コマンド/アドレス解析部710は、パケットバッファ2(740)に記憶された読み出しコマンドをデコードしてコマンドの種類を読み出しコマンドであると特定すると共に、読み出しデータが記憶されている不揮発性メモリ131におけるアドレスや読み出しデータのデータ量について特定する。そして、コマンド/アドレス解析部710からメモリ制御部700に対して、読み出しデータのアドレスや読み出しデータのデータ量等の情報が送られる。そうするとメモリ制御部700は、不揮発性メモリ131に対して読み出しデータのアドレスとリードイネーブル信号を入力する。そしてメモリ制御部700は、不揮発性メモリ131から読み出されるデータを、メモリ側セレクタ回路730を介して、パケットバッファ1(740)に転送する。パケットバッファ1(740)に転送された読み出しデータは、内部接続部150を介してチャネル制御部110に送信される。メモリ制御部700は、要求された全てのデータが不揮発性メモリ131から読み出されるまで順次アドレスを更新しながら、上記読み出しデータの転送を行う。また全ての読み出しデータの読み出しが完了したら、終了ステータス情報をスタータスレジスタ750に書き込むと共に、その終了ステータス情報を、メモリ側セレクタ回路730を介してパケットバッファ1(740)に転送し、内部接続部150を介してチャネル制御部110に送信する。これにより、チャネル制御部110から送信されたキャッシュメモリ130への読み出しコマンドに応じて、データを不揮発性メモリ131から読み出すことができる。

まず管理端末160からデータの消去要求を受信したチャネル制御部110から、内部接続部150を経由して消去コマンドが送信されてくると、その消去コマンドはパス側セレクタ回路720を介してパケットバッファ2(740)に記憶される。そうすると、コマンド/アドレス解析部710は、パケットバッファ2(740)に記憶された消去コマンドをデコードしてコマンドの種類を消去コマンドであると特定する。また消去コマンドに、不揮発性メモリ131においてデータを消去する範囲(所定範囲)を示す情報(第1のアドレス、第2のアドレス)や消去のためのデータ(他のデータ)を示す情報が含まれている場合には、それらの情報についても特定する。そして、コマンド/アドレス解析部710からメモリ制御部700に対して、データを消去する範囲を示す情報や消去のためのデータを示す情報が送られる。そうするとメモリ制御部700は、コマンド/アドレス解析部710から送信されたデータを消去する範囲を示す情報のうち、消去を開始するアドレス(第1のアドレス)を示す情報を消去開始アドレスレジスタ(消去範囲記憶回路)752に記憶し、消去を終了するアドレス(第2のアドレス)を示す情報を消去終了アドレスレジスタ(消去範囲記憶回路)753に記憶する。またメモリ制御部700は消去のためのデータを消去データレジスタ(書き換えデータ記憶回路)751に記憶する。またコマンド/アドレス解析部710からは、不揮発性メモリ131に記憶されているデータを消去すべき旨の情報がモードレジスタ134に書き込まれる。モードレジスタ134にその旨の情報が書き込まれると、イレース制御回路133は、メモリ制御部700に不揮発性メモリ131に記憶されているデータを消去すべき旨の情報を送信する。そうするとメモリ制御部700は、不揮発性メモリ131に対して、不揮発性メモリ131のアドレスとライトイネーブル信号を入力して、消去データレジスタ751に記憶されている消去のためのデータを、不揮発性メモリ131に書き込む。このようにして不揮発性メモリ131に記憶されているデータを消去する。メモリ制御部700は、消去を開始するアドレスから消去を終了するアドレスまでの範囲に記憶されているデータを消去し終わるまで、順次不揮発性メモリ131のアドレスを更新しながら、上記消去を行う。全ての範囲のデータが消去されたら、メモリ制御部700は終了ステータス情報をスタータスレジスタ750に書き込むと共に、その終了ステータス情報を、メモリ側セレクタ回路730を介してパケットバッファ1(740)に転送し、内部接続部150を介してチャネル制御部110に送信する。これにより、チャネル制御部110から送信されたキャッシュメモリ130への消去コマンドに応じて、不揮発性メモリ131の消去を行うことができる。

不揮発性メモリ131のデータの消去が完了し、キャッシュメモリ130からチャネル制御部110を経由して終了ステータスが送信されてくると、例えば図13に示すようなメッセージが表示されるようにすることもできる。

まず、図11に示す設定画面における「データ消去」欄にマウスのカーソルが重ねられ、クリックされることにより、管理端末160にキャッシュメモリ130に記憶されているデータの消去の指示が受け付けられると(S1000)、管理端末160はチャネル制御部110に対して消去コマンドを送信する(S1001)。そうするとチャネル制御部110は、消去コマンドを内部接続部150を介してキャッシュメモリ130に送信する(S1002)。そしてキャッシュメモリ130は、不揮発性メモリ131に記憶されているデータの消去を開始し(S1003)、データの消去が終了したらチャネル制御部110に対して終了ステータス情報を送信する(S1004)。そうするとチャネル制御部110は終了ステータス情報を管理端末160に送信する(S1005)。そして管理端末160は、例えば図13に示したようなメッセージを出力装置166に表示することにより、終了ステータスを表示する(S1006)。

基板取り外し検出器135は、キャッシュメモリ130の回路基板が論理基板180から取り外されたことを示す回路基板取り外し情報を出力する。この回路基板取り外し情報により、キャッシュメモリ130の回路基板が論理基板180から取り外されたことを検出することができる。

120 共有メモリ 130 キャッシュメモリ

131 不揮発性メモリ 132 キャッシュメモリコントローラ

133 イレース制御回路 134 モードレジスタ

135 基板取り外し検出器 136 キャパシタ

137 コネクタ 138 ピン

140 ディスク制御部 150 接続部

160 管理端末 180 論理基板

181 コネクタ 182 長ピン

183 短ピン 190 電源装置

191 バッテリ 200 情報処理装置

300 ストレージ駆動装置 310 記憶ボリューム

500 SAN 600 ストレージ装置

700 メモリ制御部 710 コマンド/アドレス解析部

720 パス側セレクタ回路 730 メモリ側セレクタ回路

740 パケットバッファ 750 ステータスレジスタ

751 消去データレジスタ

752 消去開始アドレスレジスタ

753 消去終了アドレスレジスタ

754 基板取り外し時消去実行可否レジスタ

755 デステージ可否レジスタ

Claims (13)

- 情報処理装置からデータ入出力要求を受信し、前記データ入出力要求に応じてハードディスクドライブに対してデータの読み書きを行うストレージ制御装置であって、

前記ハードディスクドライブに対して前記読み書きが行われるデータを記憶するキャッシュメモリとして機能する不揮発性メモリを有する回路基板と、前記回路基板が挿抜可能に取り付けられる回路基板装着部とを備え、

前記回路基板は、

前記回路基板が前記回路基板装着部から取り外されたことを示す回路基板取り外し情報を出力する取り外し情報出力回路と、

前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリに記憶されているデータを消去するデータ消去回路と、

を備え、

前記データ消去回路が、前記不揮発性メモリに記憶されている前記データの消去コマンドが送信されてきた場合、前記ハードディスクドライブに未書き込みのデータについて消去する前に前記ハードディスクドライブに書き込むデステージ処理を行うかを判定し、前記デステージ処理を行うと判定した場合、前記ハードディスクドライブに未書き込みの前記データを前記ハードディスクドライブに書き込んでから前記データの消去を開始する、

ことを特徴とするストレージ制御装置。 - 前記データ消去回路は、

前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリの所定の範囲に記憶されているデータを消去すること

を特徴とする請求項1に記載のストレージ制御装置。 - 前記回路基板は、

前記不揮発性メモリのアドレス空間における第1のアドレス及び第2のアドレスを記憶する消去範囲記憶回路を備え、

前記データ消去回路は、

前記第1のアドレスから前記第2のアドレスまでの範囲に記憶されているデータを消去することにより、前記範囲に記憶されているデータを消去すること

を特徴とする請求項2に記載のストレージ制御装置。 - 前記データ消去回路は、

前記不揮発性メモリに記憶されているデータを他のデータに書き換えることにより、前記不揮発性メモリに記憶されているデータを消去すること

を特徴とする請求項1に記載のストレージ制御装置。 - 前記回路基板は、

前記他のデータを記憶する書き換えデータ記憶回路を備え、

前記データ消去回路は、

前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリに記憶されているデータを前記書き換えデータ記憶回路に記憶されている前記他のデータに書き換えることにより、前記不揮発性メモリに記憶されているデータを消去すること

を特徴とする請求項4に記載のストレージ制御装置。 - 前記不揮発性メモリは、

前記不揮発性メモリに記憶されているデータを消去するためのメモリ消去要求信号が入力されると、前記不揮発性メモリに記憶されているデータを消去する機能を備え、

前記データ消去回路は、

前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記メモリ消去要求信号を前記不揮発性メモリに入力することにより、前記不揮発性メモリに記憶されているデータを消去すること

を特徴とする請求項1に記載のストレージ制御装置。 - 情報処理装置からデータ入出力要求を受信し、前記データ入出力要求に応じてハードディスクドライブに対してデータの読み書きを行い、

前記ハードディスクドライブに対して前記読み書きが行われるデータを記憶するキャッシュメモリとして機能する不揮発性メモリを有する回路基板と、前記回路基板が挿抜可能に取り付けられる回路基板装着部とを備え、

前記回路基板は、前記回路基板が前記回路基板装着部から取り外されたことを示す回路基板取り外し情報を出力する取り外し情報出力回路

を備えるストレージ制御装置の制御方法であって、

前記回路基板が、前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリに記憶されているデータを消去し、

前記回路基板が、前記不揮発性メモリに記憶されている前記データの消去コマンドが送信されてきた場合、前記ハードディスクドライブに未書き込みのデータについて消去する前に前記ハードディスクドライブに書き込むデステージ処理を行うかを判定し、前記デステージ処理を行うと判定した場合、前記ハードディスクドライブに未書き込みの前記データを前記ハードディスクドライブに書き込んでから前記データの消去を開始する、

ことを特徴とするストレージ制御装置の制御方法。 - 前記回路基板が、前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリの所定の範囲に記憶されているデータを消去すること

を特徴とする請求項7に記載のストレージ制御装置の制御方法。 - 前記回路基板は、

前記不揮発性メモリのアドレス空間における第1のアドレス及び第2のアドレスを記憶する消去範囲記憶回路を備え、

前記範囲に記憶されているデータの消去は、前記第1のアドレスから前記第2のアドレスまでの範囲に記憶されているデータを消去することにより行われること

を特徴とする請求項8に記載のストレージ制御装置の制御方法。 - 前記不揮発性メモリに記憶されているデータの消去は、前記不揮発性メモリに記憶されているデータを他のデータに書き換えることにより行われること

を特徴とする請求項7に記載のストレージ制御装置の制御方法。 - 前記回路基板は、

前記他のデータを記憶する書き換えデータ記憶回路を備え、

前記不揮発性メモリに記憶されているデータの消去は、前記不揮発性メモリに記憶されているデータを前記書き換えデータ記憶回路に記憶されている前記他のデータに書き換えることにより行われること

を特徴とする請求項10に記載のストレージ制御装置の制御方法。 - 前記不揮発性メモリは、

前記不揮発性メモリに記憶されているデータを消去するためのメモリ消去要求信号が入力されると、前記不揮発性メモリに記憶されているデータを消去する機能を備え、

前記不揮発性メモリに記憶されているデータの消去は、前記メモリ消去要求信号を前記不揮発性メモリに入力することにより行われること

を特徴とする請求項7に記載のストレージ制御装置の制御方法。 - 情報処理装置からデータ入出力要求を受信し、前記データ入出力要求に対応するI/O要求を出力するチャネル制御部が形成された第1の回路基板と、

前記I/O要求が記憶される共有メモリが形成された第2の回路基板と、

前記共有メモリに記憶された前記I/O要求に応じてハードディスクドライブに対してデータの読み書きを行うディスク制御部が形成された第3の回路基板と、

前記チャネル制御部と前記ディスク制御部との間で授受される、前記ハードディスクドライブに記憶されるデータを記憶するキャッシュメモリとして機能する不揮発性メモリを有する第4の回路基板と、

前記第1の回路基板、前記第2の回路基板、前記第3の回路基板、及び前記第4の回路基板がそれぞれ挿抜可能に取り付けられる回路基板装着部と、

を備え、

前記第4の回路基板は、

前記第4の回路基板が前記回路基板装着部から取り外されたことを示す回路基板取り外し情報を出力する取り外し情報出力回路と、

前記回路基板取り外し情報が前記取り外し情報出力回路から出力されると、前記不揮発性メモリに記憶されているデータを消去するデータ消去回路と、

を備え、

前記データ消去回路が、前記不揮発性メモリに記憶されている前記データの消去コマンドが送信されてきた場合、前記ハードディスクドライブに未書き込みのデータについて消去する前に前記ハードディスクドライブに書き込むデステージ処理を行うかを判定し、前記デステージ処理を行うと判定した場合、前記ハードディスクドライブに未書き込みの前記データを前記ハードディスクドライブに書き込んでから前記データの消去を開始する、

ことを特徴とするストレージ制御装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004030825A JP4494031B2 (ja) | 2004-02-06 | 2004-02-06 | ストレージ制御装置、及びストレージ制御装置の制御方法 |

| US10/809,465 US7055001B2 (en) | 2004-02-06 | 2004-03-26 | Storage array controller with a nonvolatile memory as a cache memory and control method of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004030825A JP4494031B2 (ja) | 2004-02-06 | 2004-02-06 | ストレージ制御装置、及びストレージ制御装置の制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005222383A JP2005222383A (ja) | 2005-08-18 |

| JP2005222383A5 JP2005222383A5 (ja) | 2007-02-22 |

| JP4494031B2 true JP4494031B2 (ja) | 2010-06-30 |

Family

ID=34824141

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004030825A Expired - Fee Related JP4494031B2 (ja) | 2004-02-06 | 2004-02-06 | ストレージ制御装置、及びストレージ制御装置の制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7055001B2 (ja) |

| JP (1) | JP4494031B2 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7360010B2 (en) * | 2003-04-14 | 2008-04-15 | Copan Systems, Inc. | Method and apparatus for storage command and data router |

| US7644239B2 (en) | 2004-05-03 | 2010-01-05 | Microsoft Corporation | Non-volatile memory cache performance improvement |

| JP5038589B2 (ja) * | 2004-10-04 | 2012-10-03 | 株式会社日立製作所 | ディスクアレイ装置及びその負荷分散方法 |

| US7490197B2 (en) | 2004-10-21 | 2009-02-10 | Microsoft Corporation | Using external memory devices to improve system performance |

| US8914557B2 (en) | 2005-12-16 | 2014-12-16 | Microsoft Corporation | Optimizing write and wear performance for a memory |

| US7549021B2 (en) * | 2006-02-22 | 2009-06-16 | Seagate Technology Llc | Enhanced data integrity using parallel volatile and non-volatile transfer buffers |

| JP4272227B2 (ja) * | 2006-06-16 | 2009-06-03 | 三洋電機株式会社 | メモリおよび制御装置 |

| US20080186787A1 (en) * | 2007-02-05 | 2008-08-07 | Seiko Epson Corporation | Storage device |

| JP5026102B2 (ja) * | 2007-02-07 | 2012-09-12 | 株式会社日立製作所 | ストレージ制御装置及びデータ管理方法 |

| KR101431480B1 (ko) * | 2008-04-22 | 2014-09-23 | 엘에스아이 코포레이션 | 드라이브 어레이내의 분산 캐시 시스템 |

| JP5062847B2 (ja) * | 2008-07-27 | 2012-10-31 | 株式会社リコー | 画像処理装置 |

| US9032151B2 (en) * | 2008-09-15 | 2015-05-12 | Microsoft Technology Licensing, Llc | Method and system for ensuring reliability of cache data and metadata subsequent to a reboot |

| US7953774B2 (en) | 2008-09-19 | 2011-05-31 | Microsoft Corporation | Aggregation of write traffic to a data store |

| JP5483063B2 (ja) * | 2009-09-01 | 2014-05-07 | 日本電気株式会社 | ストレージ装置、ストレージシステム、及び消去処理方法 |

| JP2013229013A (ja) * | 2012-03-29 | 2013-11-07 | Semiconductor Energy Lab Co Ltd | アレイコントローラ及びストレージシステム |

| US9542399B2 (en) * | 2013-01-08 | 2017-01-10 | Spectra Logic, Corporation | System and method for removable data storage elements provided as cloud based storage system |

| JP5767657B2 (ja) * | 2013-01-30 | 2015-08-19 | レノボ・シンガポール・プライベート・リミテッド | 不揮発性メモリが記憶するデータを保護する方法およびコンピュータ |

| JP6119533B2 (ja) * | 2013-09-27 | 2017-04-26 | 富士通株式会社 | ストレージ装置,ステージング制御方法及びステージング制御プログラム |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0720994A (ja) * | 1993-06-30 | 1995-01-24 | Hitachi Ltd | 記憶システム |

| JPH11175406A (ja) * | 1997-12-16 | 1999-07-02 | Fujitsu Ltd | 情報機器の補助記憶装置 |

| JP2002189635A (ja) * | 2000-12-21 | 2002-07-05 | Nec Corp | 記憶装置 |

| WO2003040932A1 (en) * | 2001-11-08 | 2003-05-15 | Chaparral Network Storage, Inc. | Data mirroring using shared buses |

| JP2003140835A (ja) * | 2001-11-02 | 2003-05-16 | Nec Gumma Ltd | データ記憶装置 |

| JP2003345520A (ja) * | 2002-05-24 | 2003-12-05 | Hitachi Ltd | ディスクアレイ・システム及びディスクアレイ・システムにおけるキャッシュ制御方法 |

| JP2004104581A (ja) * | 2002-09-11 | 2004-04-02 | Canon Inc | 画像形成装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1993006695A1 (en) | 1991-09-23 | 1993-04-01 | Z-Microsystems | Enhanced security system for computing devices |

| US5935244A (en) | 1997-01-21 | 1999-08-10 | Dell Usa, L.P. | Detachable I/O device for computer data security |

| JPH11203201A (ja) | 1998-01-08 | 1999-07-30 | Hitachi Ltd | キャッシュメモリの配置方法およびデータ記憶システム |

| JP3562563B2 (ja) | 1998-06-12 | 2004-09-08 | ティアック株式会社 | 交換型記録媒体を使用するデ−タ蓄積装置 |

| US20030097508A1 (en) * | 2001-11-16 | 2003-05-22 | Aneshansley Nicholas E. | Dynamically configuring processor resources |

| JP4372427B2 (ja) | 2003-01-20 | 2009-11-25 | 株式会社日立製作所 | 記憶デバイス制御装置 |

-

2004

- 2004-02-06 JP JP2004030825A patent/JP4494031B2/ja not_active Expired - Fee Related

- 2004-03-26 US US10/809,465 patent/US7055001B2/en not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0720994A (ja) * | 1993-06-30 | 1995-01-24 | Hitachi Ltd | 記憶システム |

| JPH11175406A (ja) * | 1997-12-16 | 1999-07-02 | Fujitsu Ltd | 情報機器の補助記憶装置 |

| JP2002189635A (ja) * | 2000-12-21 | 2002-07-05 | Nec Corp | 記憶装置 |

| JP2003140835A (ja) * | 2001-11-02 | 2003-05-16 | Nec Gumma Ltd | データ記憶装置 |

| WO2003040932A1 (en) * | 2001-11-08 | 2003-05-15 | Chaparral Network Storage, Inc. | Data mirroring using shared buses |

| JP2005508551A (ja) * | 2001-11-08 | 2005-03-31 | チヤパラル ネツトワーク ストレージ,インコーポレーテツド | 共有バスを用いたデータのミラー化 |

| JP2003345520A (ja) * | 2002-05-24 | 2003-12-05 | Hitachi Ltd | ディスクアレイ・システム及びディスクアレイ・システムにおけるキャッシュ制御方法 |

| JP2004104581A (ja) * | 2002-09-11 | 2004-04-02 | Canon Inc | 画像形成装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7055001B2 (en) | 2006-05-30 |

| JP2005222383A (ja) | 2005-08-18 |

| US20050177680A1 (en) | 2005-08-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4494031B2 (ja) | ストレージ制御装置、及びストレージ制御装置の制御方法 | |

| JP4901316B2 (ja) | ストレージシステム及び記憶制御装置 | |

| JP4688584B2 (ja) | ストレージ装置 | |

| JP5310480B2 (ja) | ストレージ制御装置および方法 | |

| JP7326430B2 (ja) | 不揮発性メモリエクスプレスデバイスのネットワークをサニタイズするときに使用する方法および装置 | |

| JP2007011522A (ja) | データの消去方法、ストレージ・デバイス及び計算機システム | |

| JP6975202B2 (ja) | 瞬断からの回復処理方法及び装置、並びにコンピュータ読み取り可能な記憶媒体 | |

| US20080301774A1 (en) | Information processing apparatus | |

| JP2007265492A (ja) | データ消去機能付きディスク装置 | |

| US20080244173A1 (en) | Storage device using nonvolatile cache memory and control method thereof | |

| JP2007018401A (ja) | 記憶制御装置、記憶制御装置の上位インターフェース制御部及び記憶制御装置の情報保護方法 | |

| JP2008225672A (ja) | 半導体メモリ装置 | |

| US6192448B1 (en) | Structure and method for disk drive sizing using a disk drive controller coupled to a computer system | |

| US20030159012A1 (en) | Back-up system | |

| JP5027805B2 (ja) | メモリコントローラ、不揮発性記憶装置、及び不揮発性記憶装置システム | |

| CN100524239C (zh) | 储存装置的数据保护方法 | |

| JP3794322B2 (ja) | データコピーシステム | |

| JP2005313568A (ja) | 印刷装置、印刷装置におけるデータの消去方法およびプログラムならびに記録媒体 | |

| US11586508B2 (en) | Systems and methods for backing up volatile storage devices | |

| US20220100403A1 (en) | Systems for modular hybrid storage devices | |

| JP4674591B2 (ja) | 補助記憶装置及びそのセキュリティ確保方法とプログラム | |

| JP2001084115A (ja) | 情報記録制御システムおよび情報記録制御方法 | |

| JP2006011751A (ja) | 情報記憶装置及びその制御方法、並びにコンピュータ・プログラム | |

| JP2020038426A (ja) | 記憶デバイス及び記憶デバイスの制御方法 | |

| JP2864751B2 (ja) | ディスク制御装置の不揮発性メモリ管理方式 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061228 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091124 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100406 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100407 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130416 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130416 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140416 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |