JP4447230B2 - 発光装置及びそれを用いた電子機器 - Google Patents

発光装置及びそれを用いた電子機器 Download PDFInfo

- Publication number

- JP4447230B2 JP4447230B2 JP2003052443A JP2003052443A JP4447230B2 JP 4447230 B2 JP4447230 B2 JP 4447230B2 JP 2003052443 A JP2003052443 A JP 2003052443A JP 2003052443 A JP2003052443 A JP 2003052443A JP 4447230 B2 JP4447230 B2 JP 4447230B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- light emitting

- emitting element

- source

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0254—Control of polarity reversal in general, other than for liquid crystal displays

- G09G2310/0256—Control of polarity reversal in general, other than for liquid crystal displays with the purpose of reversing the voltage across a light emitting or modulating element within a pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

Description

【発明の属する技術分野】

本発明は発光装置の技術に関し、より詳しくは発光装置及びその駆動方法に関する。

【0002】

【従来の技術】

近年、画像の表示を行う表示装置の開発が進められている。表示装置としては、液晶素子を用いて画像の表示を行う液晶表示装置が、高画質、薄型、軽量などの利点を活かして、携帯電話の表示画面やパソコンを使用するときの表示装置として幅広く用いられている。

【0003】

一方、自発光素子である発光素子を用いた発光装置の開発も近年進められている。発光装置は、既存の液晶表示装置がもつ利点に加えて、動画表示に適した速い応答速度、低電圧、低消費電力駆動などの特徴を有しているため、新世代の携帯電話や携帯情報端末(PDA)をはじめ、幅広い用途が見込まれ、次世代ディスプレイとして大きく注目されている。

【0004】

発光素子は有機発光ダイオード(Organic Light Emitting Diode : OLED)とも称され、陽極と、陰極と、前記陽極と前記陰極との間に有機化合物層が挟まれた構造を有している。発光素子に流れる電流量と、発光素子の輝度は正比例の関係にあり、発光素子は有機化合物層に流れる電流量に応じた輝度で発光を行う。

【0005】

発光装置において、時間階調方式を採用する場合がある(例えば、特許文献1参照。)。また、発光素子に逆方向バイアスを印加するものもある(例えば、特許文献2参照。)。

【0006】

【特許文献1】

特開2001-5426号公報

【特許文献2】

特開2001-142413号公報

【0007】

【発明が解決しようとする課題】

しかしながら、発光素子は空気中の水分や酸素に弱く、有機化合物層の劣化によって生じる信頼性、耐熱安定性、耐久性などの低さが問題となっている。そこで、一定の期間ごとに発光時とは逆の極性の駆動電圧(逆バイアス電圧)を発光素子に印加することが提案されている。これは、逆の極性の駆動電圧を発光素子に印加すると、発光素子の電流−電圧特性の劣化が改善されるためである。

【0008】

逆の極性の駆動電圧を発光素子に印加するためには、発光素子が有する第1又は第2の電極の電位を変えることが必要となる。そして、第1又は第2の電極の電位を変える最も簡単な方法は、発光素子の対向電位を変えることである。しかし、発光素子の対向電位は全画素で共通な配線に接続されている場合が多く、画素毎、又はライン毎に対向電位を変えることは出来なかった。つまり、発光素子の対向電位を変えたいときには、一度に全画素で行う以外に方法はなく、該対向電位を変えるタイミングは難しかった。従って、発光素子の対向電位を変えることで逆バイアスをかけようとすると、階調表示に影響を及ぼしていた。

【0009】

また、発光素子を用いた発光装置に多階調の画像を表示するときの駆動方法としては、さまざまな方式があるが、そのうちの一つとして電圧入力方式がある。電圧入力方式とは、画素に入力するビデオ信号を駆動用素子のゲート電極に入力して、該駆動用素子を用いて発光素子の輝度を制御する方式を示す。

【0010】

しかしながら、電圧入力方式の場合には、発光素子を駆動する半導体素子はオン電流が大きい多結晶半導体(ポリシリコン)により形成される。しかし、ポリシリコンにより形成されたポリシリコントランジスタは、結晶粒界における欠陥に起因して、その電気的特性にバラツキが生じやすいという問題点を有している。そして、画素を構成するトランジスタのしきい値やオン電流等の特性が画素ごとにばらつくと、同じビデオ信号を入力した場合にも、それに応じてトランジスタのドレイン電流の大きさが異なってくるため、発光素子の輝度がばらついてしまう。さらには、画面上の各画素の発光輝度が均一とならずムラが生じてしまう。

【0011】

そこで本発明は、画素を構成するトランジスタの特性に左右されずに発光素子に流れる電流の大きさを制御することが出来る電流入力方式が適用される発光装置を提供することを課題とする。

【0012】

また、階調表示に影響を及ぼさずに発光素子に逆方向バイアスを印加することで、電流-電圧特性の劣化を改善した発光装置を提供することを課題とする。

【0013】

【課題を解決するための手段】

本発明は、逆バイアス電圧(逆方向バイアス)を発光素子に印加するために、新たに半導体素子を配置する。上記半導体素子とは、トランジスタ又はダイオードに相当する。そして、新たに配置した半導体素子を用いることで、画素毎又はライン毎などの任意の画素毎に逆バイアスを印加することが出来るようにする。

【0014】

より具体的には、上記半導体素子が導通状態になると同時に、発光素子に逆バイアスが印加されるようにする。つまり上記半導体素子が導通状態になると、ある配線と発光素子とが電気的に接続される状態になるようにする。このとき、このある配線の電位を発光素子の対向電位よりも低くしておくことで、上記半導体素子が導通状態になると同時に、発光素子に逆バイアスが印加されるようにする。

【0015】

逆方向バイアスを印加すると、発光素子は必然的に非発光となるが、上記構成を有する本発明は、全画素で一斉に逆方向バイアスを印加する必要がなく、任意の画素に任意のタイミングで逆方向バイアスを印加することができるため、階調表示に影響を及ぼすことはない。

【0016】

また本発明は、発光素子に流れる電流量を制御することにより、トランジスタの特性に左右されない発光装置を提供する。より具体的には、画素内に電流源を配置しておき、前記電流源から供給される信号電流が発光素子に供給されるようにする。そうすることで、画素を構成するトランジスタの特性バラツキに左右されず、一定の値の信号電流を発光素子に供給することが出来る。

【0017】

なお、前記電流源は、少なくとも1つのトランジスタと、前記トランジスタのゲート・ソース間電圧を保持する容量素子を含む。そして電流源は、トランジスタの特性バラツキの影響を受けずに、所定の信号電流を供給する。発光素子の輝度は、両電極間に流れる電流に比例するため、電流源を用いて所定の信号電流を供給し、該発光素子から所望の輝度を得ることが可能な本発明の構成は大変有効である。

【0018】

また従来では、ビデオ信号の電圧をトランジスタのゲート電極に入力することで、発光素子に流れる電流量が決定されていた。しかし本発明では、画素に入力されるビデオ信号は、発光素子に電流を流す場合と、電流を流さない場合を選択するためだけに用いる。その結果、画素を構成するトランジスタの特性バラツキの影響を抑制することが出来る。

【0019】

本発明の発光装置の具体的な構成は、入力されるビデオ信号の同期タイミングに対応する単位フレーム期間内に、複数のサブフレーム期間を設定する第1設定手段と、

前記ビデオ信号を保持する容量手段と、

前記サブフレーム期間毎に、前記ビデオ信号に応じて前記電流源から供給される所定の信号電流を前記発光素子に供給する駆動手段と、

前記フレーム期間の所定の期間に対し、前記発光素子の各々の発光期間が所定の発光期間に達したときに前記発光素子の各々の発光を停止せしめる消去手段と、

前記フレーム期間の所定の期間に対し、前記第1又は前記第2の電極の電位はそのままで、前記発光素子に逆バイアスの電圧が供給される第2設定手段とを有することを特徴とする。

【0020】

なお、前記第1設定手段とは、画素へのビデオ信号の入力を制御する選択用トランジスタに相当する。また前記第1設定手段とは、前記画素を駆動する駆動回路、コントロール回路などにも相当する。さらに前記駆動手段とは、画素における駆動用トランジスタに相当する。前記駆動用トランジスタは、多くの場合においてそのソース端子又はドレイン端子が発光素子の第1又は第2の電極に直接接続されているトランジスタを指す。また前記消去手段とは、発光素子の発光を停止せしめる機能を有し、具体的には消去用トランジスタに相当する。そして発光素子の発光を停止せしめるためには、ビデオ信号を保持する容量素子の電荷を放電するため、消去用トランジスタのソース及びドレインは、容量素子の両電極間を挟んで接続している場合が多い。また第2設定手段とは、発光素子に逆バイアスを印加するときに導通状態になるトランジスタに相当する。

【0021】

第2設定手段が導通状態になると、発光素子の第1及び第2の電極の一方の電極の電位はそのままで、他方の電極は逆バイアス用の配線に接続されて、その電位が変わる。そうすると、発光素子の両電極間には逆方向バイアスが印加される。なお、容量手段は、ビデオ信号を保持するものであり、明示的に設けられる必要はなく、充分な容量が得られるならば、寄生容量や駆動用トランジスタのゲート容量を用いてもよい。また、駆動用トランジスタは、単なるスイッチング機能を有するものであり、該駆動用トランジスタが導通状態になると、電流源から所定の信号電流が供給される。

【0022】

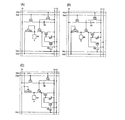

ここで、本発明の発光装置の画素の概略について、図1(A)(B)を用いて説明する。図1(A)には、複数の画素を有する画素部において、i列j行目に配置された画素10を示す。画素10は、信号線(Si)、電源線(Vi)、第1走査線(Gaj)、第2走査線(Gbj)、スイッチング機能を有する選択用スイッチ11、消去用スイッチ12、駆動用素子13、放電用スイッチ14、容量素子15、発光素子16、電流源17を有する。

【0023】

選択用スイッチ11、消去用スイッチ12、放電用スイッチ14には、トランジスタなどのスイッチング機能を有する半導体素子が1個又は複数個用いることが好ましい。選択用スイッチ11は第1走査線(Gaj)から与えられる信号によりオン又はオフが決定され、消去用スイッチ12は第2走査線(Gbj)から与えられる信号によりオン又はオフが決定される。

【0024】

放電用スイッチ14のゲート電極は、ある配線から与えられる信号によりオン又はオフが決定される。また放電用スイッチ14のソース電極はある配線に接続される。放電用スイッチ14の詳しい接続は、実施の形態において後述する。

【0025】

容量素子15は、信号線(Si)を介して画素10に入力される信号を保持する。また容量素子15は、駆動用素子13のゲート・ソース間電圧の保持を行う。

【0026】

そして本発明は、放電用スイッチ14を用いて発光素子16に逆バイアスの電圧を印加するタイミングを制御する。より詳しくは発光素子16が発光していない期間に逆バイアスを印加できるように放電用スイッチ14を用いて制御する。さらに本発明は、画素10に電流源17を設けることにより、所望の電流量を発光素子16に流すことが出来るようにする。そして、画素10を構成するトランジスタの特性バラツキの影響を抑制できるようにする。

【0027】

図1(B)には、図1(A)に示した画素10とは異なる構成を有する画素10を示す。画素10は、信号線(Si)、電源線(Vi)、第1走査線(Gaj)、第2走査線(Gbj)、スイッチング機能を有する選択用スイッチ21、消去用スイッチ22、駆動用素子23、放電用ダイオード24、容量素子25、発光素子26、電流源27を有する。

【0028】

選択用スイッチ21、消去用スイッチ22には、トランジスタなどのスイッチング機能を有する半導体素子が1個又は複数個用いることが好ましい。選択用スイッチ21は第1走査線(Gaj)から与えられる信号によりオン又はオフが決定され、消去用スイッチ22は第2走査線(Gbj)から与えられる信号によりオン又はオフが決定される。

【0029】

放電用ダイオード24の一方の端子は、ある配線に接続される。放電用ダイオード24の詳しい接続は、実施の形態において後述する。なお放電用ダイオード24としては、整流性を有する素子を用いればよい。例えばダイオードの他には、ゲート電極とドレイン電極とを接続したトランジスタが挙げられる。なお本明細書では、ゲート電極とドレイン電極とを接続したトランジスタをダイオード接続したトランジスタと称する。

【0030】

容量素子25は、信号線(Si)を介して画素10に入力される信号を保持する。また容量素子25は、駆動用素子23のゲート・ソース間電圧の保持を行う。

【0031】

そして本発明は、放電用ダイオード24を用いて発光素子26に逆バイアスの電圧を印加するタイミングを制御する。より詳しくは発光素子26が発光していない期間に逆バイアスを印加できるように放電用ダイオード24を用いて制御する。さらに本発明は、画素10に電流源27を設けることにより、所望の電流量を発光素子26に流すことが出来るようにする。そして、画素10を構成するトランジスタの特性バラツキの影響を抑制できるようにする。

【0032】

また、発光装置の駆動方式として、時間階調方式を採用した場合には、発光素子が発光していない期間に逆方向バイアスを印加することで、階調表示に全く影響を及ぼさずに、逆方向バイアスを印加することができる。

【0033】

【発明の実施の形態】

(実施の形態1)

本発明の発光装置の画素の概略を図1(A)(B)を用いて2種類上述したが、本実施の形態では、図1(A)の具体的な画素の構成の例とその動作について図2、図4を用いて説明する。より詳しくは、図1(A)に示した画素10を構成する放電用トランジスタ14のゲート電極の接続を工夫した場合について、図2、図4を用いて説明する。さらに、図2に示した画素10のレイアウトについて図3を用いて説明する。

【0034】

図2(A)において、画素10は、選択用トランジスタ31、消去用トランジスタ32、駆動用トランジスタ33、放電用トランジスタ34、容量素子35、発光素子36、電流源トランジスタ37、設定用トランジスタ38、設定用トランジスタ39、容量素子40を有する。また画素10は、第1走査線(Gaj)〜第4走査線(Gdj)と、信号線(Si)、電源線(Vi)、電流線(Ci)を有する。そして画素10の周囲には、走査線駆動回路、信号線駆動回路、電流源、電源(全て図示せず)などが設けられている。そして、走査線駆動回路から第1走査線(Gaj)〜第4走査線(Gdj)を介して画素10に信号が入力され、信号線駆動回路から信号線(Si)を介して画素10に信号が入力される。

【0035】

選択用トランジスタ31と容量素子35は直列に接続され、信号線(Si)と電源線(Vi)の間に配置されている。選択用トランジスタ31のゲート電極は第1走査線(Gaj)に接続されている。以下、選択用トランジスタ31は、トランジスタ31と表記する。また消去用トランジスタ32のゲート電極は第2走査線(Gbj)に接続され、ソース電極とドレイン電極は、容量素子35の両電極間を介して接続されている。以下、消去用トランジスタ32は、トランジスタ32と表記する。なおトランジスタ31、32は単なるスイッチとして機能するので、導電型は特に限定されない。但しトランジスタ32のゲート電極とトランジスタ34のゲート電極は同じ走査線に接続される場合があるので、そのときには両トランジスタの導電型を同じにすることが好ましい。

【0036】

放電用トランジスタ34、駆動用トランジスタ33、電流源トランジスタ37は直列に接続されて、電源線(Vi)と第4走査線(Gdj)の間に配置されている。放電用トランジスタ34のゲート電極は第2走査線(Gbj)に接続されている。駆動用トランジスタ33のゲート電極は容量素子35の一方の端子に接続され、電流源トランジスタ37のゲート電極は容量素子40の一方の端子に接続されている。以下、放電用トランジスタ34はトランジスタ34と表記し、駆動用トランジスタ33はトランジスタ33と表記し、電流源トランジスタ37はトランジスタ37と表記する。

【0037】

設定用トランジスタ38と設定用トランジスタ39はゲート電極が共通で第3走査線(Gcj)に接続されている。設定用トランジスタ38と容量素子40は直列に接続され、電流線(Ci)と電源線(Vi)との間に配置されている。設定用トランジスタ39と電流源トランジスタ37は直列に接続され、電流線(Ci)と電源線(Vi)との間に配置されている。以下、設定用トランジスタ38、39は、トランジスタ38、39と表記する。そして、トランジスタ38、39の導電型は特に限定されないが、両トランジスタには同じ信号が入力されるので導電型は同じであることが必要である。なお、トランジスタ37〜39及び容量素子40が図1(A)に示した電流源17に相当する。

【0038】

なお図2では、容量素子40の一方の電極はトランジスタ37のゲート、他方の電極は電源線(Vi)に接続されている。しかし、容量素子の他方の電極は、一定の電位をもつ配線に接続されていればよく、例えば接地されていてもよい。

【0039】

次いで、画素10の動作について図2(A)〜(C)を用いて説明する。

【0040】

本実施の形態では、画素10の動作を電流源が所望の電流を流すように設定する動作(以下、設定動作と称する)、発光素子36が発光する動作(以下、発光動作と称する)、容量素子35に保持された電荷を放電する動作(以下、消去動作と称する)及び発光素子36に逆バイアスを印加する動作(以下、逆バイアス印加動作と称する)に分けて説明をする。そして本実施の形態では、設定動作を図2(A)を用いて説明し、発光動作を図2(B)を用いて説明し、消去動作及び逆バイアス印加動作を図2(C)を用いて説明する。

【0041】

まず電流源が所望の電流を流すように設定する動作について、図2(A)を用いて説明する。はじめに、画素10の周囲に設けられた走査線駆動回路(図示せず)から、j行目の第3走査線(Gcj)に入力される信号によって、j行目の第3走査線(Gcj)が選択される。そうすると、第3走査線(Gcj)からトランジスタ38、39のゲート電極にHレベルの信号が入力される。そうすると、nチャネル型のトランジスタ38、39がオンとなる。このとき、第1走査線(Gaj)、第2走査線(Gbj)には信号が入力されず、トランジスタ38、39以外のトランジスタはオフを維持する。

【0042】

トランジスタ38、39がオンした瞬間には、まだ容量素子40には電荷が保持されていないため、トランジスタ37はオフしている。このときは、画素10の周囲に設けられた電源(図示せず)から電源線(Vi)を介して、容量素子40及びトランジスタ38のソース・ドレイン間を介して電流線(Ci)の方向に電流が流れている。

【0043】

その後、徐々に容量素子40に電荷が蓄積され、両電極間に電位差が生じ始める。容量素子40の両電極の電位差がトランジスタ37のしきい値電圧(Vth)以上になると、トランジスタ37がオンする。そうすると、電源線(Vi)からトランジスタ37、39のソース・ドレイン間を介して電流線(Ci)の方向に電流が流れていく。

【0044】

容量素子40においては、その両電極の電位差、つまりトランジスタ37のゲート・ソース間電圧が所望の電圧、つまりトランジスタ37が所定の信号電流Idataを流すことが出来るだけの電圧(Vgs)になるまで電荷の蓄積が続く。

【0045】

そして、容量素子40に対する電荷の蓄積が終了すると、トランジスタ37は電流線(Ci)に流れている電流と等しい電流Idataが流れるようになる。そうすると、画素10に対する信号の書き込み動作が完了し、第3走査線(Gcj)の選択が終了して、トランジスタ38、39はオフする。

【0046】

次いで、発光素子36の発光動作に移る(図2(B))。画素11の周囲に設けられた走査線駆動回路(図示せず)から、j行目の第1走査線(Gaj)に入力される信号によって、j行目の第1走査線(Gaj)が選択される。そして、第1走査線(Gaj)からトランジスタ31のゲート電極にHレベルの信号が入力される。そうすると、nチャネル型のトランジスタ31がオンとなる。このとき、第2走査線(Gbj)、第3走査線(Gcj)には信号が入力されないので、トランジスタ31以外のトランジスタはオフを維持する。そして同時に、画素10の周囲に設けられた信号線駆動回路(図示せず)から、i列目の信号線(Si)を介して画素10にビデオ信号が入力される。前記ビデオ信号は、容量素子35に保持されて、容量素子35の両電極間の電位差はトランジスタ33のしきい値電圧(Vth)以上となると、トランジスタ33はオンする。

【0047】

このとき、容量素子40には先ほど書き込んだ電荷が保持されているため、トランジスタ37はオンしており、電源線(Vi)から信号電流Idataに等しい電流が、トランジスタ37のソース・ドレイン間、トランジスタ33のソース・ドレイン間を流れていき、最後に発光素子36に達する。その結果、発光素子36には所望の電流である信号電流Idataが流れる。なお、トランジスタ37が飽和領域において動作するようにしておけば、トランジスタ37のソース・ドレイン間電圧が変化したとしても、発光素子36に流れる電流は変化することなく流れることが出来る。

【0048】

続いて、画素10の消去・逆バイアス印加動作に移る(図2(C))。画素10の周囲に設けられた走査線駆動回路(図示せず)から、j行目の第2走査線(Gbj)に入力される信号によって、j行目の第2走査線(Gbj)が選択される。そして、第2走査線(Gbj)からトランジスタ32、34のゲート電極にHレベルの信号が入力されて、トランジスタ32、34がオンになる。このとき、第1走査線(Gaj)、第3走査線(Gcj)には信号が入力されないので、トランジスタ32、34以外のトランジスタはオフを維持する。

【0049】

トランジスタ32がオンになると、容量素子35に保持されていた電荷が放出されて、トランジスタ33がオフになる。トランジスタ33がオフになると、発光素子36には電源線(Vi)から電流が供給されなくなるため、発光素子36は発光しなくなる。このとき、第4走査線(Gdj)の電位は、発光素子36の対向電極の電位よりも低いので、発光素子36に逆バイアスを印加することが出来る。なお図2(C)において、発光素子36からトランジスタ34のソース・ドレイン間を介して第4走査線(Gdj)の方向に矢印が図示してある。これは、発光素子36に逆バイアスを印加すると、実際には電流は流れないが、説明を分かりやすくするために点線で示したものである。

【0050】

このようにして画素10は、画素10の周囲に設けられた駆動回路(図示せず)から与えられる信号によって、設定動作(図2(A))と、発光素子36が発光する動作(図2(B))、消去・逆バイアス印加動作(図2(C))を繰り返す。

【0051】

なおデジタル駆動の場合には、容量素子40に保持される電荷は常に同じなので、一旦容量素子40に所定の電荷を設定したらその後はビデオ信号が入力される毎に設定動作を行う必要はない。つまり設定動作、発光動作、消去・逆バイアス印加動作のうち、一旦設定動作を行った後は、該設定動作を省略して発光動作、消去・逆バイアス印加動作を繰り返してもよい。しかし、容量素子40に保持された電荷は時間の経過に伴って放電してしまう場合があるので、それを防ぐようなタイミングで容量素子40に設定動作を行うことは必要である。

【0052】

また図2に示した画素10の場合には、消去動作と逆バイアス印加動作を同時に行っているが、本発明はこれに限定されず、消去動作と逆バイアス印加動作を別々に行ってもよい。そして逆バイアス印加動作は、ビデオ信号が入力される毎に行わなくてもよく、ある一定期間毎に行うようにしてもよい。

【0053】

また、画素10を構成するトランジスタ34の接続の構成は、図2に示した構成に限定されない。例えば図4(A)に示すように、トランジスタ33のゲート電極にトランジスタ34のゲート電極を接続してもよい。そうすると、画素10の消去動作と逆バイアスを印加する動作を同時に行うことが出来る。但しこのときには、トランジスタ33、34が同時にオンにならないように、互いに導電型が異なるように設定することが必要である。これは、トランジスタ33、34が同時にオンになると、電源線(Vi)から発光素子36に電流が供給されてしまい発光素子36に上手く逆バイアスを印加することが出来なくなるからである。

【0054】

また図4(B)に示すように、トランジスタ34のゲート電極を第3走査線(Gcj)に接続して、ソース電極を第4走査線(Gdj)に接続してもよい。この場合には、画素10の設定動作(図2(A)に相当)と、画素10の消去動作及び逆バイアスを印加する動作(図2(C)に相当)を同時に行うことが出来る。そのため、トランジスタ34とトランジスタ38、39は同じ導電型であるように設定することが必要である。

【0055】

なお、図4(A)(B)に示した画素10の動作は、図2を用いて説明した画素10の動作に準ずるので、本実施の形態では省略する。

【0056】

続いて、図2に示した画素10を例に挙げて、そのレイアウト図の一例について図3を用いて説明する。

【0057】

図2と図3(A)の画素10を構成する素子の符号は同じであるので、互いに参照するとよい。図3(A)において、画素10は、選択用トランジスタ31、消去用トランジスタ32、駆動用トランジスタ33、放電用トランジスタ34、容量素子35、発光素子36、電流源トランジスタ37、設定用トランジスタ38、設定用トランジスタ39、容量素子40を有する。また画素10は、第1走査線(Gaj)〜第4走査線(Gdj)と、信号線(Si)、電源線(Vi)、電流線(Ci)を有する。

【0058】

そして、レイアウトした画素10をそのまま回路図で示すと、図3(B)のように示すことが出来る。図3(B)から分かるように、トランジスタ32、34は同じ走査線に接続されているので、直線状に配置している。そして41は画素電極であり、開口部に相当する。そしてその他のトランジスタは、なるべく画素10の右側に配置することで開口率を上げて、且つ画素10の開口部をシンプルな形状にしている。

【0059】

(実施の形態2)

実施の形態1では、図1(A)の放電用トランジスタ14のゲート電極の接続を工夫した場合について説明した。本実施の形態では、図1(A)の放電用トランジスタ14のソース電極の接続を工夫した場合について図5を用いて説明する。

【0060】

図2(A)に示した画素10と、図5(A)〜(D)に示す画素10とは、放電用トランジスタ34(以下、トランジスタ34と表記)の接続が異なる以外は、画素10を構成する素子の数や前記素子の接続の関係は同じであるので、本実施の形態では詳しい説明は省略する。

【0061】

図5(A)〜(D)において、トランジスタ34のゲート電極は、第4走査線(Gdj)に接続されている。そして、図5(A)に示す画素10ではトランジスタ34のソース電極は第1走査線(Gaj)に接続され、図5(B)に示す画素10ではトランジスタ34のソース電極は信号線(Si)に接続されている。図5(C)に示す画素10ではトランジスタ34のソース電極は第3走査線(Gcj)に接続され、図5(D)に示す画素10ではトランジスタ34のソース電極は電流線(Ci)に接続されている。

【0062】

なお画素10を構成するトランジスタ34の接続は、図5(A)〜(D)に示した接続に限定されない。トランジスタ34のゲート電極は、第4走査線(Gdj)ではなく第1走査線(Gaj)〜第3走査線(Gcj)のいずれか一本に接続されていてもよい。また、トランジスタ34のソース電極は第2走査線(Gbj)に接続されていてもよい。さらに、発光素子36の陰極の電位を変動させるのであれば、トランジスタ34のソース電極を電源線(Vi)に接続させてもよい。

【0063】

そして、図5(A)〜(D)に示した画素10の動作は、図2を用いて説明した画素10の動作に準ずるので、本実施の形態では省略する。

【0064】

なお図5(A)〜(D)に示した画素10では、トランジスタ34のゲート電極は、第4走査線(Gdj)に接続されている。従って走査線駆動回路を制御すれば、トランジスタ34はその他のトランジスタと同時に信号は入力されないので、発光素子36に逆バイアスを印加する動作を独立して行うことが出来る。

【0065】

しかし、トランジスタ38、39に信号を与えてオンにするタイミングと、トランジスタ34に信号を与えてオンにするタイミングを同時にすれば、画素10の設定動作と逆バイアスを印加する動作を同時に行うことが出来る。また、トランジスタ32に信号を与えてオンにするタイミングと、トランジスタ34に信号を与えてオンにするタイミングを同時にすれば、画素10の消去動作と逆バイアスを印加する動作を同時に行うことが出来る。このときには、トランジスタ34のゲート電極を第4走査線(Gdj)ではなく第1走査線(Gaj)〜第3走査線(Gcj)のいずれか一つに接続するようにすればよい。しかしながら、トランジスタ34のゲート電極とソース領域とが同じ配線に接続されないように注意する必要がある。

【0066】

なお本実施の形態は、実施の形態1と任意に組み合わせることが可能である。

【0067】

(実施の形態3)

本発明の発光装置の画素の概略を図1(A)(B)を用いて2種類上述したが、本実施の形態では、図1(B)の具体的な画素の構成の例とその動作について図6を用いて説明する。なお図6においては、放電用ダイオード24としてダイオード接続をしたトランジスタを図示している。

【0068】

図2(A)に示した画素10と、図6(A)〜(C)に示す画素10とは、放電用トランジスタ34(以下、トランジスタ34と表記)の接続が異なる以外は、画素10を構成する素子の数や前記素子の接続の関係は同じであるので、本実施の形態では素子の接続の詳しい説明は省略する。

【0069】

図6(A)に示す画素10ではトランジスタ34はnチャネル型であり、該トランジスタ34のゲート電極とドレイン電極とは互いに接続されている。またトランジスタ34のソース電極は第4走査線(Gdj)に接続されている。なお、本発明は図6(A)に示す構成に限定されず、トランジスタ34のソース電極は第4走査線(Gdj)ではなく、第2走査線(Gbj)に接続されていてもよい。

【0070】

図6(B)に示す画素10ではトランジスタ34はpチャネル型であり、該トランジスタ34のゲート電極とドレイン電極とは互いに接続されて第4走査線(Gdj)に接続されている。トランジスタ34のソース電極は発光素子36に接続されている。

【0071】

図6(C)に示す画素10ではトランジスタ34はpチャネル型であり、該トランジスタ34のゲート電極とドレイン電極とは互いに接続されて第2走査線(Gbj)に接続されている。トランジスタ34のソース電極は発光素子36に接続されている。またトランジスタ32をpチャネル型にすることで第4走査線(Gdj)を削除して、トランジスタ32、34のゲート電極を第2走査線(Gbj)に接続している。

【0072】

続いて、図6(A)〜(C)に示した画素10の動作について説明する。なお上述したように、画素10の動作は、画素10の設定動作(図2(A)に相当)、発光動作(図2(B)に相当)、画素10の消去動作(図2(C)に相当)、発光素子36に逆バイアスを印加する動作(図2(C)に相当)の4つの動作に大別できる。そして、上記の設定動作、発光動作、消去動作の3つの動作は、図2を用いて説明した画素10の動作と同じであるので本実施の形態では省略し、逆バイアスを印加する動作のみを説明する。

【0073】

図6(A)に示す画素10では、トランジスタ33がオフのときに発光素子36に逆バイアスを印加する。そして発光素子36に逆バイアスを印加するときには、第4走査線(Gdj)の電位を発光素子36の対向電極の電位よりも低くして発光素子36に逆バイアスを印加する。

【0074】

同様に、図6(B)に示す画素10においても、トランジスタ33がオフのときに発光素子36に逆バイアスを印加する。つまり、第4走査線(Gdj)の電位を発光素子36の対向電極の電位よりも低くして発光素子36に逆バイアスを印加する。また図6(C)に示す画素10の逆バイアスを印加する動作は、図6(B)に示す画素10に準ずるので、ここでは省略する。

【0075】

なお発光素子36に逆バイアスを印加する動作は、画素10の設定動作と同時に行ってもよい。そのため、例えば図6(C)に示す画素10において、トランジスタ32、34、38、39が同時にオンになるように設定してもよい。

【0076】

なお本実施の形態は、実施の形態1、2と任意に組み合わせることが可能である。

【0077】

(実施の形態4)

本実施の形態では、実施の形態1〜3とは異なる実施の形態について図7を用いて説明する。

【0078】

図7に示す画素10は、図1(A)で示す画素10において、放電用トランジスタ14が設けられていない場合を示している。図7に示す画素10が有するその他の素子と、該素子の接続の構成は、実施の形態1で上述した通りであるので、本実施の形態では省略する。

【0079】

そして、図7に示す画素10に逆バイアスを印加するときは、発光素子36の対向電源42の電位を高くする。そうすると、発光素子36に逆バイアスを印加することが出来る。

【0080】

なお本実施の形態は、実施の形態1〜3と任意に組み合わせることが可能である。

【0081】

(実施の形態5)

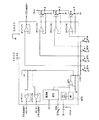

本実施の形態では、本発明の発光装置の構成について図8を用いて説明する。

【0082】

本発明の発光装置は、基板1801上に、複数の画素がマトリクス状に配置された画素部1802を有し、画素部1802の周辺には、信号線駆動回路1803、第1の走査線駆動回路1804及び第2の走査線駆動回路1805を有する。なお画素部1802が有する複数の画素とは、実施の形態1〜実施の形態4において上述した画素10に相当する。図8(A)においては、信号線駆動回路1803と、2組の走査線駆動回路1804、1805を有しているが、本発明はこれに限定されず、駆動回路の個数は画素の構成に応じて任意に設計することができる。また信号線駆動回路1803と、第1の走査線駆動回路1804及び第2の走査線駆動回路1805には、FPC1806を介して外部より信号が供給される。

【0083】

第1の走査線駆動回路1804及び第2の走査線駆動回路1805の構成について図8(B)を用いて説明する。第1の走査線駆動回路1804及び第2の走査線駆動回路1805は、シフトレジスタ1821、バッファ1822を有する。動作を簡単に説明すると、シフトレジスタ1821は、クロック信号(G-CLK)、スタートパルス(S-SP)及びクロック反転信号(G-CLKb)に従って、順次サンプリングパルスを出力する。その後バッファ1822で増幅されたサンプリングパルスは、走査線に入力されて1行ずつ選択状態にしていく。そして選択された走査線によって、制御される画素には、順に信号線から信号電流Idataが書き込まれる。

【0084】

なおシフトレジスタ1821と、バッファ1822の間にはレベルシフタ回路を配置した構成にしてもよい。レベルシフタ回路を配置することによって、電圧振幅を大きくすることが出来る。

【0085】

次いで信号線駆動回路1803の構成について図8(C)(D)を用いて説明する。図8(C)に示す信号線駆動回路1803はシフトレジスタ1811、バッファ1812、サンプリング回路1813、定電流回路1814を有する。動作を簡単に説明すると、シフトレジスタ1811は、クロック信号(G-CLK)、スタートパルス(S-SP)及びクロック反転信号(G-CLKb)に従って、順次サンプリングパルスを出力する。その後バッファ1812で増幅されたサンプリングパルスは、サンプリング回路1813に入力される。サンプリング回路にはビデオ信号が入力されており、サンプリングパルスが入力されるタイミングに従って、定電流回路1814にビデオ信号が入力される。

【0086】

次いで図8(C)とは異なる構成の信号線駆動回路を図8(D)を用いて説明する。図8(D)に示す信号線駆動回路はシフトレジスタ1831、第1のラッチ回路1832、第2のラッチ回路1833、定電流回路1834を有する。

【0087】

動作を簡単に説明するとシフトレジスタ1831は、フリップフロップ回路(FF)等を複数列用いて構成され、クロック信号(S-CLK)、スタートパルス(S-SP)、クロック反転信号(S-CLKb)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

【0088】

シフトレジスタ1831より出力されたサンプリングパルスは、第1のラッチ回路1832に入力される。第1のラッチ回路1832には、デジタルビデオ信号が入力されており、サンプリングパルスが入力されるタイミングに従って、各列でビデオ信号を保持していく。

【0089】

第1のラッチ回路1832において、最終列までビデオ信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路1833にラッチパルスが入力され、第1のラッチ回路1832に保持されていたビデオ信号は、一斉に第2のラッチ回路1833に転送される。すると、第2のラッチ回路1833に保持されたビデオ信号は、1行分が同時に定電流回路1834に入力されることになる。

【0090】

第2のラッチ回路1833に保持されたビデオ信号が定電流回路1834に入力されている間、シフトレジスタ1831においては再びサンプリングパルスが出力される。以後この動作を繰り返し、1フレーム分のビデオ信号の処理を行う。なお定電流回路1834は、デジタル信号をアナログ信号に変換する役割を持つ場合もある。

【0091】

なお本実施の形態は、実施の形態1〜4と任意に組み合わせることが可能である。

【0092】

(実施の形態6)

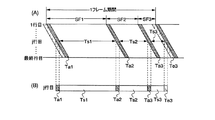

上述した本発明の発光装置をデジタル駆動する場合には、多階調の画像を表現するためにデジタル階調方式と面積階調方式とを組み合わせた方式やデジタル階調方式と時間階調方式とを組み合わせた方式(以下時間階調方式と表記)が提案されている。そして本実施の形態では、上述した時間階調方式について図9(A)(B)を用いて説明する。なお図9(A)は、縦軸は走査線、横軸は時間のときのタイミングチャートを示し、図9(B)はj行目の走査線に注目したときのタイミングチャートを示している。

【0093】

通常、液晶表示装置や発光装置等の表示装置においては、フレーム周波数は60Hz程度である。つまり、1秒間に60回程度の画面の描画が行われる。これにより、人間の眼にフリッカ(画面のちらつき)を感じさせないようにすることが出来る。このとき、画面の描画を1回行う期間を1フレーム期間と呼ぶ。

【0094】

本実施の形態では一例として、特許文献1にて公開されている時間階調方式を説明する。時間階調方式では、1フレーム期間を複数のサブフレーム期間に分割する。このときの分割数は、階調ビット数に等しい場合が多く、ここでは簡単のために、分割数が階調ビット数に等しい場合を示す。つまり本実施の形態では3ビット階調であるので、3つのサブフレーム期間SF1〜SF3に分割している例を示す。

【0095】

各サブフレーム期間は、書き込み(アドレス)期間Taと、発光(サステイン)期間Tsを有する。アドレス期間とは、画素にビデオ信号を書き込む期間であり、各サブフレーム期間での長さは等しい。サステイン期間とは、アドレス期間において画素に書き込まれたビデオ信号に基づいて発光素子が発光する期間である。このとき、発光(サステイン)SF1〜SF3は、その長さの比をTs1:Ts2:Ts3=4:2:1としている。つまり、nビット階調を表現する際は、n個のサステイン期間の長さの比は、2(n-1):2(n-2):・・・:21:20としている。そして、どのサステイン期間で発光素子が発光するかによって、1フレーム期間あたりに、各画素が発光する期間の長さが決定し、これによって階調表現を行う。

【0096】

つまり、サステイン期間Ts1〜Ts3のそれぞれにおいて、発光、非発光のいずれかの状態をとることによって、その合計発光時間の長短を利用して、輝度0%、14%、28%、43%、57%、71%、86%、100%の8階調を表現することが出来る。Ts1が発光し、Ts2、Ts3が発光しない場合、その輝度は57%であり、Ts1とTs3が発光し、Ts2が発光しない場合、その輝度は71%となる。つまり時間階調方式の場合は、100%の輝度で、合計発光時間のうち71%の長さの時間で発光することによって同様の階調を表現する。

【0097】

また図9において、サブフレーム期間SF3は消去期間Te3を有する。消去期間とは、画素に書き込まれたビデオ信号を消去してリセットする期間に相当する。そして例えば図2(A)〜(C)に示す画素10では、消去と逆バイアスを同じタイミングで行っている。つまり、前記画素10では、消去期間Teにおいて消去動作と逆バイアス印加動作を同時に行っている。

【0098】

なお、表示階調数を増やしたい場合は、サブフレーム期間の分割数を増やせば良い。また、サブフレーム期間の順序は、図9(A)(B)に示すように、必ずしも上位ビットから下位ビットといった順序である必要はなく、1フレーム期間中、ランダムに並んでいても良い。さらに各フレーム期間内で、その順序が変化しても良い。

【0099】

本実施の形態は、実施の形態1〜実施の形態5と任意に組み合わせることが可能である。

【0100】

(実施の形態7)

本実施の形態では、本発明の発光装置の断面構造について、図10を用いて簡単に説明する。なお説明を簡単にするために、図10には駆動用TFT507と発光素子の断面構造のみを図示する。

【0101】

図10において、500は絶縁表面を有する基板である。基板500上には、駆動用TFT507が設けられている。そして、駆動用TFT507が有する活性層に設けられた不純物領域に接続するように配線が設けられ、前記配線と接続するように画素電極509が設けられている。画素電極509上には有機導電体膜522が設けられ、該有機導電体膜522上には有機薄膜(発光層)523が設けられている。有機薄膜(発光層)523上には、対向電極524が設けられている。

【0102】

そして、画素電極509、有機導電体膜522、有機薄膜(発光層)523及び対向電極524との積層体が発光素子に相当する。発光素子から発せられる光は、基板500に向かって発せられる場合と、基板500と反対方向に発せられる場合がある。前者は下面出射と称され、後者は上面出射と称されており、下面出射の場合は、画素電極509が陽極に相当し対向電極524が陰極に相当する。また上面出射の場合は、画素電極509が陰極に相当し対向電極524が陽極に相当する。

【0103】

なお有機薄膜(発光層)523には、赤、青、緑、白等の光を発する材料を適宜用いることが出来る。そして、白色の光を発する材料を用いて有機薄膜(発光層)523を構成するときには、画素電極509又は対向電極524を透明導電膜で形成し、それに対向する面にカラーフィルターの着色層を配置するとよい。そうすると、白色の材料を用いてもカラー表示を実現することが出来る。

【0104】

本実施の形態は、実施の形態1〜実施の形態6と任意に組み合わせることが可能である。

【0105】

(実施の形態8)

本発明の発光装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図11に示す。

【0106】

図11(A)は発光装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明は表示部2003に用いることができる。また本発明により、図11(A)に示す発光装置が完成される。発光装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。なお、発光装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0107】

図11(B)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明は、表示部2102に用いることができる。また本発明により、図11(B)に示すデジタルスチルカメラが完成される。

【0108】

図11(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明は、表示部2203に用いることができる。また本発明により、図11(C)に示す発光装置が完成される。

【0109】

図11(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明は、表示部2302に用いることができる。また本発明により、図11(D)に示すモバイルコンピュータが完成される。

【0110】

図11(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読み込み部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示するが、本発明は表示部A、B2403、2404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。また本発明により図11(E)に示す画像表示装置が完成される。

【0111】

図11(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明は、表示部2502に用いることができる。また本発明により、図11(F)に示すゴーグル型ディスプレイが完成される。

【0112】

図11(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609等を含む。本発明は、表示部2602に用いることができる。また本発明により、図11(G)に示すビデオカメラが完成される。

【0113】

図11(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。本発明は、表示部2703に用いることができる。なお、表示部2703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。また本発明により、図11(H)に示す携帯電話が完成される。

【0114】

なお、将来的に発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

【0115】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。発光材料の応答速度は非常に高いため、発光装置は動画表示に好ましい。

【0116】

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

【0117】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また本実施の形態の電子機器は、実施の形態1〜7に示したいずれの構成の発光装置を用いても良い。

【0118】

(実施の形態9)

形態8において示した電子機器には、発光素子が封止された状態にあるパネルに、コントローラ、電源回路等を含むICが実装された状態にあるモジュールが搭載されている。モジュールとパネルは、共に表示装置の一形態に相当する。ここでは、モジュールの具体的な構成について説明する。

【0119】

図12(A)に、コントローラ801及び電源回路802がパネル800に実装されたモジュールの外観図を示す。パネル800には、発光素子が各画素に設けられた画素部803と、前記画素部803が有する画素を選択する走査線駆動回路804と、選択された画素にビデオ信号を供給する信号線駆動回路805とが設けられている。またプリント基板806にはコントローラ801、電源回路802が設けられ、コントローラ801又は電源回路802から出力された各種信号及び電源電圧は、FPC807を介してパネル800の画素部803、走査線駆動回路804及び信号線駆動回路805に供給される。そしてプリント基板806への電源電圧及び各種信号は、複数の入力端子が配置されたインターフェース(I/F)部808を介して供給される。

【0120】

なお、本実施例ではパネル800にプリント基板806がFPCを用いて実装されているが、必ずしもこの構成に限定されない。COG(Chip on Glass)方式を用い、コントローラ801、電源回路802をパネル800に直接実装させるようにしても良い。また、プリント基板806において、引きまわしの配線間に形成される容量や配線自体が有する抵抗等によって、電源電圧や信号にノイズがのったり、信号の立ち上がりが鈍ったりすることがある。そこで、プリント基板806にコンデンサ、バッファ等の各種素子を設けて、電源電圧や信号にノイズがのったり、信号の立ち上がりが鈍ったりするのを防ぐようにしても良い。

【0121】

図12(B)に、プリント基板806の構成をブロック図で示す。インターフェース808に供給された各種信号と電源電圧は、コントローラ801と、電源電圧802に供給される。コントローラ801は、アナログインターフェイス回路809、位相ロックドループ(PLL:Phase Locked Loop)810、制御信号生成回路811及びSRAM(Static Random Access Memory)812、813とを有する。なおここではSRAMを用いているが、SRAMの代わりに、SDRAMや、高速でデータの書き込みや読み出しが可能であるならばDRAM(Dynamic Random Access Memory)も用いることが可能である。

【0122】

インターフェース808を介して供給されたアナログビデオ信号は、アナログインターフェイス回路809においてA/D変換及びパラレル-シリアル変換され、R、G、Bの各色に対応するデジタルビデオ信号として制御信号生成回路811に入力される。また、インターフェース808を介して供給された各種信号を基に、アナログインターフェイス回路809においてHsync信号、Vsync信号、クロック信号CLKなどが生成され、制御信号生成回路811に入力される。インターフェース808に直接デジタルビデオ信号が入力される時は、アナログインターフェイス回路809は配置しなくてもよい。

【0123】

位相ロックドループ810は、インターフェース808を介して供給される各種信号の周波数と制御信号生成回路811の動作周波数の位相とを合わせる機能を有する。制御信号生成回路811の動作周波数は、インターフェース808を介して供給された各種信号の周波数と必ずしも同じではないが、互いに同期するように制御信号生成回路811の動作周波数を位相ロックドループ810において調整する。

【0124】

制御信号生成回路811に入力されたビデオ信号は、一旦SRAM812、813に書き込まれ、保持される。制御信号生成回路811では、SRAM812に保持されている全ビットのビデオ信号のうち、全画素に対応するビデオ信号を1ビット分づつ読み出し、パネル800の信号線駆動回路805に供給する。制御信号生成回路811は、各ビットの発光素子が発光する期間に関する情報を、パネル800の走査線駆動回路804に供給する。電源回路802は、所定の電源電圧をパネル800の信号線駆動回路805、走査線駆動回路804及び画素部803に供給する。

【0125】

次いで、電源回路802の構成について、図13を用いて説明する。電源回路802は、4つのスイッチングレギュレータコントロール860を用いたスイッチングレギュレータ854とシリーズレギュレータ855とからなる。一般的にスイッチングレギュレータは、シリーズレギュレータに比べて小型、軽量であり、降圧だけでなく昇圧や正負反転することも可能である。一方シリーズレギュレータは、降圧のみに用いられるが、スイッチングレギュレータに比べて出力電圧の精度は良く、リプルやノイズはほとんど発生しない。本実施例の電源回路802では、両者を組み合わせて用いる。

【0126】

図13に示すスイッチングレギュレータ854は、スイッチングレギュレータコントロール(SWR)860、アテニュエイター(減衰器:ATT)861、トランス(T)862、インダクター(L)863、基準電源(Vref)864、発振回路(OSC)865、ダイオード866、バイポーラトランジスタ867、可変抵抗868及び容量869を有する。スイッチングレギュレータ854において外部のLiイオン電池(3.6V)等の電圧が変換されると、陰極に与えられる電源電圧と、スイッチングレギュレータ854に供給される電源電圧が生成される。

【0127】

シリーズレギュレータ855は、バンドギャップ回路(BG)870、アンプ871、オペアンプ1〜6、電流源873、可変抵抗874及びバイポーラトランジスタ875を有し、スイッチングレギュレータ854において生成された電源電圧が供給されている。シリーズレギュレータ855では、スイッチングレギュレータ854において生成された電源電圧を用い、バンドギャップ回路870において生成された一定の電圧に基づいて、各色の発光素子の陽極に電流を供給するための配線(電流供給線)に与える直流の電源電圧を生成する。

【0128】

なお電流源873は、ビデオ信号の電流が画素に書き込まれる駆動方式の場合に用いる。この場合、電流源873において生成された電流は、パネル800の信号線駆動回路805に供給される。なお、ビデオ信号の電圧が画素に書き込まれる駆動方式の場合には、電流源873は必ずしも設ける必要はない。

【0129】

次いで、電源回路802の構成要素であるシリーズレギュレータ855における動作について、図14を用いて簡単に説明する。バンドギャップ回路870では基準電圧を発生し、その基準電圧はアンプ871で増幅され、ここでは10Vの電源を作成する。また、バンドギャップ回路870で生成された電圧は、電流源873にも使用される。

なおバンドギャップ回路870は外部のON/OFF端子で制御される。これは主に電源立ち上がり時などに、スイッチングレギュレータ854から供給される電圧が安定していない場合があり、そのまま使うとバンドギャップ回路870から所望の信号を得ることが困難であるために配置するものであり、ON/OFF端子によりディレイを持たせてこのような現象を抑制する。

【0130】

オペアンプ1はアンプ871から供給される+10Vの電圧を内部抵抗で+5Vに分圧したものを供給し、バッファとして機能する。オペアンプ2はアンプ871から供給される+10Vの電圧を内部抵抗で+8Vにしたものを供給し、バッファとして機能する。オペアンプ3はアンプ871から供給される+10Vの電圧を外部可変抵抗で分圧したものを供給し、バッファとして機能する。オペアンプ4〜6はアンプ871から供給される+10Vの電圧を外部可変抵抗で分圧したものを供給し、バッファとして機能する。なお、オペアンプ4〜6は出力電流量が多く必要なため、最終出力段にはトランジスタ875を用いる。電流源873はバンドギャップ回路870で発生した基準電圧を外部抵抗で電流に変換し、内部のカレントミラーで反転して出力する。この電流源873は温度変化により供給する電流量が左右される場合があるため、温度変化は小さく抑制する必要がある。本構成では、シリーズレギュレータ855は、スイッチングレギュレータ854で構成された+12Vの電源により、6つの直流電源を構成している。

【0131】

次いで、電源回路802の構成要素であるスイッチングレギュレータ854における構成と動作について、図15を用いて簡単に説明する。スイッチングレギュレータコントロール(SWR)860は、誤差アンプ1〜4、コンパレータ1〜4及び出力回路1〜4から構成される。ATT861は抵抗890、891から構成される。誤差アンプ1〜4はスイッチングレギュレータの出力電圧を検出する。誤差アンプ1〜4は、電圧利得が固定しており、システムに対して安定した位相補償ができる。コンパレータ1〜4は1つの反転入力と2つの非反転入力をもつ電圧比較器で、入力電圧に応じて出力パルスのオン時間をコントロールする電圧-パルス幅変換器である。上記以外のスイッチングレギュレータ854の構成要素は、上述したので省略する。

【0132】

スイッチングレギュレータ854では、トランジスタ867の動作がオンかオフかのどちらかのモードで常に動作をしている。このモードの時間の比率を変えることによって、直流出力電圧を安定化させる。従って、トランジスタ867の電力損失は少なく、電力変換効率のよい電源となる。しかしながら、オン/オフのスイッチング周波数は高周波数であるため、トランス862は小型化できる。ここでは、スイッチングレギュレータ854は、+3.6Vの電源を入力し、その電圧を昇圧して6つの直流電源を構成する。その出力電圧は、+12V、−2V、+8V、−12V、+5V、−3Vとなる。そのうち、+12Vと−2V、+5Vと−3Vは同一の回路から発生させる。

【0133】

次いで、ON/OFF端子とバンドギャップ回路870の構成について、図16を用いて説明する。バンドギャップ回路870はトランジスタ892〜899、抵抗900〜903から構成される。出力端子は、アンプ871に接続される。図16の構成を有するバンドギャップ回路870は、基準電圧を発生する機能を有する。

続いて、シリーズレギュレータ855の構成要素であるアンプ(DCアンプ)871の構成について、図17を用いて説明する。アンプ871はトランジスタ905〜915、抵抗916〜920、容量体922を有する。入力端子にはバンドギャップ回路870から信号が供給される。出力端子から出力される信号は、オペアンプ1〜6に供給される。

オペアンプ1〜3の構成について図18を用いて説明する。オペアンプ1〜3は、トランジスタ925〜935、940、抵抗936〜939、41、容量素子942を有する。入力端子にはバンドキャップ回路870から信号が供給される。出力端子から出力される信号はパネル800に供給される。

オペアンプ4〜6の構成について図19を用いて説明する。オペアンプ4〜6は、トランジスタ945〜955、960、抵抗956〜959、961、962、容量素子962を有する。入力端子にはバンドキャップ回路870から信号が供給される。出力端子から出力される信号は、各色の発光素子の陽極に電流を供給するための配線(電流供給線)に与える。

電流源873の構成について図20を用いて説明する。電流源873は、トランジスタ965〜973、抵抗974〜980、容量素子981、982を有する。入力端子にはバンドギャップ回路870から信号が供給される。

【0134】

上記構成を有する電源回路802とコントローラ801がパネル800に実装され、本発明の一実施形態であるモジュールが完成する。

【0135】

【実施例】

(実施例1)

本実施の形態においては、有機化合物層として高分子化合物を適用し、さらに陽極と発光層との間に導電性高分子化合物からなるバッファ層を設けた自発光素子において、直流駆動(常に順方向バイアスを印加)と、交流駆動(順方向バイアスと逆方向バイアスを一定周期で交互に印加)を行った際の輝度劣化について測定を行った結果について述べる。

【0136】

図21(A)(B)は、順方向バイアス:3.7V、逆方向バイアス:1.7V、デューティ50%、交流周波数60Hzにおいて交流駆動を行った際の信頼性試験の結果を示している。初期輝度は約400cd/cm2であった。比較用に、直流駆動(順方向バイアス:3.65V)を行った際の信頼性試験の結果も同時に示した。その結果、直流駆動においては、400時間程度で輝度が半減したのに対し、交流駆動においては、約700時間経過後も、半減には至らなかった。

【0137】

図21(C)(D)は、順方向バイアス:3.8V、逆方向バイアス:1.7V、デューティ50%、交流周波数600Hzにおいて交流駆動を行った際の信頼性試験の結果を示している。初期輝度は約300cd/cm2であった。比較用に、直流駆動(順方向バイアス:3.65V)を行ったさいの信頼性試験の結果も同時に示した。結果、直流駆動においては、500時間程度で輝度が半減したのに対し、交流駆動においては、約700時間経過後も、初期輝度の60%程度を保持していた。

【0138】

以上の結果より、交流駆動を行った自発光素子は、直流駆動を行った自発光素子よりも信頼性が高いことが分かる。

【0139】

【発明の効果】

本発明は、発光素子に一定の期間ごとに発光時とは逆の極性の駆動電圧をかけることによって、発光素子の電流−電圧特性の劣化が改善されることを用いた発光装置を提供することが出来る。さらに本発明は、発光素子に流れる電流量を制御することにより、トランジスタの特性に左右されない発光装置を提供することが出来る。

【0140】

また、階調表示に影響を及ぼさずに発光素子に逆方向バイアスを印加することで、電流-電圧特性の劣化を改善した発光装置を提供することが出来る。

【図面の簡単な説明】

【図1】 本発明の発光装置の画素を示す図。

【図2】 本発明の発光装置の画素を示す図。

【図3】 本発明の発光装置の画素のレイアウト図。

【図4】 本発明の発光装置の画素を示す図。

【図5】 本発明の発光装置の画素を示す図。

【図6】 本発明の発光装置の画素を示す図。

【図7】 本発明の発光装置の画素を示す図。

【図8】 本発明の発光装置の全体図。

【図9】 本発明の発光装置の駆動方法を説明する図。

【図10】 本発明の発光装置の断面構造を示す図。

【図11】 本発明が適用される電子機器の図。

【図12】 モジュールを示す図。

【図13】 電源回路を示す図。

【図14】 シリーズレギュレータを示す図。

【図15】 スイッチングレギュレータを示す図。

【図16】 バンドギャップ回路を示す図。

【図17】 DCアンプを示す図。

【図18】 オペアンプを示す図。

【図19】 オペアンプを示す図。

【図20】 電流源を示す図。

【図21】 発光素子の輝度と時間の関係を示す図。

Claims (9)

- 発光素子、前記発光素子に電流を供給する電流源、第1のトランジスタ、第2のトランジスタ、及び第3のトランジスタが設けられた画素を有し、

前記発光素子の第1の電極は、前記第1のトランジスタのソース又はドレインの一方と前記第2のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記電流源に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、配線に電気的に接続され、

前記第3のトランジスタのゲートは走査線に電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は信号線に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は前記第1のトランジスタのゲートに電気的に接続され、

前記発光素子の第2の電極と前記配線の電位差は、前記発光素子に逆方向バイアスが印加される電位差であることを特徴とする発光装置。 - 発光素子、前記発光素子に電流を供給する電流源、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタが設けられた画素を有し、

前記発光素子の第1の電極は、前記第1のトランジスタのソース又はドレインの一方と前記第2のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記電流源に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、配線に電気的に接続され、

前記第3のトランジスタのゲートは第1の走査線に電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は信号線に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は前記第1のトランジスタのゲートと前記第4のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第4のトランジスタのゲートは第2の走査線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は電源線に電気的に接続され、

前記発光素子の第2の電極と前記配線の電位差は、前記発光素子に逆方向バイアスが印加される電位差であることを特徴とする発光装置。 - 発光素子、前記発光素子に電流を供給する電流源、第1のトランジスタ、第2のトランジスタ、及びダイオードが設けられた画素を有し、

前記発光素子の第1の電極は、前記第1のトランジスタのソース又はドレインの一方と前記ダイオードの一方の端子に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記電流源に電気的に接続され、

前記ダイオードの他方の端子は、配線に電気的に接続され、

前記第2のトランジスタのゲートは走査線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は信号線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は前記第1のトランジスタのゲートに電気的に接続され、

前記発光素子の第2の電極と前記配線の電位差は、前記発光素子に逆方向バイアスが印加される電位差であることを特徴とする発光装置。 - 発光素子、前記発光素子に電流を供給する電流源、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及びダイオードが設けられた画素を有し、

前記発光素子の第1の電極は、前記第1のトランジスタのソース又はドレインの一方と前記ダイオードの一方の端子に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記電流源に電気的に接続され、

前記ダイオードの他方の端子は、配線に電気的に接続され、

前記第2のトランジスタのゲートは第1の走査線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は信号線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は前記第1のトランジスタのゲートと前記第3のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第3のトランジスタのゲートは第2の走査線に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は電源線に電気的に接続され、

前記発光素子の第2の電極と前記配線の電位差は、前記発光素子に逆方向バイアスが印加される電位差であることを特徴とする発光装置。 - 請求項1乃至請求項4のいずれか一項において、

前記電流源は、容量素子と、少なくとも1つのトランジスタとを有することを特徴とする発光装置。 - 請求項1乃至請求項5のいずれか一項において、

前記画素と同じ基板上に設けられた駆動回路を有することを特徴とする発光装置。 - 請求項1乃至請求項5のいずれか一項において、

前記画素と同じ基板上に設けられた駆動回路を有し、

前記駆動回路は、定電流回路を有することを特徴とする発光装置。 - 請求項1乃至請求項7のいずれか一項において、

前記発光素子は、有機発光ダイオードであることを特徴とする発光装置。 - 請求項1乃至請求項8のいずれか一項に記載の前記発光装置を用いた電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003052443A JP4447230B2 (ja) | 2002-02-28 | 2003-02-28 | 発光装置及びそれを用いた電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002055063 | 2002-02-28 | ||

| JP2002228952 | 2002-08-06 | ||

| JP2003052443A JP4447230B2 (ja) | 2002-02-28 | 2003-02-28 | 発光装置及びそれを用いた電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004126501A JP2004126501A (ja) | 2004-04-22 |

| JP2004126501A5 JP2004126501A5 (ja) | 2006-04-06 |

| JP4447230B2 true JP4447230B2 (ja) | 2010-04-07 |

Family

ID=32303198

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003052443A Expired - Fee Related JP4447230B2 (ja) | 2002-02-28 | 2003-02-28 | 発光装置及びそれを用いた電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4447230B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7173377B2 (en) * | 2004-05-24 | 2007-02-06 | Samsung Sdi Co., Ltd. | Light emission device and power supply therefor |

| US7462897B2 (en) | 2005-01-31 | 2008-12-09 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and electronic device |

| JP4462081B2 (ja) * | 2005-03-18 | 2010-05-12 | セイコーエプソン株式会社 | 有機el装置及びその駆動方法並びに電子機器 |

| JP2007003706A (ja) * | 2005-06-22 | 2007-01-11 | Sony Corp | 画素回路、表示装置、並びに画素回路の駆動方法 |

| JP2007333913A (ja) * | 2006-06-14 | 2007-12-27 | Sony Corp | 表示装置 |

| JP5249325B2 (ja) * | 2008-05-29 | 2013-07-31 | パナソニック株式会社 | 表示装置およびその駆動方法 |

| KR101087749B1 (ko) | 2008-12-08 | 2011-11-30 | 한양대학교 산학협력단 | 전류 감지기 및 이를 포함하는 발광 다이오드의 구동 장치 |

| JP6314902B2 (ja) | 2015-04-30 | 2018-04-25 | 日亜化学工業株式会社 | 表示装置及び点灯制御回路並びに表示装置の点灯駆動方法 |

-

2003

- 2003-02-28 JP JP2003052443A patent/JP4447230B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004126501A (ja) | 2004-04-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7042162B2 (en) | Light emitting device | |

| JP5063769B2 (ja) | 表示装置 | |

| JP5427844B2 (ja) | 表示装置 | |

| JP4823477B2 (ja) | 表示装置及びその駆動方法 | |

| JP4916642B2 (ja) | 表示装置及びその制御方法 | |

| JP4628447B2 (ja) | 半導体装置 | |

| JP4244617B2 (ja) | 電気光学装置、電気光学装置の駆動方法 | |

| JP2003330419A (ja) | 表示装置 | |

| US8593381B2 (en) | Method of driving light-emitting device | |

| JP2005134435A (ja) | 画像表示装置 | |

| JPWO2002077958A1 (ja) | アクティブマトリクス型発光素子の駆動回路 | |

| TW200534217A (en) | Data line driving circuit, electro-optic device, and electronic apparatus | |

| US7961160B2 (en) | Display device, a driving method of a display device, and a semiconductor integrated circuit incorporated in a display device | |

| JP4447230B2 (ja) | 発光装置及びそれを用いた電子機器 | |

| JP4588300B2 (ja) | 半導体装置、電子機器 | |

| JP4198483B2 (ja) | 表示装置、電子機器 | |

| JP4467900B2 (ja) | 発光装置の駆動方法 | |

| JP4889926B2 (ja) | 表示装置、及びその駆動方法 | |

| JP4869688B2 (ja) | アクティブマトリクス型発光装置 | |

| JP4758062B2 (ja) | 半導体装置 | |

| JP4906119B2 (ja) | 発光装置及び電子機器 | |

| JP2007025713A (ja) | 発光装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100119 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100120 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130129 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130129 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130129 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |