自発光型の発光素子を有したアクティブマトリクス型の発光装置の研究が活発化している。このような自発光型の発光装置の代表例として、EL表示装置があげられる。

また、近年、中、大型のディスプレイ装置のみならず、携帯情報端末の表示部にも広く用いられるようになったフラットパネル型の表示装置は、その高精細化に伴って、画素数が増加している。画素数の増加に対応するため、各画素毎に薄膜トランジスタ(TFT)を設け画像データを保持することができるアクティブマトリクス構造の画素が採用されている。

アクティブマトリクス構造のEL表示装置の階調方式には大きく分けてアナログ階調方式とデジタル階調方式の2つがある。このうちデジタル階調方式には時分割階調方式と、面積階調方式と、時分割階調方式と面積階調方式の混合した方式等がある。時分割階調方式、面積階調方式のいずれのデジタル階調方式においても、各画素あるいはサブ画素をon状態あるいはoff状態の2値で駆動する。

このため画素に配された薄膜トランジスタ(TFT)のしきい値電圧Vthのばらつきによる画質の劣化をアナログ階調方式に比べて低減させることができる利点がある。時分割方式でデジタル階調表示を行うことが、特許文献1に開示されている。

また、多数の画素に迅速に映像信号を各画素に書き込むために、1行ごと同時にデータ入力をする線順次方式を採用することが望まれる。図9を用いて、アクティブマトリクス型のEL表示装置を線順次方式のデジタル階調表示により駆動することを説明する。

図9は、アクティブマトリクス構造の画素に2値のデータを入力するデジタル階調方式型の表示装置の構成を示している。画素部501には、EL素子に代表される発光素子、発光素子の発光を制御するためのTFTが設けられる。画素部501の周辺部には、シフトレジスタ504と、第1のラッチ回路505と、第2のラッチ回路506と、レベルシフタ507とバッファ群回路508を有するソース信号線駆動回路502と、シフトレジスタ509と、レベルシフタ510と、バッファ群回路511を有するゲート信号線駆動回路503が配置されている。図10はバッファ群回路508の等価回路を示している。

図10(A)に示すようにバッファ群回路508は、各列に設けられた複数のバッファ601でなる。そして、図10(B)はバッファ601の等価回路図であり、2つのインバータでなる。入力はレベルシフタ507に接続され、出力は画素部501に接続されている。また、信号線602によりバッファ高電源電位(VBH)が与えられ、信号線603によりバッファ低電源電位(VBL)が与えられている。

図9のアクティブマトリクス型表示装置を線順次方式によりデジタル階調表示で駆動する方法を説明する。まず、シフトレジスタ509は、クロック信号(GCK)、スタートパルス(GSP)にしたがって、1段目から順次選択パルスを出力する。その後、レベルシフタ510によって振幅変換をし、バッファ群回路511により1行目から順次ゲート線が選択される。

ゲートが選択される行において、シフトレジスタ504は、クロック信号(SCK)、スタートパルスにしたがって、1段目から順次サンプリングパルスを出力する。第1のラッチ回路505は、サンプリングパルスが入力されるタイミングで、映像信号(Video)の取り込みを行い、各段で取り込まれた映像信号は第1のラッチ回路505において保持される。

1行分の映像信号の取り込みが完了した後、ラッチパルス(LAT)が入力されると、第1のラッチ回路505において保持されていた映像信号は、一斉に第2のラッチ回路506へと転送され、全てのソース信号が一斉に充放電される。

このとき、ソース信号線を充放電するバッファの高電源電位(VBH)は、発光素子高電源電位(ANODE)と同期し、低電源電位(VBL)は固定である。本明細書において発光素子高電源電位(ANODE)とは、発光素子の陽極(アノード)に与えられる電位をいう。

以上の動作が1行目から最終行まで繰り返され、全画素への書き込みが完了する。1フレーム分の映像が表示される。同様の動作を繰り返し、映像の表示を行う。

特開2001−5426号公報

アナログ階調方式では1フレームに最低1回のソース信号線へのデータ書込みを行えば階調表現が可能である。

これに対して、各画素をon状態あるいはoff状態の2値で駆動する時間階調方式や面積階調方式や時間階調方式と面積階調方式を複合化した方式等、デジタル階調方式においては、階調表現をするためには1フレームに複数回のソース信号線へのデータ書込みが必要となる。

EL表示装置においてソース信号線は、画素部に設けられた複数のTFTや寄生容量により、バッファに対する負荷になっている。デジタル階調方式において、ソース信号線へ書き込まれるデータがLow電位からHigh電位に変化するときには、高電源電位(VBH)を与える外部の高電位電源は前記バッファ601のPチャネル型TFTを通じてLow電位からHigh電位まで、ソース信号線による負荷容量に電荷を充電する。逆に、ソース信号線へ書き込まれるデータがHigh電位からLow電位に変化するときには低電源電位(VBL)を与える外部の低電位電源は前記バッファ601のNチャネル型TFTを通じてHigh電位からLow電位までソース信号線による負荷容量から電荷を放電する。

これらの電力はソース信号線の電圧の変化時に消費されるので、ソース信号線の出力の変化がたびたび起これば、外部電源の電力消費は大きくなる。このためデジタル階調方式においては、自然画のように多くの階調数が必要な画像や1dotチェッカ(ここでは、マトリクス状に並べられた画素において、点灯、非点灯が交互に並んだ表示画素のことを意味する)のように1行ごとに論理が頻繁に逆転するような画像では、ソース信号線の電位の変化が多くなるため、外部電源の消費電力が増大してしまう。

また、画素部の発光素子に流れる電流の大きさは、温度によっても左右される。特に発光素子に有機化合物を用いた場合、温度特性の問題が顕著になる。EL素子の電極間にかかる電圧が同じであっても、EL素子が有する温度特性によって、温度が高くなれば高くなるほど、EL素子を流れる電流は大きくなる。よってEL素子の温度が高ければ高いほど、表示装置の消費電力が大きくなり、発光素子の輝度も上昇してしまう。

カラー表示の場合、発光素子高電源電位(ANODE)は、発光材料によって、EL素子ごとに異なる電位が設定されている。発光材料が、赤(R)で発光するEL素子、緑(G)で発光するEL素子、青(B)で発光するEL素子では、経時劣化や温度による特性の変化が異なる。

また、例えば、ユーザーが好んで赤表示をした場合、RのEL素子だけが他のEL素子に比べ先行して劣化することも想定される。したがって、様々な発光素子高電源電位(ANODE)の電位変化に対応できる表示装置が求められている。

バッファの高電源電位(VBH)は、発光素子高電源電位(ANODE)と等しいかそれ以上の電位である必要がある。バッファの高電源電位(VBH)は、ソース信号線の充電の役割を担っているため、充電する電位が小さいほど、バッファの高電源電位(VBH)が必要とする電力が少なくなる。従って、バッファの高電源電位(VBH)は、発光素子高電源電位(ANODE)と等しいことが望ましい。

また、前述の通り、発光素子高電源電位(ANODE)は、経時劣化や温度変化、ユーザーの使用状況などにより変化する。このため、バッファの高電源電位(VBH)は、発光素子高電源電位(ANODE)に追従する必要があり、任意の発光素子高電源電位(ANODE)で充電に要する電力を低減させるためには、発光素子高電源電位(ANODE)と同期させる必要がある。

このため、従来の表示装置では、ソース信号線を充放電するバッファの高電源電位(VBH)は、発光素子高電源電位(ANODE)と同期し、低電源電位(VBL)は固定であった。

その結果、上述したように、従来のバッファー回路では消費電力が大きくなり易いため、バッファの温度が上昇しやすい。そしてバッファの発熱に伴い、その結果、画素部に温度分布が生じるため、輝度のバラツキが生じてしまう。

あるいは、EL素子の経時劣化や温度上昇により、発光素子高電源電位(ANODE)が上昇してしまうため、その結果ソース信号線を充放電する電位差、すなわち高電源電位(VBH)と低電源電位(VBL)との差分が大きくなるため、ソース信号線を充放電するバッファ601による消費電力が大きくなり、バッファ601を発熱させしまい、その結果、画素部の輝度のバラツキを生じさせてしまうという問題点もある。

このためデジタル階調方式において、ソース信号線へデータの書き込みに要する消費電力は、低消費電力を必要とする携帯端末向けの小型表示装置には大きな問題となっている。また、テレビ等の表示装置においても大型化に伴うソース信号線の寄生容量の増加は避けることは困難であり、小型表示装置同様、消費電力の減少が課題となっている。

本発明は、以上のような課題に鑑みてなされたものであり、インバータを用いたバッファなどの回路の省電力化を目的とする。また、発光素子を用いたアクティブマトリクス型表示装置のソース信号線の充放電に要する消費電力を低減することを目的とする。

本発明では、ソース信号線の充放電を行うバッファ(インバータ)の低電源電位(VBL)を高電源電位(VBH)に追従させる。特に、発光装置においては、この低電源電位(VBL)を発光素子高電源電位(ANODE)に追従させることを特徴とする。

本発明はに係る発光装置は、オペアンプ、第1の抵抗、第2の抵抗、第3の抵抗、及び第4の抵抗を有する回路と、バッファを有する駆動回路とを有し、オペアンプは、出力端子、第1の入力端子、及び第2の入力端子を有し、第1の抵抗は、一方の端子が第1の高電源電位に接続され、他方の端子がオペアンプの第1の入力端子に接続され、第2の抵抗は、一方の端子がオペアンプの第1の入力端子に接続され、他方の端子は、オペアンプの出力端子に接続され、第3の抵抗は、一方の端子が第2の高電源電位に接続され、他方の端子がオペアンプの第2の入力端子に接続され、第4の抵抗は、一方の端子がオペアンプの第2の入力端子に接続され、他方の端子が低電源電位に接続され、第2の抵抗の他方の端子の電位は、バッファの低電源電位と等しく、第2の高電源電位は、バッファの高電源電位と等しいことを特徴とする。

本発明はに係る発光装置は、ベース端子、コレクタ端子、及びエミッタ端子を有するバイポーラトランジスタと、オペアンプ、第1の抵抗、第2の抵抗、第3の抵抗、及び第4の抵抗を有する回路と、バッファを有する駆動回路とを有し、オペアンプは、出力端子、第1の入力端子、及び第2の入力端子を有し、バイポーラトランジスタのベース端子はオペアンプの出力端子と電気的に接続され、バイポーラトランジスタのコレクタ端子は低電源電位と電気的に接続され、第1の抵抗は、一方の端子が第1の高電源電位に接続され、他方の端子がオペアンプの第1の入力端子に接続され、第2の抵抗は、一方の端子がオペアンプの第1の入力端子に接続され、他方の端子がバイポーラトランジスタのエミッタ端子に接続され、第3の抵抗は、一方の端子が第2の高電源電位に接続され、他方の端子がオペアンプの第2の入力端子に接続され、第4の抵抗は、一方の端子がオペアンプの第2の入力端子に接続され、他方の端子が低電源電位に接続され、バイポーラトランジスタのエミッタ端子及び第2の抵抗の他方の端子からの電位は、駆動回路のバッファの低電源電位と等しく、第2の高電源電位は、バッファの高電源電位と等しいことを特徴とする。

本発明に係る他の発光装置は、発光素子、オペアンプ、第1の抵抗、第2の抵抗、第3の抵抗、及び第4の抵抗を有し、第1の抵抗は、一方の端子が第1の高電源電位に接続され、他方の端子がオペアンプの第1の入力端子に接続され、第2の抵抗は、一方の端子がオペアンプの第1の入力端子に接続され、他方の端子は、オペアンプの出力端子に接続され、第3の抵抗は、一方の端子が第2の高電源電位に接続され、他方の端子がオペアンプの第2の入力端子に接続され、第4の抵抗は、一方の端子がオペアンプの第2の入力端子に接続され、他方の端子が低電源電位に接続され、第2の抵抗の他方の端子の電位がバッファの低電源電位として供給され、第2の高電源電位がバッファの高電源電位として供給されることを特徴とする。

本発明はに係る発光装置は、発光素子、バイポーラトランジスタ、オペアンプ、駆動回路、第1の抵抗、第2の抵抗、第3の抵抗、及び第4の抵抗を有し、バイポーラトランジスタは、ベース端子がオペアンプの出力端子に接続され、コレクタ端子が低電源電位に接続され、第1の抵抗は、一方の端子が第1の高電源電位に接続され、他方の端子がオペアンプの第1の入力端子に接続され、第2の抵抗は、一方の端子がオペアンプの第1の入力端子に接続され、他方の端子がバイポーラトランジスタのエミッタ端子に接続され、第3の抵抗は、一方の端子が第2の高電源電位に接続され、他方の端子がオペアンプの第2の入力端子に接続され、第4の抵抗は、一方の端子がオペアンプの第2の入力端子に接続され、他方の端子が低電源電位に接続され、バイポーラトランジスタのエミッタ端子及び第2の抵抗の他方の端子からの電位が、駆動回路のバッファの低電源電位として供給され、第2の高電源電位がバッファの高電源電位として供給されることを特徴とする。

本発明において、発光装置の発光素子は画素に配置される。また発光素子としてEL素子が用いられる。EL素子は一対の電極(陽極と陰極)間に、電場を加えることでルミネッセンスが発生する層(以下、EL層と記す)が挟まれた構造となっている。EL層として、有機化合物が使用されるが、EL層は通常、積層構造となっている。代表的には、「正孔輸送層、発光層、電子輸送層」という積層構造が挙げられる。

また、EL層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とがあるが、本発明の発光装置は、上述した発光のうちのいずれか一方の発光を用いても良いし、または両方の発光を用いても良い。

また他にも、陽極上に正孔注入層、正孔輸送層、発光層、電子輸送層の順に積層する構造、または正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

本明細書において陰極と陽極の間に設けられる全ての層を総称してEL層と呼ぶ。よって上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、全てEL層に含まれる。

また、本発明の発光装置は、半導体基板上に設けられていてもよいし、ガラス基板上に設けられていてもよい。また、可撓性基板上に設けられていてもよいし、SOI基板上に設けたれていても良い。

なお、発光装置は薄膜トランジスタを含んで構成されていてもよい。

また、上記構成の発明の発光装置は、電子機器等に用いることができる。

本発明では、高電源電位(VBH又はANODE)の上昇が生じても、バッファの低電源電位が高電源電位に追従して上昇するため、バッファー(インバータ)に供給されている高電源電位と低電源電位との電位差の上昇を小さくすることができる。その結果、少ない電力でソース信号線のデータ書き換えが可能になる。それに伴い、バッファの発熱も抑えられ、発熱による画素部の輝度のバラツキが低減される。

よって、本発明は、線順次方式のデジタル階調駆動を行うEL表示装置のような発光装置に非常に好適である。

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

(実施の形態1)

図1及び図2を用いて、本実施形態を説明する。

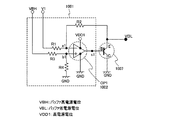

図1は、本実施形態の電位発生回路の回路図である。図1に示すように、電位発生回路は、抵抗R1〜R4、オペアンプ(OP1)1002、及びバイポーラトランジスタ(Bi1)1007で構成される。

オペアンプ(OP1)の2つの電源接続端子には、それぞれ高電源電位(VDD1)、低電源電位(GND)が入力される。また、オペアンプ(OP1)の出力端子c1に、バイポーラトランジスタ(Bi1)のベース端子Bが接続されている。バイポーラトランジスタ(Bi1)は、ベース端子Bがオペアンプ(OP1)の出力端子c1に、コレクタ端子Cが低電源電位(GND)に接続されている。

抵抗R1は、一方の端子が高電源電位(V1)に接続され、他方の端子がオペアンプ(OP1)の入力端子a1に接続されている。抵抗R2は、一方の端子がオペアンプ(OP1)の入力端子a1に、他方の端子がバイポーラトランジスタ(Bi1)のエミッタ端子Eに接続されている。抵抗R3は、一方の端子が高電源電位(VBH)に、他方の端子がオペアンプ(OP1)の入力端子b1に接続されている。抵抗R4は、一方の端子がオペアンプ(OP1)の入力端子b1に、他方の端子が低電源電位(GND)に接続されている。バイポーラトランジスタ(Bi1)のエミッタ端子E及び抵抗R2の他方の端子の電位が低電源電位(VBL)として取り出される。この低電源電位(VBL)は、高電源電位(VBH)と高電源電位V1との差分になる。

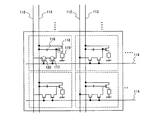

図2(A)に、図1の回路が用いられた発光装置を示す。図2(A)において図9と同じ符号は同じ構成要素を示す。

図2(A)において、画素部501には、発光素子、代表的にはEL素子、発光素子の発光を制御するためのTFTが設けられ、アクティブマトリクス構造の画素となっている。画素部501の周辺部には、画素部501と同一基板500上に、TFTを用いて構成されたソース信号線駆動回路502及びゲート信号線駆動回路503が配置されている。

ソース信号線駆動回路502はシフトレジスタ504と、第1のラッチ回路505と、第2のラッチ回路506と、レベルシフタ507とバッファ群回路508を有する。ゲート信号線駆動回路503はシフトレジスタ509と、レベルシフタ510と、バッファ群回路511を有する。

図2(A)においても、バッファ群回路508は図10(A)に示すように、列ごとにバッファ601が配置されている。バッファ601の等価回路は図10(B)に示されている。バッファ群回路508には、バッファ高電源電位(VBH)を供給する信号線(電源線)1003及びバッファ低電源電位(VBL)を供給する信号線(電源線)1004が接続されている。さらに、信号線1003はバッファ群回路508のバッファ高電源電位(VBH)を供給する信号線602に接続され、信号線1004は、バッファの低電源電位(VBL)を供給する信号線603に接続されている(図10(B)参照)。その結果、バッファ群回路508には、信号線1003によりバッファの高電源電位(VBH)が供給され、信号線1004によりバッファ低電源電位(VBL)が供給される。

また、画素部には、発光素子の陽極に電源を供給する電源供給線が設けられており、この電源供給線は、バッファ高電源電位(VBH)を与えている外部電源に接続される。したがって、バッファ高電源電位(VBH)は発光素子高電源電位(ANODE)と等しくなる。なお、バッファ高電源電位(VBH)と発光素子高電源電位(ANODE)が同じであっても、異なる外部電源を設けてもよい。電源を共通にすることにより、電源の削減、接続部の削減につながる。

本実施形態では、信号線1004には図1に示す電位発生回路が接続されている。この電位発生回路は、抵抗R1〜R4、オペアンプ(OP1)1002によって構成された回路1001、及びバイポーラトランジスタ(Bi1)1007で構成される。本実施形態の発光装置のおいて、バイポーラトランジスタ(Bi1)1007以外は、同一基板500上に、画素部501、ソース信号線駆動回路502及びゲート信号線駆動回路503と共に、TFTを用いて形成することを特徴とする。バイポーラトランジスタ(Bi1)1007は、ICチップを用いて形成され、例えばCOG法により基板500上に実装される。

図2(B)に回路1001の回路図を示す。オペアンプ(OP1)1002の2つの電源接続端子には、それぞれ高電源電位(VDD1)、低電源電位(GND)が入力される。また、オペアンプ(OP1)1002の出力端子c1に、バイポーラトランジスタ(Bi1)1007のベース端子Bが接続されている。

バイポーラトランジスタ(Bi1)1007は、ベース端子Bがオペアンプ(OP1)1002の出力端子c1に、コレクタ端子Cが低電源電位(GND)に、エミッタ端子Eが抵抗R2及び低電源電位(VBL)を供給する信号線1004に接続されている。

抵抗R1は、一方の端子が高電源電位(V1)を供給する信号線(電源線)1005に接続され、他方の端子がオペアンプ(OP1)1002の入力端子a1に接続されている。抵抗R2は、一方の端子がオペアンプ(OP1)1002の入力端子a1に、他方の端子がバイポーラトランジスタ(Bi1)1007のエミッタ端子Eに接続されている。抵抗R3は、一方の端子がバッファ高電源電位(VBH)及び発光素子高電源電位(ANODE)を供給する信号線1003に、他方の端子がオペアンプ(OP1)1002の入力端子b1に接続されている。抵抗R4は、一方の端子がオペアンプ(OP1)1002の入力端子b1に、他方の端子が低電源電位(GND)に接続されている。

高電源電位(V1)は、バッファ高電源電位(VBH)及び発光素子高電源電位(ANODE)よりも、電位が低いものとする。また、本実施形態ではバッファ高電源電位(VBH)は発光素子高電源電位(ANODE)と等しいものとしたが、バッファ高電源電位(VBH)の方を大きくしてもよい。この場合は、発光素子高電源電位(ANODE)とバッファ高電源電位(VBH)に対応して、異なる外部電源が用意される。

本実施形態では、オペアンプ(OP1)1002の増幅比を1とし、抵抗R1〜R4の抵抗値は等しくなるようにする。なお、バッファ高電源電位(VBH)、発光素子高電源電位(ANODE)、バッファの低電源電位(VBL)、高電源電位(V1)を設計者が要求する値にするため、抵抗R1〜R4の抵抗値を必要に応じて変更できることはいうまでもない。また、オペアンプ(OP1)1002は、消費電力の小さなものを設計するのが好ましい。

本実施形態のオペアンプ(OP1)1002等でなる電位発生回路により、バッファの低電源電位(VBL)は、発光素子高電源電位(ANODE)から高電源電位(V1)を減算したものとなる。

よって、バッファの低電源電位(VBL)は、発光素子高電源電位(ANODE)に追従して上昇することになり、バッファの消費電力の増加を抑えることができる。

本実施形態の電位発生回路は、バイポーラトランジスタ(Bi1)の以外の回路1001を同一基板上に、画素部501、ソース信号線駆動回路502及びゲート信号線駆動回路503と共に形成しているため、外付けの部品点数を減らすことが可能となる。なお、図1に示す電位発生回路を全てICで形成し、例えばCOG法などにより基板500上に実装しても良い。

また、本実施形態では、ソース信号線駆動回路502、ゲート信号線駆動回路503を画素部501と共にTFTで形成したが、それぞれの回路の一部又は全てをICで形成し、COG法やTAB法により実装しても良い。

(実施の形態2)

図3は、本実施形態の電位発生回路の回路図である。図3に示すように、電位発生回路は、抵抗R1〜R4、オペアンプ(OP1)で構成される。

オペアンプ(OP1)の2つの電源接続端子には、それぞれ高電源電位(VDD1)、低電源電位(GND)が入力される。

抵抗R1は、一方の端子が高電源電位(V1)に接続され、他方の端子がオペアンプ(OP1)1102の入力端子a1に接続されている。抵抗R2は、一方の端子がオペアンプ(OP1)1102の入力端子a1に、他方の端子がオペアンプ(OP1)1102の出力端子c1に接続されている。抵抗R3は、一方の端子が高電源電位(VBH)に、他方の端子がオペアンプ(OP1)1102の入力端子b1に接続されている。抵抗R4は、一方の端子がオペアンプ(OP1)1102の入力端子b1に、他方の端子が低電源電位(GND)に接続されている。オペアンプ(OP1)1102の出力端子c1の電位が低電源電位(VBL)として取り出される。この低電源電位(VBL)は、高電源電位(VBH)と高電源電位(V1)との差分になる。

図4(A)に、図3の電位発生回路を用いた発光装置を示す。なお、図4において、図9及び図2と同じ符号は同じ構成要素を示す。また、本実施形態の発光装置は電位発生回路1101の他は、実施形態1の図2と同様である。

本実施形態の電位発生回路1101は全て同一基板500上に、画素部501、ソース信号線駆動回路502及びゲート信号線駆動回路503と共に、TFTを用いて形成することを特徴とする。

図4(B)に示すように、電位発生回路1101において、オペアンプ(OP1)1102の2つの電源接続端子に、それぞれ、高電源電位(VDD1)、低電源電位(GND)が接続されている。また、オペアンプ(OP1)1102の出力端子c1に、抵抗R2の一方の端子、及びバッファ群回路508に低電源電位(VBL)を供給する信号線(電源線)1104が接続されている。

抵抗R1は、一方の端子が高電源電位(V1)を供給する信号線(電源線)1105に接続され、他方の端子がオペアンプ(OP1)1102の入力端子a1に接続されている。抵抗R2は、一方の端子がオペアンプ(OP1)1102の入力端子a1に、他方の端子がオペアンプ(OP1)1102の出力端子c1に接続されている。抵抗R3は、一方の端子がバッファ高電源電位(VBH)及び発光素子高電源電位(ANODE)を供給する信号線(電源線)1103に接続され、他方の端子がオペアンプ(OP1)1102の入力端子b1に接続されている。抵抗R4は、一方の端子がオペアンプ(OP1)1102の入力端子b1に接続され、他方の端子が低電源電位(GND)に接続されている。

ここでは、オペアンプ(OP1)1102の増幅比を1とし、抵抗R1〜R4の抵抗値を等しくする。もちろん、バッファ高電源電位(VBH)、発光素子高電源電位(ANODE)、バッファの低電源電位(VBL)、高電源電位(V1)を設計者が要求する値にするため、抵抗R1〜R4の抵抗値を必要に応じて変更できることはいうまでもない。また、オペアンプ(OP1)1102は、消費電力の小さなものを設計するのが好ましい。

バッファ群回路508には、信号線1103及び1104が接続され、信号線1103はバッファ群回路508のバッファ高電源電位(VBH)を供給する信号線602に接続され、信号線1004はバッファの低電源電位(VBL)を供給する信号線603に接続されている(図10(B)参照)。その結果、信号線1104により、バッファの高電源電位(VBH)が供給され、信号線1104により、バッファ低電源電位(VBL)が供給される。

また、画素部501には、発光素子の陽極に電源を供給する電源供給線が設けられており、この電源供給線はバッファ高電源電位(VBH)を与えている外部電源に接続される。したがって、本実施形態では、バッファ高電源電位(VBH)は発光素子高電源電位(ANODE)と等しくなる。なお、バッファ高電源電位(VBH)と発光素子高電源電位(ANODE)が同じであっても、異なる外部電源を設けてもよい。電源を共通にすることにより、電源の削減、接続部の削減につながる。

高電源電位(V1)は、バッファ高電源電位(VBH)及び発光素子高電源電位(ANODE)よりも、電位が低いものとする。また、ここではバッファ高電源電位(VBH)は発光素子高電源電位(ANODE)と等しくしたが、もしくは発光素子高電源電位(ANODE)よりも大きい電位とすることができる。

電位発生回路1101により、バッファの低電源電位(VBL)は、発光素子高電源電位(ANODE)から高電源電位(V1)を減算したものとなる。したがって、発光素子高電源電位(ANODE)が上昇しても、バッファの低電源電位(VBL)は、発光素子高電源電位(ANODE)に追従して上昇させることができる。

本実施の形態では、電位発生回路1101を同一基板500上に、画素部501、ソース信号線駆動回路502、及びゲート信号線駆動回路503と共に形成することにより、外付けの部品点数を減らすことが可能となる。なお、電位発生回路1101を全てICで形成し、例えばCOG法などにより基板500上に実装しても良いことはいうまでもない。

また、本実施形態では、ソース信号線駆動回路502、ゲート信号線駆動回路503を画素部501と共にTFTで形成しているが、それぞれの回路の一部又は全てをICで形成し、COG法でやTAB法により実装しても良い。

また、実施形態1及び2において、赤(R)で発光するEL素子、緑(G)で発光するEL素子、青(B)で発光するEL素子など、EL材料が異なる複数種類の発光素子を画素部501に設ける場合は、R,G,Bなど発光素子の種類ごとに、発光素子高電源電位(ANODE)の値を異ならせることが好ましい。そのため、発光素子高電源電位(ANODE)とバッファの低電源電位(VBL)が、発光素子の種類ごとに設けるとよい。

(実施の形態3)

実施形態1、2で説明したように、本発明は、画素の高精細化に伴う、EL表示装置の消費電力を抑え、かつ画素部の輝度のバラツキをおさえることができるため、高精細な表示部が必要とされる電子機器に好適である。例えば、テレビジョン装置(テレビ、テレビジョン受信機)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図11を参照して説明する。

例えば、図11(A)の携帯情報端末、図11(B)のデジタルビデオカメラ、図11(C)の携帯電話、図11(D)に示す携帯型のテレビジョン装置、図11(E)に示すノート型のコンピュータ、図11(F)に示すテレビジョン装置である。それぞれの表示部2001〜2006に、本発明を用いた発光装置が用いられる。

本発明により、図11(A)〜(E)に示すようなバッテリーを用いているものは、消費電力を削減した分、電子機器の使用時間を長持ちさせることができる。

また、図11(F)にテレビジョン装置のような大型の表示部であっても、ソース信号線駆動回路の発熱が抑えられるため、長時間使用しても発熱による輝度のバラツキが生じにくい。

実施例1に、図2に示す実施形態1の発光装置を作製した例を示す。なお、実施形態1と異なり、図1の回路には全てICを使用した。本実施例の画素部の等価回路構成を図5に示す。なお、本発明の画素構造は、図5の回路に限定されないことはいうまでもない。

図5に示すように、ソース信号線112は、Nチャネル型TFT120のソース端子に接続されており、Nチャネル型TFT120のドレイン端子は、Nチャネル型TFT117のソース端子と接続されている。Nチャネル型TFT120とNチャネル型TFT117のゲート端子は、ゲート信号線114に接続されている。なお、Nチャネル型TFT120とNチャネル型TFT117は、直列に接続された2つのTFTとして記されているが、作製するときは、チャネルが設けられる半導体層を共有するダブルゲートTFTとして、2つのNチャネル型TFT117、120とを1つのTFTで作製されている。

画素容量Cp116は、一方の端子が発光素子高電源電位(ANODE)を与える信号線(電源線)113に接続され、他方の端子がNチャネル型TFT117のドレイン端子及びPチャネル型TFT118のゲート端子に接続されている。

Pチャネル型TFT118は、ソース端子が発光素子高電源電位(ANODE)を与える信号線113と接続されており、ドレイン端子が発光素子119の陽極に接続されている。

発光素子119は、EL素子でなり、陽極がPチャネル型TFT118のドレイン端子と接続されており、陰極には、発光素子低電源電位(CATHODE)に接続されている。

図6、図7に本実施例の効果を示す測定データを示す。図6、図7とも、バッファの高電源電位(VBH)を発光素子高電源電位(ANODE)と等しくなるように同期させたときのデータである。

図6には、発光素子高電源電位(ANODE)の変化に対する、バッファの低電源電位(VBL)の変化を示す。図7には、発光素子高電源電位(ANODE)の変化に対する、バッファの低電源電位(VBL)を供給する信号線1004に流れる電流の変化を示す。それぞれ、オペアンプ(OP1)の高電源電位(VDD1)=15V、低電源電位(GND)=0Vとし、発光素子高電源電位(ANODE)を5Vから12Vまで変化させ、高電源電位(V1)を3V、4V、5Vとし、発光装置を線順次方式のデジタル階調駆動した。

図6においてバッファの低電源電位(VBL)=0Vに固定されているデータは、図1の回路を備えていない比較例の発光装置のデータに該当する。図7、図8の比較例についても同様である。

図6に示すように、従来の構成では、バッファの低電源電位(VBL)が0Vに固定されているため、発光素子高電源電位(ANODE)が上昇すると、バッファのインバータに供給される高電源電位(VBH)と低電源電位(VBL)の電位差が大きくなっていることがわかる。

一方、本実施例では、発光素子高電源電位(ANODE)の上昇に追従してバッファの低電源電位(VBL)が上昇することで、比較例に比べて、高電源電位(VBH)と低電源電位(VBL)の電位差が小さくなることが、図6によって確認できる。

図7から、比較例の表示装置では、バッファの低電源電位(VBL)が固定されている場合、電流値が発光素子高電源電位(ANODE)と比例関係であり、発光素子高電源電位(ANODE)が上昇すると、電流値が大きくなっていたことがわかる。

一方、本実施例では、発光素子高電源電位(ANODE)の上昇に比例することなく、発光素子高電源電位(ANODE)が7V以上では、バッファの低電源電位(VBL)が3Vのときは約5.6mA、4Vのときは約7mA、5Vのときは約9mAとなり、電流値がほぼ一定にとなっていることが確認できる。

すなわち、本実施例により、経時変化や温度によって、発光素子高電源電位(ANODE)が上昇しても、消費電力の上昇が抑えられ、またソース信号線回路の発熱をおさえることができることが理解できる。

また、実施例の効果をさらに確認するため発光装置を1時間駆動後に測定した、ソース信号線駆動回路の温度、及び画素部の輝度を測定した。図8(A)、(B)は、それぞれ、実施例、比較例のソース信号線の温度であり、図8(C)、(D)は、それぞれ、実施例、比較例の発光素子の輝度を示す。実施例の発光装置は、発光素子高電源電位(ANODE)=10V、高電源電位(V1)=4Vにて固定して、駆動させた。また、比較例の発光装置は発光素子高電源電位(ANODE)=10Vにて固定し、測定を行った。

図8(A)、(B)から、ソース信号線駆動回路の温度は、本実施例の発光装置が比較例よりも低くなっていることがわかる。図から(A)の実施例は(B)の比較例より平均温度が約5℃低くなる。環境温度によるの輝度の劣化は2〜3℃で影響を受けるため、本発明による5℃の低下は大きな影響と考えられる。すなわち、本実施例により発熱が抑えられ、発熱による輝度のバラツキが抑えられたことがわかる。

また、図8(C)に示す実施例では、ソース信号線駆動回路の発熱が抑えられているため、画素部のソース信号線駆動回路付近と中央付近とで、輝度はほぼ等しくなっているのに対し、図8(D)から、比較例は、ソース信号線駆動回路の発熱の影響を受け、ソース信号線駆動回路側の部分の輝度が高くなり、輝度のバラツキが生じていることがわかる。すなわち、本実施例により、発熱による画素部の輝度のバラツキが抑えられていることがわかる。

なお、本実施例では、実施形態1の回路の効果を実証したが、実施形態2の回路も同様の効果が得られることは、以上の実験結果から容易に推測される。