JP4416456B2 - エレクトロルミネッセンス装置 - Google Patents

エレクトロルミネッセンス装置 Download PDFInfo

- Publication number

- JP4416456B2 JP4416456B2 JP2003305081A JP2003305081A JP4416456B2 JP 4416456 B2 JP4416456 B2 JP 4416456B2 JP 2003305081 A JP2003305081 A JP 2003305081A JP 2003305081 A JP2003305081 A JP 2003305081A JP 4416456 B2 JP4416456 B2 JP 4416456B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- current

- switch

- signal

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005401 electroluminescence Methods 0.000 title claims description 75

- 239000003990 capacitor Substances 0.000 claims description 48

- 238000005070 sampling Methods 0.000 description 27

- 238000006243 chemical reaction Methods 0.000 description 20

- 238000002347 injection Methods 0.000 description 11

- 239000007924 injection Substances 0.000 description 11

- 238000000034 method Methods 0.000 description 10

- 238000013459 approach Methods 0.000 description 8

- 230000003071 parasitic effect Effects 0.000 description 6

- 230000007704 transition Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 4

- 238000007599 discharging Methods 0.000 description 3

- 230000005669 field effect Effects 0.000 description 2

- 241000282376 Panthera tigris Species 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

- G09G3/325—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror the data current flowing through the driving transistor during a setting phase, e.g. by using a switch for connecting the driving transistor to the data driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0297—Special arrangements with multiplexing or demultiplexing of display data in the drivers for data electrodes, in a pre-processing circuitry delivering display data to said drivers or in the matrix panel, e.g. multiplexing plural data signals to one D/A converter or demultiplexing the D/A converter output to multiple columns

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/066—Waveforms comprising a gently increasing or decreasing portion, e.g. ramp

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0238—Improving the black level

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

Description

電圧設定方式によるカラー化したELパネルの回路構成を図12に示す。

電圧設定方式の画素回路2の構成を図13に示す。

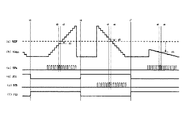

時間t1〜t5において該当行の画素回路2の行制御信号P13〜P15は、各々Hレベル、Hレベル、Lレベルになっており、時間t1〜t2において各水平サンプリングパルスSPが一斉にHレベルに変化しても、該当画素回路2のM200、M300、M400が各々OFF、OFF、ONのままであるので、容量C100及びM100のゲート容量の保持電圧である該当画素回路2のM100/G電圧によって決定されるM100のドレイン電流が該当EL素子に注入され発光を継続している。尚、水平ブランキング期間内の時間t1〜t2においては、入力映像信号video電圧は図15に示すように黒レベル近傍の電圧Vblである。

時刻t5において、該当行の行制御信号P13及びP15はLレベル及びHレベルに変化する。時間t5〜t6において、再び各水平サンプリングパルスSPは一斉にHレベルに変化するとともに、このとき入力映像信号であるブランキング電圧が列制御信号14とされる。

時刻t9において、P13及びP15は再びHレベル及びLレベルに変化して、該当画素回路2のM300及びM400はOFF及びON状態になる。こうして変化した該当画素回路のM100/G電圧によって決定されるM100のドレイン電流が該当EL素子に注入され、発光量の変化が起こり、この状態が保持される。

電流設定方式によるカラー化したELパネルの回路構成を図3に示す。まず、図12の電圧設定方式によるELパネルとの違いについて説明する。

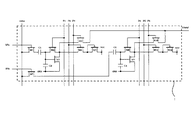

電流設定方式のELパネルの水平画素数と同数配列される列制御回路1の構成を図8に示す。

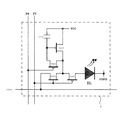

図6は電流設定方式の画素回路2の構成例である。P9及びP10が行制御信号20に対応し、列制御信号14として電流信号i(data)が入力され、M100/Dは接地されたEL素子の電流注入端子に接続されている。

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1から第6のスイッチと、第1、第2の容量素子と、第1、第2のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続され、

第1のトランジスタの第2主電極は第4のスイッチの第1端子に接続され、

第2のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第2のスイッチの第2端子は第2の容量素子の第1端子に接続され、

第2の容量素子の第2端子は第2のトランジスタのゲート電極に接続され、

第5のスイッチの第1端子と第2端子とは第2のトランジスタのゲート電極と第2主電極とに夫々接続され、

第2のトランジスタの第1主電極は第1の電源に接続され、

第2のトランジスタの第2主電極は第6のスイッチの第1端子に接続され、

第4及び第6のスイッチの第2端子は互いに接続されて前記電流信号を出力する電流信号出力端子とされ、

第1から第6のスイッチの制御端子は、夫々第1から第6の制御信号線に接続されていることを特徴とする電流信号出力回路、である。

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1から第8のスイッチと、第1、第2の容量素子と、第1から第4のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続され、

第1のトランジスタの第2主電極は第4のスイッチの第1端子と第7のスイッチの第1端子とに接続され、

第7のスイッチの第2端子は第3のトランジスタの第1主電極に接続され、

第3のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源に接続され、

第2のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第2のスイッチの第2端子は第2の容量素子の第1端子に接続され、

第2の容量素子の第2端子は第2のトランジスタのゲート電極に接続され、

第5のスイッチの第1端子と第2端子とは第2のトランジスタのゲート電極と第2主電極とに夫々接続され、

第2のトランジスタの第1主電極は第1の電源に接続され、

第2のトランジスタの第2主電極は第6のスイッチの第1端子と第8のスイッチの第1端子とに接続され、

第8のスイッチの第2端子は第4のトランジスタの第1主電極に接続され、

第4のトランジスタはゲート電極と第1主電極又は第2主電極とが短絡されており且つ第2主電極は第2の電源に接続され、

第4及び第6のスイッチの第2端子は互いに接続されて外部に前記電流信号を出力する電流信号出力端子とされ、

第1から第8のスイッチの制御端子は、夫々第1から第8の制御信号線に接続されていることを特徴とする電流信号出力回路である。

(4)

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1及び第3のスイッチと、第1の容量素子と、第1のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第3のスイッチの第1端子と第2端子とは第1のトランジスタのゲート電極と第2主電極とに夫々接続され、

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流信号出力回路である。

(5)

前記第3のスイッチを介して第1のトランジスタのゲート電極を充電した後、第1のトランジスタのゲート電極の電圧が閾値電圧に近づくように放電させてから、前記第1のスイッチに与えられる電圧信号に応じた電圧に第1のトランジスタのゲート電極を充電し、該充電された状態に応じた電流信号を前記第1のトランジスタの第2主電極から電流信号を出力する構成を好適に採用できる。

また、前記第3のスイッチの第2端子には第3のスイッチを介して第1のトランジスタのゲート電極を充電するための電流供給経路が接続されている構成を好適に採用できる。該電流供給経路に流れる電流を制御するスイッチを更に有する構成を好適に採用できる。

(6)

入力される電圧信号に応じて電流信号を出力する電流信号出力回路であって、

電流信号制御回路を有しており、

該電流信号制御回路は、

少なくとも、第1のスイッチと、第1の容量素子と、第1のトランジスタとを備えており、

第1のスイッチの第1端子は電圧信号を与える電圧信号線に接続され、第1のスイッチの第2端子は第1の容量素子の第1端子に接続され、

第1の容量素子の第2端子は第1のトランジスタのゲート電極に接続され、

第1のトランジスタの第1主電極は第1の電源に接続されていることを特徴とする電流信号出力回路である。

各電流信号制御回路が前記第1のトランジスタの第2主電極から出力される電流信号を外部に出力するか否かを制御するスイッチを有しており、一方の電流信号制御回路の該スイッチが第1のトランジスタの第2主電極から出力される電流信号を外部に出力する状態にあるときに、他方の電流信号制御回路の該スイッチが第1のトランジスタの第2主電極から出力される電流信号を外部に出力しない状態に制御しておく構成を好適に採用できる。

電流信号出力回路を構成する少なくとも2つの電流信号制御回路と前記複数の表示素子それぞれとの対応関係が非固定的に制御されるとは、複数の表示素子に対する電流信号の順次の供給を複数回行う際に、ある一巡の順次供給の際に所定の表示素子に対して一方の電流信号制御回路からの出力電流が供給された場合には、該一巡に続く一巡など前記一巡とは異なる一巡の順次供給の際には前記所定の表示素子に対しては他方の電流信号制御回路からの出力電流が供給されるようにすることを言う。複数の表示素子により画面を構成する場合、例えば1フレーム毎など画面の更新(表示画面の内容が変化しない場合を含む)ごとに各表示素子に対応する電流信号制御回路が変化する構成が特に好適である。

第4及び第6のスイッチを選択的に動作させる機能を有し、表示する映像信号のフレームによって第4及び第6のスイッチの動作を奇数行または偶数行で変更する表示装置を好適に採用できる。第4及び第6のスイッチに相当する他のスイッチがなければ第4及び第6のスイッチを相補的に動作させればよい。

これらのうち、本発明のエレクトロルミネッセンス装置は、

エレクトロルミネッセンス素子(EL)と、該エレクトロルミネッセンス素子を発光させる駆動電流を供給するための駆動トランジスタ(M100)と、該駆動トランジスタのゲートに接続された容量(C100)と、を有する画素回路(2)の複数と、

トランジスタ(M3)、該トランジスタのゲートに容量素子(C1)を介して映像電圧信号を書き込むための第1のスイッチ(M1)、該トランジスタの一方の主電極をダイオード接続されたトランジスタ(M5)を介して参照電源(Vcc)に接続するための第2のスイッチ(M4)、該トランジスタの該一方の主電極とゲート電極とを接続するための第3のスイッチ(M2)、ならびに該トランジスタの該一方の主電極から前記複数の画素回路に電流信号を供給するための第4のスイッチ(M6)、を有する列制御回路(1)と、

を具備し、

前記列制御回路から前記画素回路に供給された電流信号は、当該画素回路の容量(C100)に充電電圧として保持され、該保持された充電電圧に基づいて前記駆動トランジスタ(M100)が前記エレクトロルミネッセンス素子に前記駆動電流を供給する、エレクトロルミネッセンス装置において、

前記列制御回路は、

前記第1のスイッチ(M1)を閉じてブランキングレベルの電圧を前記容量素子(C1)に入力した状態で、前記第2のスイッチ(M4)を閉じて前記トランジスタ(M3)の前記一方の主電極をダイオード接続されたトランジスタ(M5)を介して前記参照電源(Vcc)に接続し、第3のスイッチ(M2)を閉じて前記トランジスタ(M3)のゲート容量(C2)を充電し、

前記充電を停止して、前記トランジスタ(M3)のゲート容量(C2)に充電された電荷を、前記第3のスイッチ(M2)を介して放電し、

前記第3のスイッチ(M2)を切り離し、前記第2のスイッチ(M4)を閉じた状態で、前記第1のスイッチ(M1)を介して映像電圧信号を前記容量素子(C1)に入力し、前記第1のスイッチ(M1)を切り離して前記トランジスタ(M3)のゲート容量(C2)の電圧を保持し、

前記第2のスイッチ(M4)を切り離し、前記第4のスイッチ(M6)を閉じて、前記トランジスタ(M3)の前記一方の主電極から電流信号を前記画素回路に供給する、

回路であることを特徴とするエレクトロルミネッセンス装置であり、前記列制御回路(1)を2組備え、前記複数の画素回路(2)への電流信号の供給を交互に行う構成を好適に採用でき、前記複数の画素回路(2)の各々に供給される電流信号は、前記映像電圧信号のフレームごとに、前記列制御回路(1)の2組から交互に供給される構成をより好適に採用できる。

M1=M7、M3=M9、M2=M8、M5=M12、C1=C3、C2=C4 ・・・(3)

となっている。

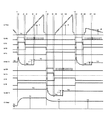

図2は図1の動作を説明するタイムチャートである。図2は映像信号の3水平走査期間、ELパネルからすると3行分の動作を示したものである。

SPa、SPbは各々L、Lレベルであり、P1〜P6は各々L、L、H、L、H、Lレベルである。したがって、各SW動作をするトランジスタは

M1=OFF、M2=OFF、M4=OFF、M6=ON

M7=OFF、M8=OFF、M11=ON、M10=OFF となる。

時刻t1において、入力映像信号videoはブランキングレベルVblになっているとともに、SPa、P2、P3、P5、P6は各々H、H、L、L、Hレベルに変化する。

M1=ON、M2=OFF、M4=ON、M6=OFF

M7=OFF、M8=OFF、M11=OFF、M10=ON となる。

時刻t7において、入力映像信号videoはブランキングレベルVblになっているとともに、SPb、P2、P3、P5、P6は各々H、L、H、H、Lレベルに変化する。

M1=OFF、M2=OFF、M4=OFF、M6=ON

M7=ON、M8=OFF、M11=ON、M10=OFF となる。

C(M9)はM9ゲート入力容量を示す。このときM9/D電流は(2)式で示される。該当するSPbがLレベルに変化するとM7=OFFなり、M7の寄生容量動作によって多少電圧降下したVb2に変化して再びM9/G電圧は保持状態になる。

時刻t13において、入力映像信号videoはブランキングレベルVblになっているとともに、SPa、P2、P3、P5、P6は各々H、H、L、L、Hレベルに変化する。

M1=ON、M2=OFF、M4=ON、M6=OFF

M7=OFF、M8=OFF、M11=OFF、M10=ON となる。

2 画素回路

3 水平シフトレジスタ

4 ゲート回路

5 垂直シフトレジスタ

6,7,8 入力回路

9 画素表示領域

10 入力映像信号

11,11a 水平走査制御信号

12,12a 垂直走査制御信号

13,13a 補助列制御信号

14 列制御信号

15 水平サンプリング信号ゲート回路

16 ゲート回路

17 水平サンプリング信号

18 水平サンプリング信号

19 制御信号

20 行制御信号

21 制御信号

22 列制御回路

Claims (3)

- エレクトロルミネッセンス素子(EL)と、該エレクトロルミネッセンス素子を発光させる駆動電流を供給するための駆動トランジスタ(M100)と、該駆動トランジスタのゲートに接続された容量(C100)と、を有する画素回路(2)の複数と、

トランジスタ(M3)、該トランジスタのゲートに容量素子(C1)を介して映像電圧信号を書き込むための第1のスイッチ(M1)、該トランジスタの一方の主電極をダイオード接続されたトランジスタ(M5)を介して参照電源(Vcc)に接続するための第2のスイッチ(M4)、該トランジスタの該一方の主電極とゲート電極とを接続するための第3のスイッチ(M2)、ならびに該トランジスタの該一方の主電極から前記複数の画素回路に電流信号を供給するための第4のスイッチ(M6)、を有する列制御回路(1)と、

を具備し、

前記列制御回路から前記画素回路に供給された電流信号は、当該画素回路の容量(C100)に充電電圧として保持され、該保持された充電電圧に基づいて前記駆動トランジスタ(M100)が前記エレクトロルミネッセンス素子に前記駆動電流を供給する、エレクトロルミネッセンス装置において、

前記列制御回路は、

前記第1のスイッチ(M1)を閉じてブランキングレベルの電圧を前記容量素子(C1)に入力した状態で、前記第2のスイッチ(M4)を閉じて前記トランジスタ(M3)の前記一方の主電極をダイオード接続されたトランジスタ(M5)を介して前記参照電源(Vcc)に接続し、第3のスイッチ(M2)を閉じて前記トランジスタ(M3)のゲート容量(C2)を充電し、

前記充電を停止して、前記トランジスタ(M3)のゲート容量(C2)に充電された電荷を、前記第3のスイッチ(M2)を介して放電し、

前記第3のスイッチ(M2)を切り離し、前記第2のスイッチ(M4)を閉じた状態で、前記第1のスイッチ(M1)を介して映像電圧信号を前記容量素子(C1)に入力し、前記第1のスイッチ(M1)を切り離して前記トランジスタ(M3)のゲート容量(C2)の電圧を保持し、

前記第2のスイッチ(M4)を切り離し、前記第4のスイッチ(M6)を閉じて、前記トランジスタ(M3)の前記一方の主電極から電流信号を前記画素回路に供給する、

回路であることを特徴とするエレクトロルミネッセンス装置。 - 前記列制御回路(1)を2組備え、前記複数の画素回路(2)への電流信号の供給を交互に行うことを特徴とする請求項1に記載のエレクトロルミネッセンス装置。

- 前記複数の画素回路(2)の各々に供給される電流信号は、前記映像電圧信号のフレームごとに、前記列制御回路(1)の2組から交互に供給されることを特徴とする請求項2に記載のエレクトロルミネッセンス装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003305081A JP4416456B2 (ja) | 2002-09-02 | 2003-08-28 | エレクトロルミネッセンス装置 |

| US10/650,776 US7126565B2 (en) | 2002-09-02 | 2003-08-29 | Current signal output circuit and display apparatus and information display apparatus using the current signal output circuit |

| US11/440,182 US7221341B2 (en) | 2002-09-02 | 2006-05-25 | Display apparatus driving method using a current signal |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002256432 | 2002-09-02 | ||

| JP2003305081A JP4416456B2 (ja) | 2002-09-02 | 2003-08-28 | エレクトロルミネッセンス装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004145296A JP2004145296A (ja) | 2004-05-20 |

| JP2004145296A5 JP2004145296A5 (ja) | 2006-08-10 |

| JP4416456B2 true JP4416456B2 (ja) | 2010-02-17 |

Family

ID=32396230

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003305081A Expired - Fee Related JP4416456B2 (ja) | 2002-09-02 | 2003-08-28 | エレクトロルミネッセンス装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7126565B2 (ja) |

| JP (1) | JP4416456B2 (ja) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7342560B2 (en) * | 2004-04-01 | 2008-03-11 | Canon Kabushiki Kaisha | Voltage current conversion device and light emitting device |

| JP2005331900A (ja) * | 2004-06-30 | 2005-12-02 | Eastman Kodak Co | 表示装置 |

| JP4843203B2 (ja) * | 2004-06-30 | 2011-12-21 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | アクティブマトリクス型表示装置 |

| JP4889205B2 (ja) * | 2004-06-30 | 2012-03-07 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | アクティブマトリクス型表示装置 |

| JP4160032B2 (ja) * | 2004-09-01 | 2008-10-01 | シャープ株式会社 | 表示装置およびその駆動方法 |

| KR101057275B1 (ko) * | 2004-09-24 | 2011-08-16 | 엘지디스플레이 주식회사 | 유기발광소자 |

| US20060120357A1 (en) * | 2004-12-03 | 2006-06-08 | Canon Kabushiki Kaisha | Programming circuit, light emitting device using the same, and display device |

| JP2007271968A (ja) * | 2006-03-31 | 2007-10-18 | Canon Inc | カラー表示装置及びアクティブマトリクス装置 |

| US7852299B2 (en) * | 2006-03-31 | 2010-12-14 | Canon Kabushiki Kaisha | Active-matrix device |

| JP2007271969A (ja) * | 2006-03-31 | 2007-10-18 | Canon Inc | カラー表示装置及びアクティブマトリクス装置 |

| JP2008009277A (ja) * | 2006-06-30 | 2008-01-17 | Canon Inc | 電圧電流変換方法、電圧電流変換回路、及びアクティブマトリクス型表示装置 |

| JP2008009276A (ja) * | 2006-06-30 | 2008-01-17 | Canon Inc | 表示装置及びそれを用いた情報処理装置 |

| JP4281765B2 (ja) | 2006-08-09 | 2009-06-17 | セイコーエプソン株式会社 | アクティブマトリクス型発光装置、電子機器およびアクティブマトリクス型発光装置の画素駆動方法 |

| JP5495510B2 (ja) * | 2007-06-19 | 2014-05-21 | キヤノン株式会社 | 表示装置及びそれを用いた電子機器 |

| JP2009014836A (ja) * | 2007-07-02 | 2009-01-22 | Canon Inc | アクティブマトリクス型表示装置及びその駆動方法 |

| CN101779229B (zh) * | 2007-08-21 | 2012-11-07 | 佳能株式会社 | 显示装置及其驱动方法 |

| JP2009080272A (ja) * | 2007-09-26 | 2009-04-16 | Canon Inc | アクティブマトリクス型表示装置 |

| JP2009109641A (ja) | 2007-10-29 | 2009-05-21 | Canon Inc | 駆動回路、及びアクティブマトリクス型表示装置 |

| US7989701B2 (en) * | 2007-11-27 | 2011-08-02 | Sabic Innovative Plastics Ip B.V. | Multiconductor cable assembly and fabrication method therefor |

| JP5284198B2 (ja) * | 2009-06-30 | 2013-09-11 | キヤノン株式会社 | 表示装置およびその駆動方法 |

| JP2011013415A (ja) * | 2009-07-01 | 2011-01-20 | Canon Inc | アクティブマトリックス型表示装置 |

| JP2011028135A (ja) * | 2009-07-29 | 2011-02-10 | Canon Inc | 表示装置及びその駆動方法 |

| JP2013110282A (ja) * | 2011-11-21 | 2013-06-06 | Canon Inc | 発光素子の駆動回路および発光装置 |

| JP6124573B2 (ja) | 2011-12-20 | 2017-05-10 | キヤノン株式会社 | 表示装置 |

| CN106982337B (zh) * | 2017-04-27 | 2019-07-23 | 京东方科技集团股份有限公司 | 一种cmos图像传感器及其像素电路、驱动方法 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3144166B2 (ja) * | 1992-11-25 | 2001-03-12 | ソニー株式会社 | 低振幅入力レベル変換回路 |

| US5675278A (en) * | 1994-02-09 | 1997-10-07 | Texas Instruments Incorporated/Hiji High-Tech Co., Ltd. | Level shifting circuit |

| US5714968A (en) * | 1994-08-09 | 1998-02-03 | Nec Corporation | Current-dependent light-emitting element drive circuit for use in active matrix display device |

| JP3325780B2 (ja) | 1996-08-30 | 2002-09-17 | シャープ株式会社 | シフトレジスタ回路および画像表示装置 |

| US5952789A (en) * | 1997-04-14 | 1999-09-14 | Sarnoff Corporation | Active matrix organic light emitting diode (amoled) display pixel structure and data load/illuminate circuit therefor |

| US6229506B1 (en) * | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| GB9812742D0 (en) | 1998-06-12 | 1998-08-12 | Philips Electronics Nv | Active matrix electroluminescent display devices |

| KR100296113B1 (ko) * | 1999-06-03 | 2001-07-12 | 구본준, 론 위라하디락사 | 전기발광소자 |

| JP2001147659A (ja) * | 1999-11-18 | 2001-05-29 | Sony Corp | 表示装置 |

| GB0008019D0 (en) * | 2000-03-31 | 2000-05-17 | Koninkl Philips Electronics Nv | Display device having current-addressed pixels |

| TW493153B (en) * | 2000-05-22 | 2002-07-01 | Koninkl Philips Electronics Nv | Display device |

| CN1658266A (zh) * | 2000-07-07 | 2005-08-24 | 精工爱普生株式会社 | 驱动电流驱动元件的驱动电路及其方法 |

| JP3593982B2 (ja) * | 2001-01-15 | 2004-11-24 | ソニー株式会社 | アクティブマトリクス型表示装置およびアクティブマトリクス型有機エレクトロルミネッセンス表示装置、並びにそれらの駆動方法 |

| JP2002278504A (ja) * | 2001-03-19 | 2002-09-27 | Mitsubishi Electric Corp | 自発光型表示装置 |

| JP2002351401A (ja) * | 2001-03-21 | 2002-12-06 | Mitsubishi Electric Corp | 自発光型表示装置 |

| JP2002297053A (ja) * | 2001-03-30 | 2002-10-09 | Sanyo Electric Co Ltd | アクティブマトリクス型表示装置及びその検査方法 |

| JP3610923B2 (ja) * | 2001-05-30 | 2005-01-19 | ソニー株式会社 | アクティブマトリクス型表示装置およびアクティブマトリクス型有機エレクトロルミネッセンス表示装置、並びにそれらの駆動方法 |

| TW554558B (en) * | 2001-07-16 | 2003-09-21 | Semiconductor Energy Lab | Light emitting device |

| US6847171B2 (en) * | 2001-12-21 | 2005-01-25 | Seiko Epson Corporation | Organic electroluminescent device compensated pixel driver circuit |

| JP3997109B2 (ja) * | 2002-05-08 | 2007-10-24 | キヤノン株式会社 | El素子駆動回路及び表示パネル |

| JP3984938B2 (ja) * | 2002-09-02 | 2007-10-03 | キヤノン株式会社 | シフトレジスタ及び表示装置及び情報表示装置 |

| JP4350463B2 (ja) * | 2002-09-02 | 2009-10-21 | キヤノン株式会社 | 入力回路及び表示装置及び情報表示装置 |

-

2003

- 2003-08-28 JP JP2003305081A patent/JP4416456B2/ja not_active Expired - Fee Related

- 2003-08-29 US US10/650,776 patent/US7126565B2/en not_active Expired - Fee Related

-

2006

- 2006-05-25 US US11/440,182 patent/US7221341B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004145296A (ja) | 2004-05-20 |

| US20060208978A1 (en) | 2006-09-21 |

| US20040104909A1 (en) | 2004-06-03 |

| US7221341B2 (en) | 2007-05-22 |

| US7126565B2 (en) | 2006-10-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4416456B2 (ja) | エレクトロルミネッセンス装置 | |

| JP4194451B2 (ja) | 駆動回路及び表示装置及び情報表示装置 | |

| US8614656B2 (en) | Display apparatus, and driving circuit for the same | |

| US7663615B2 (en) | Light emission drive circuit and its drive control method and display unit and its display drive method | |

| US7969389B2 (en) | Pixel circuit for a current-driven light emitting element | |

| JP3925435B2 (ja) | 発光駆動回路及び表示装置並びにその駆動制御方法 | |

| US7196568B2 (en) | Input circuit, display device and information display apparatus | |

| US20020041278A1 (en) | Electro-optical device and method of driving the same, organic electroluminescent display device, and electronic apparatus | |

| US7307463B2 (en) | Source follower, voltage follower, and semiconductor device | |

| KR101102372B1 (ko) | 반도체장치 및 발광 장치 | |

| JP2007179037A (ja) | El表示装置及びel表示装置の駆動方法 | |

| US6137465A (en) | Drive circuit for a LCD device | |

| KR100615128B1 (ko) | 능동 매트릭스형 유기 el 패널 구동 회로 및 유기 el디스플레이 장치 | |

| JP2005157322A (ja) | 駆動回路、表示装置と駆動方法、制御方法、及び駆動装置 | |

| US7791570B2 (en) | Electrical circuit arrangement for a display device | |

| JP2005173434A (ja) | 電圧電流変換回路、該回路を用いた表示装置 | |

| JP2011170289A (ja) | 表示装置 | |

| JP2005165095A (ja) | エレクトロルミネッセンス表示装置 | |

| KR20010039024A (ko) | 전계방출디스플레이(fed) 및 그 구동방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060623 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080325 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080715 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080916 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091117 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091124 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121204 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131204 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |