JP4395941B2 - 任意電圧発生構造及びこれを用いた固体撮像素子 - Google Patents

任意電圧発生構造及びこれを用いた固体撮像素子 Download PDFInfo

- Publication number

- JP4395941B2 JP4395941B2 JP31280699A JP31280699A JP4395941B2 JP 4395941 B2 JP4395941 B2 JP 4395941B2 JP 31280699 A JP31280699 A JP 31280699A JP 31280699 A JP31280699 A JP 31280699A JP 4395941 B2 JP4395941 B2 JP 4395941B2

- Authority

- JP

- Japan

- Prior art keywords

- fuse

- insulating film

- substrate

- film

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000003384 imaging method Methods 0.000 title claims description 14

- 239000000758 substrate Substances 0.000 claims description 63

- 239000004065 semiconductor Substances 0.000 claims description 4

- 239000010408 film Substances 0.000 claims 24

- 239000010409 thin film Substances 0.000 claims 4

- 230000002093 peripheral effect Effects 0.000 claims 2

- 239000011810 insulating material Substances 0.000 description 20

- 230000001681 protective effect Effects 0.000 description 15

- 229910004298 SiO 2 Inorganic materials 0.000 description 7

- 230000006378 damage Effects 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 239000013256 coordination polymer Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000012776 electronic material Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/148—Charge coupled imagers

- H01L27/14831—Area CCD imagers

- H01L27/14843—Interline transfer

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Integrated Circuits (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、任意電圧発生構造及びこれを用いた固体撮像素子に関する。特に、基板上に複数のヒューズを設けて該ヒューズの特定の切断により任意の電圧を得るようにした任意電圧発生構造、及びこれを用いた固体撮像素子に関するものである。本発明の任意電圧発生構造は、任意電圧発生を要する各種機器等で汎用することができ、また、本発明の固体撮像素子はこのような任意電圧発生構造を内蔵して、利用することができるものである。

【0002】

【従来の技術】

基板上に複数のヒューズを設けて、特定の電圧の印加により数本のヒューズを切断することで、所望の出力電圧を取り出せるようにした任意電圧発生回路が知られている。たとえばCCD等の固体撮像素子においては、希望する任意の出力電圧を得る場合に、その希望する電圧を外部印加でなく、チップ内部で発生させるために、このような任意電圧発生回路を使用することがある。たとえば図7に示す回路が知られている(特開平6−153079号公報)。

【0003】

この回路は、抵抗(たとえばポリシリコンで形成)の横に接続したヒューズ(たとえばポリシリコンで形成)の両端に、振幅数10V/時間、幅数msecのパルス状サージ電圧を数回印加し、ヒューズを切断する構造になっている。全ヒューズの内、数本を切断することで、この回路から所望の出力電圧(Vout)を取り出すことができる。

【0004】

図7に示す任意電圧発生回路についてさらに詳細に説明すると、次のとおりである。ある電圧VとアースGRNの間に抵抗R0,R1,・・・,Rn−1,Rn(たとえばポリシリコンで形成)を直列に接続し、それらの横にヒューズF1,F2,・・・,Fn−1,Fn(たとえばポリシリコンで形成)を配置する。ヒューズの両端にサージ電圧を与え、n個のヒューズの内、いくつかを選択的に切る。たとえば、ヒューズF1を切る場合は、パッドP1とCPにサージ電圧を印加する。これにより、0(V)〜V(V)の間の任意の電圧を出力電圧Voutとして得ることができる。

【0005】

図8に示す任意電圧発生回路は、上記の変形で、抵抗とヒューズとを並列に接続したものであるが、同様な作用を示す。

【0006】

上記したような任意電圧発生回路を基板上に形成して、基板上に複数のヒューズを設け、該ヒューズに所定の電圧を印加することにより該ヒューズの少なくともいずれか1つを切断することで所望の出力電圧を取り出せるようにした任意電圧発生構造を組む場合、従来、次のような問題点がある。

【0007】

図9に、従来構造を示す。これはサージ電圧印加前のヒューズ部分の構造の断面を示すものである。図9の構造は、基板1(シリコン基板等)上に、絶縁膜2(SiO2等)を介してヒューズ3(ポリシリコン等で形成)を形成し、該ヒューズ3の両端に電圧を印加するための配線5(アルミニウム配線等)を形成し、かつ、該配線5とヒューズ3との間に絶縁膜4を介在させたものである。図9の構造はさらに2層の保護膜▲1▼6及び保護膜▲2▼7を備えた例であるが、1層の場合もある。ここでは保護膜が2層の場合について説明する。

【0008】

ヒューズ3の両端につながっているアルミニウム配線5にサージ電圧を印加してヒューズ3を切った場合、理想的には図10のようになり、ヒューズ3は完全に切断し、かつ他の部分には影響を与えない。しかしサージ電圧が小さい場合には、図11に示すように、ヒューズ3が完全には切れない現象が起こる。これを防止するために、ヒューズ3に大きなサージ電圧を印加すると、図12に示すように、ヒューズ3と基板1とが導通してしまうことがある。

【0009】

上記のようなショートが発生すると、この回路から希望する任意の電圧を取り出すことができなくなり、問題である。このショートの発生は、ヒューズ3に大きなサージ電圧を印加するとサージ電圧印加時のダメージが基板方向(図の下方)に向かうために、ヒューズ3−シリコン基板1間の絶縁膜2が破壊されるためと考えられる。

【0010】

【発明が解決しようとする課題】

本発明は、上記の問題点に鑑みてなされたもので、基板上に複数のヒューズを設け、該ヒューズに所定の電圧を印加することにより該ヒューズの少なくともいずれか1つを切断することで所望の出力電圧を取り出せる構成とした任意電圧発生構造について、また該任意電圧発生構造を用いた固体撮像素子について、ヒューズ−基板間のショートを防止できるとともに、適正なヒューズ切断により所望の電圧が得られるようにした任意電圧発生構造及びこれを用いた固体撮像素子を提供することを目的とする。

【0011】

【課題を解決するための手段】

本発明に係る任意電圧発生構造は、基板上に複数のヒューズを設け、該ヒューズにはその両端に電圧を印加し得る構造とするとともに、該ヒューズに所定の電圧を印加することにより該ヒューズの少なくともいずれか1つを切断することで所望の出力電圧を取り出せる構成とした任意電圧発生構造において、上記ヒューズと基板とを絶縁する基板側の絶縁膜と、該ヒューズの基板とは反対側の絶縁材料との膜厚の関係を、ヒューズ切断用印加電圧において該基板側の絶縁膜が絶縁機能を維持し得る膜厚の関係としたことを特徴とするものである。

【0012】

本発明に係る固体撮像素子は、基板上に複数のヒューズを設け、該ヒューズにはその両端に電圧を印加し得る構造とするとともに、該ヒューズに所定の電圧を印加することにより該ヒューズの少なくともいずれか1つを切断することで所望の出力電圧を取り出せる構成とした任意電圧発生構造を備える固体撮像素子において、上記任意電圧発生構造について、上記ヒューズと基板とを絶縁する基板側の絶縁膜と、該ヒューズの基板とは反対側の絶縁材料との膜厚の関係を、ヒューズ切断用印加電圧において該基板側の絶縁膜が絶縁機能を維持し得る膜厚の関係としたことを特徴とするものである。

【0013】

本発明は、本発明者による次のような知見に基づいてなされたものである。すなわち、従来構造においては、ヒューズ3の上側(基板1とは逆の側)の絶縁材料の膜厚(ヒューズ3上の絶縁膜4及び保護膜6,7の合計膜厚)が厚いため、ヒューズ3の破壊時のダメージが上方(基板1と逆の側の方向)に抜けず、基板1の方に向かい、その結果、基板1側の絶縁膜2が破壊され、ヒューズ3と基板1とがショートすると考えられる。具体的には、ヒューズ3の下の基板1側の絶縁膜2の膜厚(数100nm)に比べ、ヒューズ3の上の絶縁材料の膜厚が1000nm程度と厚い(保護膜▲1▼6の膜厚が厚い、もしくは、ヒューズ3−配線5間の絶縁膜4が厚い)ので、図12に示すようにサージ電圧印加時のダメージは下方(基板1側)に向かって、これによりヒューズ3−基板1間の絶縁膜2が破壊され、よってヒューズ3と基板1とがショートに到ると考えられる。

【0014】

本発明は、上記知見に立ち、ヒューズの基板とは逆の側(上側)の絶縁材料の膜厚が適正であれば、サージ電圧印加時のダメージが下方(基板1側)に向かうことが抑制され、ヒューズと基板とのショートが防止できることを発見して、本発明に到達したものである。

【0015】

すなわち、本発明によれば、ヒューズと基板とを絶縁する基板側の絶縁膜と、該ヒューズの基板とは反対側の絶縁材料との膜厚の関係を適正に設定することによって、基板側の絶縁膜に向かうダメージを緩和し、該絶縁膜の破壊を防止して、ヒューズ−基板間のショートを防止し、適正なヒューズ切断により所望の電圧が得られるようにできるのである。

【0016】

本発明によれば、ヒューズの基板とは反対側の絶縁材料の膜厚を適正なものとすることにより、ヒューズが切れはじめるサージ電圧と、ヒューズと基板が導通しはじめるサージ電圧との差を十分にでき、適正なサージ電圧を選択できるようになる。従来技術に見られる、上記電圧差が小さいことに起因する、適正なサージ電圧の選択ができないという問題点が解決できる。

【0017】

【発明の実施の形態】

以下、本発明の実施の形態についてさらに説明し、また、その好ましい具体例を図面を参照して説明する。なお当然のことではあるが、本発明は図示実施の形態例に限定されるものではない。

【0018】

本発明においては、ヒューズと基板とを絶縁する基板側の絶縁膜と、該ヒューズの基板とは反対側の絶縁材料との膜厚の関係を、ヒューズ切断用印加電圧において該基板側の絶縁膜が絶縁機能を維持し得る膜厚の関係とするに際して、上記ヒューズと基板とを絶縁する基板側の絶縁膜の膜厚に対し、該ヒューズの基板とは反対側の絶縁材料の膜厚を、該基板側の絶縁膜の膜厚と同程度もしくはそれ以下とする形態をとることができる。

【0019】

また本発明においては、上記ヒューズの基板とは反対側の絶縁材料の膜厚を、数100nm程度とする形態をとることができる。

【0020】

以下の具体的な実施の形態例の記述においては、任意電圧発生構造を固体撮像素子に適用する場合で本発明を説明するが、本発明はその他、この種の任意電圧発生構造を用いる各種装置、たとえば電子材料、半導体デバイス等へも同様に応用できるものである。

【0021】

実施の形態例1

図1(サージ電圧印加前のヒューズ部の構造)を参照する。本例においては、基板1(シリコン基板等)上に、絶縁膜2(SiO2等)を介してヒューズ3(ポリシリコン等で形成)を形成し、該ヒューズ3の両端に電圧を印加するための配線5(アルミニウム配線等)を形成し、かつ、該配線5とヒューズ3との間に絶縁膜4(SiO2等)を介在させる構造について、ヒューズ3上の絶縁材料(SiO2等の絶縁膜4、SiN等の保護膜等)の膜厚を適正にしたものである。図1の構造では、2層の保護膜▲1▼6及び保護膜▲2▼7のうち、保護膜▲1▼6は、ヒューズ3上から除去すること、及びヒューズ3上の絶縁膜4を一部薄くすることで、ヒューズ3上の絶縁材料の厚さを小さくした。

【0022】

すなわち、ヒューズ3上の絶縁材料(SiO2、SiN等)を、必ずしもすべて除去する必要は無く、ヒューズ3が切れはじめるサージ電圧と、ヒューズ3と基板1が導通しはじめるサージ電圧との電圧差が十分で、適正なサージ電圧が選択できる厚さとする。ヒューズ3上の絶縁材料の膜厚は、ヒューズ3下の絶縁膜2の膜厚の4倍以下であることが好ましい。該ヒューズ3上の絶縁材料の膜厚は、ヒューズ3下の絶縁膜2の膜厚と同程度(数100nm)、もしくは、それ以下にすることがさらに望ましい。具体的には、ヒューズ3下の絶縁膜2の膜厚は一般に300nm〜700nmとすることが好ましいので、その場合ヒューズ3上の絶縁材料の膜厚は、300nm〜1500nmであることが適切で好ましい。

【0023】

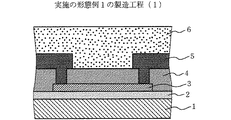

本例において、ヒューズ3上の絶縁材料の厚さを適正に(小さく)する手段として、図1に示すように、ヒューズ3上の保護膜▲1▼6を除去すること(これによりヒューズ3上には凹入9が形成される)、及びヒューズ3上の絶縁膜4を一部薄くすることを行ったが、この構造は、次の工程で製造することができる。図2ないし図6を参照する。

【0024】

図2に示すように、基板1(シリコン基板等)上に、絶縁膜2(SiO2等)を介してヒューズ3(ポリシリコン等で形成)を形成し、絶縁膜4(SiO2等)を形成し、ヒューズ3の両端に電圧を印加する配線5(アルミニウム配線等)を形成し、さらに保護膜▲1▼6を形成した構造を得る。

【0025】

レジスト8をコーティングして、図3の構造とする。

【0026】

レジスト8をパターニングして、ヒューズ3に該当する部分のレジスト8を除去し、図4の構造とする。

【0027】

上記パターニングしたレジスト8をマスクとして、ヒューズ3上の膜をエッチングする。すなわち、ヒューズ3上の保護膜▲1▼6をエッチング除去する。このとき、ヒューズ3上の絶縁膜4も、多少エッチングされてよい。これにより、図5の構造を得る。

【0028】

レジスト8を除去して、図6の構造を得る。さらに保護膜▲2▼7を形成して、図1の構造を得る。

【0029】

本例によれば、ヒューズ3上の絶縁材料の膜厚を適正にした(薄膜にした)ことにより、ヒューズ3にサージ電圧を印加する際に発生するダメージを基板1方向(下方)に向かうことを防ぎ、ヒューズ3と基板1との導通を防止できる。

【0030】

本例によれば、ヒューズ3が切れはじめるサージ電圧と、ヒューズ3と基板1とが導通する電圧の差を広げることができ、適切なサージ電圧を選択できる。つまり、安定した条件でヒューズ3を切ることができる。

【0031】

本例によれば、CCD撮像素子について、適正に任意電圧を発生させることが可能になった。なお、同様の任意電圧発生回路を用いる他の半導体製品等についても、同様に好ましく適用できる。

【0032】

【発明の効果】

本発明によれば、基板上に複数のヒューズを設け、該ヒューズに所定の電圧を印加することにより該ヒューズの少なくともいずれか1つを切断することで所望の出力電圧を取り出せる構成とした任意電圧発生構造について、また該任意電圧発生構造を用いた固体撮像素子について、ヒューズ−基板間のショートを防止できるとともに、適正なヒューズ切断により所望の電圧が得られるようにできるという効果を奏する。

【図面の簡単な説明】

【図1】 本発明の実施の形態例1のヒューズ部を示す断面図である。

【図2】 本発明の実施の形態例1の構造を得る製造工程を示す断面図である(1)。

【図3】 本発明の実施の形態例1の構造を得る製造工程を示す断面図である(2)。

【図4】 本発明の実施の形態例1の構造を得る製造工程を示す断面図である(3)。

【図5】 本発明の実施の形態例1の構造を得る製造工程を示す断面図である(4)。

【図6】 本発明の実施の形態例1の構造を得る製造工程を示す断面図である(5)。

【図7】 本発明を適用できる任意電圧発生回路の例を示す。

【図8】 本発明を適用できる任意電圧発生回路の例を示す。

【図9】 従来技術を示す図である。

【図10】 従来技術を示す図である。

【図11】 従来技術の問題点を示す図である。

【図12】 従来技術の問題点を示す図である。

【符号の説明】

1・・・基板、2・・・(基板側の)絶縁膜、3・・・ヒューズ、4・・・絶縁膜(基板と逆の側の絶縁材料)、5・・・配線、6・・・保護膜▲1▼(基板と逆の側の絶縁材料)、7・・・保護膜▲2▼(基板と逆の側の絶縁材料)

Claims (2)

- 半導体基板上に第1の絶縁膜を介して設けられた複数のヒューズと、該ヒューズの上層に設けられた第2の絶縁膜とを有し、前記ヒューズに所定の電圧を印加することで同ヒューズの少なくともいずれか1つを切断して所望の出力電圧を取り出せる構成とした任意電圧発生回路において、

前記ヒューズ上の前記第2の絶縁膜の少なくとも一部は、前記ヒューズの周辺領域上の前記第2の絶縁膜より薄膜であり、

前記ヒューズ上の前記第2の絶縁膜の薄膜部分の膜厚は300nm〜1500nmであると共に、

前記ヒューズ下の前記第1の絶縁膜の膜厚は前記第2の絶縁膜の薄膜部分の膜厚の4倍以下であり、かつ、前記ヒューズ下の前記第1の絶縁膜の膜厚は300nm〜700nmである

任意電圧発生回路。 - 半導体基板上に第1の絶縁膜を介して設けられた複数のヒューズと、該ヒューズの上層に設けられた第2の絶縁膜とを有し、前記ヒューズに所定の電圧を印加することで同ヒューズの少なくともいずれか1つを切断して所望の出力電圧を取り出せる構成とした任意電圧発生回路を備える固体撮像素子において、

前記ヒューズ上の前記第2の絶縁膜の少なくとも一部は、前記ヒューズの周辺領域上の

前記第2の絶縁膜より薄膜であり、

前記ヒューズ上の前記第2の絶縁膜の薄膜部分の膜厚は300nm〜1500nmであると共に、

前記ヒューズ下の前記第1の絶縁膜の膜厚は前記第2の絶縁膜の薄膜部分の膜厚の4倍以下であり、かつ、前記ヒューズ下の前記第1の絶縁膜の膜厚は300nm〜700nmである

固体撮像素子。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31280699A JP4395941B2 (ja) | 1999-09-29 | 1999-09-29 | 任意電圧発生構造及びこれを用いた固体撮像素子 |

| KR1020000057446A KR20010030546A (ko) | 1999-09-29 | 2000-09-29 | 임의 전압 발생 구조 및 이 구조를 사용하는 고체 촬상 소자 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31280699A JP4395941B2 (ja) | 1999-09-29 | 1999-09-29 | 任意電圧発生構造及びこれを用いた固体撮像素子 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001102533A JP2001102533A (ja) | 2001-04-13 |

| JP2001102533A5 JP2001102533A5 (ja) | 2006-05-11 |

| JP4395941B2 true JP4395941B2 (ja) | 2010-01-13 |

Family

ID=18033644

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31280699A Expired - Fee Related JP4395941B2 (ja) | 1999-09-29 | 1999-09-29 | 任意電圧発生構造及びこれを用いた固体撮像素子 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP4395941B2 (ja) |

| KR (1) | KR20010030546A (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4940517B2 (ja) * | 2001-08-07 | 2012-05-30 | ソニー株式会社 | 固体撮像装置およびその製造方法 |

| JP2005277398A (ja) * | 2004-02-25 | 2005-10-06 | Sony Corp | Ccdリニアセンサ |

| KR100594262B1 (ko) * | 2004-03-05 | 2006-06-30 | 삼성전자주식회사 | 바이어스 회로, 이를 구비한 고체 촬상 소자 및 그 제조방법 |

| KR101096439B1 (ko) | 2006-06-29 | 2011-12-20 | 주식회사 하이닉스반도체 | 반도체 소자의 퓨즈 박스 형성방법 |

-

1999

- 1999-09-29 JP JP31280699A patent/JP4395941B2/ja not_active Expired - Fee Related

-

2000

- 2000-09-29 KR KR1020000057446A patent/KR20010030546A/ko not_active Application Discontinuation

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001102533A (ja) | 2001-04-13 |

| KR20010030546A (ko) | 2001-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4536949A (en) | Method for fabricating an integrated circuit with multi-layer wiring having opening for fuse | |

| JP4395941B2 (ja) | 任意電圧発生構造及びこれを用いた固体撮像素子 | |

| JP2001176975A (ja) | 半導体装置及びその製造方法 | |

| JP2002026675A (ja) | 弾性表面波装置及びその製造方法 | |

| JPH08227901A (ja) | 半導体装置の製造方法 | |

| JP3037019B2 (ja) | 半導体装置の製造方法 | |

| JPH0332230B2 (ja) | ||

| JPH04243150A (ja) | ポリシリコンヒューズ | |

| JP3039163B2 (ja) | 半導体装置の製造方法 | |

| JP2001102533A5 (ja) | ||

| JPH01273347A (ja) | 半導体装置 | |

| JPH058578B2 (ja) | ||

| JPH05235275A (ja) | 集積回路装置 | |

| JP2004363341A (ja) | 半導体装置及びその製造方法 | |

| JPH07153910A (ja) | 半導体基板上の絶縁構造 | |

| JPH02119170A (ja) | 半導体装置の製造方法 | |

| JPH0669422A (ja) | 半導体集積回路 | |

| JP2607677Y2 (ja) | 弾性表面波装置 | |

| JPS5895825A (ja) | 半導体装置 | |

| JPH02170537A (ja) | 半導体装置 | |

| JPS60113944A (ja) | 半導体集積回路装置 | |

| JPS63202950A (ja) | 半導体集積回路装置 | |

| JPS61290757A (ja) | 半導体装置 | |

| JPH10163324A (ja) | 半導体装置の製造方法 | |

| JPH0563135A (ja) | 保護素子付リードフレーム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20051207 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060320 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060320 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090526 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090724 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090929 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091012 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121030 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |