JP4315744B2 - 積層体及び半導体装置の製造方法 - Google Patents

積層体及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4315744B2 JP4315744B2 JP2003180676A JP2003180676A JP4315744B2 JP 4315744 B2 JP4315744 B2 JP 4315744B2 JP 2003180676 A JP2003180676 A JP 2003180676A JP 2003180676 A JP2003180676 A JP 2003180676A JP 4315744 B2 JP4315744 B2 JP 4315744B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- etching

- thin film

- release layer

- semiconductor thin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 159

- 238000004519 manufacturing process Methods 0.000 title claims description 35

- 238000005530 etching Methods 0.000 claims description 205

- 239000010409 thin film Substances 0.000 claims description 124

- 239000000758 substrate Substances 0.000 claims description 118

- 229910001218 Gallium arsenide Inorganic materials 0.000 claims description 86

- 239000000203 mixture Substances 0.000 claims description 34

- 238000005253 cladding Methods 0.000 claims description 30

- 238000000034 method Methods 0.000 claims description 18

- 238000000926 separation method Methods 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 456

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 40

- 239000000463 material Substances 0.000 description 25

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 18

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 12

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 9

- KRKNYBCHXYNGOX-UHFFFAOYSA-N citric acid Chemical compound OC(=O)CC(O)(C(O)=O)CC(O)=O KRKNYBCHXYNGOX-UHFFFAOYSA-N 0.000 description 9

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 8

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 8

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 7

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 5

- QOSATHPSBFQAML-UHFFFAOYSA-N hydrogen peroxide;hydrate Chemical compound O.OO QOSATHPSBFQAML-UHFFFAOYSA-N 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 239000012466 permeate Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000002040 relaxant effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000003628 erosive effect Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- IXCSERBJSXMMFS-UHFFFAOYSA-N hcl hcl Chemical compound Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

Images

Landscapes

- Weting (AREA)

- Led Devices (AREA)

- Recrystallisation Techniques (AREA)

- Semiconductor Lasers (AREA)

- Drying Of Semiconductors (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置の製造方法に関し、特に基板の上に半導体薄膜を形成した後分離して半導体装置を製造し、基板の再利用を可能にする半導体装置の製造方法に関する。本発明はまた、上記のような製造方法で用いられる積層体に関する。本発明は例えば半導体薄膜により発光素子の列を形成する場合に用いられる。

【0002】

【従来の技術】

発光素子を安価に形成する方法として、サファイア基板上に中間層を形成し、その上に化合物半導体層を形成し、そこに発光部を形成する方法がある(特許文献1)。

【0003】

【特許文献1】

特開平7−202265号公報

【0004】

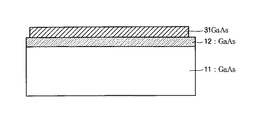

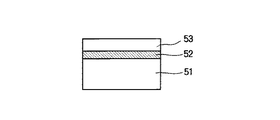

また、化合物半導体としてGaAs系の半導体を用いる場合には、図22乃至図23に示すように行うことが知られている。

【0005】

この方法においては、まず図22に示したように、GaAs基板51の上に厚さ約5μmのAl0.7Ga0.3As層52を形成し、その上に厚さ約30μmのGaAs薄膜53を形成する。

【0006】

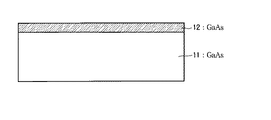

その後、図23に示すように、弗酸(HF)に浸すことによって、選択的にAl0.7Ga0.3As層52をエッチング除去し、GaAs薄膜53をGaAs基板51から分離することができるものである。

【0007】

【発明が解決しようとする課題】

上で述べた方法によって半導体薄膜を剥離する場合、例えば、半導体薄膜を剥離して残った半導体基板を、半導体薄膜を得るための基板として再利用できれば、材料の利用効率を向上させることができると考えられる。

【0008】

しかし、上記した剥離方法を用いて、大きな口径の基板から多数の半導体薄膜を得る方法としては、例えば図24に示すように、エッチング溝55の形成により多数の薄膜領域56に分割し、この溝55によって、剥離のための選択エッチング層(例えば上記のAl0.7Ga0.3As層)52を露出させ、選択エッチング層52をエッチング除去して多数の半導体薄膜を得る方法が考えられる。しかし、GaAs薄膜53をエッチングするエッチャントにはAlGaAs層52もエッチングされる。例えば、一般的によく知られている、GaAs薄膜53をエッチングする燐酸過水(燐酸+過酸化水素水+水)や硫酸過水(硫酸+過酸化水素水+水)は、GaAs薄膜53だけでなく、AlGaAs層52もエッチングする。したがって、上記の分割のための溝55を形成する場合、エッチングがAlGaAs層52を貫通してGaAs基板51まで及ぶことがあるという問題がある。エッチングが基板51にまで及ぶと、基板51の再利用に先立ち、表面を平坦化するための処理が必要となり、効率的ではない。

【0009】

本発明は、上で述べた課題を解決し、効率的に基板の再利用ができる半導体装置の製造方法、及びそのような製造方法に用いられる積層体を提供することを目的とする。

【0010】

本発明は、GaAsからなる基板と、前記基板の上に形成され、Al q Ga 1−q As(1≧q≧0)で表される組成を有する第2の剥離層と、前記第2の剥離層の上に形成され、(Al x Ga 1−x ) y In 1−y P層(1≧x≧0、1≧y≧0)で表される組成を有するエッチングストッパ層と、前記エッチングストッパ層の上に形成され、Al p Ga 1−p As(1≧p≧0)で表される組成を有する第1の剥離層と、前記第1の剥離層上に形成された半導体薄膜とを有し、前記半導体薄膜の各層が、Al z Ga 1−z As(1≧z≧0)で表される組成を有し、前記半導体薄膜の各層のAl組成比z、第1の剥離層のAl組成比p、第2の剥離層のAl組成比qについて、z<p、z<qであることを特徴とする積層体を提供する。

【0011】

【発明の実施の形態】

以下図面を参照して本発明の実施の形態を説明する。各図は実施の形態の特徴を模式的に示したもので、寸法関係や位置関係の詳細などを限定するものではない。

以下の実施の形態の半導体薄膜は、発光ダイオードアレイ(LEDアレイ)を構成するものであり、他の半導体基板にボンディングされて当該他の半導体基板に形成された駆動回路と接続されて、上記他の基板に形成された駆動回路と、半導体薄膜内に形成された被駆動素子としてのLEDアレイとから成る複合半導体装置を形成するために用いられるものである。

以下の実施の形態では、半導体薄膜が複数の層から成るが、本発明は半導体薄膜が単層で構成される場合にも適用することができる。

【0012】

第1の実施の形態

図1乃至図4は本発明の第1の実施の形態の製造方法を説明するための概略断面図及び概略平面図である。以下、これらの図を参照しながら第1の実施の形態について説明する。

【0013】

最初に、図1に示すように、半導体基板、例えばn型GaAs基板11と、その上に形成された、例えばGaAsバッファー層12と、その上に形成された例えば(AlxGa1−x)yIn1−yPエッチングストッパ層13と、その上に形成された例えばAlAs剥離層14と、その上に形成された例えばn型GaAs下側コンタクト層15と、その上に形成された例えばn型AlsGa1−sAs下側クラッド層16と、その上に形成された例えばp型AltGa1−tAs活性層17と、その上に形成された例えばp型AluGa1−uAs上側クラッド層18と、その上に形成された例えばp型GaAs上側コンタクト層19とを有する積層体を用意する。

【0014】

そのような積層体は、以下のようにして形成することができる。即ち、半導体基板、例えばn型GaAs基板11上に、例えばGaAsバッファー層12、例えば(AlxGa1−x)yIn1−yPエッチングストッパ層13、例えばAlAs剥離層14、例えばn型GaAs下側コンタクト層15、例えばn型AlsGa1−sAs下側クラッド層16、例えばp型AltGa1−tAs活性層17、例えばp型AluGa1−uAs上側クラッド層18、例えばp型GaAs上側コンタクト層19を順に形成する。

これらの層は、例えば、有機金属気相成長法(MOCVD法)でエピタキシャル成長させることにより、形成することができる。

【0015】

ここで、下側コンタクト層15、下側クラッド層16、活性層17、上側クラッド層18、上側コンタクト層19は、後に基板11から剥離により分離されて、他の半導体基板にボンディングされる半導体薄膜20を構成する。図示の例の半導体薄膜20はLEDアレイとして用いられるものであり、下側コンタクト層15及び上側コンタクト19は、半導体薄膜20を剥離した後に、LEDにおける電極コンタクト層としての役割を担う。

【0016】

一方、剥離層14は、基板11から半導体薄膜20を剥離により分離するために、選択的にエッチングされて溶解乃至分解されるものである。また、エッチングストッパ層13は、後述のように、半導体薄膜20を分割する溝を形成するためのエッチングに際し、エッチングを停止させるものである。

バッファー層12は、基板11と半導体薄膜20との格子定数のミスマッチを緩和するとともに、基板11と半導体薄膜20の熱膨張率の差による応力を緩和するためのものである。

【0017】

なお、活性層を上下2つの層に分け、下側の活性層をn型とし、上側の活性層をp型とすることとしても良い。

さらに、下側コンタクト層15及び下側クラッド層16をp型とし、上側のクラッド層18及び上側コンタクト層をn型としても良い。この場合において、活性層を上下2つの層に分ける場合には、下側をp型とし、上側をn型とする。

【0018】

なおまた、上記のようなヘテロ接合型のLEDとする代わりに、ホモ接合型のLEDを構成することもできる。この場合、各層をエピタキシャル成長させた後、最上層の表面から固相拡散法により不純物拡散を行って活性層内にpn接合を形成する。

また、同一組成のエピタキシャル層を形成し、該エピタキシャル層内にpn接合を形成したLEDであってもよい。例えば、エピタキシャル半導体層として、n型GaAs層を形成し、Znを拡散してもよいし、n型GaAs層/p型GaAs層を積層してもよい。

【0019】

図1に示す積層体乃至は積層構造物を形成した後、素子分離(例えば発光領域以外の部分の活性層までをエッチング除去する)或いは上記の拡散領域の形成などを行うことにより、半導体素子を形成する。半導体薄膜20は、以下に詳述するように、溝21の形成により複数の半導体薄膜片に分割されるものであり、半導体素子は、各半導体薄膜片形成予定領域内に形成される。本実施の形態では、各半導体薄膜がLEDアレイを構成する場合を想定しており、各半導体薄膜片内に複数のLED素子から成るLEDアレイが形成される。

【0020】

なお、本実施の形態の説明では、後述するように、各半導体薄膜片形成予定領域内に半導体素子、例えばLEDアレイを形成した後、各半導体薄膜片への分離および第1の基板からの該半導体薄膜片の剥離を行う製造工程について説明しているが、次のようにしてもよい。すなわち、溝21によって半導体薄膜片に分割した後に第1の基板から該半導体薄膜片を剥離し、第2の基板上にボンディングした後に、半導体薄膜内に半導体素子を形成(例えば、発光領域以外の部分の少なくとも活性層までをエッチング除去し、必要な層間絶縁膜形成・加工、電極形成、配線形成などを行う)することもできる。

【0021】

上記のように半導体素子を形成した後、図2及び図3に示すように、エッチングを行って溝21を形成する。このエッチングは、溝21により半導体薄膜20を複数の半導体薄膜片に分割するために行なうものであり、それぞれの半導体薄膜片が占める領域が符号Rで示してある。図2では、複数の半導体薄膜片や領域Rのうち2つのみが示され、図3では6つのみが示されている。なお、本明細書では、混同が生じないと思われる限り、分割により得られる半導体薄膜片も半導体薄膜と呼んでいる。

【0022】

エッチングを行うには、まず上側コンタクト層19の上に図示しないフォトマスクを使って、フォトレジストなどの感光性材料を使ってエッチングマスクパターンを形成し、このマスクパターンを通してエッチング液に浸す。

【0023】

エッチング液としては、半導体薄膜20を構成する各層のエッチング速度が高く、半導体薄膜20と基板11の間に位置するストッパ層13のエッチング速度が低いもの、例えば硫酸過水(硫酸/過酸化水素水/純水=16/1/1)、燐酸過水(燐酸/過酸化水素水/水=12/8/80)、又はクエン酸過水を用いる。

逆に言えば、ストッパ層13は、半導体薄膜20のエッチングに用いられるエッチング液により比較的エッチングされにくい材料、即ち半導体薄膜20や剥離層14に比べ、上記のエッチング液によるエッチング速度が低い材料で構成されている。

【0024】

このエッチングは、図2に示すように、エッチングストッパ層13の上面まで進行したときに終了させる。即ち、図2に示す状態では、エッチング溝21が剥離層14を貫通して剥離層14をその厚さ方向において完全に露出させる一方、(AlxGa1−x)yIn1−yPエッチングストッパ層13で止まっている。

上記のようなエッチング速度の違いにより、エッチング時間などのエッチング条件を厳密に制御しなくても、ストッパ層13の上面でエッチングの進行を確実に止めることができる。

【0025】

エッチング溝21の幅Gwは、例えば約50μm乃至100μmである。エッチング液の浸透を良好にするには、溝の幅が広い方が良いが、基板11や半導体薄膜20の材料の有効活用の観点からは溝の幅が小さい方が良い。

分割領域Rの寸法Ra×Rbは、約100μm×8mmである。分割領域の大きさは適宜設計により選択することができ、例えば、約5mm×5mmから10mm×15mmのようなサイズであってもよい。

【0026】

次にエッチングにより剥離層14を除去することにより、基板11から半導体薄膜20を剥離する。

このエッチングは、図2及び図3に示す構造物を、エッチング液で満たされたエッチング液槽(図示しない)内に浸漬することにより行う。

エッチング液としては、剥離層14のエッチング速度が高く、半導体薄膜20及びエッチングストッパ層13のエッチング速度が低いもの、例えば10%の弗酸(10%−HF)を用いる。

逆に言えば、エッチングストッパ層13は、剥離層14のエッチングに用いられるエッチング液により比較的エッチングされにくい材料、即ち剥離層14に比べ、上記のエッチング液によるエッチング速度が低い材料で構成されている。

【0027】

エッチングにより基板11から剥離された薄膜20は、例えば図示しない別の半導体基板(例えばSi基板)にボンディングされて、複合半導体装置となる。

【0028】

上記のようなエッチングを行って、薄膜20を除去すると、図4に示すように、ストッパ層13と、バッファー層12と、基板11が残る。

図4において、符号23は、分割された半導体薄膜20が除去された跡を示し、符号22は、エッチング溝21の領域を示す。

【0029】

図4に示す構造物に対し、次に、ストッパ層13をエッチングにより選択的に除去して、バッファー層12の表面を露出させる。

このエッチングには、例えば塩酸(HCl)系のエッチング液を用いる。

これにより、バッファー層12を侵食することなくストッパ層13を選択的にエッチングすることができる。

【0030】

このようにして、バッファー層12のみが残った基板11(即ち基板11とバッファー層12との組み合わせ)は、再利用される。即ち、このバッファー層12の上に、図1で示したのと同様に、層13乃至19を順次形成し、その後図2乃至図4を参照して説明したのと同様の処理を繰り返すことにより、再び半導体薄膜20を得ることができる。

【0031】

以下、半導体薄膜20の各層、エッチングストッパ層13、剥離層14の構成及びその特性、特にそのエッチング特性、格子整合性などについてさらに詳しく説明する。

【0032】

半導体薄膜20を構成する、GaAs下側コンタクト層15、AlsGa1−sAs下側クラッド層16、AltGa1−tAs活性層17、AluGa1−uAsクラッド層18、GaAs上側コンタクト層19は例えば以下のような特徴を持つ。即ち、GaAs下側コンタクト層15がn型、AlSGa1−sAs下側クラッド層16がn型、AltGa1−tAs活性層17がp型、AluGa1−uAs上側クラッド層18がp型、GaAs上側コンタクト層19がp型であり、AlSGa1−sAs下側クラッド層16、AltGa1−tAs活性層17、AluGa1−uAs上側クラッド層18のAl組成比の関係が、s>t、u>tと定められており、いわゆるダブルヘテロ構造を形成しており、これにより、発光効率を高くしている。発光効率が高くなるのは、半導体薄膜20を剥離した後にGaAs下側コンタクト層15とGaAs上側コンタクト層19の間に電流が流されたとき、pn接合を介して注入されたキャリアが、ヘテロエピタキシャル界面のエネルギー障壁で閉じ込められ、この結果、キャリア再結合確率が高くなるためである。

【0033】

(AlxGa1−x)yIn1−yPエッチングストッパ層13は、半導体薄膜20にエッチング溝21を形成する際にエッチング溝21がGaAs基板11へ到達するのを防ぐものである。ストッパ層13を構成する(AlxGa1−x)yIn1−yPと、半導体薄膜20の各層を構成するGaAs及びAlGaAsとは、GaAs及びAlGaAsをエッチングすることができるエッチャント、例えば、硫酸過水、燐酸過水、クエン酸過水におけるエッチング速度に大きな差異があることが知られている。したがって、半導体薄膜20にエッチング溝21を設ける際、そのエッチング構21はGaAs基板11に到達することはない。言い換えると、半導体薄膜20にエッチング溝21を設ける際に、GaAs基板11へエッチング溝21が到達することを防ぐために、エッチング条件を厳密に制御する必要がない。エッチング条件を厳密に制御する必要がないため、確実にAlAs剥離層14を露出するように長めのエッチング時間を設定することができる。

【0034】

半導体エピタキシャル層を形成する場合、エピタキシャル層への欠陥発生を防止するためには、結晶の格子定数が整合するように材料を選択することが望ましい。例えば、GaAs基板11の上に、(AlxGa1−x)yIn1−yPエッチングストッパ層13を設け、さらにその上に半導体素子を形成するための半導体薄膜20を設ける場合、(AlxGa1−x)yIn1−yPエッチングストッパ層13の格子定数は基板11を構成するGaAsの格子定数と等しいことが望ましい。(AlxGa1−x)yIn1−yPは、0.48≦y≦0.52とすることにより、格子定数がGaAsの格子定数と等しくなることが知られている。(理想状態では、y=0.5の場合にGaAsと格子整合するが、分子線エピタキシー法(MBE法)、有機金属気相成長法、液層成長法などの半導体エピタキシャル成長層の作製方法やそれらの方法によるエピタキシャル層成長条件により、格子整合する組成比y(実際に分析・測定で得られるyの値)に若干の幅が生じる。)

【0035】

より具体的には、例えば、x=0、0.48≦y≦0.52、即ち、GayIn1−yP(0.48≦y≦0.52)とすることができる。従って、エピタキシャル層の欠陥発生の防止の観点からは、上記のように、エッチングストッパ層103の組成を、(AlxGa1−x)yIn1−yPにおいて、例えば、x=0、0.48≦y≦0.52とし、GayIn1−yP(0.48≦y≦0.52)とすることが望ましい。

【0036】

上記のように、基板上のすべてのエッチング溝21が(AlxGa1−x)yIn1−yPエッチングストッパ層13表面で止まっている場合、エッチング溝21の深さが均一であり、AlAs剥離層14の露出の程度も基板上の全領域で均一であるため、続いて行われる、半導体薄膜20の剥離のためのAlAs剥離層14のエッチングが、基板全域で均一に進行し、面積が大きな基板であっても良好な半導体薄膜20の剥離を行うことができる。

【0037】

図4に示すように半導体薄膜20の剥離後に残留している(AlxGa1−x)yIn1−yPエッチングストッパ層13は、例えば塩酸系のエッチング液によって、GaAsバッファー層12をエッチングすることなく選択的にエッチング除去することができる。選択的に(AlxGa1−x)yIn1−yPエッチングストッパ層13をエッチング除去できるので、面積が大きい基板であっても基板表面全体にわたり、均一な状態のGaAsバッファー層12の表面を露出させることができる。

【0038】

したがって、再びGaAsバッファー層上に、例えばMOCVD法により良好な半導体エピタキシャル層を形成することができる。

【0039】

以上詳細に説明したように、上記の第1の実施の形態では、半導体薄膜20をGaAs基板11から剥離するためのAlAs層剥離14とGaAs基板11の間に、半導体薄膜20を構成する各層をエッチングするエッチング液に対して非エッチング性を有する(AlxGa1−x)yIn1−yPエッチングストッパ層13を設けた積層体を形成し、これを用いて半導体装置を形成することとしたので、以下の効果が得られる。

【0040】

まず、基板11上に、半導体薄膜20を複数の領域に分割するためのエッチング溝21を設けても、エッチング溝21がGaAs基板11に到達するのを防止することができ、GaAs基板11を効率的に再利用することができる。

【0041】

また、厳密なエッチング条件の制御によることなく、エッチング溝21による剥離層14の露出状態を基板全面で均一にすることができ、面積が大きな基板であっても基板全面で良好な半導体薄膜の剥離を行なうことができる。

【0042】

第2の実施の形態

上記の第1の実施の形態では、(AlxGa1−x)yIn1−yPストッパ層13の上にAlAs剥離層14を形成した積層体を用いているが、図5に示すように、ストッパ層13の上の剥離層14を省略し、代わりにストッパ層13の下側に剥離層24を設けた積層体を用いても良い。言い換えると、ストッパ層13と剥離層(14、24)の積層順を入れ替えても良い。

即ち、図5に示すように、半導体基板、例えばn型GaAs基板11と、その上に形成された、例えばGaAsバッファー層12と、その上に形成された例えばAlAs剥離層24と、その上に形成された例えば(AlxGa1−x)yIn1−yPエッチングストッパ層13と、その上に形成された例えばn型GaAs下側コンタクト層15と、その上に形成された例えばn型AlsGa1−sAs下側クラッド層16と、その上に形成された例えばp型AltGa1−tAs活性層17と、その上に形成された例えばp型AluGa1−uAs上側クラッド層18と、その上に形成された例えばp型GaAs上側コンタクト層19とを有する積層体を用意することとしても良い。

【0043】

上記のようにストッパ層13と剥離層(14、24)の入れ替えを行った場合、図6に示すように、エッチング溝21に形成に当たり、エッチングがストッパ層13の上面まで進行したときにエッチングを終了させる。従って、溝21は剥離層24を貫通せず、剥離層24は基板11の周縁部以外では露出されていない。

【0044】

第1の実施の形態について述べたのと同じく、溝21を形成するためのエッチング液として、半導体薄膜20を構成する各層のエッチング速度が高く、ストッパ層13のエッチング速度が低いものを用いることにより、エッチング時間などのエッチング条件を厳密に制御しなくても、エッチングをストッパ層13の表面で停止させることができる。

【0045】

溝21の形成の次に、AlAs剥離層24をエッチングすることにより、図7に示したように、半導体薄膜20およびストッパ層13を剥離する。このエッチングに際しては、エッチング液は、基板11の周縁から中央部に向け、剥離層24に沿って浸透する。この剥離を行うと、図7に示した通り、バッファー層12とGaAs基板11が残留する。

【0046】

AlAs剥離層24のエッチングの工程ではAlAsのエッチング速度が高く、基板11やバッファー層12を構成するGaAsのエッチング速度が低いもの(例えばエッチング速度比が約107倍)エッチング液(例えば弗酸)を用いるので、GaAs基板11上のGaAsバッファー層12の表面はほとんどエッチングの影響を受けず、再利用が容易である。即ち、GaAs基板11や、その上のGaAsバッファー層12の表面は、直ちに再度エピタキシャル成長させるのに支障がない程度に十分平坦で良好な状態を有する。

【0047】

基板11から分離された半導体薄膜20とストッパ層13の組合せは、例えば塩酸系のエッチング液に浸漬することにより、選択的にストッパ層13の全体を溶解させ、これにより、エッチング溝21で分割されている各半導体薄膜20を互いに分離し、図8に示したように、独立した半導体薄膜を得ることができる。

【0048】

なお,第1の実施の形態及び第2の実施の形態では、GaAs基板11上にGaAsバッファー層12を設けた。バッファー層12はその上に形成されるエピタキシャル層を良好なものとするために設けられるが、バッファー層12を省略し、基板11の上に直接(AlxGa1−x)yIn1−yPストッパ層13又は剥離層14を形成しても良い。

【0049】

また、上記の第1及び第2の実施の形態では、バッファー層12が残った基板11を再利用しているが、バッファー層12を例えば、ケミカル・メカニカル・ポリッシュなどの方法により除去して、基板11のみを再利用することとしても良い。この場合、基板11上に改めてバッファー層12を形成し、その上に層13乃至19を形成する。

【0050】

さらに、基板11は、GaAs基板に限定されず、(AlxGa1−x)yIn1−yPストッパ層13と選択的なエッチングが可能なものであれば、他の材料の基板であっても良い。

【0051】

第1の実施の形態では、エッチングストッパ層13について、エピタキシャル成長において格子整合が取れるような材料を用いているが、基板材料の選択によって、半導体薄膜20とは格子整合するが、基板11とは格子整合しないような組成を有する(AlxGa1−x)yIn1−yPストッパ層13を用いてもよい。また、(AlxGa1−x)yIn1−yPストッパ層13の上にバッファー層を設け半導体薄膜20との格子定数のミスマッチを緩和するようにすることできる。

【0052】

第3の実施の形態

第1の実施の形態では、最初に図1に示す積層体を形成したが、第3の実施の形態では、最初に図9に示す積層体を形成する。

この積層体は、半導体基板、例えばn型GaAs基板11と、その上に形成された、例えばGaAsバッファー層12と、その上に形成された例えばAlAs剥離層31と、その上に形成された例えば(AlxGa1−x)yIn1−yPエッチングストッパ層13と、その上に形成された例えばAlAs剥離層14と、その上に形成された例えばn型GaAs下側コンタクト層15と、その上に形成された例えばn型AlsGa1−sAs下側クラッド層16と、その上に形成された例えばp型AltGa1−tAs活性層17と、その上に形成された例えばp型AluGa1−uAs上側クラッド層18と、その上に形成された例えばp型GaAs上側コンタクト層19とを有する。

図1に対する図9の違いは、ストッパ層13と、バッファー層12の間に、第2の剥離層31が設けられていることである。なお、剥離層14を、第2の剥離層31との区別のため、第1の剥離層と呼ぶ。

【0053】

この第2の剥離層31は、第2の実施の形態の剥離層31と同様に例えばAlAs層で形成される。

【0054】

図9の積層体は、基板11の上に、バッファー層12、第2の剥離層31、エッチングストッパ層13、第1の剥離層14、下側コンタクト層15、下側クラッド層16、活性層17、上側クラッド層18、上側コンタクト層19を順にエピタキシャル成長させることにより得られる。

【0055】

図9の積層体を形成した後、第1の実施の形態について説明したのと同様、エッチング溝21を形成する(図10)。このエッチング溝21は、ストッパ層13の表面に達する深さとする。こうすることで、第1の剥離層14がその厚さ方向において完全に露出される。

【0056】

エッチング溝21を形成するためのエッチング液としては、エッチングストッパ層13のエッチング速度が低く、薄膜20を構成する各層のエッチング速度が高いエッチング液、例えば、第1の実施の形態で説明したのと同様、硫酸過水、燐酸過水、クエン酸過水を使用することができる。

【0057】

第1の実施の形態に関して説明した通り、エッチング溝21の形成のためのエッチング時間として、例えば大面積の基板(ウエハ)全面にわたってエッチング溝21の深さが不十分にならないように、エッチング時間を十分長くとっても、(AlxGa1−x)yIn1−yPエッチングストッパ層13の表面でエッチングを停止することができる。

【0058】

次に、図11に示すように、半導体薄膜20をGaAs基板11から剥離する。これは、第1の実施の形態に関して述べたように、第1の剥離層14を弗酸(HF)によってエッチングすることによって行われる。

【0059】

図11に示すように、エッチング溝21によって細分化された半導体薄膜20下の第1の剥離層14も細分化されているため、エッチング液はエッチング溝21から第1の剥離層14に高速に浸透する。

【0060】

一方、第2の剥離層31は、基板(ウエハ)全面にわたり(AlxGa1−x)yIn1−yPストッパ層13とGaAs基板11に挟まれているため、上下方向においてはエッチング液から遮蔽されており、基板11の周縁から中央に向けて剥離層31に沿ってエッチングが進行する。そのため、図11に示したように、第1の剥離層14のエッチング除去が終わって、半導体薄膜20がGaAs基板11から分離された時点では、第2の剥離層層31は周縁付近の部分のみが除去されており、大部分が残留している。

【0061】

ここで、第2の剥離層の層厚さを第1の剥離層の層厚さ以下にして第2の剥離層へのエッチング液の浸透が遅くなるようにし、第1の剥離層のエッチングの際に確実に第2の剥離層が残留するようにすることができる。また、第2の剥離層の材料を第1の剥離層の材料と同等の材料とする、あるいは第2の剥離層のエッチング速度が第1の剥離層のエッチング速度よりも遅くなるようにして、第1の剥離層のエッチングの際に確実に第2の剥離層が残留するようにすることができる。この場合には、例えば第1の剥離層の材料をAlsGa1−sAs(1≧s>0)、第2の剥離層の材料をAltGa1−tAs(1≧t>0)として、s≧tとすることができる。

【0062】

半導体薄膜20を剥離した後、(AlxGa1−x)yIn1−yPエッチングストッパ層13を例えば、塩酸系のエッチング液によってエッチング除去して第2の剥離層31を露出させる(図12)。

【0063】

上記のように、第2の剥離層31を露出させた後、例えば、10%弗酸によって第2の剥離層31をエッチング除去する(図13)。

【0064】

弗酸による第2の剥離層31のエッチングでは、バッファー層12を構成するGaAsの弗酸に対するエッチング速度は、剥離層31を構成するAlAsの弗酸に対するエッチング速度と比較して極めて遅い(約1/107)ため、GaAsバッファー層12はほとんど侵食されず、AlAs剥離層31をエッチング除去した後のGaAsバッファー層12の表面はきわめて平滑である。

【0065】

なお、上記のように、図11の構造物に対し、塩酸系のエッチング液でエッチングを行ってストッパ層13を除去した後、その後弗酸をエッチング液として剥離層31をエッチング除去する代りに、図11の構造物に対し、弗酸を用いたエッチングによって第2の剥離層31を除去することにより、第2の剥離層31とその上にあるストッパ層13を同時に除去することとしても良い(図14)。この場合には、基板11の周縁部から中心に向けて、第2の剥離層31に沿ってエッチング液が浸透する。

【0066】

また、第1の剥離層14の除去と第2の剥離層31の除去とは同じエッチング液(弗酸)を用いて行うことができるものであり、これらを同時に(一つの工程として)行うことができる。この場合、第1の剥離層14及び第2の剥離層31の組成、厚さなどを適宜選択することにより、第1の剥離層14の除去と第2の剥離層31の除去とが略同時に完了するようにすることもできる。これについては、後に詳しく説明する。

【0067】

上記の第3の実施の形態によれば、エッチングストッパ層13とバッファー層12の間に第2の剥離層31を介在させたので、第2の剥離層31のエッチング除去の際、バッファー層12がエッチングの影響をほとんど受けず、剥離層31(及びストッパ層13)の除去の後に、十分に平坦な表面を有するバッファー層12を得ることができる。従ってバッファー層12を備えた基板11を再利用する際、バッファー層12上に良好なエピタキシャル層を成長することができる。

【0068】

なお、第3の実施の形態において、GaAsバッファー層12を設けず、基板11上に直接第2の剥離層31を設けることとしても良い。その場合には、剥離層31を剥離したときに、GaAs基板11の表面が極めて平坦なものとなるため、基板を再利用する際、GaAs基板11表面に、良好なエピタキシャル層を成長することができる。

【0069】

第4の実施の形態

第3の実施の形態では、最初に図9に示す積層体を形成したが、代りに、図15に示す積層体を形成することとしても良い。

この積層体は、半導体基板、例えばn型GaAs基板11と、その上に形成された、例えばGaAsバッファー層12と、その上に形成された例えばAlAs剥離層31と、その上に形成された例えばGaAsバッファー層33と、その上に形成された例えば(AlxGa1−x)yIn1−yPエッチングストッパ層13と、その上に形成された例えばGaAsバッファー層34と、その上に形成された例えばAlAs剥離層14と、その上に形成された例えばn型GaAs下側コンタクト層15と、その上に形成された例えばn型AlsGa1−sAs下側クラッド層16と、その上に形成された例えばp型AltGa1−tAs活性層17と、その上に形成された例えばp型AluGa1−uAs上側クラッド層18と、その上に形成された例えばp型GaAs上側コンタクト層19とを有する。

【0070】

図9に対する図15の違いは、ストッパ層13と、下側の剥離層31の間に第2のバッファー層33が設けられ、ストッパ層13と、上側の剥離層14の間に第3のバッファー層34が設けられていることである。第2及び第3のバッファー層33及び34との区別のため、バッファー層12を第1のバッファー層と呼ぶ。

【0071】

第2のバッファー層33及び第3のバッファー層34はともにGaAsで形成されている。

【0072】

図15の積層体は、基板11の上にバッファー層12、第2の剥離層31、バッファー層33、ストッパ層13、バッファー層34、第1の剥離層14、コンタクト層15、クラッド層16、活性層17、クラッド層18、コンタクト層19を順にエピタキシャル成長させることにより得られる。

【0073】

図15に示す積層体を形成した後、第1の実施の形態について説明したのと同様に、エッチング溝21を形成し、第1の剥離層14を露出させる(図16)。

エッチング溝21は、少なくともAlAs層14を露出する深さとする。ここに示す図では、例えば、ストッパ層13の表面に達する深さとする。

【0074】

次に、第1の剥離層14を弗酸でエッチング除去して、半導体薄膜20を剥離する(図17)。

【0075】

次に、弗酸で第2の剥離層31をエッチング除去し、GaAsバッファー層12を露出させる(図18)。弗酸による剥離層31のエッチング除去の際は、エッチング液(弗酸)は、基板11の周縁から中央に向けて第2の剥離層31に沿って浸透する。

上記の第4の実施の形態でも上記第3の実施の形態と同様の効果が得られ、また同様の変形が可能である。

【0076】

なお、第4の実施の形態では、第2のバッファー層あるいは第3のバッファー層を設けてからストッパ層、第1の剥離層を設けるようにしたので、第1の剥離層および半導体薄膜層の品質を向上させることができ、半導体薄膜の剥離界面の状態をよりよくすることができる。また、より品質の高い半導体素子が得られる。

【0077】

第5の実施の形態

第1の実施の形態では、最初に図1に示す積層体を形成したが、代わりに図19に示す積層体を形成することとしても良い。

この積層体は、半導体基板、例えばシリコン(Si)基板41と、その上に形成された、例えばGaAsバッファー層12と、その上に形成された例えばAlAs剥離層14と、その上に形成された例えばn型GaAs下側コンタクト層15と、その上に形成された例えばn型AlsGa1−sAs下側クラッド層16と、その上に形成された例えばp型AltGa1−tAs活性層17と、その上に形成された例えばp型AluGa1−uAs上側クラッド層18と、その上に形成された例えばp型GaAs上側コンタクト層19とを有する。

図1に対する図19の違いは、GaAs基板11の代わりにシリコン(Si)基板41が用いられていること、ストッパ層13が設けられていないことである。

【0078】

図19の積層体は、基板41の上に、バッファー層12、剥離層14、コンタクト層15、クラッド層16、活性層17、クラッド層18、コンタクト層19を順にエピタキシャル成長させることにより得られる。

【0079】

本実施の形態のように、Si基板41上に化合物半導体の半導体薄膜を形成する場合には、半導体薄膜の欠陥密度を低減するため、バッファー層12を比較的厚く形成する必要がある。

【0080】

図19の積層体を形成した後、第1の実施の形態について説明したのと同様にして、エッチング溝21を形成して剥離層14を露出させる(図20)。

エッチング溝21はGaAsバッファー層12の途中までとする。

エッチング液としては、半導体薄膜20、AlAs層14、バッファー層12をエッチングできるもの、例えば燐酸過水(燐酸+過酸化水素水+純水)を用いる。

【0081】

その後、例えば10%の弗酸によって剥離層14をエッチング除去し、半導体薄膜20を基板41から分離する(図21)。

【0082】

その後、Si基板41はエッチングされないエッチング液、例えば、燐酸過水を用いて、バッファー層12を選択的にエッチング除去する。

その結果、表面が平坦なSi基板41が得られる(図21)。

このSi基板41は平坦な表面を有するものであり、再利用することができる。

【0083】

なお、上記の例では、図20に示すように、エッチング溝21をバッファー層12の途中までとしたが、本実施の形態ではバッファー層12が比較的厚いのでエッチング時間等の制御を正確に行なわなくても、エッチングの進行をバッファー層12の途中で止めることができる。

【0084】

第5の実施の形態では、Si基板41を使用したもので、基板41上の半導体薄膜にエッチング溝21を設け、個別半導体薄膜領域に細分化しても、エッチング溝21はSi基板41を侵食することがなく、半導体薄膜20剥離後に平坦なSi基板41を得ることができる。

【0085】

なお、第1及び第2の実施の形態(図1乃至図8)について述べた変形のいくつかは、他の実施の形態にも適用可能である。

【0086】

例えば、第1及び第2の実施の形態(図1乃至図8)について述べたように、第3及び第4の実施の形態(図9乃至図18)においても、基板11は、GaAs基板に限定されず、(AlxGa1−x)yIn1−yPストッパ層13と選択的なエッチングが可能なものであれば、他の材料の基板であっても良い。

【0087】

また、第1、第2及び第3の実施の形態(図1乃至図14)について述べたように、第4及び第5の実施の形態(図5乃至図21の実施の形態)においても、バッファー層12を省略しても良い。

また、第4の実施の形態で、第2のバッファー層33を省略してもよい。

【0088】

なおまた、上記の各実施の形態では、剥離層14として、AlAsで形成されたものを用いているが、剥離層14の材料は、半導体薄膜20を構成する層と格子整合する材料であって、半導体薄膜20を構成する層に対するエッチング速度が低いエッチング液で高速にエッチングされる材料であれば、他の材料であっても良い。

例えば、AlAsの代りに、AlpGa1−pAs(1>p>0)を用いることができる

なお、AlAsは、pが1≧p>0の範囲の値をとり得るとすれば、AlpGa1−pAs(1≧p>0)でp=1とした場合と考えることもできる。

ただし、選択的エッチングのため、半導体薄膜20の下側クラッド層16、活性層17、上側クラッド層18を構成するAlGaAsよりもAlの組成比を高くすることが必要である。即ち、半導体薄膜20の下側クラッド層16、活性層17、上側クラッド層18の材料をAlzGa1−zAsで表す(下側クラッド層16についてはz=s、活性層17についてはz=t、上側クラッド層18についてはz=u)とするとき、

z<p

を満たすことが必要である。

【0089】

さらに、図9乃至図14の実施の形態、及び図15乃至図18の実施の形態においては、

第2の剥離層の組成をAlqGa1−qAs(1>q>0)で表すとき、

z<q

を満たすことが必要である。第1の剥離層のエッチングの際に第2の剥離層の大部分のエッチングが完了するためには、少なくとも以下のような条件とすることが望ましい。すなわち、p<qであることが望ましい。

さらに、第1の剥離層14の層厚よりも第2の剥離層31の層厚が大きいことが望ましい。

さらに、第2のエッチング液(弗酸)に対して、第1の剥離層14のエッチング速度よりも第2の剥離層31のエッチング速度が高いことが望ましい。

さらに、第1の剥離層14のエッチング完了時間と第2の剥離層31のエッチング完了時間をほぼ一致させて、1回のエッチングによって、第1の剥離層と第2の剥離層のエッチングを完了させることができる。

【0090】

上記の点についてさらに詳しく説明する。

剥離層14及び31がAlGaAsで構成されている場合、Alの組成比が大きい程、第2のエッチング液として用いられる弗酸によるエッチング速度が高くなる。そのため、第1の剥離層14のAl組成比p及び第2の剥離層31のAl組成比qが、

p<q

を満たすようにすれば、第1の剥離層14よりも第2の剥離層31のエッチング速度を高くすることができる。

【0091】

また、第1の剥離層14はエッチング溝21により個別の島状に分離された半導体薄膜20の下に位置し、多数の溝21に露出されているのに対し、第2の剥離層31はエッチングストッパ層13により被覆され、基板11の縁部において露出されているに過ぎない。したがって、この状態で第1及び第2の剥離層14及び31をエッチングする場合には、弗酸が浸透しなければならない第1及び第2の剥離層14及び31の長さ(エッチング進行方向に沿う距離)L1及びL2は、

L2>L1

の関係を有する。ここで第1及び第2の剥離層14及び31のエッチング速度をS1、S2とすると、第1及び第2の剥離層14及び31のエッチングに要する時間T1、T2はそれぞれ

T1=L1/S1

T2=L2/S2

となる。上記のように、L2>L1の場合にはS2>S1となるような条件、すなわち第1の剥離層14に対して、第2の剥離層31のエッチング速度が高い条件を選べば、T1とT2とがおよそ等しい結果を得ることができる。T1=T2とすることができれば、第2のエッチング液による半導体薄膜20の剥離工程において、半導体薄膜20の剥離のみならず第2の剥離層の除去をほぼ同時に完了することができる。言い換えると、第1の剥離層14のエッチング除去による半導体薄膜20の剥離と第2の剥離層31の除去を一度に行い略同時に完了することができる。

【0092】

また、第1の剥離層14よりも第2の剥離層31を厚くすれば、第1の剥離層14と第2の剥離層31の材料が同じ場合、第2の剥離層31の材料のエッチング速度S2は、第1の剥離層の材料のエッチング速度よりも速くなる。即ち、S2>S1となる。したがって、上で説明したAlGaAsのAl組成比について

p<q

とする場合と同じように、第1の剥離層のエッチング時間T1=L1/S1と第2の剥離層のエッチング時間T2=L2/S2を略同等となるようにすることができる。この結果、第2のエッチング液による半導体薄膜20の剥離工程において、半導体薄膜20の剥離のみならず第2の剥離層の除去を略同時に完了することが可能となる。言い換えると、第1の剥離層14のエッチング除去による半導体薄膜20の剥離と第2の剥離層31の除去を一度に行い、略同時に完了することができる。

【0093】

なお、上記のように、第1の剥離層14のAl組成比pよりも第2の剥離層31のAl組成比qを大きくする代わりに、pとqとが互いに等しくないようにしてもよい。例えばp>qとしてもよい。

また、上記のように、第1の剥離層14の厚さよりも第2の剥離層31を厚くする代わりに、第1の剥離層14の厚さと第2の剥離層31の厚さがが互いに等しくないようにしてもよい。例えば、第1の剥離層14の厚さを第2の剥離層31の厚さよりも厚くしても良い。このような場合(p>qや、第1の剥離層14の厚さ>第2の剥離層31の厚さ、とした場合)には、第1の剥離層14のエッチングの際に第2の剥離層31のエッチングはほとんど進行せず、エッチングストッパ層13を全面エッチング(ウエハ全体にわたり全面露出したエッチングストッパ層13を全面同時にエッチング)した後、第2の剥離層31を全面エッチング(ウエハ全面にわたり全面露出した第2の剥離層31を全面同時にエッチング)することができる。

【0094】

また、上記の各実施の形態では、エッチングストッパ層13としてAlxGa1−x)yIn1−yPで形成されたものを用いた。

そして、第1の実施の形態(図1乃至図4)に関して述べたように、第2乃至第4の実施の形態(図5乃至図18)においても、基板11がGaAsである場合には、GaAsとの格子整合の観点からは、0.48≦y≦0.52であるのが望ましい。より具体的には、例えばx=0、0.48≦y≦0.52である、GayIn1−yP(0.48≦y≦0.52)であるのが望ましい。

しかし、エッチングストッパ層13の材料は、半導体薄膜20を構成する層と選択的なエッチングが可能なものであれば、他の材料であっても良い。例えば、InP、InGaAs、InAlAs、InGaAsPなどを用い得る。

【0095】

さらにまた、第1及び第3の実施の形態では、エッチング時間を調整することにより、AlAs剥離層14の途中でエッチングが終わるように、即ち、AlAs剥離層14をその厚さ方向の一部のみ露出させるようにすることもできる。

【0096】

また、上記の各実施の形態では、半導体薄膜20がLEDアレイとして用いられるものであるが、本発明は、これに限定されず、半導体薄膜がLED以外の種々の素子や回路の形成に用いられる場合にも適用可能である。

【0097】

【発明の効果】

以上のように、本発明によれば、基板を効率的に再利用することができる。

【図面の簡単な説明】

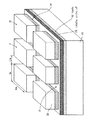

【図1】 本発明の第1の実施の形態の製造方法において、半導体薄膜の積層構造を形成した状態を示す概略部分断面図である。

【図2】 本発明の第1の実施の形態の製造方法において、溝を形成した状態を示す概略部分断面図である。

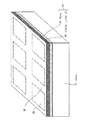

【図3】 本発明の第1の実施の形態の製造方法において、溝を形成した状態を示す概略部分斜視図である。

【図4】 本発明の第1の実施の形態の製造方法において、半導体薄膜を除去した状態を示す概略部分斜視図である。

【図5】 本発明の第2の実施の形態の製造方法において、半導体薄膜の積層構造を形成した状態を示す概略部分断面図である。

【図6】 本発明の第2の実施の形態の製造方法の一工程において、溝を形成した状態を示す概略部分断面図である。

【図7】 本発明の第2の実施の形態の製造方法において、半導体薄膜及びエッチングストッパ層を除去した状態を示す概略部分断面図である。

【図8】 本発明の第2の実施の形態の製造方法において、エッチングストッパ層から半導体薄膜を分離した状態を示す概略部分断面図である。

【図9】 本発明の第3の実施の形態の製造方法において、半導体薄膜の積層構造を形成した状態を示す概略部分断面図である。

【図10】 本発明の第3の実施の形態の製造方法において、溝を形成した状態を示す概略部分断面図である。

【図11】 本発明の第3の実施の形態の製造方法において、半導体薄膜を剥離した状態を示す概略部分断面図である。

【図12】 本発明の第3の実施の形態の製造方法において、エッチングストッパ層を除去した状態を示す概略部分断面図である。

【図13】 本発明の第3の実施の形態の製造方法において、剥離層を除去した状態を示す概略部分断面図である。

【図14】 本発明の第3の実施の形態の変形例の製造方法において、エッチングストッパ層及び剥離層を除去した状態を示す概略部分断面図である。

【図15】 本発明の第4の実施の形態の製造方法において、半導体薄膜の積層構造を形成した状態を示す概略部分断面図である。

【図16】 本発明の第4の実施の形態の製造方法において、溝を形成した状態を示す概略部分断面図である。

【図17】 本発明の第4の実施の形態の製造方法において、半導体薄膜を剥離した状態を示す概略部分断面図である。

【図18】 本発明の第4の実施の形態の製造方法において、第2及び第3のバッファー層、並びにエッチングストッパ層を除去した状態を示す概略部分断面図である。

【図19】 本発明の第5の実施の形態の製造方法において、半導体薄膜の積層構造を形成した状態を示す概略部分断面図である。

【図20】 本発明の第5の実施の形態の製造方法において、溝を形成した状態を示す概略部分断面図である。

【図21】 本発明の第5の実施の形態の製造方法において、半導体薄膜を剥離した状態を示す概略部分断面図である。

【図22】 従来の半導体装置の製造方法の一工程における半導体装置の状態を示す概略部分断面図である。

【図23】 従来の半導体装置の製造方法において、Al0.7Ga0.3As層をエッチングした状態を示す概略部分断面図である。

【図24】 従来の半導体装置の製造方法において、溝により半導体薄膜を分割した状態を示す概略部平面図である。

【符号の説明】

11 基板、 12 バッファー層、 13 エッチングストッパ層、 14 剥離層、 15 下側コンタクト層、 16 下側クラッド層、 17 活性層、 18 上側クラッド層、 19 上側コンタクト層、 20 半導体薄膜、 21 溝、 24 剥離層、 31 剥離層、 33 バッファー層、 34 バッファー層、 41 基板。

Claims (13)

- GaAsからなる基板と、

前記基板の上に形成され、Al q Ga 1−q As(1≧q≧0)で表される組成を有する第2の剥離層と、

前記第2の剥離層の上に形成され、(Al x Ga 1−x ) y In 1−y P層(1≧x≧0、1≧y≧0)で表される組成を有するエッチングストッパ層と、

前記エッチングストッパ層の上に形成され、Al p Ga 1−p As(1≧p≧0)で表される組成を有する第1の剥離層と、

前記第1の剥離層上に形成された半導体薄膜とを有し、

前記半導体薄膜の各層が、Al z Ga 1−z As(1≧z≧0)で表される組成を有し、

前記半導体薄膜の各層のAl組成比z、第1の剥離層のAl組成比p、第2の剥離層のAl組成比qについて、

z<p、z<qである

ことを特徴とする積層体。 - 前記第1の剥離層のAl組成比pと前記第2の剥離層のAl組成比qとが互いに等しくないことを特徴とする請求項1に記載の積層体。

- 前記第1の剥離層の厚さと前記第2の剥離層の厚さとが互いに等しくないことを特徴とする請求項1に記載の積層体。

- 前記第1の剥離層のAl組成比pと前記第2の剥離層のAl組成比qについて、p<qであることを特徴とする請求項1に記載の積層体。

- 前記第1の剥離層と前記第2の剥離層がAlAsであることを特徴とする請求項1に記載の積層体。

- 前記第1の剥離層の層厚よりも前記第2の剥離層の層厚が大きいことを特徴とする請求項5に記載の積層体。

- 前記ストッパ層の組成(AlxGa1−x)yIn1−yPにおいて、x=0、0.48≦y≦0.52である

ことを特徴とする請求項1に記載の積層体。 - 前記基板の上に形成された第1のバッファー層をさらに含み、

前記第2の剥離層は、前記第1のバッファー層の上に形成されており、

前記第2の剥離層の上に形成された第2のバッファー層をさらに含み、

前記ストッパ層は、前記第2のバッファー層の上に形成されており、

前記ストッパ層の上に形成された第3のバッファー層をさらに含み、

前記第1の剥離層は、前記第3のバッファー層の上に形成されている

ことを特徴とする請求項1に記載の積層体。 - 前記半導体薄膜が、下側コンタクト層と、その上に位置する下側クラッド層と、その上に位置する活性層と、その上に位置する上側クラッド層と、その上に位置する上側コンタクト層とを含むことを特徴とする請求項1乃至8のいずれかに記載の積層体。

- 前記半導体薄膜が、前記下側コンタクト層、前記下側クラッド層、前記活性層、前記上側クラッド層、及び前記上側コンタクト層を順にエピタキシャル成長させることにより形成されたものであることを特徴とする請求項9に記載の積層体。

- 請求項1乃至10のいずれかに記載の積層体を用意する工程と、

前記半導体薄膜に半導体素子を形成する工程と、

第1のエッチング液を用いて前記半導体薄膜に溝を形成する工程と、

第2のエッチング液を用いて前記第1の剥離層を除去する工程と、

前記第1の剥離層を除去する工程の後に、前記第2の剥離層を除去する工程と

を有する半導体装置の製造方法。 - 前記第1の剥離層を除去する工程の後であって、かつ前記第2の剥離層を除去する工程の前に、前記ストッパ層を除去する工程をさらに有することを特徴とする請求項11に記載の半導体装置の製造方法。

- 請求項8に記載の積層体を用意する工程と、

前記半導体薄膜に半導体素子を形成する工程と、

前記第1のエッチング液を用いて前記半導体薄膜に溝を形成する工程と、

前記第2のエッチング液を用いて前記第1の剥離層を除去する工程と、

前記第1の剥離層を除去する工程の後に、前記第2の剥離層を除去することにより、前記第3のバッファー層、前記ストッパ層、及び前記第2のバッファー層を前記基板から分離する工程と有する半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003180676A JP4315744B2 (ja) | 2003-06-25 | 2003-06-25 | 積層体及び半導体装置の製造方法 |

| TW93116795A TWI330412B (en) | 2003-06-25 | 2004-06-11 | Method for manufacturing semiconductor device |

| CN 200410061801 CN1577905B (zh) | 2003-06-25 | 2004-06-25 | 半导体器件的制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003180676A JP4315744B2 (ja) | 2003-06-25 | 2003-06-25 | 積層体及び半導体装置の製造方法 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009027465A Division JP5394091B2 (ja) | 2009-02-09 | 2009-02-09 | 半導体装置の製造方法 |

| JP2009027497A Division JP2009105451A (ja) | 2009-02-09 | 2009-02-09 | 積層体及び半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005019590A JP2005019590A (ja) | 2005-01-20 |

| JP2005019590A5 JP2005019590A5 (ja) | 2006-04-06 |

| JP4315744B2 true JP4315744B2 (ja) | 2009-08-19 |

Family

ID=34181600

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003180676A Expired - Fee Related JP4315744B2 (ja) | 2003-06-25 | 2003-06-25 | 積層体及び半導体装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP4315744B2 (ja) |

| CN (1) | CN1577905B (ja) |

| TW (1) | TWI330412B (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4518886B2 (ja) * | 2004-09-09 | 2010-08-04 | シャープ株式会社 | 半導体素子の製造方法 |

| JP2008053250A (ja) * | 2006-08-22 | 2008-03-06 | Sony Corp | 半導体装置の製造方法 |

| JP5171016B2 (ja) | 2006-10-27 | 2013-03-27 | キヤノン株式会社 | 半導体部材、半導体物品の製造方法、その製造方法を用いたledアレイ |

| JP2009260325A (ja) * | 2008-03-26 | 2009-11-05 | Univ Of Tokyo | 半導体基板、半導体基板の製造方法および半導体装置 |

| US8378385B2 (en) * | 2009-09-10 | 2013-02-19 | The Regents Of The University Of Michigan | Methods of preparing flexible photovoltaic devices using epitaxial liftoff, and preserving the integrity of growth substrates used in epitaxial growth |

| EP2521189A3 (en) * | 2011-04-29 | 2013-05-01 | Institute of Nuclear Energy Research Atomic Energy Council | Lift-off structure for substrate of a photoelectric device and the method thereof |

| CA2840517A1 (en) * | 2011-06-29 | 2013-06-27 | Stephen R. Forrest | Sacrificial etch protection layers for reuse of wafers after epitaxial lift off |

| TWI585990B (zh) * | 2011-08-26 | 2017-06-01 | 行政院原子能委員會核能研究所 | 用於光電元件之基板的剝離結構 |

| JPWO2016017762A1 (ja) * | 2014-07-30 | 2017-05-18 | 日産化学工業株式会社 | フッ酸エッチング用樹脂薄膜形成用組成物およびフッ酸エッチング用樹脂薄膜 |

| KR102533932B1 (ko) | 2015-03-18 | 2023-05-17 | 더 리젠츠 오브 더 유니버시티 오브 미시간 | 사전 패터닝된 메사들을 통한 스트레인 경감 에피택셜 리프트-오프 |

| WO2020121649A1 (ja) * | 2018-12-10 | 2020-06-18 | 株式会社フィルネックス | 半導体基板、半導体基板の製造方法及び半導体素子の製造方法 |

| CN110600435A (zh) * | 2019-09-05 | 2019-12-20 | 方天琦 | 多层复合基板结构及其制备方法 |

| CN118737811A (zh) | 2023-03-28 | 2024-10-01 | 冲电气工业株式会社 | 基板单元的制造方法和基板单元 |

| CN117913017B (zh) * | 2024-01-19 | 2024-10-22 | 江苏宜兴德融科技有限公司 | 一种薄膜半导体芯片制备方法和薄膜半导体芯片制备结构 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4883561A (en) * | 1988-03-29 | 1989-11-28 | Bell Communications Research, Inc. | Lift-off and subsequent bonding of epitaxial films |

| US5300788A (en) * | 1991-01-18 | 1994-04-05 | Kopin Corporation | Light emitting diode bars and arrays and method of making same |

| DE19632627A1 (de) * | 1996-08-13 | 1998-02-19 | Siemens Ag | Verfahren zum Herstellen eines Licht aussendenden und/oder empfangenden Halbleiterkörpers |

| CN1142599C (zh) * | 2000-11-27 | 2004-03-17 | 国联光电科技股份有限公司 | 发光二极管及其制造方法 |

-

2003

- 2003-06-25 JP JP2003180676A patent/JP4315744B2/ja not_active Expired - Fee Related

-

2004

- 2004-06-11 TW TW93116795A patent/TWI330412B/zh not_active IP Right Cessation

- 2004-06-25 CN CN 200410061801 patent/CN1577905B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW200503297A (en) | 2005-01-16 |

| CN1577905A (zh) | 2005-02-09 |

| JP2005019590A (ja) | 2005-01-20 |

| TWI330412B (en) | 2010-09-11 |

| CN1577905B (zh) | 2010-08-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4315744B2 (ja) | 積層体及び半導体装置の製造方法 | |

| JP5313651B2 (ja) | 半導体素子の製造方法 | |

| JP5394091B2 (ja) | 半導体装置の製造方法 | |

| AU2006276661B2 (en) | Method for manufacturing photoelectric conversion element and the photoelectric conversion element | |

| TW200834986A (en) | Method of forming light-emitting element | |

| CN101946335A (zh) | 太阳能电池及太阳能电池的制造方法 | |

| US9184338B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2010093186A (ja) | 窒化ガリウム系化合物半導体発光素子の製造方法、窒化ガリウム系化合物半導体素子の積層構造及び窒化ガリウム系化合物半導体発光素子、並びにランプ | |

| US8330036B1 (en) | Method of fabrication and structure for multi-junction solar cell formed upon separable substrate | |

| JP4136795B2 (ja) | 半導体装置の製造方法 | |

| JP4638000B2 (ja) | 半導体基板の製造方法 | |

| JP7657924B2 (ja) | 半導体ボディを製造する方法および半導体デバイス | |

| JP2009105451A (ja) | 積層体及び半導体装置の製造方法 | |

| TWI480928B (zh) | The manufacturing method of the semiconductor element and the epitaxial substrate used in the manufacturing method and the semi-finished product of the semiconductor device | |

| TW202414515A (zh) | 微型led用接合型晶圓的製造方法 | |

| JP4221818B2 (ja) | 光半導体素子の製造方法 | |

| JP4565320B2 (ja) | 発光素子の製造方法 | |

| KR100586609B1 (ko) | 질화갈륨계 발광 소자의 제조 방법 | |

| US20240332080A1 (en) | Manufacturing method of substrate unit, and substrate unit | |

| CN101840965A (zh) | 在金属衬底上制造的发光二极管的衬底切割方法 | |

| KR100956202B1 (ko) | 수직형 발광소자의 제조 방법 | |

| KR101018244B1 (ko) | 질화물계 반도체 발광소자의 제조방법 | |

| KR960015785B1 (ko) | 재성장에 의한 이종접합 계면 형성방법 및 그를 이용한 다이오드 제조방법 | |

| JP3111257B2 (ja) | GaAlAs系半導体素子の製造法 | |

| CN113964252A (zh) | 半导体结构及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060222 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081202 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081209 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090519 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090519 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4315744 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120529 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130529 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140529 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |