JP4313190B2 - ショットキー整流器 - Google Patents

ショットキー整流器 Download PDFInfo

- Publication number

- JP4313190B2 JP4313190B2 JP2003502893A JP2003502893A JP4313190B2 JP 4313190 B2 JP4313190 B2 JP 4313190B2 JP 2003502893 A JP2003502893 A JP 2003502893A JP 2003502893 A JP2003502893 A JP 2003502893A JP 4313190 B2 JP4313190 B2 JP 4313190B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- layer

- vapor deposition

- insulating layer

- semiconductor region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004065 semiconductor Substances 0.000 claims description 38

- 238000007740 vapor deposition Methods 0.000 claims description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 12

- 239000010936 titanium Substances 0.000 claims description 9

- 230000007547 defect Effects 0.000 claims description 7

- 238000005229 chemical vapour deposition Methods 0.000 claims description 6

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 5

- 229910052719 titanium Inorganic materials 0.000 claims description 5

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 claims description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 5

- 229910052721 tungsten Inorganic materials 0.000 claims description 5

- 239000010937 tungsten Substances 0.000 claims description 5

- 229910052710 silicon Inorganic materials 0.000 claims description 4

- 239000010703 silicon Substances 0.000 claims description 3

- 238000000034 method Methods 0.000 description 15

- 230000004888 barrier function Effects 0.000 description 12

- 230000003647 oxidation Effects 0.000 description 12

- 238000007254 oxidation reaction Methods 0.000 description 12

- 230000015556 catabolic process Effects 0.000 description 10

- 239000012535 impurity Substances 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 6

- 230000000903 blocking effect Effects 0.000 description 6

- 239000001301 oxygen Substances 0.000 description 6

- 229910052760 oxygen Inorganic materials 0.000 description 6

- 239000000758 substrate Substances 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- 235000012239 silicon dioxide Nutrition 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000008092 positive effect Effects 0.000 description 1

- 238000005036 potential barrier Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000009279 wet oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/0817—Thyristors only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/095—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being Schottky barrier gate field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66083—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by variation of the electric current supplied or the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. two-terminal devices

- H01L29/6609—Diodes

- H01L29/66143—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

- H01L29/8725—Schottky diodes of the trench MOS barrier type [TMBS]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Electrodes Of Semiconductors (AREA)

Description

Claims (9)

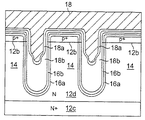

- 互いに反対面となる第1及び第2の面と、上記第1の面に隣接する第1の伝導性タイプを有するカソード領域と、上記第2の面に隣接し、上記カソード領域より正味ドープ濃度が低い第1の伝導性タイプを有するドリフト領域とを有する半導体領域と、

上記第2の面から上記半導体領域内に延び、該半導体領域内に1つ以上のメサを画定する1つ以上のトレンチと、

上記1つ以上のトレンチ内の上記半導体領域に隣接し、該半導体領域に接する熱成長絶縁層と、該熱成長絶縁層上に蒸着された蒸着成長絶縁層とを有する絶縁領域と、

上記半導体領域に隣接し、上記第2の面においてショットキー整流コンタクトを形成し、上記トレンチ内の上記絶縁領域に隣接するアノード電極とを備え、

上記アノード電極は、チタン層、チタン−タングステン層及びタングステン層を有し、上記トレンチは、上記カソード領域内まで延びていることを特徴とするショットキー整流器。 - 上記絶縁領域は、酸化物を含むことを特徴とする請求項1記載のショットキー整流器。

- 上記絶縁領域は、酸化シリコンを含むことを特徴とする請求項2記載のショットキー整流器。

- 上記蒸着成長絶縁層は、化学気相成長法によって成長されていることを特徴とする請求項1記載のショットキー整流器。

- 上記蒸着成長絶縁層は、化学気相成長法によって成長されていることを特徴とする請求項2記載のショットキー整流器。

- 上記蒸着成長絶縁層は、化学気相成長法によって成長されていることを特徴とする請求項3記載のショットキー整流器。

- 上記半導体領域は、シリコンを材料とすることを特徴とする請求項1記載のショットキー整流器。

- 上記第1の伝導性タイプは、n型伝導性であることを特徴とする請求項1記載のショットキー整流器。

- 互いに反対面となる第1及び第2の面と、上記第1の面に隣接する第1の伝導性タイプを有するカソード領域と、上記第2の面に隣接し、上記カソード領域より正味ドープ濃度が低い第1の伝導性タイプを有するドリフト領域とを有する半導体領域と、

上記第2の面から上記半導体領域内に延び、該半導体領域内に1つ以上のメサを画定する1つ以上のトレンチと、

上記1つ以上のトレンチ内の上記半導体領域に隣接し、該半導体領域に接する熱成長絶縁層と、該熱成長絶縁層上に蒸着された蒸着成長絶縁層とを有する絶縁領域と、

上記半導体領域に隣接し、上記第2の面においてショットキー整流コンタクトを形成し、上記トレンチ内の上記絶縁領域に隣接するアノード電極とを備え、

上記アノード電極は、チタン層、チタン−タングステン層及びタングステン層を有し、上記絶縁領域の熱成長絶縁層が蒸着成長絶縁層より欠陥密度が低いことを特徴とするショットキー整流器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/872,926 US6580141B2 (en) | 2001-06-01 | 2001-06-01 | Trench schottky rectifier |

| PCT/US2002/017322 WO2002099889A1 (en) | 2001-06-01 | 2002-05-31 | Trench schottky rectifier |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004529506A JP2004529506A (ja) | 2004-09-24 |

| JP2004529506A5 JP2004529506A5 (ja) | 2006-01-05 |

| JP4313190B2 true JP4313190B2 (ja) | 2009-08-12 |

Family

ID=25360613

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003502893A Expired - Lifetime JP4313190B2 (ja) | 2001-06-01 | 2002-05-31 | ショットキー整流器 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6580141B2 (ja) |

| EP (1) | EP1393379B1 (ja) |

| JP (1) | JP4313190B2 (ja) |

| KR (1) | KR100884077B1 (ja) |

| CN (1) | CN1280915C (ja) |

| TW (1) | TW548855B (ja) |

| WO (1) | WO2002099889A1 (ja) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6707127B1 (en) * | 2000-08-31 | 2004-03-16 | General Semiconductor, Inc. | Trench schottky rectifier |

| US20060038223A1 (en) * | 2001-07-03 | 2006-02-23 | Siliconix Incorporated | Trench MOSFET having drain-drift region comprising stack of implanted regions |

| US7033876B2 (en) * | 2001-07-03 | 2006-04-25 | Siliconix Incorporated | Trench MIS device having implanted drain-drift region and thick bottom oxide and process for manufacturing the same |

| US7009247B2 (en) * | 2001-07-03 | 2006-03-07 | Siliconix Incorporated | Trench MIS device with thick oxide layer in bottom of gate contact trench |

| US7291884B2 (en) * | 2001-07-03 | 2007-11-06 | Siliconix Incorporated | Trench MIS device having implanted drain-drift region and thick bottom oxide |

| US7323402B2 (en) * | 2002-07-11 | 2008-01-29 | International Rectifier Corporation | Trench Schottky barrier diode with differential oxide thickness |

| US7084423B2 (en) | 2002-08-12 | 2006-08-01 | Acorn Technologies, Inc. | Method for depinning the Fermi level of a semiconductor at an electrical junction and devices incorporating such junctions |

| US6833556B2 (en) | 2002-08-12 | 2004-12-21 | Acorn Technologies, Inc. | Insulated gate field effect transistor having passivated schottky barriers to the channel |

| US7439555B2 (en) * | 2003-12-05 | 2008-10-21 | International Rectifier Corporation | III-nitride semiconductor device with trench structure |

| US7098521B2 (en) * | 2004-10-01 | 2006-08-29 | International Business Machines Corporation | Reduced guard ring in schottky barrier diode structure |

| DE102004056663A1 (de) * | 2004-11-24 | 2006-06-01 | Robert Bosch Gmbh | Halbleitereinrichtung und Gleichrichteranordnung |

| EP1681725A1 (fr) * | 2005-01-18 | 2006-07-19 | St Microelectronics S.A. | Composant unipolaire vertical à faible courant de fuite |

| US8039328B2 (en) * | 2005-10-18 | 2011-10-18 | International Rectifier Corporation | Trench Schottky device with single barrier |

| EP2762107B1 (en) | 2006-01-20 | 2017-11-29 | Zimmer Technology, Inc. | Shoulder arthroplasty system |

| US20090053864A1 (en) * | 2007-08-23 | 2009-02-26 | Jinping Liu | Method for fabricating a semiconductor structure having heterogeneous crystalline orientations |

| US7741693B1 (en) | 2007-11-16 | 2010-06-22 | National Semiconductor Corporation | Method for integrating trench MOS Schottky barrier devices into integrated circuits and related semiconductor devices |

| US20090309181A1 (en) * | 2008-06-12 | 2009-12-17 | Force Mos Technology Co. Ltd. | Trench schottky with multiple epi structure |

| US7750412B2 (en) * | 2008-08-06 | 2010-07-06 | Fairchild Semiconductor Corporation | Rectifier with PN clamp regions under trenches |

| TWI455209B (zh) | 2009-10-12 | 2014-10-01 | Pfc Device Co | 溝渠式金氧半p-n接面蕭基二極體結構及其製作方法 |

| CN101800252B (zh) * | 2010-03-04 | 2012-05-30 | 无锡新洁能功率半导体有限公司 | 沟槽型肖特基势垒整流器及其制造方法 |

| CN101853850B (zh) * | 2010-03-17 | 2011-10-26 | 无锡新洁能功率半导体有限公司 | 一种超势垒半导体整流器件及其制造方法 |

| DE102010028203A1 (de) * | 2010-04-26 | 2011-10-27 | Robert Bosch Gmbh | Gleichrichter-Brückenschaltung |

| BR112013017505A2 (pt) * | 2011-01-07 | 2016-09-27 | Infineon Technologies Austria | arranjo de dispositivo semicondutor com um primeiro dispositivo semicondutor e com uma pluralidade de segundos dispositivos semicondutores |

| JP2013030618A (ja) | 2011-07-28 | 2013-02-07 | Rohm Co Ltd | 半導体装置 |

| US9059329B2 (en) * | 2011-08-22 | 2015-06-16 | Monolithic Power Systems, Inc. | Power device with integrated Schottky diode and method for making the same |

| KR101990622B1 (ko) | 2011-11-23 | 2019-06-18 | 아콘 테크놀로지스 인코포레이티드 | 계면 원자 단일층의 삽입에 의한 ⅳ족 반도체에 대한 금속 접점의 개선 |

| CN102916055B (zh) * | 2012-10-11 | 2014-12-24 | 杭州立昂微电子股份有限公司 | 一种沟槽肖特基势垒二极管及其制造方法 |

| CN103035751A (zh) * | 2012-11-23 | 2013-04-10 | 上海华虹Nec电子有限公司 | 肖特基二极管 |

| JP5922014B2 (ja) * | 2012-12-27 | 2016-05-24 | 新電元工業株式会社 | トレンチショットキバリアダイオード及びその製造方法 |

| CN104183485B (zh) * | 2013-05-23 | 2017-11-10 | 上海宝芯源功率半导体有限公司 | 一种超级势垒整流器结构及其制作方法 |

| TWI514578B (zh) * | 2013-06-21 | 2015-12-21 | Chip Integration Tech Co Ltd | 雙溝渠式整流器及其製造方法 |

| US20150017774A1 (en) * | 2013-07-10 | 2015-01-15 | Globalfoundries Inc. | Method of forming fins with recess shapes |

| US9620611B1 (en) | 2016-06-17 | 2017-04-11 | Acorn Technology, Inc. | MIS contact structure with metal oxide conductor |

| US10170627B2 (en) | 2016-11-18 | 2019-01-01 | Acorn Technologies, Inc. | Nanowire transistor with source and drain induced by electrical contacts with negative schottky barrier height |

| JP2017063237A (ja) * | 2017-01-13 | 2017-03-30 | ローム株式会社 | 半導体装置 |

| CN107256886A (zh) * | 2017-07-12 | 2017-10-17 | 付妮娜 | 沟槽式肖特基二极管及其制作方法 |

| DE112018007055B4 (de) * | 2018-02-09 | 2024-02-01 | Mitsubishi Electric Corporation | Leistungshalbleitereinheit |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS4822390B1 (ja) * | 1969-03-18 | 1973-07-05 | ||

| JPS5294773A (en) * | 1976-02-05 | 1977-08-09 | Sumitomo Electric Ind Ltd | Semiconductor element and its manufacture |

| US4835580A (en) * | 1987-04-30 | 1989-05-30 | Texas Instruments Incorporated | Schottky barrier diode and method |

| US5365102A (en) * | 1993-07-06 | 1994-11-15 | North Carolina State University | Schottky barrier rectifier with MOS trench |

| US6078090A (en) * | 1997-04-02 | 2000-06-20 | Siliconix Incorporated | Trench-gated Schottky diode with integral clamping diode |

| US5612567A (en) * | 1996-05-13 | 1997-03-18 | North Carolina State University | Schottky barrier rectifiers and methods of forming same |

| US5883422A (en) * | 1996-06-28 | 1999-03-16 | The Whitaker Corporation | Reduced parasitic capacitance semiconductor devices |

| JP3502531B2 (ja) * | 1997-08-28 | 2004-03-02 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| US6184563B1 (en) * | 1998-07-27 | 2001-02-06 | Ho-Yuan Yu | Device structure for providing improved Schottky barrier rectifier |

| US6252258B1 (en) * | 1999-08-10 | 2001-06-26 | Rockwell Science Center Llc | High power rectifier |

| JP2001085686A (ja) * | 1999-09-13 | 2001-03-30 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP2001094094A (ja) * | 1999-09-21 | 2001-04-06 | Hitachi Ltd | 半導体装置およびその製造方法 |

-

2001

- 2001-06-01 US US09/872,926 patent/US6580141B2/en not_active Expired - Lifetime

-

2002

- 2002-05-31 WO PCT/US2002/017322 patent/WO2002099889A1/en active Application Filing

- 2002-05-31 EP EP02739587A patent/EP1393379B1/en not_active Expired - Lifetime

- 2002-05-31 TW TW091111744A patent/TW548855B/zh not_active IP Right Cessation

- 2002-05-31 CN CNB028111443A patent/CN1280915C/zh not_active Expired - Lifetime

- 2002-05-31 KR KR1020037015603A patent/KR100884077B1/ko active IP Right Grant

- 2002-05-31 JP JP2003502893A patent/JP4313190B2/ja not_active Expired - Lifetime

-

2003

- 2003-05-05 US US10/429,817 patent/US6770548B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP1393379A1 (en) | 2004-03-03 |

| WO2002099889A1 (en) | 2002-12-12 |

| CN1280915C (zh) | 2006-10-18 |

| US6770548B2 (en) | 2004-08-03 |

| TW548855B (en) | 2003-08-21 |

| KR20040005998A (ko) | 2004-01-16 |

| US6580141B2 (en) | 2003-06-17 |

| US20020179993A1 (en) | 2002-12-05 |

| EP1393379A4 (en) | 2009-08-12 |

| KR100884077B1 (ko) | 2009-02-19 |

| US20030193074A1 (en) | 2003-10-16 |

| WO2002099889A9 (en) | 2004-04-08 |

| CN1520615A (zh) | 2004-08-11 |

| JP2004529506A (ja) | 2004-09-24 |

| EP1393379B1 (en) | 2011-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4313190B2 (ja) | ショットキー整流器 | |

| JP2004529506A5 (ja) | ||

| JP4855636B2 (ja) | トレンチショットキー整流器 | |

| US7491633B2 (en) | High switching speed two mask schottky diode with high field breakdown | |

| US9059284B2 (en) | Semiconductor device | |

| TWI441340B (zh) | 無需利用附加遮罩來製造的積體有肖特基二極體的平面mosfet及其佈局方法 | |

| US6673662B2 (en) | Epitaxial edge termination for silicon carbide Schottky devices and methods of fabricating silicon carbide devices incorporating same | |

| US6998694B2 (en) | High switching speed two mask Schottky diode with high field breakdown | |

| US6740951B2 (en) | Two-mask trench schottky diode | |

| JP2004521487A (ja) | トレンチショットキーバリア整流器 | |

| US10797182B2 (en) | Trench semiconductor device having shaped gate dielectric and gate electrode structures and method | |

| US20230307556A1 (en) | Silicon carbide semiconductor device | |

| US20060131686A1 (en) | LOCOS-based junction-pinched schottky rectifier and its manufacturing methods | |

| CN114284348A (zh) | 一种终端结构、制作方法以及功率器件 | |

| CN114497182A (zh) | 一种基于体内多区终端结构的功率器件及制备方法 | |

| KR100483074B1 (ko) | 쇼트키 다이오드 및 그 제조방법 | |

| JP4715324B2 (ja) | 整流素子 | |

| JP2024011076A (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| CN117038741A (zh) | 一种碳化硅肖特基二极管及其制备方法 | |

| CN115621300A (zh) | 集成超结结构的碳化硅基沟槽型mosfet及其制作方法 | |

| CN118800806A (zh) | 一种带有突出p阱的umosfet器件及其制备方法 | |

| JP2010283403A (ja) | 整流素子およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050519 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050519 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080331 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080819 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081119 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081127 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081219 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090105 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090119 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090219 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090414 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090514 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120522 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4313190 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130522 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |