JP4201202B2 - パス装置用低電圧変調回路 - Google Patents

パス装置用低電圧変調回路 Download PDFInfo

- Publication number

- JP4201202B2 JP4201202B2 JP2004530071A JP2004530071A JP4201202B2 JP 4201202 B2 JP4201202 B2 JP 4201202B2 JP 2004530071 A JP2004530071 A JP 2004530071A JP 2004530071 A JP2004530071 A JP 2004530071A JP 4201202 B2 JP4201202 B2 JP 4201202B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- input

- signal

- supply voltage

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

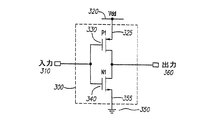

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/1733—Controllable logic circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0013—Arrangements for reducing power consumption in field effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

- H03K19/0185—Coupling arrangements; Interface arrangements using field effect transistors only

- H03K19/018585—Coupling arrangements; Interface arrangements using field effect transistors only programmable

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/224,093 US6859084B2 (en) | 2002-08-19 | 2002-08-19 | Low-power voltage modulation circuit for pass devices |

| PCT/EP2003/008576 WO2004019495A2 (en) | 2002-08-19 | 2003-08-01 | Supply voltage modulation circuit for mos transistors, reconfigurable logic device and method of processing an input signal to a logic circuit |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005536161A JP2005536161A (ja) | 2005-11-24 |

| JP2005536161A5 JP2005536161A5 (enExample) | 2006-01-12 |

| JP4201202B2 true JP4201202B2 (ja) | 2008-12-24 |

Family

ID=31715215

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004530071A Expired - Fee Related JP4201202B2 (ja) | 2002-08-19 | 2003-08-01 | パス装置用低電圧変調回路 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6859084B2 (enExample) |

| EP (1) | EP1537666B1 (enExample) |

| JP (1) | JP4201202B2 (enExample) |

| AT (1) | ATE401700T1 (enExample) |

| AU (1) | AU2003260358A1 (enExample) |

| DE (1) | DE60322231D1 (enExample) |

| WO (1) | WO2004019495A2 (enExample) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6946903B2 (en) * | 2003-07-28 | 2005-09-20 | Elixent Limited | Methods and systems for reducing leakage current in semiconductor circuits |

| KR100687867B1 (ko) * | 2004-07-21 | 2007-02-27 | 주식회사 하이닉스반도체 | 저전력 고성능 인버터 회로 |

| US20070008004A1 (en) * | 2005-07-11 | 2007-01-11 | Vikram Santurkar | Apparatus and methods for low-power routing circuitry in programmable logic devices |

| US7362126B1 (en) * | 2005-08-17 | 2008-04-22 | National Semiconductor Corporation | Floating CMOS input circuit that does not draw DC current |

| US20070047364A1 (en) * | 2005-08-31 | 2007-03-01 | International Business Machines Corporation | Methods and apparatus for varying a supply voltage or reference voltage using independent control of diode voltage in asymmetrical double-gate devices |

| US7567096B2 (en) * | 2007-03-21 | 2009-07-28 | Qualcomm Incorporated | Circuit device and method of controlling a voltage swing |

| DE102008002749A1 (de) * | 2008-06-27 | 2009-12-31 | Carl Zeiss Smt Ag | Beleuchtungsoptik für die Mikrolithografie |

| US9166567B2 (en) * | 2013-03-15 | 2015-10-20 | University Of California, San Diego | Data-retained power-gating circuit and devices including the same |

| WO2021247010A1 (en) * | 2020-06-02 | 2021-12-09 | Intel Corporation | Dynamic power rail floating for cdac circuits |

| CN115201542A (zh) * | 2021-04-09 | 2022-10-18 | 联芸科技(杭州)股份有限公司 | 电压检测电路 |

| CN114389598A (zh) * | 2022-03-23 | 2022-04-22 | 武汉市聚芯微电子有限责任公司 | 一种转换装置、接口电路及芯片 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59208926A (ja) | 1983-05-13 | 1984-11-27 | Hitachi Ltd | シユミツトトリガ回路 |

| JP2770941B2 (ja) | 1985-12-10 | 1998-07-02 | シチズン時計株式会社 | シユミツトトリガ回路 |

| JPS62178015A (ja) | 1986-01-31 | 1987-08-05 | Nippon Telegr & Teleph Corp <Ntt> | デイジタル論理fet回路 |

| JP2585348B2 (ja) * | 1988-02-22 | 1997-02-26 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US5684415A (en) * | 1995-12-22 | 1997-11-04 | Symbios Logic Inc. | 5 volt driver in a 3 volt CMOS process |

| US5894227A (en) * | 1996-03-15 | 1999-04-13 | Translogic Technology, Inc. | Level restoration circuit for pass logic devices |

| US5828231A (en) * | 1996-08-20 | 1998-10-27 | Xilinx, Inc. | High voltage tolerant input/output circuit |

| US5767728A (en) | 1996-09-05 | 1998-06-16 | International Business Machines Corporation | Noise tolerant CMOS inverter circuit having a resistive bias |

| US6285213B1 (en) | 1997-11-19 | 2001-09-04 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor integrated circuit device |

| US6118303A (en) * | 1998-04-17 | 2000-09-12 | Lsi Logic Corporation | Integrated circuit I/O buffer having pass gate protection with RC delay |

| KR100297139B1 (ko) | 1998-04-20 | 2001-10-29 | 가네꼬 히사시 | 반도체 집적회로 |

| EP1061525B1 (en) * | 1999-06-17 | 2006-03-08 | STMicroelectronics S.r.l. | Row decoder for a nonvolatile memory with possibility of selectively biasing word lines to positive or negative voltages |

-

2002

- 2002-08-19 US US10/224,093 patent/US6859084B2/en not_active Expired - Lifetime

-

2003

- 2003-08-01 JP JP2004530071A patent/JP4201202B2/ja not_active Expired - Fee Related

- 2003-08-01 AT AT03792245T patent/ATE401700T1/de not_active IP Right Cessation

- 2003-08-01 WO PCT/EP2003/008576 patent/WO2004019495A2/en not_active Ceased

- 2003-08-01 DE DE60322231T patent/DE60322231D1/de not_active Expired - Lifetime

- 2003-08-01 EP EP03792245A patent/EP1537666B1/en not_active Expired - Lifetime

- 2003-08-01 AU AU2003260358A patent/AU2003260358A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| DE60322231D1 (de) | 2008-08-28 |

| EP1537666B1 (en) | 2008-07-16 |

| JP2005536161A (ja) | 2005-11-24 |

| WO2004019495A3 (en) | 2004-10-14 |

| AU2003260358A8 (en) | 2004-03-11 |

| EP1537666A2 (en) | 2005-06-08 |

| US20040032289A1 (en) | 2004-02-19 |

| ATE401700T1 (de) | 2008-08-15 |

| US6859084B2 (en) | 2005-02-22 |

| WO2004019495A2 (en) | 2004-03-04 |

| AU2003260358A1 (en) | 2004-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4814791B2 (ja) | レベル・シフター | |

| JP3699764B2 (ja) | ドライバ回路装置及びインターフェース | |

| KR100591520B1 (ko) | 감소된 전압 입출력의 3상태 버퍼 및 그 제조 방법 | |

| US5574389A (en) | CMOS 3.3 volt output buffer with 5 volt protection | |

| US6060906A (en) | Bidirectional buffer with active pull-up/latch circuit for mixed-voltage applications | |

| US20030179032A1 (en) | Level shifter circuit and semiconductor device including the same | |

| EP1011197B1 (en) | Method for generating differential tri-states and differential tri-state circuit | |

| JP4201202B2 (ja) | パス装置用低電圧変調回路 | |

| JPH0338873A (ja) | 集積回路 | |

| US6373291B1 (en) | Pass transistor logic circuit for reducing power consumption | |

| KR100225833B1 (ko) | 출력회로 | |

| KR20010033685A (ko) | 고성능 저전력 온-칩 상호접속을 위한 차동 혼합 스윙3상태 드라이버 회로 | |

| KR101230794B1 (ko) | 입출력 회로 및 반도체 입출력 장치 | |

| US6094067A (en) | Output buffer circuit | |

| US20040207450A1 (en) | Voltage level shifter and system mounting voltage level shifter therein | |

| JPWO2004107578A1 (ja) | 半導体装置 | |

| KR100759775B1 (ko) | 입출력 버퍼 회로 | |

| US12381560B2 (en) | Semiconductor device including a level shifter and method of mitigating a delay between input and output signals | |

| US5408145A (en) | Low power consumption and high speed NOR gate integrated circuit | |

| US7656210B2 (en) | Semiconductor integrated circuit | |

| US20030184358A1 (en) | Low voltage level shifter with latching function | |

| EP0388074A1 (en) | Cmos level shifting circuit | |

| US6366126B1 (en) | Input circuit, output circuit, and input/output circuit and signal transmission system using the same input/output circuit | |

| JPH0795040A (ja) | ノイズ減少回路を有する出力バッファ回路 | |

| US6433594B1 (en) | Semiconductor integrated circuit and semiconductor integrated circuit system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050830 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050830 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20071212 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20071212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20071212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080401 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080501 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20080509 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080902 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081002 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121017 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |