JP4178807B2 - 半導体発光素子およびその製造方法 - Google Patents

半導体発光素子およびその製造方法 Download PDFInfo

- Publication number

- JP4178807B2 JP4178807B2 JP2002041171A JP2002041171A JP4178807B2 JP 4178807 B2 JP4178807 B2 JP 4178807B2 JP 2002041171 A JP2002041171 A JP 2002041171A JP 2002041171 A JP2002041171 A JP 2002041171A JP 4178807 B2 JP4178807 B2 JP 4178807B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- type

- gan

- cladding layer

- undoped

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

この発明は、半導体発光素子およびその製造方法に関し、特に、窒化物系III−V族化合物半導体を用いた半導体レーザや発光ダイオードに適用して好適なものである。

【0002】

【従来の技術】

近年、光ディスクの高密度化に必要である青色領域から紫外線領域におよぶ発光が可能な半導体レーザとして、AlGaInNなどの窒化物系III−V族化合物半導体を用いた半導体レーザの研究開発が盛んに行われ、すでに実用化されている。

【0003】

この窒化物系III−V族化合物半導体を用いた半導体レーザとして、選択成長により形成されたリッジ構造を有する半導体レーザが提案されている(J.Crystal Growth 144(1994)133 および特開2000−58461号公報)。この半導体レーザの要部を図9に示す。図9に示すように、この半導体レーザを製造するには、c面サファイア基板上に低温成長によるGaNバッファ層を介してp型GaNコンタクト層(いずれも図示せず)、n型AlGaNクラッド層101、n型GaN光導波層102、活性層103、p型GaN光導波層104およびp型AlGaNクラッド層105を順次成長させ、その上にSiO2 膜106を形成し、このSiO2 膜106の所定部分にストライプ状の開口106aを形成した後、このSiO2 膜106を成長マスクとしてその開口106aの部分におけるp型AlGaNクラッド層105上にp型AlGaNクラッド層107およびp型GaNコンタクト層108を順次選択成長させてリッジを形成する。

【0004】

【発明が解決しようとする課題】

しかしながら、本発明者の検討によれば、上述の従来の半導体レーザにおいては、SiO2 膜106の開口106aの部分におけるp型AlGaNクラッド層105上にp型AlGaNクラッド層107を選択成長させるとき、下層のn型層の成長時にドーピングに用いられるn型不純物(主としてSi)が成長装置の成長室内に残存しており、このn型不純物により成長界面が汚染されたり、成長界面にドナーとして働く欠陥が発生したりすることにより、成長界面近傍がn型化する。このため、実際には、図10に示すように、p型AlGaNクラッド層105と選択成長されるp型AlGaNクラッド層107との界面にn型AlGaN層109が形成され、これらの層によりpnp構造が形成されてしまう。この結果、p型AlGaNクラッド層105とp型AlGaNクラッド層107とからなるp型クラッド層の全体で見た直列抵抗が増大し、半導体レーザの動作電圧の上昇をもたらすという問題があった。

【0005】

したがって、この発明が解決しようとする課題は、p側クラッド層の厚さを良好な光学特性を得るのに必要かつ十分な値に保持しつつ、動作電圧の低減を図ることができる半導体発光素子およびそのような半導体発光素子を容易に製造することができる半導体発光素子の製造方法を提供することにある。

この発明の上記課題およびその他の課題は、添付図面を参照した本明細書の以下の記述により明らかとなるであろう。

【0006】

【課題を解決するための手段】

上記課題を解決するために、この発明の第1の発明は、

n側クラッド層と、

n側クラッド層上の活性層と、

活性層上のp側クラッド層とを有し、

p側クラッド層に選択成長により形成されたリッジを有する、窒化物系III−V族化合物半導体を用いた半導体発光素子において、

p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、第2の層がこの第2の層よりバンドギャップが大きい第3の層を有し、

リッジの成長界面が第1の層に含まれる

ことを特徴とするものである。

ここで、リッジと下地層との成長界面が第1の層または第1の層と第2の層との間に第1の層と接してアンドープまたはn型の他の層が設けられる場合には第1の層もしくはこの他の層に含まれるとは、リッジと下地層との成長界面が第1の層または第1の層もしくはこの他の層の中に完全に含まれる場合のほか、リッジと下地層との成長界面が第1の層の第2の層側の面またはこの他の層の第2の層側の面と一致する場合も意味するものとする。これは、リッジの両側の部分の底面(下地層の表面)と活性層との間の距離をd、リッジに含まれる、活性層に最も近いp型層と活性層との間の距離をLp とすると、Lp ≧dであると言い換えることもできる。

【0007】

この半導体発光素子は、典型的にはSCH(Separate Confinement Heterostructure)構造を有する。すなわち、n側クラッド層と活性層との間にn側光導波層が設けられ、p側クラッド層と活性層との間にp側光導波層が設けられる。

【0008】

p側クラッド層の全体の厚さは、一般には500〜600nmあれば足りる。p側クラッド層のp型の第2の層の厚さは一般的には0nmより大きく、550nm以下あるいは450nm以下であるが、典型的には390nm以上550nm以下、より典型的には400nm以上530nm以下である。一方、p側クラッド層のアンドープの第1の層(この場合、n- 型を呈し、比抵抗は一般にp型層に比べて数分の1から1桁程度低い)の厚さは、一般には0nmより大きく、500nm以下であるが、p側クラッド層の抵抗の低減を十分に図る観点より、好適には50nm以上、より好適には70nm以上、更に好適には90nm以上に選ばれ、一方、典型的には400nm以下あるいは300nm以下あるいは200nm以下に選ばれ、これらの上限および下限を任意に組み合わせた範囲であってよい。この第1の層の厚さは、一つの典型的な例では70nm以上130nm以下であり、更に典型的な例では90nm以上110nm以下に選ばれる。これらのアンドープまたはn型の第1の層およびp型の第2の層は、必要な光学特性、例えば十分に高い光閉じ込め係数Γが得られて良好な遠視野像(far fieldpattern,FFP) などが得られる限り、互いに同じ材料からなるものであっても、互いに異なる材料からなるものであってもよい。前者の例としては、第1の層および第2の層の材料ともAlGaNを用いる場合が挙げられ、後者の例としては、第2の層の材料としてAlGaNを用い、第1の層の材料としてAlGaInN、GaN、InGaNなどを用いる場合が挙げられる。第1の層および第2の層は互いに直接接する場合のほか、何らかの機能を有する他の層を介して間接的に接する場合もあり得る。このうち特に、第1の層と第2の層との間に第1の層と接してアンドープまたはn型の他の層が設けられる場合には、上述のようにリッジと下地層との成長界面は第1の層もしくはこの他の層に含まれる。

【0009】

また、n側光導波層およびp側光導波層が設けられる場合、それらの厚さは一般的には0nmより大きく、50nm以下である。

【0010】

p側クラッド層のアンドープまたはn型の第1の層は、半導体発光素子の動作時にp側電極側から注入される正孔をトンネル効果により活性層に到達しやすくして注入効率を高くするとともに、ヘテロ界面の導入により、第2の層のp型不純物として通常用いられるMgが活性層側に拡散するのを抑制して活性層の劣化を防止する観点より、好適には超格子構造とする。一つの典型的な例においてはp側クラッド層全体を超格子構造とする。

【0011】

p型の第2の層に存在する第3の層は、一般的にはAlおよびGaを含むp型の窒化物系III−V族化合物半導体からなり、より具体的には、例えばp型Alx Ga1-x N(ただし、0<x<1)からなり、活性層に注入される電子のオーバフローを効果的に抑制する観点からは、好適にはp型Alx Ga1-x N(ただし、0.15≦x<1)からなる。

【0012】

また、p型の第2の層のp型不純物として通常用いられるMgが活性層に拡散することによる活性層の劣化を防止する観点からは、活性層とp側クラッド層のp型の第2の層との間の距離は、好適には20nm以上、より好適には50nm以上、更に好適には100nm以上に選ばれる。また、最近の報告によれば、GaNにおける正孔の拡散距離は約0.28μm(280nm)であり、これを考慮すると、電子との再結合の確率を低くし、活性層への正孔の注入効率を高くするためには、活性層とp側クラッド層のp型の第2の層との間の距離は、この拡散距離以下にすることが望ましい。

【0013】

一方、p側クラッド層のp型の第2の層から活性層へのp型不純物、例えばMgの拡散を抑制して活性層の劣化を防止する観点からは、好適には、活性層とp側クラッド層の第2の層との間に、バンドギャップまたは格子定数が互いに異なる層の組み合わせが少なくとも1組以上存在するようにし、あるいは、互いに原子組成比が異なる層からなる超格子構造が少なくとも1層以上存在するようにし、これを格子歪み層としてMgの拡散を防止するようにする。

【0014】

典型的には、活性層の障壁層を構成する窒化物系III−V族化合物半導体はInx Ga1-x N(ただし、0<x<1)であり、活性層の井戸層を構成する窒化物系III−V族化合物半導体はIny Ga1-y N(ただし、0<y<1かつy>x)である。

【0015】

窒化物系III−V族化合物半導体は、一般的には、Ga、Al、InおよびBからなる群より選ばれた少なくとも一種のIII族元素と、少なくともNを含み、場合によって更にAsまたはPを含むV族元素とからなり、具体例を挙げると、GaN、InN、AlN、AlGaN、InGaN、AlGaInNなどである。

【0016】

典型的には、下地層上に成長マスクが形成され、この成長マスクの開口部における下地層上にリッジが選択成長される。成長マスクは一般的には絶縁膜により形成され、絶縁膜の具体例を挙げると、二酸化シリコン(SiO2 )膜、窒化シリコン(Si3 N4 )膜、酸窒化シリコン(SiON)膜などである。選択成長の下地層は、第1の層であることもあるし、第1の層を途中の厚さまで成長させたアンドープまたはn型の層であることもあり、更には、第1の層と第2の層との間に第1の層と接してアンドープまたはn型の他の層が設けられる場合にはこの他の層であることもある。リッジは、例えば、第1の層の上層部、第2の層および第3の層を含み、具体的には、例えば、第1の層の上層部、第2の層、第3の層およびp型コンタクト層からなる。あるいは、リッジは、第2の層、第3の層およびp型コンタクト層からなる。

【0017】

この発明の第2の発明は、

n側クラッド層と、

n側クラッド層上の活性層と、

活性層上のp側クラッド層とを有し、

p側クラッド層に選択成長により形成されたリッジを有する、窒化物系III−V族化合物半導体を用いた半導体発光素子において、

p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、

リッジの成長界面が第1の層に含まれる

ことを特徴とするものである。

この発明の第2の発明においては、その性質に反しない限り、第1の発明に関連して説明したことが成立する。

【0018】

この発明の第3の発明は、

n側クラッド層と、

n側クラッド層上の活性層と、

活性層上のp側クラッド層とを有し、

p側クラッド層に選択成長により形成されたリッジを有する半導体発光素子において、

p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、

リッジの成長界面が第1の層に含まれる

ことを特徴とするものである。

【0019】

ここで、この半導体発光素子は、基本的にはどのような半導体を用いたものであってもよく、窒化物系III−V族化合物半導体を用いたもののほか、AlGaAs系半導体、AlGaInP系半導体、InGaAsP系半導体、GaInNAs系半導体などの各種のIII−V族化合物半導体や、ZnSe系半導体などのII−VI族化合物半導体、更にはダイヤモンドなどを用いたものなどであってもよい。

この発明の第3の発明においては、その性質に反しない限り、第1の発明に関連して説明したことが成立する。

【0020】

この発明の第4の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、第2の層がこの第2の層よりバンドギャップが大きい第3の層を有する、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上にアンドープまたはn型の層、第2の層および第3の層を成長させる工程とを有する

ことを特徴とするものである。

【0021】

この発明の第5の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、第2の層がこの第2の層よりバンドギャップが大きい第3の層を有する、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上に第2の層および第3の層を成長させる工程とを有する

ことを特徴とするものである。

【0022】

この発明の第6の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなる、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上にアンドープまたはn型の層および第2の層を成長させる工程とを有する

ことを特徴とするものである。

【0023】

この発明の第7の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなる、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上に第2の層を成長させる工程とを有する

ことを特徴とするものである。

【0024】

この発明の第8の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなる半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上にアンドープまたはn型の層および第2の層を成長させる工程とを有する

ことを特徴とするものである。

【0025】

この発明の第9の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなる半導体発光素子の製造方法であって、

第1の層を成長させた後、第1の層上に所定の開口部を有する成長マスクを形成する工程と、

成長マスクの開口部における第1の層上に第2の層を成長させる工程とを有する

ことを特徴とするものである。

【0026】

この発明の第4〜第9の発明においては、典型的には、p側クラッド層の第2の層上に更に、p型コンタクト層が成長される。

この発明の第4〜第9の発明においては、その性質に反しない限り、第1〜第3の発明に関連して説明したことが成立する。

【0027】

この発明の第10の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、第2の層がこの第2の層よりバンドギャップが大きい第3の層を有する、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

活性層から第3の層までの成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにした

ことを特徴とするものである。

【0028】

この発明の第11の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなる、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

活性層からp側クラッド層の第1の層までの成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにした

ことを特徴とするものである。

【0029】

この発明の第12の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有する、窒化物系III−V族化合物半導体を用いた半導体発光素子において、

活性層とこの活性層に最も近い、p型不純物がドープされたp型の層との間の距離が50nm以上である

ことを特徴とするものである。

【0030】

この発明の第12の発明においては、活性層とこの活性層に最も近いp型の層との間の距離は、p型の層にドープされたp型不純物の拡散による活性層の劣化をより効果的に防止する観点より、好適には60nm以上、より好適には100nm以上とする。この活性層とp型の層との間の距離は、p型不純物の拡散による活性層の劣化を防止するためには他に支障がない限りできるだけ大きくするのが望ましいが、一般的には500nm以下である。この活性層とp型の層との間の距離は、典型的には50nm以上500nm以下、より典型的には100nm以上200nm以下である。活性層に最も近いp型の層は、例えば、p側クラッド層よりバンドギャップが大きいp型の層であり、この発明の第1の発明における第3の層と同じものである。

【0031】

この発明の第13の発明は、

n側クラッド層とp側クラッド層との間に活性層がはさまれた構造および選択成長により形成されたリッジ構造を有し、活性層とこの活性層に最も近い、p型不純物がドープされたp型の層との間の距離が50nm以上であり、活性層に最も近いp型の層がp側クラッド層よりバンドギャップが大きいp型の層である、窒化物系III−V族化合物半導体を用いた半導体発光素子の製造方法であって、

活性層からp側クラッド層よりバンドギャップが大きいp型の層までの成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにした

ことを特徴とするものである。

【0032】

この発明の第10〜第13の発明においては、その性質に反しない限り、第1の発明に関連して説明したことが成立する。

【0033】

この発明の第12および第13の発明においては、p側クラッド層の全体がp型の層であっても、第1〜第11の発明と同様にアンドープまたはn型の第1の層とp型の第2の層とからなるものであってもよい。後者の場合は、その性質に反しない限り、この発明の第1〜第11の発明に関連して述べたことが成立する。

【0034】

この発明の第10、第11および第13の発明においては、Inを含む層、例えば活性層からのInの脱離をより効果的に防止する観点より、最も好適には、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気としてN2 ガス雰囲気を用いる。一方、この実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気を用いて成長を行った後に行われるp型の層の成長については、そのp型層の抵抗の低減を図る観点より、好適には、窒素と水素とを主成分とするキャリアガス雰囲気を用い、最も好適には、N2 とH2 との混合ガス雰囲気を用いる。

【0035】

窒化物系III−V族化合物半導体層を成長させる基板としては、種々のものを用いることができ、具体的には、サファイア基板、SiC基板、Si基板、GaAs基板、GaP基板、InP基板、スピネル基板、酸化シリコン基板などのほか、厚いGaN層などの窒化物系III−V族化合物半導体層からなる基板を用いてもよい。

【0036】

窒化物系III−V族化合物半導体の成長方法または選択成長方法としては、例えば、有機金属化学気相成長(MOCVD)、ハイドライド気相エピタキシャル成長またはハライド気相エピタキシャル成長(HVPE)などを用いることができる。窒化物系III−V族化合物半導体を含む化合物半導体全般の成長方法としては、これらに加えて、例えば分子線エピタキシー(MBE)などを用いることもできる。

【0037】

上述のように構成されたこの発明の第1〜第9の発明によれば、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、リッジと下地層との成長界面が第1の層または第1の層と第2の層との間に第1の層と接してアンドープまたはn型の他の層が設けられる場合には第1の層もしくはこの他の層に含まれることにより、すなわちリッジと下地層との成長界面がn型層に含まれることにより、リッジと下地層との成長界面がp型層の表面である従来技術のようにリッジを選択成長により形成する場合にn型不純物により成長界面が汚染されたり、成長界面にドナーとして働く欠陥が発生したりすることにより成長界面近傍がn型化してpnp構造が形成される問題が本質的に存在せず、したがってp側クラッド層全体の直列抵抗の低減を図り、動作電圧の低減を図ることができる。また、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなることにより、光閉じ込め係数Γなどの光学特性の良否を左右するp側クラッド層の厚さと動作電圧の大小を左右するp型の第2の層の厚さとを独立に制御することができるため、低動作電圧でかつ光学特性が良好な(例えば、FFPのθ⊥が小さいなど)半導体発光素子を容易に実現することができる。言い換えれば、半導体発光素子に対して良好な光場を得て良好な光学特性を得るのに必要なp側クラッド層の厚さを確保しつつ、動作電圧上昇の原因となる高比抵抗のp型層の厚さを可能な限り薄くして動作電圧の低減を図ることができる。また、活性層と第2の層との間の距離を十分に大きくすることができるため、第2の層のp型不純物が活性層に拡散するのを抑制することができ、活性層の劣化を防止することができる。更に、特に、第2の層がこの第2の層よりバンドギャップが大きいp型の第3の層を有する場合には、この第3の層により、活性層に注入される電子がオーバーフローするのを抑制することができる一方、通常活性層と組成が大きく異なるこの第3の層と活性層との間の距離を自由に設計することができ、それによって活性層に生じる歪を緩和することができるため、活性層の劣化を防止することができる。

【0038】

また、p型の第2の層などのp型層の全部がリッジ内に収まっていることにより、半導体発光素子の動作温度が上昇してp型の第2の層などのp型層中のp型不純物、例えばMgの活性化率が高まり、このp型層が低抵抗化しても、リッジの外部に漏れ出る電流を大幅に低減することができる。これは特に、半導体レーザの特性温度T0 の向上に資するものである。

【0039】

また、この発明の第10および第11の発明によれば、第10の発明においては活性層から第3の層までの成長を、第11の発明においては活性層からp側クラッド層の第1の層までの成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにしているので、Inを含む層、例えば活性層からInが脱離するのを効果的に抑えることができ、活性層の劣化を防止することができる。一方、この後のp型の層は、窒素と水素とを主成分とするキャリアガス雰囲気中で成長させることにより、良好な結晶性で成長させることができる。

【0040】

また、この発明の第12の発明によれば、活性層とこの活性層に最も近い、p型不純物がドープされたp型の層との間の距離が50nm以上であるので、このp型の層にドープされたp型不純物の活性層への拡散を大幅に減少させることができ、活性層の劣化を防止することができる。

【0041】

また、この発明の第13の発明によれば、活性層からp側クラッド層よりバンドギャップが大きいp型の層までの成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにしているので、Inを含む層、例えば活性層からInが脱離するのを抑えることができ、活性層の劣化を防止することができる。この後のp型の層は、窒素と水素とを主成分とするキャリアガス雰囲気中で成長させることにより、良好な結晶性で成長させることができる。

【0042】

【発明の実施の形態】

以下、この発明の実施形態について図面を参照しながら説明する。なお、実施形態の全図において、同一または対応する部分には同一の符号を付す。

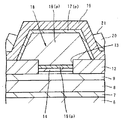

図1はこの発明の第1の実施形態によるGaN系半導体レーザを示す。このGaN系半導体レーザは、選択成長により形成されたリッジ構造およびSCH構造を有するものである。図2はこのGaN系半導体レーザのリッジ部近傍の拡大図である。また、図3はこのGaN系半導体レーザのエネルギーバンド、特にその伝導帯を示す。

【0043】

図1に示すように、この第1の実施形態によるGaN系半導体レーザにおいては、c面サファイア基板1の一主面に、横方向結晶成長技術(例えば、AppliedPhysics Letters vol.75(1999)pp.196-198) によりGaN系半導体層が積層されている。具体的には、c面サファイア基板1の一主面に、低温成長によるアンドープGaNバッファ層2とその上のアンドープGaN層3とからなり、〈1−100〉方向に延在するストライプが形成され、このストライプのアンドープGaN層3を種結晶としてn型GaNコンタクト層4が連続層として成長されている。ここで、このストライプの両側の部分のc面サファイア基板1の表層部も除去されており、この部分では、n型GaNコンタクト層4はこのc面サファイア基板1から浮いた構造になっている。そして、このn型GaNコンタクト層4上に、n型AlGaNクラッド層5、n側光導波層としてのアンドープInGaN光導波層6、例えばアンドープのInx Ga1-x N/Iny Ga1-y N多重量子井戸構造の活性層7、p側光導波層としてのアンドープInGaN光導波層8およびp側クラッド層としてのアンドープAlGaNクラッド層9が順次積層されている。アンドープInGaN光導波層6、アンドープInGaN光導波層8およびアンドープAlGaNクラッド層9はいずれもn- 型である。これらの層には横方向結晶成長の種結晶から上層に伝播した転位10と互いに隣接する種結晶からの横方向成長の会合部11が形成されている。

【0044】

n型GaNコンタクト層4の上層部からアンドープAlGaNクラッド層9までの層は全体として所定幅のメサ形状を有する。このメサ部のアンドープAlGaNクラッド層9上には、成長マスクである例えばSiO2 膜のような絶縁膜12が設けられている。この絶縁膜12の所定部分には、例えば〈1−100〉方向に延在するストライプ状の開口13が形成されている。そして、この開口13の部分において、下地のアンドープAlGaNクラッド層9上に、薄いアンドープAlGaNクラッド層9、アンドープInGaN層14、p型AlGaN電子ブロック層15、p側クラッド層としてのp型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17が選択成長により順次積層され、例えば〈1−100〉方向に延在するリッジ18が形成されている。このリッジ18の幅、言い換えれば絶縁膜12の開口13の幅は例えば1.6μmである。このリッジ18、すなわちレーザストライプ部は、横方向結晶成長の種結晶から上層に伝播した転位10と互いに隣接する種結晶からの横方向成長の会合部11との間の低欠陥領域の上方に位置している。アンドープInGaN層14はn- 型である。p側クラッド層としてp型AlGaN/GaN超格子クラッド層16を用いているのは、トンネル効果により正孔が通りやすくするためである。

【0045】

ここで、アンドープGaNバッファ層2は厚さが例えば30nmである。アンドープGaN層3は厚さが例えば2μmである。n型GaNコンタクト層4は厚さが例えば4μmであり、n型不純物として例えばシリコン(Si)がドープされている。n型AlGaNクラッド層5は厚さが例えば1.2μmであり、n型不純物として例えばSiがドープされ、Al組成比は例えば0.065である。アンドープInGaN光導波層6は厚さが例えば30nmであり、In組成比は例えば0.02である。また、アンドープInx Ga1-x N/Iny Ga1-y N多重量子井戸構造の活性層7は、障壁層としてのInx Ga1-x N層と井戸層としてのIny Ga1-y N層とが交互に積層されたもので、例えば、障壁層としてのInx Ga1-x N層の厚さが7nmでx=0.02、井戸層としてのIny Ga1-y N層の厚さが3.5nmでy=0.08、井戸数が3である。

【0046】

アンドープInGaN光導波層8は厚さが例えば30nmであり、In組成比は例えば0.02である。アンドープAlGaNクラッド層9は厚さが例えば100nmであり、Al組成比は例えば0.025である。アンドープInGaN層14は厚さが例えば5nmであり、In組成比は例えば0.02である。p型AlGaN電子ブロック層15は厚さが例えば10nmであり、Al組成比は例えば0.18である。p型AlGaN/GaN超格子クラッド層16は、例えば厚さが2.5nmのアンドープAlGaN層を障壁層とし、例えば厚さが2.5nmのMgがドープされたGaN層を井戸層とし、これらを交互に積層した構造を有し、平均のAl組成比は例えば0.06、全体の厚さは例えば400nmである。p型GaNコンタクト層17は厚さが例えば100nmであり、p型不純物として例えばMgがドープされている。

【0047】

p型GaNコンタクト層17を覆うようにp側電極19が、絶縁膜12上に延在して設けられている。このp側電極19は、Pd膜、Pt膜およびAu膜を順次積層した構造を有し、Pd膜、Pt膜およびAu膜の厚さは例えばそれぞれ10nm、100nmおよび300nmである。更に、メサ部の全体を覆うように例えば厚さが200nmのSiO2 膜のような絶縁膜20が設けられている。この絶縁膜20は電気絶縁および表面保護のためのものである。この絶縁膜20のうちのリッジ18の上の部分には開口21が設けられており、この開口21にp側電極19が露出している。一方、絶縁膜20のうちのメサ部に隣接する所定部分には開口22が設けられており、この開口22を通じてn型GaNコンタクト層4にn側電極23が接触している。このn側電極23は、Ti膜、Pt膜およびAu膜を順次積層した構造を有し、Ti膜、Pt膜およびAu膜の厚さは例えばそれぞれ10nm、50nmおよび100nmである。

【0048】

次に、この第1の実施形態によるGaN系半導体レーザの製造方法について説明する。

まず、あらかじめサーマルクリーニングなどにより表面を清浄化したc面サファイア基板1上に有機金属化学気相成長(MOCVD)法により例えば500℃程度の温度でアンドープGaNバッファ層2を成長させた後、同じくMOCVD法により例えば1000℃の成長温度でアンドープGaN層3を成長させる。

【0049】

次に、アンドープGaN層3の全面に例えばCVD法、真空蒸着法、スパッタリング法などにより例えば厚さが100nmのSiO2 膜(図示せず)を形成した後、このSiO2 膜上にリソグラフィーにより所定形状のレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、例えばフッ酸系のエッチング液を用いたウエットエッチング、または、CF4 やCHF3 などのフッ素を含むエッチングガスを用いたRIE法によりSiO2 膜をエッチングし、パターニングする。次に、この所定形状のSiO2 膜をマスクとして例えばRIE法によりc面サファイア基板1の表層部が除去されるまでエッチングを行う。このRIEのエッチングガスとしては、例えば塩素系ガスを用いる。このエッチングによって、種結晶となるストライプ形状のアンドープGaN層3が形成される。このストライプ形状のアンドープGaN層3の延在方向は〈1−100〉方向である。

【0050】

次に、エッチングマスクとして用いたSiO2 膜をエッチング除去した後、ストライプ形状のアンドープGaN層3を種結晶として上述の横方向結晶成長技術によりn型GaNコンタクト層4を成長させる。このときの成長温度は例えば1070℃とする。

【0051】

引き続いて、n型GaNコンタクト層4上に、MOCVD法により、n型AlGaNクラッド層5、アンドープInGaN光導波層6、アンドープのGa1-x Inx N/Ga1-y Iny N多重量子井戸構造の活性層7、アンドープInGaN光導波層8およびアンドープAlGaNクラッド層9を順次成長させる。

【0052】

次に、アンドープAlGaNクラッド層9の全面に例えばCVD法、真空蒸着法、スパッタリング法などにより例えば厚さが0.1μmのSiO2 膜のような絶縁膜12を形成した後、この絶縁膜12上にリソグラフィーによりメサ部の形状に対応した所定形状のレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、例えばフッ酸系のエッチング液を用いたウエットエッチング、または、CF4 やCHF3 などのフッ素を含むエッチングガスを用いたRIE法により絶縁膜12をエッチングし、開口13を形成する。次に、この開口13を有する絶縁膜12を成長マスクとして、例えばMOCVD法により、薄いアンドープAlGaNクラッド層9、アンドープInGaN層14、p型AlGaN電子ブロック層15、p側クラッド層としてのp型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17を順次選択成長させる。ここで、p型AlGaN/GaN超格子クラッド層16の選択成長は、絶縁膜12上に横方向成長して断面形状が台形となった時点で停止するようにする。

【0053】

これらのGaN系半導体層の成長温度は、例えば、n型AlGaNクラッド層5は900〜1000℃、アンドープInGaN光導波層6、活性層7、アンドープInGaN光導波層8、アンドープAlGaNクラッド層9、アンドープInGaN層14およびp型AlGaN電子ブロック層15は780℃、p型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17は900〜1000℃とする。

【0054】

これらのGaN系半導体層の成長原料は、例えば、Gaの原料としてはトリメチルガリウム((CH3 )3 Ga、TMG)、Alの原料としてはトリメチルアルミニウム((CH3 )3 Al、TMA)、Inの原料としてはトリメチルインジウム((CH3 )3 In、TMI)を、Nの原料としてはNH3 を用いる。ドーパントについては、n型ドーパントとしては例えばシラン(SiH4 )を、p型ドーパントとしては例えばビス=メチルシクロペンタジエニルマグネシウム((CH3 C5 H4 )2 Mg)あるいはビス=シクロペンタジエニルマグネシウム((C5 H5 )2 Mg)を用いる。

【0055】

また、これらのGaN系半導体層の成長時のキャリアガス雰囲気としては、n型GaNコンタクト層4およびn型AlGaNクラッド層5はN2 とH2 との混合ガス、アンドープInGaN光導波層6からp型AlGaN電子ブロック層15まではN2 ガス雰囲気、p型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17はN2 とH2 との混合ガスを用いる。この場合、アンドープInGaN光導波層6からp型AlGaN電子ブロック層15までの成長ではキャリアガス雰囲気をN2 雰囲気としており、キャリアガス雰囲気にH2 が含まれないので、アンドープInGaN光導波層6、活性層7、アンドープInGaN光導波層8およびアンドープInGaN層14からInが脱離するのを抑えることができ、これらの層の劣化を防止することができる。また、p型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17の成長時にはキャリアガス雰囲気をN2 とH2 との混合ガス雰囲気としているので、これらのp型層を良好な結晶性で成長させることができる。

【0056】

次に、上述のようにしてGaN系半導体層を成長させたc面サファイア基板1をMOCVD装置から取り出す。そして、リッジ18および絶縁膜12の全面に例えば真空蒸着法によりPd膜、Pt膜およびAu膜を順次形成してp側電極19を形成する。

【0057】

次に、p側電極19の全面に例えばCVD法、真空蒸着法、スパッタリング法などにより例えば厚さが0.1μmのSiO2 膜(図示せず)を形成した後、このSiO2 膜上にリソグラフィーによりメサ部の形状に対応した所定形状のレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、例えばフッ酸系のエッチング液を用いたウエットエッチング、または、CF4 やCHF3 などのフッ素を含むエッチングガスを用いたRIE法によりSiO2 膜をエッチングし、パターニングする。次に、この所定形状のSiO2 膜をマスクとして例えばRIE法によりn型GaNコンタクト層4に達するまでエッチングを行う。このRIEのエッチングガスとしては例えば塩素系ガスを用いる。このエッチングにより、n型GaNコンタクト層4の上層部、n型AlGaNクラッド層5、アンドープInGaN光導波層6、活性層7、アンドープInGaN光導波層8、アンドープAlGaNクラッド層9、絶縁膜12およびp側電極19がメサ形状にパターニングされる。

【0058】

次に、エッチングマスクとして用いたSiO2 膜をエッチング除去した後、基板全面に例えばCVD法、真空蒸着法、スパッタリング法などによりSiO2 膜のような絶縁膜20を成膜する。

【0059】

次に、リソグラフィーにより、n側電極形成領域を除いた領域の絶縁膜20の表面を覆うレジストパターン(図示せず)を形成する。

次に、このレジストパターンをマスクとして絶縁膜20をエッチングすることにより、開口22を形成する。

【0060】

次に、レジストパターンを残したままの状態で基板全面に例えば真空蒸着法によりTi膜、Pt膜およびAu膜を順次形成した後、レジストパターンをその上に形成されたTi膜、Pt膜およびAu膜とともに除去する(リフトオフ)。これによって、絶縁膜20の開口22を通じてn型GaNコンタクト層4にコンタクトしたn側電極23が形成される。次に、n側電極23をオーミック接触させるためのアロイ処理を行う。

【0061】

次に、リソグラフィーにより、リッジ18の上部の近傍のp側電極19が露出する開口を有するレジストパターン(図示せず)を形成する。

次に、このレジストパターンをマスクとして絶縁膜20をエッチングすることにより開口21を形成し、この開口21の部分にp側電極19を露出させる。

【0062】

この後、上述のようにしてレーザ構造が形成された基板を劈開などによりバー状に加工して両共振器端面を形成し、更にこれらの共振器端面に端面コーティングを施した後、このバーを劈開などによりチップ化する。

以上により、目的とするリッジ構造およびSCH構造を有するGaN系半導体レーザが製造される。

【0063】

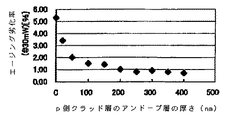

このGaN系半導体レーザにおいて、アンドープAlGaNクラッド層9とp型AlGaN/GaN超格子クラッド層16とからなるp側クラッド層中のアンドープAlGaNクラッド層9の厚さtを変化させ、そのときの動作電圧およびエージング劣化率を求めた結果を表1に示す。また、表1をグラフ化したものを図4および図5に示す。ここで、動作電圧は25℃で光出力が30mWのときのものである。エージング劣化率は、60℃で光出力が30mWのときのものであるが、エージング開始直後は動作電流IOPの上昇率が高いため、10〜100時間でのIOP上昇率を用いた。初期の動作電流IOPは55mAとした。アンドープAlGaNクラッド層9の比抵抗は数分の1Ωcm程度、p型AlGaN/GaN超格子クラッド層16の比抵抗は2Ωcm程度である。また、共振器長は600μm(0.06cm)、リッジ18の幅は1.6μm、p側クラッド層の全体の厚さは500nmとした。

【0064】

【0065】

いま、30mW(25℃)での動作電圧は5V以下が望ましく、エージング劣化率は、5000時間動作で動作電流の上昇率20%以下が実用レベルと考えると、表1、図4および図5より、これらの条件を満たすためには、アンドープAlGaNクラッド層9の厚さを50nm以上にする必要があることが分かる。また、アンドープAlGaNクラッド層9の厚さをより大きくすることにより、動作電圧およびエージング劣化率とも減少することが分かる。

【0066】

この第1の実施形態によれば、以下のような種々の利点を得ることができる。すなわち、p側クラッド層が活性層7側から順に厚さが例えば105nmのアンドープAlGaNクラッド層9と厚さが例えば400nmのp型AlGaN/GaN超格子クラッド層12とからなり、絶縁膜12の開口13の部分に選択成長により形成されるリッジ18と下地層との成長界面がn- 型のアンドープAlGaNクラッド層9に含まれることにより、リッジと下地層との成長界面がp型層の表面である従来技術のようにリッジを選択成長により形成する場合にn型不純物により成長界面が汚染されたり、成長界面にドナーとして働く欠陥が発生したりすることにより成長界面近傍がn型化してpnp構造が形成される問題が本質的に存在しない。このため、p側クラッド層全体の直列抵抗の低減を図り、動作電圧の低減を図ることができる。また、このようにp側クラッド層がアンドープAlGaNクラッド層9とp型AlGaN/GaN超格子クラッド層16とからなるので、その分だけ比抵抗が高いp型AlGaN/GaN超格子クラッド層16の厚さを小さくすることができることにより、p側クラッド層の全体をそれらの合計の厚さのp型AlGaN/GaN超格子クラッド層16で構成した場合に比べて、GaN系半導体レーザの動作電圧を例えば約0.16Vも低減することができる。また、p側クラッド層の全体の厚さは約500nmあり、十分大きいため、p側の光の閉じ込めを十分行うことができ、良好なFFPを得ることができる。すなわち、良好な光学特性を得るのに必要なp側クラッド層の厚さを確保しつつ、動作電圧の上昇の原因となっている高比抵抗のp型AlGaN/GaN超格子クラッド層16の厚さを約100nmも減少させて動作電圧の低減を図ることができる。

【0067】

また、活性層7とMgがドープされたp型層、すなわちp型AlGaN電子ブロック層15、p型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17との間の距離は、アンドープInGaN光導波層8、アンドープAlGaNクラッド層9およびアンドープInGaN層14の合計の厚さ、例えば30nm+100nm+5nm=135nmもあるため、結晶成長中やエージング中などにおいてp型層中のMgが活性層7に拡散するのを効果的に抑制することができ、それによってMgの拡散による活性層7の劣化を防止することができ、GaN系半導体レーザのエージング劣化率を低減することができ、信頼性および歩留まりの向上を図ることができる。

【0068】

また、活性層7とMgがドープされたp型層との間に格子歪層であるアンドープAlGaNクラッド層9があるため、これによってもp型層中のMgが活性層7に拡散するのを抑制することができ、活性層7の劣化をより効果的に防止することができる。

【0069】

また、Mgがドープされたp型層は一般にn型層に比べて結晶性が悪く、光の吸収が起こりやすいため、p型層が活性層7の付近にあると光吸収係数αが増大するが、上述のように活性層7とp型層とは135nmも離れているため、活性層7の付近のαを十分に低く抑えることができる。これによって、GaN系半導体レーザのしきい値電流密度Jth、したがってしきい値電流Ithを低減することができるとともに、スロープ効率の向上を図ることができる。更に、結晶性の悪いMgがドープされたp型層が光密度の高い活性層7の付近から上述のように十分に離れているため、光による活性層7の付近の結晶の劣化が生じにくく、GaN系半導体レーザの寿命および信頼性の向上を図ることができる。

【0070】

また、Al組成比が0.18と大きいp型AlGaN電子ブロック層15とInGaN層からなる活性層7との間には大きな格子定数差があるが、それらは上述のように135nmも離れているため、この格子定数差により活性層7に生じる歪を緩和することができ、発光効率の向上を図ることができる。このため、量子効率の向上により、しきい値電流密度Jth、したがってしきい値電流Ithを低減することができるとともに、スロープ効率の向上を図ることができる。

【0071】

また、アンドープAlGaNクラッド層9とp型AlGaN電子ブロック層11との間に活性層7と格子定数がほぼ等しいアンドープInGaN層14が設けられているため、活性層7とp型AlGaN電子ブロック層15およびp型AlGaN/GaN超格子クラッド層16との間に大きな格子定数差があっても、これらのp型AlGaN電子ブロック層15およびp型AlGaN/GaN超格子クラッド層16により活性層7に生じる歪を緩和することができる。このため、GaN系半導体レーザのしきい値電流密度Jth、したがってしきい値電流Ithを低減することができるとともに、スロープ効率の向上を図ることができる。

【0072】

また、上述のしきい値電流Ithの低減により、GaN系半導体レーザの雑音特性の向上を図ることができる。

【0073】

また、活性層7に注入された電子が活性層7を通り過ぎてアンドープAlGaNクラッド層9に到達すると、アンドープInGaN光導波層8とこのアンドープAlGaNクラッド層9との間の伝導帯のエネルギー差ΔEC (図3)より大きなエネルギーを持つ電子は、このアンドープAlGaNクラッド層9を飛び越える際にΔEC 分だけエネルギーが低下する。一方、ΔEC より小さいエネルギーしか持っていない電子は、アンドープAlGaNクラッド層9を飛び越えることができないため、アンドープInGaN光導波層8に留まることになる。このように、アンドープAlGaNクラッド層9を飛び越えようとする電子のエネルギーや数が減少することにより、GaN系半導体レーザのスロープ効率の向上を図ることができる。また、GaN系半導体レーザの高温、高出力駆動時の電子のオーバーフローを防止することができ、GaN系半導体レーザの動作電流の低減、動作電圧の低減および特性温度T0 の向上を図ることができる。

【0074】

また、リッジ18の部分にあるp型層は全てこのリッジ18の内部に収まっているので、GaN系半導体レーザの動作温度が上昇してこれらのp型層中のMgが活性化しp型層が低抵抗化しても、リッジ18の両脇に漏れ出る電流を極めて少なく抑えることができる。このため、GaN系半導体レーザの特性温度T0 を従来のGaN系半導体レーザに比べて著しく高くすることが可能である。具体的には、特性温度T0 を例えば230K程度と、従来のGaN系半導体レーザの特性温度T0 に比べて約90Kも高くすることが可能である。この230K程度という特性温度T0 は、他の材料系の半導体レーザと比較しても、これまで到底得られなかった著しく高い値である。更に、光出力−電流特性の傾き、すなわちスロープ効率についても、このGaN系半導体レーザは、従来のGaN系半導体レーザに比べてかなり大きくすることが可能である。

【0075】

また、リッジ18の両脇の部分における活性層7とアンドープAlGaNクラッド層9の表面(絶縁膜12とアンドープAlGaNクラッド層9との界面)との間の距離はGaN系半導体レーザの光学特性、特にリッジ18の部分における横方向屈折率差Δnに影響を及ぼし、ひいてはGaN系半導体レーザの製造歩留まりを左右するが、この距離は結晶成長により精度良く制御することができるため、製造上のばらつきが少なく、したがってGaN系半導体レーザの製造歩留まりの向上を図ることができる。

【0076】

更に、リッジ幅は絶縁膜12の開口13の幅により決定されるところ、この開口13の幅の制御は絶縁膜12のウエットエッチングなどにより精度良くしかも容易に行うことができることから、RIEなどのドライエッチングによりリッジを形成する場合に比べて生産性が高く、GaN系半導体レーザの製造コストの低減を図ることができる。

【0077】

また、p型AlGaN電子ブロック層15における正孔の活性化エネルギーは高いため、常温では大部分の正孔は不活性である。しかしながら、高温になるほど正孔が活性化してp型AlGaN電子ブロック層15の電子ブロッキング効果は高まる。ところが、従来のGaN系半導体レーザにおいては、リッジの両脇への電流漏れ量が多いため、上記効果は見えにくかったものと推測することができる。これに対し、このGaN系半導体レーザによれば、上述のようにリッジ18の両脇への電流漏れ量が極めて少ないことにより、p型AlGaN電子ブロック層15の電子ブロッキング効果は高く、高温、高出力駆動時においても電子のオーバーフローを効果的に防止することができる。

【0078】

また、上述のように高温駆動時の漏れ電流、すなわち無効電流が低減されることにより、しきい値電流Ithの低減を図ることができ、特性温度T0 の向上を図ることができるとともに、高温でも低雑音のGaN系半導体レーザを実現することができる。

【0079】

また、上述のように特性温度T0 の著しい向上により、いわゆるドループ特性を改善することができる。このドループ特性は、レーザビームプリンタなどの光源にGaN系半導体レーザを適用する上で重要なパラメータである。また、同一基板上に複数のGaN系半導体レーザを互いに隣接して集積化する場合においても、GaN系半導体レーザの特性温度T0 が著しく高いことにより、これらのGaN系半導体レーザ間の熱的クロストークを低く抑えることができるため、マルチビームレーザなどへの応用にも適している。

【0080】

また、p側クラッド層の一部をアンドープAlGaNクラッド層9により構成しているため、活性層7よりp側の部分に存在するp型層は全体として少なく、したがって活性層7からオーバーフローした電子がp型層において再結合中心にトラップされて非発光再結合する確率が小さい。高温になるほど、p型層で電子がトラップされる確率が高まると仮定すると、このGaN系半導体レーザの構造は無効電流低減に効果的と考えられる。

【0081】

また、上述のスロープ効率の向上と温度特性の向上とによって、Mgがドープされた結晶性の悪いp型層に電子がオーバーフローにより注入されて結晶を破壊することが少なくなるため、GaN系半導体レーザの信頼性および寿命の向上を図ることができる。

【0082】

更に、アンドープInGaN光導波層6からp型AlGaN電子ブロック層11までの成長ではキャリアガス雰囲気をN2 雰囲気としており、キャリアガス雰囲気にH2 が含まれないので、特に活性層7からInが脱離するのを抑えることができ、その劣化を防止することができ、GaN系半導体レーザの信頼性および寿命の向上を図ることができる。

【0083】

以上により、動作電圧およびしきい値電流が低く、温度特性が良好で長寿命かつ高信頼性のGaN系半導体レーザを実現することができる。

この第1の実施形態によるGaN系半導体レーザは、高温、高出力駆動時の動作電流および動作電圧の低減を図ることができ、長寿命でもあることから、特に光ディスクに対する書き込み用高出力半導体レーザとして用いて好適なものである。

【0084】

次に、この発明の第2の実施形態によるGaN系半導体レーザについて説明する。図6はこのGaN系半導体レーザのエネルギーバンド図を示す。

図6に示すように、この第2の実施形態によるGaN系半導体レーザにおいては、第1の実施形態によるGaN系半導体レーザにおけるアンドープAlGaNクラッド層9の代わりに、アンドープAlGaN/GaN超格子クラッド層24が設けられている。ここで、このアンドープAlGaN/GaN超格子クラッド層24は、例えば厚さが2.5nmのアンドープAlGaN層を障壁層とし、例えば厚さが2.5nmのGaN層を井戸層とし、これらを交互に積層した構造を有し、平均のAl組成比は例えば0.025〜0.10、全体の厚さは例えば100〜500nmである。その他の構成は、第1の実施形態によるGaN系半導体レーザと同様であるので、説明を省略する。

このGaN系半導体レーザの製造方法は、第1の実施形態によるGaN系半導体レーザの製造方法と同様であるので、説明を省略する。

【0085】

この第2の実施形態によれば、p側クラッド層のうちのアンドープ層がアンドープAlGaN/GaN超格子クラッド層24により構成されているので、p側電極19側から注入されてこのアンドープAlGaN/GaN超格子クラッド層24に到達した正孔はこのアンドープAlGaN/GaN超格子クラッド層24をトンネル効果により容易に通り抜けて活性層7に注入されるので、活性層7への正孔の注入が容易となり、GaN系半導体レーザの動作電圧のより一層の低減を図ることができる。また、アンドープAlGaN/GaN超格子クラッド層24に存在するヘテロ界面により、p型層中のMgが活性層7に拡散するのをより効果的に防止することができ、活性層7の劣化をより効果的に防止することができる。その他の利点は第1の実施形態と同様である。

【0086】

次に、この発明の第3の実施形態によるGaN系半導体レーザについて説明する。

この第3の実施形態によるGaN系半導体レーザは、基本的には第1の実施形態によるGaN系半導体レーザと同様な構造を有するが、アンドープInGaN光導波層8およびp型AlGaN/GaN超格子クラッド層16の厚さが第1の実施形態によるGaN系半導体レーザと異なる。具体的には、第1の実施形態によるGaN系半導体レーザにおいては、アンドープInGaN光導波層8の厚さは例えば30nm、p型AlGaN/GaN超格子クラッド層16の厚さは例えば400nmであるのに対し、この第3の実施形態によるGaN系半導体レーザにおいては、アンドープInGaN光導波層8の厚さは例えば24.5nm、p型AlGaN/GaN超格子クラッド層16の厚さは例えば500nmである。その他の構成は、第1の実施形態によるGaN系半導体レーザと同様である。

また、このGaN系半導体レーザの製造方法は、第1の実施形態によるGaN系半導体レーザの製造方法と同様であるので、説明を省略する。

【0087】

この第3の実施形態によれば、第1の実施形態と同様な利点を得ることができる。

【0088】

次に、この発明の第4の実施形態によるGaN系半導体レーザについて説明する。図7はこのGaN系半導体レーザのエネルギーバンド、特にその伝導帯を示す。

図7に示すように、この第4の実施形態によるGaN系半導体レーザにおいては、p型AlGaN/GaN超格子クラッド層16中にp型AlGaN電子ブロック層15が設けられている。すなわち、第1の実施形態によるGaN系半導体レーザにおいては、p型AlGaN電子ブロック層15はアンドープInGaN層14とp型AlGaN/GaN超格子クラッド層16との界面に設けられているのに対し、この第4の実施形態によるGaN系半導体レーザにおいては、p型AlGaN電子ブロック層15はp型AlGaN/GaN超格子クラッド層16中にアンドープInGaN層14から離れて設けられている。ここで、アンドープAlGaNクラッド層9とp型AlGaN電子ブロック層15との間に存在するp型AlGaN/GaN超格子クラッド層16の厚さは例えば10〜50nm程度である。その他の構成は、第1の実施形態によるGaN系半導体レーザと同様である。

また、このGaN系半導体レーザの製造方法は、第1の実施形態によるGaN系半導体レーザの製造方法と同様であるので、説明を省略する。

この第4の実施形態によれば、第1の実施形態と同様な利点を得ることができる。

【0089】

次に、この発明の第5の実施形態によるGaN系半導体レーザを示す。このGaN系半導体レーザは、選択成長により形成されたリッジ構造およびSCH構造を有するが、基板としてn型GaN基板を用いていることが第1〜第4の実施形態と異なる。図8にこのGaN系半導体レーザを示す。

【0090】

図8に示すように、この第5の実施形態によるGaN系半導体レーザにおいては、例えばc面方位のn型GaN基板25上に、n型不純物として例えばSiがドープされたn型GaN層26がバッファ層(低温成長によるバッファ層とは異なる)として設けられ、その上に、n型AlGaNクラッド層5、n側光導波層としてのアンドープInGaN光導波層6、例えばアンドープのInx Ga1-x N/Iny Ga1-y N多重量子井戸構造の活性層7、p側光導波層としてのアンドープInGaN光導波層8およびp側クラッド層としてのアンドープAlGaNクラッド層9が順次積層されている。

【0091】

アンドープAlGaNクラッド層9上には、成長マスクである例えばSiO2 膜のような絶縁膜12が設けられている。この絶縁膜12の所定部分には、例えば〈1−100〉方向に延在するストライプ状の開口13が形成されている。そして、この開口13の部分において、下地のアンドープAlGaNクラッド層9上に、薄いアンドープAlGaNクラッド層9、アンドープInGaN層14、p型AlGaN電子ブロック層15、p側クラッド層としてのp型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17が選択成長により順次積層され、例えば〈1−100〉方向に延在するリッジ18が形成されている。

【0092】

p型GaNコンタクト層17を覆うようにp側電極19が、絶縁膜12上に延在して設けられている。一方、n型GaN基板25の裏面にn側電極23が接触している。

上記以外のことは第1の実施形態と同様であるので、説明を省略する。

【0093】

次に、この第5の実施形態によるGaN系半導体レーザの製造方法について説明する。

まず、あらかじめサーマルクリーニングなどにより表面を清浄化したn型GaN基板25上にMOCVD法によりn型AlGaNクラッド層5、アンドープInGaN光導波層6、アンドープのGa1-x Inx N/Ga1-y Iny N多重量子井戸構造の活性層7、アンドープInGaN光導波層8およびアンドープAlGaNクラッド層9を順次成長させる。

【0094】

次に、アンドープAlGaNクラッド層9の全面に絶縁膜12を形成した後、エッチングによりこの絶縁膜12に開口13を形成する。次に、この開口13を有する絶縁膜12を成長マスクとして、例えばMOCVD法により、薄いアンドープAlGaNクラッド層9、アンドープInGaN層14、p型AlGaN電子ブロック層15、p側クラッド層としてのp型AlGaN/GaN超格子クラッド層16およびp型GaNコンタクト層17を順次選択成長させる。

【0095】

次に、上述のようにしてGaN系半導体層を成長させたc面サファイア基板1をMOCVD装置から取り出す。そして、リッジ18および絶縁膜12の全面にp側電極19を形成する。

次に、n型GaN基板25の裏面にn側電極23を形成する。

【0096】

この後、上述のようにしてレーザ構造が形成された基板を劈開などによりバー状に加工して両共振器端面を形成し、更にこれらの共振器端面に端面コーティングを施した後、このバーを劈開などによりチップ化する。

以上により、目的とするリッジ構造およびSCH構造を有するGaN系半導体レーザが製造される。

このGaN系半導体レーザの製造方法の上記以外のことは第1の実施形態と同様である。

【0097】

この第5の実施形態によれば、第1の実施形態と同様な利点を得ることができるほか、例えばGaAs系半導体レーザと同様に、p側電極19およびn側電極23がそれぞれ基板の表面および裏面に形成された構造とすることができることにより、GaAs系半導体レーザの組み立てに用いるボンディング装置などを使用することができ、特殊なボンディング装置などの組み立て装置を導入する必要がなく、その分だけGaN系半導体レーザの製造コストの低減を図ることができるという利点を得ることができる。更に、チップサイズを小さくすることができため、それによってもGaN系半導体レーザの製造コストの低減を図ることができる。

【0098】

以上、この発明の実施形態について具体的に説明したが、この発明は、上述の実施形態に限定されるものではなく、この発明の技術的思想に基づく各種の変形が可能である。

【0099】

例えば、上述の第1〜第5の実施形態において挙げた数値、構造、形状、基板、原料、プロセスなどはあくまでも例に過ぎず、必要に応じて、これらと異なる数値、構造、形状、基板、原料、プロセスなどを用いてもよい。

【0100】

具体的には、例えば、上述の第1〜第5の実施形態においては、レーザ構造を形成するn型層を基板上に最初に積層し、その上にp型層を積層しているが、これと積層順序を逆にし、基板上に最初にp型層を積層し、その上にn型層を積層した構造としてもよい。

【0101】

また、上述の第1〜第5の実施形態においては、n側光導波層としてのアンドープInGaN光導波層6およびp側光導波層としてのアンドープInGaN光導波層8は互いに同一組成であるが、これらのアンドープInGaN光導波層6およびアンドープInGaN光導波層8の組成は、良好な光学特性が得られる限り、互いに異なっていてもよく、例えばアンドープInGaN光導波層8のIn組成をアンドープInGaN光導波層6より低くしてもよい。更には、必要に応じて、n側光導波層およびp側光導波層の材料としてInGaNと異なる組成のもの、例えばGaNを用いてもよい。

【0102】

また、上述の第1〜第4の実施形態においては、c面サファイア基板を用いているが、必要に応じて、SiC基板、Si基板、スピネル基板などを用いてもよい。また、GaNバッファ層の代わりに、AlNバッファ層やAlGaNバッファ層を用いてもよい。

【0103】

また、上述の第1〜第5の実施形態においては、この発明をSCH構造のGaN系半導体レーザに適用した場合について説明したが、この発明は、例えば、DH(Double Heterostructure)構造のGaN系半導体レーザに適用してもよいことはもちろん、GaN系発光ダイオードに適用してもよい。

【0104】

更に、上述の第1〜第5の実施形態においては、p型AlGaN/GaN超格子クラッド層12において、AlGaN層にはMgをドープしていないが、必要に応じて、このAlGaN層にもMgをドープしてもよく、あるいは、GaN層にはMgをドープせず、AlGaN層にのみMgをドープしてもよい。

【0105】

【発明の効果】

以上説明したように、この発明によれば、p側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、リッジと下地層との成長界面が第1の層または第1の層と第2の層との間に第1の層と接してアンドープまたはn型の他の層が設けられる場合には第1の層もしくはこの他の層に含まれることにより、成長界面近傍がn型化してpnp構造が形成される問題が本質的に存在せず、したがってp側クラッド層全体の直列抵抗の低減を図り、動作電圧の低減を図ることができる。また、このようにp側クラッド層が活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなることにより、半導体発光素子に対して良好な光場を得て良好な光学特性を得るのに必要なp側クラッド層の厚さを確保しつつ、動作電圧上昇の原因となる高比抵抗のp型層の厚さを可能な限り薄くして半導体発光素子の動作電圧の低減を図ることができる。また、活性層と第2の層との間の距離を十分に大きくすることができるため、第2の層のp型不純物が活性層に拡散を抑えて活性層の劣化を防止することができる。更に、特に、第2の層がこの第2の層よりバンドギャップが大きいp型の第3の層を有する場合には、この第3の層により、活性層に注入される電子がオーバーフローするのを抑制することができる。

【0106】

また、リッジの部分のp型層は全てリッジの内部に収まっていることにより、半導体発光素子の動作時に注入される電流がリッジの外部に漏れ出るのを効果的に抑えることができ、これによって従来に比べて著しく高い特性温度を得ることができ、極めて良好な温度特性を得ることができる。

【0107】

また、Inを含む層を含む特定の層の成長を、実質的に水素を含まず、窒素を主成分とするキャリアガス雰囲気中で行うようにしているので、そのInを含む層、例えば活性層からInが脱離するのを効果的に抑えることができ、活性層の劣化を防止することができ、半導体発光素子の信頼性および寿命の向上を図ることができる。

【0108】

また、活性層とこの活性層に最も近い、p型不純物がドープされたp型の層との間の距離が50nm以上であるので、このp型の層にドープされたp型不純物の活性層への拡散を大幅に減少させることができ、活性層の劣化を防止することができ、半導体発光素子の信頼性および寿命の向上を図ることができる。

【図面の簡単な説明】

【図1】この発明の第1の実施形態によるGaN系半導体レーザを示す断面図である。

【図2】この発明の第1の実施形態によるGaN系半導体レーザの要部の拡大断面図である。

【図3】この発明の第1の実施形態によるGaN系半導体レーザのエネルギーバンド構造を示す略線図である。

【図4】この発明の第1の実施形態によるGaN系半導体レーザにおけるp側クラッド層のアンドープ層の厚さによる動作電圧の変化を示す略線図である。

【図5】この発明の第1の実施形態によるGaN系半導体レーザにおけるp側クラッド層のアンドープ層の厚さによるエージング劣化率の変化を示す略線図である。

【図6】この発明の第2の実施形態によるGaN系半導体レーザのエネルギーバンド構造を示す略線図である。

【図7】この発明の第4の実施形態によるGaN系半導体レーザのエネルギーバンド構造を示す略線図である。

【図8】この発明の第5の実施形態によるGaN系半導体レーザを示す断面図である。

【図9】選択成長によりリッジ構造を形成する従来のGaN系半導体レーザの要部を示す断面図である。

【図10】選択成長によりリッジ構造を形成する従来のGaN系半導体レーザの問題点を説明するための断面図である。

【符号の説明】

1・・・c面サファイア基板、4・・・n型GaNコンタクト層、5・・・n型AlGaNクラッド層、6・・・アンドープInGaN光導波層、7・・・活性層、8・・・アンドープInGaN光導波層、9・・・アンドープAlGaNクラッド層、12・・・絶縁膜、13・・・開口、14・・・アンドープInGaN層、15・・・p型AlGaN電子ブロック層、16・・・p型AlGaN/GaN超格子クラッド層、17・・・p型GaNコンタクト層、18・・・リッジ、19・・・p側電極、20・・・絶縁膜、23・・・n側電極、24・・・アンドープAlGaN/GaN超格子クラッド層、25・・・n型GaN基板

Claims (7)

- n側クラッド層と、

上記n側クラッド層上の活性層と、

上記活性層上のp側クラッド層とを有し、

上記p側クラッド層に選択成長により形成されたリッジを有する、窒化物系III−V族化合物半導体を用いた半導体発光素子において、

上記p側クラッド層が上記活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、上記第2の層がこの第2の層よりバンドギャップが大きい第3の層を有し、かつ、上記第1の層の厚さが50nm以上400nm以下であり、

上記第1の層上に絶縁膜からなる成長マスクが形成され、この成長マスクの開口部における上記第1の層上に上記リッジが選択成長されており、

上記リッジの成長界面が上記第1の層に含まれ、

上記第2の層は上記成長マスク上に横方向成長して上部の断面形状が台形となっており、

上記第2の層の上記上部の表面の全体にp型コンタクト層を有し、上記p型コンタクト層を覆うようにp側電極が設けられている

ことを特徴とする半導体発光素子。 - 上記n側クラッド層と上記活性層との間にn側光導波層が設けられ、上記p側クラッド層と上記活性層との間にp側光導波層が設けられている

ことを特徴とする請求項1記載の半導体発光素子。 - 上記第2の層の厚さが0nmより大きく、550nm以下である

ことを特徴とする請求項1記載の半導体発光素子。 - n側クラッド層と、

上記n側クラッド層上の活性層と、

上記活性層上のp側クラッド層とを有し、

上記p側クラッド層に選択成長により形成されたリッジを有する、窒化物系III−V族化合物半導体を用いた半導体発光素子において、

上記p側クラッド層が上記活性層側から順にアンドープまたはn型の第1の層とp型不純物がドープされたp型の第2の層とからなり、かつ、上記第1の層の厚さが50nm以上400nm以下であり、

上記第1の層上に絶縁膜からなる成長マスクが形成され、この成長マスクの開口部における上記第1の層上に上記リッジが選択成長されており、

上記リッジの成長界面が上記第1の層に含まれ、

上記第2の層は上記成長マスク上に横方向成長して上部の断面形状が台形となっており、

上記第2の層の上記上部の表面の全体にp型コンタクト層を有し、上記p型コンタクト層を覆うようにp側電極が設けられている

ことを特徴とする半導体発光素子。 - 上記n側クラッド層と上記活性層との間にn側光導波層が設けられ、上記p側クラッド層と上記活性層との間にp側光導波層が設けられている

ことを特徴とする請求項4記載の半導体発光素子。 - 上記第2の層の厚さが0nmより大きく、550nm以下である

ことを特徴とする請求項4記載の半導体発光素子。 - 上記第2の層がこの第2の層よりバンドギャップが大きい第3の層を有する

ことを特徴とする請求項4記載の半導体発光素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002041171A JP4178807B2 (ja) | 2002-02-19 | 2002-02-19 | 半導体発光素子およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002041171A JP4178807B2 (ja) | 2002-02-19 | 2002-02-19 | 半導体発光素子およびその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004380818A Division JP4179280B2 (ja) | 2004-12-28 | 2004-12-28 | 半導体発光素子の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003243772A JP2003243772A (ja) | 2003-08-29 |

| JP2003243772A5 JP2003243772A5 (ja) | 2005-08-11 |

| JP4178807B2 true JP4178807B2 (ja) | 2008-11-12 |

Family

ID=27781664

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002041171A Expired - Fee Related JP4178807B2 (ja) | 2002-02-19 | 2002-02-19 | 半導体発光素子およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4178807B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7485902B2 (en) * | 2002-09-18 | 2009-02-03 | Sanyo Electric Co., Ltd. | Nitride-based semiconductor light-emitting device |

| JP4508662B2 (ja) * | 2004-01-22 | 2010-07-21 | シャープ株式会社 | 窒化ガリウム系半導体発光素子 |

| JP2005294753A (ja) * | 2004-04-05 | 2005-10-20 | Toshiba Corp | 半導体発光素子 |

| JP2007066981A (ja) | 2005-08-29 | 2007-03-15 | Toshiba Corp | 半導体装置 |

| JP2007235107A (ja) * | 2006-02-02 | 2007-09-13 | Mitsubishi Electric Corp | 半導体発光素子 |

| KR101221067B1 (ko) * | 2006-02-09 | 2013-01-11 | 삼성전자주식회사 | 리지 도파형 반도체 레이저 다이오드 |

| US8178889B2 (en) | 2006-07-05 | 2012-05-15 | Panasonic Corporation | Semiconductor light emitting element having a single defect concentrated region and a light emitting which is not formed on the single defect concentrated region |

| JP2010187034A (ja) * | 2010-06-01 | 2010-08-26 | Toshiba Corp | 半導体装置 |

| JP7323786B2 (ja) | 2019-01-17 | 2023-08-09 | 日亜化学工業株式会社 | 半導体レーザ素子 |

-

2002

- 2002-02-19 JP JP2002041171A patent/JP4178807B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003243772A (ja) | 2003-08-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3864735B2 (ja) | 半導体発光素子およびその製造方法 | |

| US6870193B2 (en) | Semiconductor light emitting device and its manufacturing method | |

| US6319742B1 (en) | Method of forming nitride based semiconductor layer | |

| JP5036617B2 (ja) | 窒化物系半導体発光素子 | |

| US7755101B2 (en) | Semiconductor light emitting device | |

| JP2008109092A (ja) | 半導体発光素子 | |

| JP3460581B2 (ja) | 窒化物半導体の成長方法及び窒化物半導体素子 | |

| JP2004063537A (ja) | 半導体発光素子およびその製造方法ならびに半導体装置およびその製造方法 | |

| JP4178807B2 (ja) | 半導体発光素子およびその製造方法 | |

| JP4877294B2 (ja) | 半導体発光素子の製造方法 | |

| JP2003086903A (ja) | 半導体発光素子およびその製造方法 | |

| JP4449296B2 (ja) | GaN系半導体発光素子 | |

| JP4179280B2 (ja) | 半導体発光素子の製造方法 | |

| JP5874689B2 (ja) | 半導体発光素子およびその製造方法 | |

| JP3963233B2 (ja) | 窒化ガリウム系化合物半導体発光素子及びその製造方法 | |

| JP3938207B2 (ja) | 半導体発光素子の製造方法 | |

| JP4969210B2 (ja) | 半導体レーザおよびその製造方法 | |

| JP2001210912A (ja) | 半導体レーザおよびその製造方法 | |

| JP2006041490A (ja) | 半導体レーザ素子及びその製造方法 | |

| Hayashi et al. | Semiconductor device with SiO 2 film formed on side surface of nitride based semiconductor layer |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20041224 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20050111 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060912 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070206 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070402 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080805 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080818 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110905 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120905 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130905 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |