JP4159713B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4159713B2 JP4159713B2 JP33179499A JP33179499A JP4159713B2 JP 4159713 B2 JP4159713 B2 JP 4159713B2 JP 33179499 A JP33179499 A JP 33179499A JP 33179499 A JP33179499 A JP 33179499A JP 4159713 B2 JP4159713 B2 JP 4159713B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- pair

- impurity regions

- film

- impurity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

【発明が属する技術分野】

本願発明は薄膜トランジスタ(以下、TFTという)及び薄膜トランジスタで構成された回路を有する半導体装置に関する。半導体装置として例えば、アクティブマトリクス型液晶ディスプレイ(以下、AM−LCDという)に代表される電気光学装置またはプロセッサ等の半導体回路並びその様な電気光学装置や半導体回路を搭載した電気器具(電子機器)の構成に関する。なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電気器具も半導体装置である。

【0002】

【従来の技術】

近年、ポリシリコン膜を利用したTFTで回路を構成したアクティブマトリクス型液晶表示装置が注目されている。これはマトリクス状に配置された複数の画素によって液晶にかかる電界をマトリクス状に制御し、高精細な画像表示を実現するものである。

【0003】

この様なアクティブマトリクス型液晶表示装置は、解像度がXGA、SXGAと高精細になるに従い、画素数だけでも100万個を超えるようになる。そしてその全てを駆動するためのドライバ回路は非常に複雑かつ多くのTFTによって形成される。

【0004】

実際の液晶表示装置(液晶パネルともいう)に要求される仕様は厳しく、全ての画素が正常に動作するためには画素、ドライバともに高い信頼性が確保されなければならない。特に、ドライバ回路で異常が発生すると一列(または一行)の画素が全滅するといった線欠陥と呼ばれる不良を招くことにつながる。

【0005】

ところが、ポリシリコン膜を利用したTFTは信頼性の面でまだまだLSIなどに用いられるMOSFET(単結晶半導体基板上に形成されたトランジスタ)に及ばないとされている。そして、この弱点が克服されない限り、TFTでLSI回路を形成することは困難であるとの見方が強まっている。

【0006】

【発明が解決しようとする課題】

本出願人はTFTとMOSFETとを比較した時に、TFTの構造上の問題が信頼性(特にホットキャリア耐性)に影響していると考えた。

【0007】

本願発明はそのような問題点を克服するための技術であり、MOSFETと同等またはそれ以上の信頼性を誇るTFTを実現することを課題とする。そして、そのようなTFTで回路を形成した半導体回路を有する信頼性の高い半導体装置を実現することを課題とするものである。

【0008】

【課題を解決するための手段】

上述した課題を解決するために、本発明に係るnチャネル型TFT(以下、NTFTという)は、反転層(チャネル)が形成される半導体層にソース領域またはドレイン領域として機能するn型の第1の不純物領域と、チャネル形成領域と第1の不純物領域の間に第1の不純物領域と同じ導電型を示す二種類の不純物領域(第2の不純物領域及び第3の不純物領域)を有する。これら第2及び第3の不純物領域はその導電型を決める不純物濃度が第1の不純物領域よりも低く、LDD領域とも呼ばれる高抵抗領域として機能する。

【0009】

第2の不純物領域はゲート絶縁膜を介してゲート電極と重なった低濃度不純物領域であり、ホットキャリア耐性を高める作用を有する。他方、第3の不純物領域はゲート電極と重ならない低濃度不純物領域であり、オフ電流の増加を防ぐ作用を有する。

【0010】

そして、本願発明で最も特徴的な点は、同一基板上に第2の不純物領域の長さが異なる第1のNTFTと第2のNTFTとが存在する点である。即ち、動作電圧の違いによって第2の不純物領域の長さを異なるものとして適切なTFTを配置することを特徴としている。具体的には、第2のTFTの動作電圧が第1のTFTの動作電圧よりも高い場合、第2の不純物領域の長さは第2のTFTの方が第1のTFTよりも長いことを特徴とする。

【0011】

従来、いわゆるGOLD〔Gate-drain OverLapped LDD〕構造によってホットキャリア耐性が向上することは知られており、その技術をTFTに応用する試みはなされてきたが、従来のGOLD構造ではオフ電流(TFTがオフ状態にある時に流れる電流)が高くなってしまうという問題は無視されてきた。

【0012】

そこで本出願人は上記問題点を解決すべく検討し、ゲート電極と重ならない不純物領域(第3不純物領域)を設けることによってオフ電流が劇的に低下することを確認した。従って、本願発明において第3不純物領域を積極的に設ける点が特徴であると言える。

【0013】

なお、ゲート電極とはゲート絶縁膜を挟んで半導体層と交差している電極であって、半導体層に電界を印加して反転層を形成するための電極である。ゲート配線においては、ゲート絶縁膜を挟んで半導体層と交差している部分がゲート電極である。

【0014】

更に、本発明において、ゲート電極は、ゲート電極周囲は中央の平坦部から外側に向かって、その膜厚が線形または段階的に減少する。即ち、いわゆるテーパー形状にパターニングしてある点に特徴がある。

【0015】

第2の不純物領域にはゲート電極のテーパー部を通して(通過させて)、導電型を付与する不純物が添加されるため、その濃度勾配はゲート電極の側面の傾斜(テーパー部分の膜厚の変化)を反映することになる。すなわち、第2の不純物領域へ添加される不純物の濃度は、チャネル形成領域から第1不純物領域に向かって徐々に増加することになる。

【0016】

これはテーパー部分の膜厚の差によって不純物の到達深さが変化するためである。即ち、不純物の深さ方向の濃度分布をみた時、ピーク濃度で不純物が添加される深さは、ゲート電極のテーパー部分の傾斜に沿った形で変化する。

【0017】

このような構造とすることで、前記第2不純物領域の内部において不純物の濃度勾配を形成することができる。本願発明では積極的にこのような濃度勾配を形成して電界緩和効果を高める構造のTFTを形成する点に特徴がある。

【0018】

また、本発明において、他のゲート電極の構成においては、ゲート絶縁膜に接する第1のゲート電極と、第1のゲート電極上に形成された第2のゲート電極が積層されている。勿論、第1のゲート電極を単層で用いても構わない。

【0019】

この構成において、第1のゲート電極の側面(テーパー部)はゲート絶縁膜となす角度(θで表す。以下、テーパー角という)が3度以上40度以下(好ましくは5度以上35度以下、さらに好ましくは8度以上20度以下)であるテーパー形状となっている。他方、第2のゲート電極はチャネル長方向の幅が第1のゲート電極よりも狭くなっている。

【0020】

上記の積層型のゲート電極を有する薄膜トランジスタにおいても、第2の不純物領域に含まれる不純物の濃度分布は、第1のゲート電極におけるテーパー部の膜厚の変化を反映し、その不純物濃度はチャネル形成領域から第1の不純物領域に向かって徐々に増加することとなる。

【0021】

以上のような構造のNTFTはホットキャリア耐性が高い上、耐圧特性(電界集中による絶縁破壊等に耐える特性)も良いため、オン電流(TFTがオン状態にある時に流れる電流)の経時劣化を効果的に防止することが可能である。これは第2の不純物領域を設けたことによる効果である。

【0022】

さらに、第3の不純物領域を設けたことによって大幅にオフ電流を低減することが可能となる。この第3の不純物領域を設ける点が本願発明のNTFTの特徴であることは前述の通りである。

【0023】

このように本願発明のNTFTは非常に信頼性が高く、PTFTと相補的に組み合わせて形成したCMOS回路や液晶表示装置やEL(エレクトロルミネセンス)表示装置の画素部(画素マトリクス回路)などに用いた場合に信頼性の高い回路を形成することを可能とする。即ち、従来に比べNTFTの劣化による回路の能力低下を防ぐことができる。

【0024】

なお、本願発明においてpチャネル型薄膜トランジスタ(以下、PTFTという)は、特に上記構造のTFTを用いる必要はない。即ち、PTFTはNTFTほど劣化が問題とならないため公知の構造であっても良い。勿論、NTFTと同様の構造とすることも可能である。

【0025】

【発明の実施の形態】

[実施形態1]

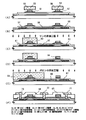

本実施形態は本願発明に用いるTFTの作製工程について図3、図4を用いて説明する。

【0026】

まず、基板100全面に下地膜101を形成し、下地膜101上に、島状の半導体層102を形成する。半導体層102を覆って基板100全面に、ゲート絶縁膜となる絶縁膜103を形成する。(図3(A))

【0027】

基板100には、ガラス基板、石英基板、結晶性ガラス基板、金属基板、ステンレス基板、またはポリエチレンテレフタレート(PET)等の樹脂基板を用いることができる。

【0028】

下地膜101は、半導体層102に基板100からナトリウムイオンなどの可動イオンが拡散するのを防いだり、基板100上に形成される半導体層の密着性を高めるための膜である。下地膜101には、酸化シリコン膜や、窒化シリコン膜、窒化酸化シリコン膜等の無機絶縁膜の単層又は多層膜が使用できる。

【0029】

例えば、下地膜はCVD法やスパッタ法などで成膜した膜だけでなく、石英基板のような耐熱性基板を用いた場合には、非晶質シリコン膜を成膜し熱酸化して、酸化シリコン膜を形成してもよい。

【0030】

半導体層102の材料はTFTに求められる特性に合わせて選択すればよい。非晶質シリコン膜、非晶質シリコンゲルマニウム膜、非晶質ゲルマニウム膜、又はこれら非晶質半導体膜をレーザ照射や加熱処理によって結晶化させた結晶質シリコン、結晶質ゲルマニウムや結晶質シリコンゲルマニウムを用いることができる。結晶化手段は公知の技術を用いれば良い。半導体層102の厚さは10〜150nm(代表的には20〜50nm)とする。

【0031】

絶縁膜103はゲート絶縁膜を構成する膜である。プラズマCVD法、スパッタ法で成膜される酸化シリコン、窒化シリコン、窒化酸化シリコンの無機絶縁膜の単層膜、多層膜が用いられる。例えば、積層膜とする場合には、窒化酸化シリコン膜と酸化シリコンの2層膜や、窒化シリコン膜を酸化シリコンで挟んだ積層膜などが用いられる。

【0032】

絶縁膜103上には、ゲート電極(ゲート配線)を構成する第1の導電膜104、第2の導電膜105を形成する。(図3(B))

【0033】

第1の導電膜104はテーパー部を有する第1のゲート電極(第1のゲート配線)を構成する。このため、テーパーエッチングが容易にできる材料でなる薄膜が望まれる。例えば、クロム(Cr)膜、タンタル(Ta)膜、タンタルを主成分(組成比が50%以上)とする薄膜、またはリンを含有するn型のシリコン(Si)膜などが代表的に用いられる。

【0034】

また、第1の導電膜104の膜厚は本願発明において第2の不純物領域(ゲート電極と重なった不純物領域)の長さ(チャネル長方向の長さ)を決定する上でも重要なパラメータである。本願発明では50〜500nm(好ましくは150〜300nm、さらに好ましくは200〜250nm)の範囲で選択する。

【0035】

また、第2の導電膜105は第2のゲート電極(第2のゲート配線)を構成する薄膜であり、アルミニウム(Al)膜、銅(Cu)膜またはアルミニウム又は銅を主成分(組成比が50%以上)とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜、リンを含有するn型のシリコン膜、タングステン−モリブデン(W−Mo)膜、またはタンタル−モリブデン(Ta−Mo)膜などの薄膜で形成することができる。さらに、前記薄膜を単層膜として用いるだけでなく、あらゆる組み合わせで積層して用いても構わない。

【0036】

ただし、第1の導電膜と第2の導電膜は互いのパターニングにおいて、エッチング選択比が取れる材料を選択する必要がある。

【0037】

例えば、第1の導電膜104/第2の導電膜105としては、n型Si/Ta、n型Si/W−Mo合金、Ta/Al、Ti/Al等の組み合わせを選択することができる。また、材料の選択する他の指標として、第2の導電膜105はできるだけ抵抗率の低い、少なくとも第1の導電膜104よりもシート抵抗が低い材料とすることが望まれる。これは、ゲート配線と上層配線との接続を第2のゲート配線でとるためである。

【0038】

次に、第2の導電膜105上にレジストマスク106を形成する。マスク106を用いて第2の導電膜105をエッチングして第2のゲート電極107を形成する。エッチングには等方性のウェットエッチングを用いればよい。(図3(C))

【0039】

次に、同じレジストマスク106を用いて、第1の導電膜104に対して異方性エッチングを行い、第1のゲート電極(第1のゲート配線)108を形成する。なお、このエッチング用に新しいレジストマスクを形成することもできる。

【0040】

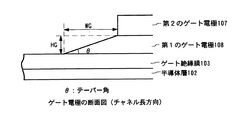

このエッチングにより、図5に示すように、第1のゲート電極108の側面がゲート絶縁膜103となすテーパー角(θ)は3度以上40度以下とされる。このテーパー角は好ましくは5度以上35度以下、より好ましくは7度以上20度以下とする。テーパー角が小さいほどゲート電極108のテーパー部において膜厚の変化が小さくなり、これに対応して、後にテーパー部と重なる半導体層において不純物濃度の変化が緩やかになる。

【0041】

また、テーパー角が40度を超えてしまうと本願発明のNTFTの最も大きな特徴である、第2の不純物領域(不純物濃度が暫時変化する領域)の長さが極端に短くなってしまうため、40度以下とすることが好ましい。

【0042】

テーパー角はテーパー部の幅WGと、厚さ(第1のゲート電極108の膜厚)HGを用いて、tanθ=HG/WGと定義できる。

【0043】

次に、レジストマスク106を除去し、第2のゲート電極107、第1のゲート電極108をマスクにして半導体層102にn型又はp型の不純物を添加する。添加方法としては、イオン注入法(質量分離したもの)、イオンドーピング法(質量分離しないもの)を用いることができる。

【0044】

n型の不純物はドナーとなる不純物であり、シリコン、ゲルマニウムに対しては15族に属する元素であり、典型的にはリン(P)、砒素(As)である。p型の不純物はアクセプターとなる不純物であり、シリコン、ゲルマニウムに対しては13族に属する元素であり、典型的には、ボロン(B)、ガリウム(Ga)である。

【0045】

ここでは、リンをイオンドーピング法にて添加し、n-型の不純物領域109、110を形成する。この場合、ゲート絶縁膜103及び第1のゲート電極108のテーパー部を通してリンを添加するため、イオンドーピング工程の加速電圧は80〜160keVとかなり高めに設定する必要がある。なお、後述するが、加速電圧によってテーパー部の真下に入るリンの濃度や分布が変化するため、注意が必要である。

【0046】

この添加工程において、後述するn-型の第2の不純物領域、及びn-型の第3の不純物領域におけるリンの濃度分布が決定される。(図4(A))

【0047】

具体的には、n-型の不純物領域109、110には第1のゲート電極108のテーパー部を通して(通過させて)リンが添加されるため、その濃度勾配は第1のゲート電極108の、テーパー部分の膜厚の変化を反映することになる。すなわち、n-型の不純物領域109、110へ添加されるリンの濃度は、テーパー部の真下においてチャネル形成領域から遠ざかるにつれて徐々に増加することになる。

【0048】

これはテーパー部分の膜厚の差によってリンの深さ方向の添加濃度が変化するためである。即ち、リンの深さ方向の濃度分布において任意の濃度で添加された深さ(例えば深さ方向に平均化した濃度)に注目した時、その深さは半導体層中の断面方向においてゲート電極のテーパー部分の傾斜に沿った形で変化する。

【0049】

図4(A)ではリンの濃度分布を波線で示しているが、これは半導体層内において波線よりも下にリンが添加されていないという意味ではなく、上述のような断面方向のリン濃度の変化が、第1のゲート電極108が有するテーパー部の傾斜に沿って形成されていることを模式的に示している。

【0050】

なお、この時のリンの添加工程は基板に対して垂直に行う必要はなく、斜めにリンを含むイオン種を添加しても良い。このような添加方法は、ゲート電極の内側深くにリンを添加する場合に効果的である。

【0051】

次にゲート電極107、108を覆ってレジストマスク111を形成する。このマスク111によって、第3の不純物領域の長さが決定される。レジストマスク111を介して、再びイオンドーピング法によりn型の不純物であるリンを半導体層102に添加する。この場合、第1のゲート電極108のテーパー部を通して添加する必要がないため、加速電圧は80〜100keVくらいで良い。(図4(B))

【0052】

このドーピング工程により、レジストマスク111で覆われていないn-型不純物領域109、110に選択的にリンが添加されて、n+型の第1の不純物領域112、113が形成される。又、第2のゲート電極107の真下にあたる領域114は図4(A)、(B)の添加工程でリンが添加されないため、チャネル形成領域となる。

【0053】

また、図4(B)の工程でリンの添加が行われなかった前記n- 型の不純物領域109、110は、第1のゲート電極108と重なっている領域115、116がn- 型の第2の不純物領域となり、第1のゲート電極108と重なっていない領域がn- 型の第3の不純物領域117、118となる。

【0054】

なお、図4(B)の添加工程に先立ってゲート配線をマスクにして、絶縁膜103をエッチングして、半導体層102表面を露出させても良い。その場合、絶縁膜をも通す必要がないため、加速電圧を10keV程度にまで低く設定することができる。即ち、装置負担を軽減できる。また、半導体層に直接的に添加できることからスループットの向上も図れる。

【0055】

この時、図6に示すように、第2の不純物領域115、116は4つのタイプに分類できる。これらを区別するため、図6では符号にA、B、C、Dの指標を付けた。なお、第2の不純物領域115、116はゲート電極を中心に左右対称に設けられるので、図6では第2の不純物領域115に注目して説明する。

【0056】

図6(A)に示すように、第2の不純物領域115Aにおけるリンの濃度分布は、第1のゲート電極108のテーパー部における膜厚の変化に対応し、テーパー部の傾斜に沿ってピーク濃度の深さが変化する。また、図6(A)の場合、チャネル形成領域114Aにはリンは全く添加されず、第3の不純物領域117Aには膜中全体にほぼ均一に添加される。

【0057】

またこの時、第2の不純物領域115A内におけるリンの濃度分布は、図4(A)の説明に示したように、第1のゲート電極108のテーパー形状に沿った形で断面方向の濃度分布が形成される。即ち、半導体層に添加されたリンを深さ方向について平均化して考えた場合、リン濃度はチャネル形成領域114Aから第3の不純物領域117Aに向かうにつれて徐々に高くなる。

【0058】

これは第1のゲート電極108のテーパー部を通してリンを添加することにより第2の不純物領域115A内において断面方向に濃度勾配ができたためである。この場合、チャネル長LAは第2のゲート電極107におけるチャネル長方向の幅に相当する。

【0059】

また、図6(B)は図4(A)のリン添加工程で、図6(A)の場合よりも加速電圧を大きくした場合の例である。この場合、図6(A)のように第2の不純物領域とチャネル形成領域との接合部(以下、チャネル接合部という)でリン濃度がほぼゼロ(またはチャネル形成領域内のリン濃度と同濃度)になるのではなく、チャネル接合部においてもある程度の濃度でリンが添加された状態になる。

【0060】

この場合、チャネル長LBは第2のゲート電極107のチャネル長方向における幅に相当する。また、図6(A)と同じ加速電圧であっても、テーバー角θが図6(A)よりも小さい時(テーパー部の膜厚が薄い時)、図6(B)のようなリンの濃度分布を持つ第2の不純物領域を得ることができる。

【0061】

更に加速電圧を大きくすることにより、図6(C)に示すように、第2の不純物領域115Cは半導体層の全体に渡ってほぼ均一にリンが添加される。この場合、チャネル長LCは第2のゲート電極107のチャネル長方向における幅に相当する。

【0062】

また、図6(D)は図4(A)のリン添加工程で、図6(A)の場合よりも加速電圧を小さくした場合の例である。この場合、図6(D)に示すように、第1のゲート電極108のテーパー部が一部においてマスクとして機能するため、テーパー部の膜厚が薄くなっている部分に選択的に添加される。

【0063】

即ち、チャネル接合部よりも外側(第3の不純物領域に近い側)からリンの添加された領域が形成され始める。このため、チャネル長は第2のゲート電極107のチャネル長方向における幅と一致しなくなり、その幅よりも長くなる。

【0064】

また、図6(A)と同じ加速電圧であっても、テーバー角θが図6(A)よりも大きい時(テーパー部の膜厚が厚い時)、図6(D)のようなリンの濃度分布を持つ第2の不純物領域を得ることができる。

【0065】

ここで、第1の不純物領域112、113の長さ(チャネル長方向の長さ)は2〜20μm(代表的には3〜10μm)である。また、半導体層中のリン濃度は1×1019〜1×1021atoms/cm3 (代表的には1×1020〜5×1020atoms/cm3 )である。この第1の不純物領域112、113はソース配線又はドレイン配線とTFTとを電気的に接続させるための低抵抗領域であり、ソース領域またはドレイン領域となる。

【0066】

また、第2の不純物領域115、116の長さは0.1〜3.5μm(代表的には0.1〜0.5μm、好ましくは0.1〜0.3μm)であり、リンの濃度は1×1015〜1×1017atoms/cm3 (代表的には5×1015〜5×1016atoms/cm3 、好ましくは1×1016〜2×1016atoms/cm3 )である。

【0067】

また、第3の不純物領域117、118の長さは0.5〜3.5μm(代表的には1.5〜2.5μm)であり、リンの濃度は1×1016〜1×1019atoms/cm3 (代表的には1×1017〜5×1018atoms/cm3、好ましくは5×1017〜1×1018atoms/cm3 )である。

【0068】

また、チャネル形成領域114は真性半導体層、又はボロンの濃度が1×1016〜5×1018atoms/cm3で添加された領域である。ボロンはしきい値電圧の制御用やパンチスルー防止用の不純物であり、同様の効果を生むものであれば他の元素で代用することもできる。

【0069】

なお、図4(B)では第1の不純物領域112、113と第2の不純物領域115、116の間に、ゲート電極と重ならない低濃度不純物領域(第3の不純物領域117、118)を1つ形成した例を示したが、この部分に、不純物濃度が互いに異なる不純物領域を2つ以上形成することもできる。本発明では、少なくとも第1の不純物領域112、113と第2の不純物領域115、116の間に、第1の不純物領域112、113よりも不純物(リン)濃度が低く、抵抗が高い不純物領域が少なくとも1つ存在すればよい。

【0070】

第1の不純物領域112、113を形成したら、レジストマスク111を除去する。そして、熱処理を行い、半導体層に添加されたリンを活性化する。活性化工程には、熱処理だけでなくエキシマレーザーや、赤外ランプ光による光アニールを行うこともできる。

【0071】

次に、酸化シリコン膜等でなる層間絶縁膜119を形成する。次に、ゲート絶縁膜103、層間絶縁膜119に第1の不純物領域112、113、及び第2のゲート配線107に達するコンタクトホールを形成する。そして、ドレイン配線120、ソース配線121、及び図示しないゲート配線の取り出し配線を形成する。こうして図4(C)に示すような構造のNTFTが完成する。

【0072】

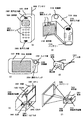

[実施形態2]

本実施形態は実施形態1において、ゲート電極(ゲート配線)の構造の変形例である。具体的には、実施形態1ではゲート電極は幅の異なる2つのゲート電極が積層された構造であったが、本実施形態は上部の第2のゲート電極を省略し、テーパー部を有する第1のゲート電極のみを形成する。

【0073】

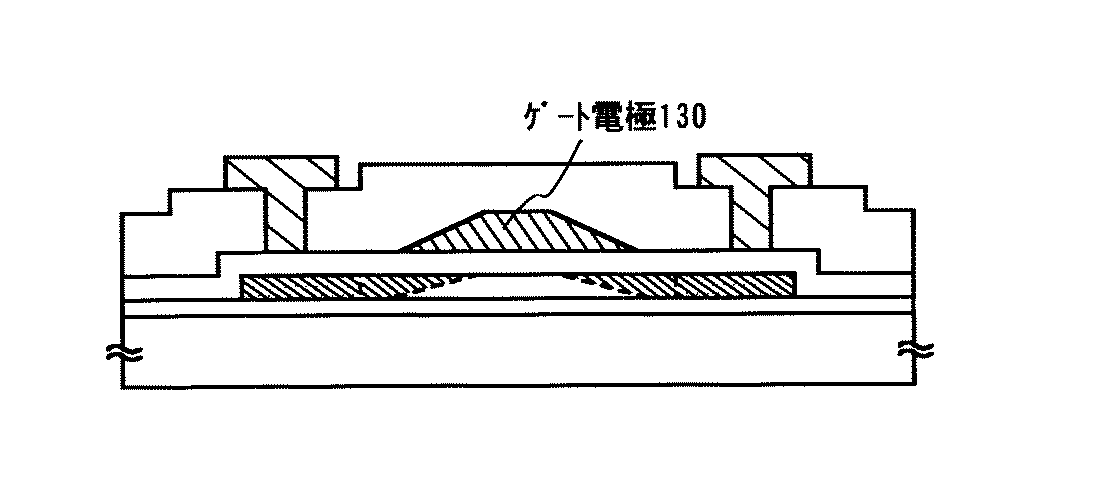

本実施形態を図7に示す。なお、構造的には実施形態1で説明した構造とほぼ同一であるため、相違点のみに符号を付して説明することとする。

【0074】

図7において図4(C)に示した構造と異なる点は、ゲート電極130が単層膜で形成されている点である。従って、そのほかの部分については実施形態1の説明がそのままあてはまる。

【0075】

ゲート電極130となる導電膜は、テーパーエッチングが容易にできる材料が望まれる。用いることのできる薄膜に関しては実施形態1で第1の導電膜104として用いたものを用いれば良い。

【0076】

また、ゲート電極130のテーパー角は3度以上40度以下とする。このテーパー角は好ましくは5度以上35度以下、より好ましくは7度以上20度以下とする。このようなテーパー形状は公知のエッチング技術でも達成できるが、高密度プラズマを用いたエッチング装置でバイアスパワー密度の制御を行うことにより所望のテーパー角を容易に得ることが可能である。

【0077】

また、本実施形態の構造のNTFTを形成するにあたって、作製工程の詳細な条件については実施形態1を参考にすれば良い。

【0078】

さらに、本実施形態でも、実施形態1と同様に第2の不純物領域は図6に示す4つのタイプに分類できる。本実施形態の場合には、チャネル長を決定するのは第2のゲート電極107に代わって、第2のゲート電極130を形成するのに用いたレジストマスクである。

【0079】

しかし、実施形態1のゲート電極は積層構造を有するため、第1のゲート電極108の厚さを薄くしても、第2のゲート電極107を厚くすることで低抵抗化が可能であるが、本実施形態のゲート電極130はテーパー部を有する単層電極でなるため、その膜厚は実施形態1で説明した第1のゲート電極108よりも厚くなってしまう。

【0080】

そのため、テーパー角の調節によりテーパー部の幅WGの長さを長めにとることが可能であり、第2の不純物領域を長くしたい場合に有利である。その代わり、テーパー角が小さいと膜厚が厚い分リンが添加されにくくなり、図6(D)のような構造になると考えられる。

【0081】

[シミュレーション結果について]

本出願人は図4(A)に示したリンの添加工程において、第1のゲート電極のテーパー部下に添加されるリンの濃度および分布をシミュレーションによって調べた結果を図12に示す。なお、ここではISE(Integrated system engineering AG)半導体デバイスシミュレータ総合パッケージを用いた。

【0082】

図12は第1のゲート電極端部におけるリンの濃度分布を示している。ここでは第1のゲート電極の膜厚を300nm、テーパー角を10.5度として計算した。また、加速電圧は110keVとし、プラズマドーピング法(イオンドーピング法)により1×1015ions/cm2のドーズ量でリンを添加した場合について計算した。なお、ゲート絶縁膜の膜厚は115nm、半導体層の膜厚は50nm、下地膜(酸化シリコン膜)の膜厚は300nmとした。

【0083】

図12を見ると明らかなように、半導体層(Si Layerと表記)のうち、第1のゲート電極のテーパー部直下にあたる領域では、リンの濃度がチャネル長方向に変化していることが判る。即ち、チャネル形成領域から遠ざかるにつれて(第1の不純物領域に近づくにつれて)、リンの濃度が高くなっていく勾配の様子が顕著に現れている。

【0084】

ここでは加速電圧を110keVとしているが、加速電圧を高くすればリンの濃度はさらに内側(第1のゲート電極の内側)で高くなると予想できる。また、イオンインプランテーション法を用いても濃度分布は変化するであろう。しかしながら、本願発明の主旨はこのようなリンの濃度勾配をLDD領域(ゲート電極に重なる部分を含む)内に形成し、電界緩和効果を高めるというものであるから、最適な濃度分布は実施者が適宜決定すればよい。

【0085】

【実施例】

[実施例1]

本実施例では発明の実施の形態において説明したNTFTを用いてアクティブマトリクス型液晶表示装置(AM−LCD)を形成する例を示す。

【0086】

図8は本実施例に示すAM−LCDの概略構成図である。AM−LCDは、アクティブマトリクス基板200と対向基板206との間に液晶が挟まれた構造を有している。アクティブマトリクス基板200は、基板上に画素部201、画素部201を駆動するためのゲートドライバ回路202及びソースドライバ回路203が形成されている。各ドライバ回路はそれぞれソース配線、ドレイン配線によって画素部201に接続されている。

【0087】

更に、基板上にはソースドライバ回路203に伝達されるビデオ信号を処理するための信号処理回路204が形成されている。信号処理回路としては、D/Aコンバータ回路、信号分割回路、γ補正回路などが挙げられる。そして、それらのビデオ信号を入力するための外部端子が形成され、この外部端子にFPC205が接続されている。

【0088】

対向基板206は、ガラス基板全面にITO膜等の透明導電膜が形成されている。透明導電膜は画素部201の画素電極に対する対向電極であり、画素電極、対向電極間に形成された電界によって液晶材料が駆動される。更に、対向基板206には必要であれば配向膜、カラーフィルタまたはブラックマスクなどが形成されている。

【0089】

以上のような構成でなるAM−LCDは、回路によって最低限必要な動作電圧(電源電圧)が異なる。例えば、画素部では液晶に印加する電圧と画素TFTを駆動するための電圧とを考慮すると、14〜20Vもの動作電圧となる。そのため、そのような高電圧が印加されても耐えうる程度のTFT(以下、高耐圧型TFTという)を用いなければならない。

【0090】

また、ソースドライバ回路やゲートドライバ回路に用いられるシフトレジスト回路などは、5〜10V程度の動作電圧で十分である。動作電圧が低いほど外部信号との互換性もあり、さらに消費電力を抑えられるという利点がある。ところが、前述の高耐圧型TFTは耐圧特性が良い代わりに動作速度が犠牲になるため、シフトレジスタ回路のように高速動作が求められる回路には不適当である。

【0091】

このように、基板上に形成される回路は、目的に応じて耐圧特性を重視したTFTを求める回路と動作速度を重視したTFTを求める回路とに分かれる。従って、本願発明のNTFTを有効に活用するためには、回路に応じた構造を持たせることが重要である。

【0092】

ここで具体的に本実施例の構成を図1に示す。図1(A)に示したのは、AM−LCDのブロック図を上面から見た図である。11は画素部であり、表示部として機能する。また、12aはシフトレジスタ回路、12bはレベルシフタ回路、12cはバッファ回路である。これらでなる回路が全体としてゲートドライバ回路12を形成している。

【0093】

なお、図1(A)に示したAM−LCDではゲートドライバ回路12を、画素部を挟んで設け、それぞれで同一ゲート配線を共有している、即ち、どちらか片方のゲートドライバに不良が発生してもゲート配線に電圧を印加することができるという冗長性を持たせている。

【0094】

また、13aはシフトレジスタ回路、13bはレベルシフタ回路、13cはバッファ回路、13dはサンプリング回路であり、これらでなる回路が全体としてソースドライバ回路13を形成している。画素部11を挟んでソースドライバ回路13と反対側にはプリチャージ回路14が設けられている。

【0095】

このような構成でなるAM−LCDにおいて、シフトレジスタ回路12a、13aは高速動作を求める回路であり、動作電圧が3.3〜10V(代表的には3.3〜5V)と低く、高耐圧特性は特に要求されない。従って、本願発明のNTFTを用いる場合には、抵抗成分となる第2の不純物領域及び第3の不純物領域は必要最小限に狭くして、動作速度が低下しないような構造を採用することが望ましい。

【0096】

図1(B)に示したのは主としてシフトレジスタ回路やその他の信号処理回路のように高速動作を求められる回路に用いるべきCMOS回路の概略図である。なお、図1(B)において、15は第1のゲート電極(A)、16aは第2のゲート電極(A)であり、NTFTのみ図4(C)に示した構造を有している。また、17は活性層、18、19はソース配線、20はドレイン配線である。

【0097】

また、図1(B)のCMOS回路の断面構造を図2(A)に示す。図2(A)の構造の場合、第2の不純物領域(A)21の長さ(WG1)は0.1〜3.0μm(好ましくは1.0〜2.0μm)とすれば良い。この長さ(WG1)は第1のゲート電極(A)15のテーパー角を調節することによって制御することができる。なぜならば、第1のゲート電極(A)15のテーパー部を通して不純物を添加することによって濃度勾配を有する第2の不純物領域(A)21が形成されるからである。この時のテーパー角は25度以上40度以下とすれば良い。ただし、第1のゲート電極(A)15の膜厚によって適切な数値は変化する。

【0098】

また、第3の不純物領域(A)22aは極力小さくする方がよく、場合によっては設けなくても構わない。なぜならば、シフトレジスタ回路や信号処理回路などはオフ電流をさほど気にする必要がないからである。設ける場合には0.1〜1.5μm(典型的には0.3〜1.0μm)の範囲で設けることにする。

【0099】

ここで図1(B)の回路についてまとめると、電源電圧が(10±2)Vの時は、チャネル長は3.5±1.0μm、第2の不純物領域(A)21の長さは2.0±1.0μm、第3の不純物領域(A)22aは1.0±0.5μmとすれば良い。また、電源電圧が(5±2)Vの時は、チャネル長は3.0±1.0μm、第2の不純物領域(A)21の長さは2.0±1.0μm、第3の不純物領域(A)22aは0.5±0.2μmとすれば良い。

【0100】

次に、図1(C)に示すCMOS回路は、主としてレベルシフタ回路12b、13b、バッファ回路12c、13c、サンプリング回路13d、プリチャージ回路14に適している。これらの回路は大電流を流す必要があるため、動作電圧は14〜16Vと高い。特にゲートドライバ側では場合によっては19Vといった動作電圧を必要とする場合もある。従って、非常に良い耐圧特性(高耐圧特性)を有するTFTが必要となる。

【0101】

この時、図1(C)に示したCMOS回路の断面構造を図2(B)に示す。この場合、第2の不純物領域(B)24の長さ(WG2)は1.5〜4.0μm(好ましくは2.0〜3.0μm)とすれば良い。この時も、第1のゲート電極(B)23のテーパー角を制御することによって、所望の長さにできる。例えば、3度以上30度以下とすれば良い。ただし、第1のゲート電極(B)23の膜厚によって適切な数値は変化する。

【0102】

この場合も、第3の不純物領域(B)22bは極力小さくすることが望ましく、特に設けなくても構わない。その理由はシフトレジスタ回路等と同様で、オフ電流をさほど気にする必要がないからである。なお、設ける場合には0.1〜5.5μm(典型的には1.0〜3.0μm)の範囲で設けることにする。ただし、ゲートドライバー側のバッファ回路は場合によって20Vといった高電圧がかかることもありうるため、その場合には第3の不純物領域(B)22bを長めに形成してオフ電流を低減することが必要である。

【0103】

ここで図1(C)の回路についてまとめると、電源電圧が(16±2)Vの時は、チャネル長は5.0±1.5μm、第2の不純物領域(B)24の長さは2.5±1.0μm、第3の不純物領域(B)22bは2.0±1.0μmとすれば良い。また、電源電圧が(20±2)Vの時は、チャネル長は5.0±2.0μm、第2の不純物領域(B)24の長さは3.0±1.0μm、第3の不純物領域(B)22bは4.0±1.5μmとすれば良い。

【0104】

特にサンプリング回路に関しては、チャネル長は4.0±2.0μm、第2の不純物領域(B)の長さは1.5±1.0μm、第3の不純物領域(B)は2.0±1.5μmとすれば良い。

【0105】

次に、図1(D)は画素部11の概略図を示し、図2(C)にその任意の画素部における断面構造を示している。図1(D)において、25は第1のゲート電極(C)、26は第2のゲート電極(C)、27は活性層、28はソース配線、29はドレイン電極、30は画素電極である。

【0106】

また、図2(C)に示すように、ドレイン電極29に接続された画素電極30は、透明導電膜31との間に絶縁膜32を介して保持容量を形成している。この保持容量は画素領域(ソース配線およびゲート配線で囲まれた領域)の大部分を占めて形成される。また、透明導電膜31は樹脂材料でなる絶縁膜33によって完全に画素電極30と絶縁分離されている。

【0107】

ところで画素TFT(画素部におけるスイッチング素子)は液晶に印加する電圧分も加味されるため、14〜16Vの動作電圧を必要とする。また、液晶及び保持容量に蓄積された電荷を1フレーム期間保持しなければならないため、極力オフ電流は小さくなければならない。

【0108】

そういった理由から、本実施例では本願発明のNTFTを用いたダブルゲート構造とし、第2の不純物領域(C)34の長さ(WG3)を0.5〜3.0μm(好ましくは1.5〜2.5μm)とする。また、WG2(図2(B)参照)とWG3とは同一の長さであっても良いし、異なる長さとしても良い。

【0109】

この時も、第1のゲート電極(C)25のテーパー角を制御することによって、所望の長さにできる。例えば、3度以上30度以下とすれば良い。ただし、第1のゲート電極(C)25の膜厚によって適切な数値は変化する。

【0110】

さらに、図2(C)の画素部に特徴的なのは、第3の不純物領域(C)35を図2(A)や図2(B)に示したCMOS回路よりも長くする点である。これは画素部にとってオフ電流を低減するという課題が最重要課題だからである。

【0111】

図4(B)で説明したように、第3の不純物領域(C)35の長さはレジストマスクの配置によって制御される。この場合、第3の不純物領域(C)35の長さ(WG3)を0.5〜4.0μm(代表的には1.5〜3.0μm)とすれば良い。

【0112】

ここで図1(D)の回路についてまとめると、電源電圧が(16±2)Vの時は、チャネル長は4.0±2.0μm、第2の不純物領域(C)34の長さは1.5±1.0μm、第3の不純物領域(C)35は2.0±1.5μmとすれば良い。

【0113】

以上のように、AM−LCDを例にとっても同一基板上には様々な回路が設けられ、回路によって必要とする動作電圧(電源電圧)が異なることがある。その結果を表1に示す。

【0114】

【表1】

【0115】

この様に、回路の目的に応じて要求する耐圧特性が異なってくる場合もあり、そういった場合には本実施例のようなTFTの使い分けが必要となる。本願発明のNTFTはこのような使い分けをしてこそ、その真価を発揮できると言える。

【0116】

[実施例2]

本実施例では実施例1に示したCMOS回路や画素部を構成するNTFTの変形例について説明する。

【0117】

図9(A)はシフトレジスタ回路等、高速動作を必要とする回路に適した構造のCMOS回路である。本実施例の特徴は、ソース配線36側には第2の不純物領域37のみを設け、ドレイン配線38側には第2の不純物領域39および第3の不純物領域40を設けている点にある。

【0118】

CMOS回路は通常ソース領域とドレイン領域が固定されており、低濃度不純物領域(LDD領域)を必要とするのはドレイン領域側のみである。逆にソース領域側に設けられたLDD領域(またはオフセット領域)は単に抵抗成分として働き、動作速度を低下させる要因ともなる。

【0119】

そのため本実施例のように、ドレイン領域側のみに第3の不純物領域を設ける構成が好ましいのである。第3の不純物領域はレジストマスクを用いて形成されるため、ドレイン領域側のみに設けることは容易である。

【0120】

また、図9(B)に示したのは、画素部を形成する画素TFT(NTFT)に対して本実施例の構成を適用した場合の例である。図9(B)において、41〜44が第2の不純物領域、45、46が第3の不純物領域である。なお、図9(B)の構造は保持容量を二層の透明電極(代表的にはITO電極)で形成している点に特徴があるが、この構造の作製方法等については本出願人による特願平10−254097号出願を参考にすれば良い。

【0121】

画素TFTの場合、動作モードがCMOS回路と異なり、ソース領域とドレイン領域とが入れ替わる動作をする。第3の不純物領域45、46は、画素TFTと引き出し端子(ソース配線またはドレイン配線)との接続する部分に設けておく必要がある。

【0122】

しかし、図9(B)に示したようなダブルゲート構造の場合、二つのTFTをつなぐ領域に設けられた第2の不純物領域42、43は実質的に抵抗成分として機能してしまう。まして、第3の不純物領域を設けてしまうとさらに抵抗の高い領域を形成してしまうことにもなる。従って、図9(B)の構造では直列に並んだ二つのTFTの間には第3の不純物領域(ゲート電極と重ならない低濃度不純物領域)を設けない構造を採用している。

【0123】

液晶表示装置において、高精細な表示画面を要求されるようになると画素への書き込み時間(液晶に必要な電圧を印加する時間)は極端に短いものとなってくる。そうなると画素TFTにもある程度の動作速度を求められるので、抵抗成分をできるだけ減らす構造が必要となる。そういった意味で、本実施例の構造は非常に好ましい形態であると言える。

【0124】

また、図9(A)ではソース配線36側に第2の不純物領域37のみを設け、ドレイン配線38側に第2の不純物領域39と第3の不純物領域40とを設ける構造を示したが、図9(C)に示す構造はこれをさらに顕著にし、ソース配線36側に第2の不純物領域も第3の不純物領域も設けない構造とする。

【0125】

即ち、ソース配線36と接続する第1の不純物領域(ソース領域)47がチャネル形成領域と直接的に接する構造となる。こうすることでソース側に不要な抵抗成分が形成されることを防ぎ、高速動作の可能なCMOS回路を実現することができる。

【0126】

なお、本実施例の構成は実施例1に示した全ての回路に対して有効である。即ち、NTFTにおいてソース領域側には第3の不純物領域を設けず、ドレイン領域側のみに第3の不純物領域を設けることで、高い信頼性を確保したまま、動作速度を向上させることが可能である。勿論、図6に示した全ての場合についても本実施例と組み合わせることができる。

【0127】

[実施例3]

本実施例では、本願発明を用いたCMOS回路の作製工程について説明する。説明には図10を用いる。

【0128】

まず、前述の「実施形態1」の工程に従って図3(A)、(B)、(C)、(D)までを行う。この状態を図10(A)に示す。ただし、図10(A)では同一半導体層上に二つのTFT(図面に向かって左がNTFT、右がPTFT)を形成する例を示すことにする。

【0129】

図10(A)において、51、52は第1のゲート電極、53、54は第2のゲート電極、55、56は第1のゲート電極および第2のゲート電極を形成する際に用いたレジストマスクである。このレジストマスク55、56は第1のゲート電極51、52にテーパーを形成する際にも用いられる。

【0130】

なお、図1に示したように、同一基板上で回路に応じて第2の不純物領域の長さを異ならせるためには、回路の動作する動作電圧に応じて第1のゲート電極のテーパー角を調節しなければならない。その場合、第1のゲート電極を形成する際に、動作電圧の異なる回路はレジストマスクを用いて別々にテーパー角を形成する必要がある。

【0131】

次に第2のゲート電極53、54をマスクにしてリンの添加工程を行い、n-型の不純物領域57〜59を形成する。添加条件は実施形態1を参考にすれば良い。この時、第1のゲート電極51、52のテーパー部ではリンが第1のゲート電極を突き抜けて添加されるため、図6を用いて説明したような濃度勾配を示す不純物領域が形成される。(図10(B))

【0132】

次に、レジストマスク60を形成し、その後、再度リンの添加工程を行ってn+型の不純物領域61〜63を形成する。このレジストマスクによって図6で説明した第3の不純物領域が画定する。この時、動作電圧の異なる回路に応じて第3の不純物領域の長さを異ならせるためには、レジストマスクの幅を変更すれば良いだけである。(図10(C))

【0133】

図10(C)の工程が終了した時点でCMOS回路のNTFTが完成する。次に、PTFTの第2のゲート電極54をマスクにして自己整合的に第1のゲート電極52をエッチングしてテーパー部を除去する。こうして第2のゲート電極と同一形状の第1のゲート電極64が形成される。なお、この工程は省略しても構わない。(図10(D))

【0134】

次に、NTFTを覆ってレジストマスク65を形成し、実施形態1の条件でボロンの添加工程を行う。この工程では前述したn-型の不純物領域およびn+型の不純物領域がどちらも反転してp++型の不純物領域66、67が形成される。(図10(E))

【0135】

このあと、レジストマスク65を除去した後、窒化シリコン膜68で第1のゲート電極および第2のゲート電極を覆い、添加したリンおよびボロンの活性化を行う。この工程はファーネスアニール、レーザーアニールまたはランプアニールを自由に組み合わせて行えば良い。また、この窒化シリコン膜68には第1及び第2のゲート電極を熱や酸化反応から保護する目的もある。

【0136】

次に、窒化シリコン膜68上に層間絶縁膜69を形成し、コンタクトホールを形成した後、ソース配線70、71およびドレイン配線72を形成する。こうして図10(F)に示すような構造のCMOS回路が得られる。

【0137】

なお、本実施例では本願発明のNTFTを用いたCMOS回路の一例を示しただけであり、本実施例のCMOS回路の構造に限定される必要はない。また、図1に示したような構成を実現する場合、動作電圧の異なる回路ごとに別々に第1のゲート電極のテーパー角を異ならせる必要がある。

【0138】

また、本実施例の構成は実施例1、2のいずれの構成とも自由に組み合わせる事が可能である。

【0139】

[実施例4]

本実施例では、本願発明のNTFTにおいて第1のゲート電極の側面をテーパー形状にするためのエッチング条件について説明する。本実施例では第1のゲート電極を形成する導電膜を、純度が6N(99.9999%)以上のタングステンターゲットを用いたスパッタ法により形成する。スパッタガスとしては希ガスを用いればよいが、窒素(N2)を添加することにより窒化タングステン膜を形成することもできる。

【0140】

本実施例では30nmの窒化タングステン膜の上に370nmのタングステン膜を積層した構造とする。但し、窒化タングステン膜は設けなくても良いし、窒化タングステン膜の下にシリコン膜を形成しても良い。また、タングステン膜の上に窒化タングステン膜を設けた積層膜としても良い。

【0141】

このようにして得た積層膜は酸素の含有量を30ppm以下とすることができる。そのため、電気抵抗率は20μΩcm以下、代表的には、6μ〜15μΩcmとすることができ、膜の応力は−5×109〜5×109dyn/cm2とすることができる。

【0142】

次に、上記積層膜上にレジストパターンを形成し、積層膜のエッチングを行って第1のゲート電極を形成する。このとき、本実施例では、上記積層膜のパターニングに高密度プラズマを使用するICP(Inductively Coupled Plasma)エッチング装置を使用する。

【0143】

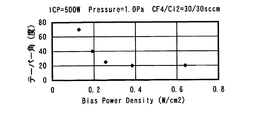

本実施例は、所望のテーパー角を得るためにICPエッチング装置のバイアスパワー密度を調節する点に特徴がある。図13は、テーパー角のバイアスパワー依存性を示した図である。図13に示したように、バイアスパワー密度に応じてテーパー角を制御することができる。

【0144】

本実施例ではテーパー角を20度とするために、バイアスパワー密度を0.4W/cm2とする。勿論、0.4W/cm2以上とすればテーパー角を20度とすることができる。なお、ICPパワーは500W、ガス圧は1.0Pa、ガス流量はCF4/Cl2=30/30sccmとする。

【0145】

また、エッチングガス(CF4とCl2との混合ガス)のCF4の流量比を調節してもテーパー角を制御することができる。図14はテーパー角とCF4の流量比依存性を示した図である。CF4の流量比を大きくすればタングステン膜とレジストとの選択比が大きくなり、ほぼCF4の流量比に比例して第1のゲート電極のテーパー角が増加する。

【0146】

このようにタングステン膜とレジストとの選択比によってテーパー角は変化する。ここでタングステン膜とレジストの選択比とテーパー角との関係を図15に示す。図15からも明らかなように、タングステン膜とレジストの選択比とテーパー角との間には比例関係が見られる。

【0147】

以上のようにICPエッチング装置を用いてバイアスパワー密度や反応ガス流量比を調節することで、容易に第1のゲート電極の側面におけるテーパー角を制御することができる。なお、実験データはテーパー角が20〜80度の範囲しか示されていないが、条件を適切に設定すれば、20度以下(3〜20度)のテーパー角も形成しうる。

【0148】

なお、本実施例では、タングステン膜を一例として示したが、Ta、Ti、Mo、Cr、Nb、Si等の導電膜についても、ICPエッチング装置を用いると、容易にパターンの端部をテーパー形状とすることができる。

【0149】

また、本実施例ではエッチングガスとしてCF4とCl2との混合ガスを例に挙げたが、これに限定する必要はなく、C2F6またはC4F8から選ばれたフッ素を含む反応ガスとCl2、SiCl4、またはBCl3から選ばれた塩素を含むガスとの混合ガスを用いることも可能である。さらに、CF4とCl2との混合ガスに20〜60%の酸素を添加しても良い。

【0150】

本実施例のエッチング技術は、実施形態1、実施形態2または実施例1乃至実施例3のいずれの構成に組み合わせて実施しても良い。

【0151】

[実施例5]

本願発明の構成は実施例1に示した液晶表示装置だけでなく、あらゆる半導体回路に適用することが可能である。即ち、RISCプロセッサ、ASICプロセッサ等のマイクロプロセッサに適用しても良いし、D/Aコンバータ等の信号処理回路から携帯機器(携帯電話、PHS、モバイルコンピュータ)用の高周波回路に適用しても良い。

【0152】

さらに、従来のMOSFET上に層間絶縁膜を形成し、その上に本発明を用いて半導体回路を作製したような三次元構造の半導体装置を実現することも可能である。このように本発明は現在LSIが用いられている全ての半導体装置に適用することが可能である。即ち、SIMOX、Smart−Cut(SOITEC社の登録商標)、ELTRAN(キャノン株式会社の登録商標)などのSOI構造(単結晶半導体薄膜を用いたTFT構造)に本発明を適用しても良い。

【0153】

また、本実施例の半導体回路は実施例1〜4のどのような組み合わせからなる構成を用いても実現することができる。

【0154】

〔実施例6〕

本実施例では、本願発明を用いてEL(エレクトロルミネッセンス)表示装置を作製した例について説明する。

【0155】

図16(A)は本願発明を用いたEL表示装置の上面図である。図16(A)において、4010は基板、4011は画素部、4012はソース側駆動回路、4013はゲート側駆動回路であり、それぞれの駆動回路は配線4014〜4016を経てFPC(フレキシブルプリントサーキット)4017に至り、外部機器へと接続される。

【0156】

このとき、少なくとも画素部、好ましくは駆動回路及び画素部を囲むようにしてカバー材6000、第1シール材7000及び第2シール材7001が設けられている。

【0157】

また、図16(B)は本実施例のEL表示装置の断面構造であり、基板4010、下地膜4021の上に駆動回路部(但し、ここではnチャネル型TFTとpチャネル型TFTを組み合わせたCMOS回路を図示している。)4022及び画素部(但し、ここではEL素子への電流を制御するTFTのみ図示している。)4023が形成されている。

【0158】

本実施例では、駆動回路部4022には図2(A)のCMOS回路が用いられる。また、画素部4023のうち、EL素子への電流を制御するTFT(以下、電流制御用TFTという)には図9(C)のnチャネル型TFTの構造が用いられ、電流制御用TFTのゲート信号を切り替えるTFT(以下、スイッチング用TFTという)には図2(C)の構造のTFTが用いられる。

【0159】

本願発明を用いて駆動回路部4022、画素部4023が完成したら、樹脂材料でなる層間絶縁膜(平坦化膜)4024の上に画素部用TFT4023のドレインと電気的に接続する画素電極(陰極)4025を形成する。画素電極4025としては遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)を用いることができる。本実施例ではアルミニウム合金を画素電極として用いる。そして、画素電極4025を形成したら、絶縁膜4026を形成し、画素電極4025上に開口部を形成する。

【0160】

次に、EL(エレクトロルミネッセンス)層4027を形成する。EL層4027は公知のEL材料(正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

【0161】

本実施例では、シャドーマスクを用いて蒸着法によりEL層を形成する。シャドーマスクを用いて画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層及び青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルターを組み合わせた方式、白色発光層とカラーフィルターを組み合わせた方式があるがいずれの方法を用いても良い。勿論、単色発光のEL表示装置とすることもできる。

【0162】

EL層4027を形成したら、その上に透明導電膜からなる陽極4028を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物または酸化インジウムと酸化亜鉛との化合物を用いることができる。陽極4028とEL層4027の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中でEL層4027と陽極4028を連続成膜するか、EL層4027を不活性雰囲気で形成し、大気解放しないで陽極4028を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0163】

そして陽極4028は4029で示される領域において配線4016に接続される。配線4016は陽極4028に所定の電圧を与えるための配線であり、導電性材料4030を介してFPC4017に電気的に接続される。

【0164】

4029に示された領域において陽極4028と配線4016とを電気的に接続するために、層間絶縁膜4024及び絶縁膜4026にコンタクトホールを形成する必要がある。これらは層間絶縁膜4024のエッチング時(画素電極用コンタクトホールの形成時)や絶縁膜4026のエッチング時(EL層形成前の開口部の形成時)に形成しておけば良い。また、絶縁膜4026をエッチングする際に、層間絶縁膜4024まで一括でエッチングしても良い。この場合、層間絶縁膜4024と絶縁膜4026が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができる。

【0165】

このようにして形成されたEL素子の表面を覆って、パッシベーション膜4031形成される。さらに、EL素子を囲むようにして第1シール材7000が設けられ、第1シール材7000によってカバー材6000が貼り合わされる。そして、基板4010、カバー材6000及び第1シール材7000で囲まれた領域には充填材6004が形成される。

【0166】

このとき、この充填材6004は、カバー材6000を接着するための接着剤としても機能する。充填材6004としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材6004の内部に吸湿性物質(好ましくは酸化バリウム)を設けておくと、吸湿効果を保持できるので好ましい。

【0167】

また、充填材6004の中にスペーサーを含有させてもよい。このとき、スペーサーを酸化バリウムで形成すればスペーサー自体に吸湿性をもたせることが可能である。また、スペーサーを設けた場合、パッシベーション膜4031はスペーサーからの圧力を緩和するバッファとしても機能する。また、パッシベーション膜とは別のバッファとして樹脂膜を設けてもよい。

【0168】

尚、充填材の代わりに不活性ガス(窒素又は希ガス)を充填してもよい。

【0169】

また、カバー材6000としては、ガラス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。本実施例の場合、EL素子からの光の放射方向がカバー材6000の方へ向かうため透光性材料でなければならない。

【0170】

但し、EL素子からの光の放射方向がカバー材とは反対側に向かう場合には透光性材料を用いる必要はなく、金属板(代表的にはステンレス板)、セラミックス板、またはアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることができる。

【0171】

また、配線4016は第1シール材7000と基板4010との隙間を通ってFPC4017に電気的に接続される。なお、ここでは配線4016について説明したが、他の配線4014、4015も同様にして第1シール材7000の下を通ってFPC4017に電気的に接続される。

【0172】

最後に、第1シール材7000の露呈部及びFPC4017の一部を覆うように第2シール材7001を設け、外気を完全に遮断した構造とする。こうして図16(B)の断面構造を有するEL表示装置となる。

【0173】

以上のような構成でなるEL表示装置において、本願発明を用いることで、信頼性の高いEL表示装置が得られる。なお、本実施例のEL表示装置は実施例1〜実施例5のいずれの構成を組み合わせて作製しても構わない。

【0174】

〔実施例7〕

本実施例では、実施例6の構造EL表示装置において画素部のさらに詳細な断面構造を図17に、上面構造を図18(A)に、回路図を図18(B)に示す。図17、図18(A)及び図18(B)では共通の符号を用いるので互いに参照すれば良い。

【0175】

図17において、基板1701上に設けられたスイッチング用TFT1702は図2(C)の構造のNTFTを用いて形成される。本実施例ではダブルゲート構造としている。ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流値を低減することができるという利点がある。

【0176】

なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。また、図2(A)や図2(B)に示されたPTFTを用いて形成しても構わない。

【0177】

また、電流制御用TFT1703は図9(C)の構造のNTFTを用いて形成される。このとき、スイッチング用TFT1702のドレイン配線1704は配線1705によって電流制御用TFTのゲート電極1706に電気的に接続されている。

【0178】

このとき、電流制御用TFT1703が本願発明の構造であることは非常に重要な意味を持つ。電流制御用TFTはEL素子を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用TFTのドレイン側に、ゲート絶縁膜を介してゲート電極に重なるようにLDD領域を設ける本願発明の構造は極めて有効である。

【0179】

また、本実施例では電流制御用TFT1703をシングルゲート構造で図示しているが、複数のTFTを直列につなげたマルチゲート構造としても良い。さらに、複数のTFTを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

【0180】

また、図18(A)に示すように、電流制御用TFT1703のゲート電極1706となる配線は1707で示される領域で、電流制御用TFT1703のドレイン配線1708と絶縁膜を介して重なる。このとき、1707で示される領域ではコンデンサが形成される。このコンデンサ1707は電流制御用TFT1703のゲートにかかる電圧を保持するためのコンデンサとして機能する。なお、ドレイン配線1708は電流供給線(電源線)1709に接続される。

【0181】

さらに、スイッチング用TFT1702及び電流制御用TFT1703の上には第1パッシベーション膜1710が設けられ、その上に樹脂絶縁膜でなる平坦化膜1711が形成される。平坦化膜1711を用いてTFTによる段差を平坦化することは非常に重要である。後に形成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0182】

また、1712は反射性の高い導電膜でなる画素電極(EL素子の陰極)であり、電流制御用TFT1703のドレインに電気的に接続される。画素電極1712としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。

【0183】

また、絶縁膜(好ましくは樹脂)で形成されたバンク1713a、1713bにより形成された溝(画素に相当する)の中に発光層1714が形成される。なお、ここでは一画素しか図示していないが、R(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けても良い。本実施例では発光層とする有機EL材料としてはπ共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン(PPV)系、ポリビニルカルバゾール(PVK)系、ポリフルオレン系などが挙げられる。

【0184】

なお、PPV系有機EL材料としては様々な型のものがあるが、例えば「H. Shenk,H.Becker,O.Gelsen,E.Kluge,W.Kreuder,and H.Spreitzer,“Polymers for Light Emitting Diodes”,Euro Display,Proceedings,1999,p.33-37」や特開平10−92576号公報に記載されたような材料を用いれば良い。

【0185】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30〜150nm(好ましくは40〜100nm)とすれば良い。

【0186】

但し、以上の例は発光層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。

【0187】

例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0188】

本実施例では発光層1714の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層1715を設けた積層構造のEL層としている。そして、正孔注入層1715の上には透明導電膜でなる陽極1716が設けられる。本実施例の場合、発光層1714で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。

【0189】

陽極1716まで形成された時点でEL素子1717が完成する。なお、ここでいうEL素子1717は、画素電極(陰極)1712、発光層1714、正孔注入層1715及び陽極1716で形成されたコンデンサを指す。図18(A)に示すように画素電極1712は画素の面積にほぼ一致するため、画素全体がEL素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。

【0190】

ところで、本実施例では、陽極1716の上にさらに第2パッシベーション膜1718を設けている。第2パッシベーション膜1718としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部とEL素子とを遮断することであり、有機EL材料の酸化による劣化を防ぐ意味と、有機EL材料からの脱ガスを抑える意味との両方を併せ持つ。これによりEL表示装置の信頼性が高められる。

【0191】

以上のように本願発明のEL表示装置は図17のような構造の画素からなる画素部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能なEL表示装置が得られる。

【0192】

なお、本実施例の構成は、実施例1〜5のいずれの構成とも自由に組み合わせて実施することが可能である。

【0193】

〔実施例8〕

本実施例では、実施例7に示した画素部において、EL素子1717の構造を反転させた構造について説明する。説明には図19を用いる。なお、図17の構造と異なる点はEL素子の部分と電流制御用TFTだけであるので、その他の説明は省略し、同一部分には同じ符号を用いる。

【0194】

図19において、電流制御用TFT1901は実施例3の作製工程で形成されたPTFTを用いる。

【0195】

また、本実施例では、画素電極(陽極)1902として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

【0196】

そして、絶縁膜でなるバンク1903a、1903bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層1904が形成される。その上にはアルカリ金属錯体(好ましくはカリウムアセチルアセトネート)でなる電子注入層1905、アルミニウム合金でなる陰極1906が形成される。この場合、陰極1906がパッシベーション膜としても機能する。こうしてEL素子1907が形成される。

【0197】

本実施例の場合、発光層1904で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。

【0198】

なお、本実施例の構成は、実施例1〜5のいずれの構成とも自由に組み合わせて実施することが可能である。

【0199】

〔実施例9〕

本実施例では、図18(B)に示した回路図とは異なる構造の画素とした場合の例について図20(A)〜(C)に示す。なお、本実施例において、3801はスイッチング用TFT3802のソース配線、3803はスイッチング用TFT3802のゲート配線、3804は電流制御用TFT、3805はコンデンサ、3806、3808は電流供給線、3807はEL素子とする。

【0200】

図20(A)は、二つの画素間で電流供給線3806を共通とした場合の例である。即ち、二つの画素が電流供給線3806を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0201】

また、図20(B)は、電流供給線3808をゲート配線3803と平行に設けた場合の例である。なお、図20(B)では電流供給線3808とゲート配線3803とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線3808とゲート配線3803とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0202】

また、図20(C)は、図20(B)の構造と同様に電流供給線3808をゲート配線3803と平行に設け、さらに、二つの画素を電流供給線3808を中心に線対称となるように形成する点に特徴がある。また、電流供給線3808をゲート配線3803のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0203】

なお、本実施例の構成は、実施例1〜5のいずれの構成とも自由に組み合わせて実施することが可能である。

【0204】

[実施例10]

実施例7に示した図18(A)、(B)では電流制御用TFT1703のゲートにかかる電圧を保持するためにコンデンサ1704を設ける構造としているが、コンデンサ1704を省略することも可能である。実施例7の場合、電流制御用TFT1703として図9(C)のNTFTを用いているため、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している。この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、本実施例ではこの寄生容量をコンデンサ1704の代わりとして積極的に用いる点に特徴がある。

【0205】

この寄生容量のキャパシタンスは、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。

【0206】

また、実施例9に示した図20(A)〜(C)の構造においても同様に、コンデンサ3805を省略することは可能である。

【0207】

なお、本実施例の構成は、実施例1〜5のいずれの構成とも自由に組み合わせて実施することが可能である。

【0208】

〔実施例11〕

本願発明の電気光学装置、具体的には本願発明の液晶表示装置にはネマチック液晶以外にも様々な液晶を用いることが可能である。例えば、1998, SID, "Characteristics and Driving Scheme of Polymer-Stabilized Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gray-Scale Capability" by H. Furue et al.や、1997, SID DIGEST, 841, "A Full-Color Thresholdless Antiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time" by T. Yoshida et al.や、1996, J. Mater. Chem. 6(4), 671-673, "Thresholdless antiferroelectricity in liquid crystals and its application to displays" by S. Inui et al.や、米国特許第5594569 号に開示された液晶を用いることが可能である。

【0209】

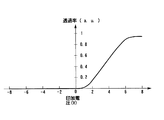

また、等方相−コレステリック相−カイラルスメクティックC相転移系列を示す強誘電性液晶(FLC)を用い、DC電圧を印加しながらコレステリック相−カイラルスメクティックC相転移をさせ、かつコーンエッジをほぼラビング方向に一致させた単安定FLCの電気光学特性を図21に示す。

【0210】

図21に示すような強誘電性液晶による表示モードは「Half−V字スイッチングモード」と呼ばれている。図21に示すグラフの縦軸は透過率(任意単位)、横軸は印加電圧である。「Half−V字スイッチングモード」については、寺田らの”Half−V字スイッチングモードFLCD”、第46回応用物理学関係連合講演会講演予稿集、1999年3月、第1316頁、および吉原らの”強誘電性液晶による時分割フルカラーLCD”、液晶第3巻第3号第190頁に詳しい。

【0211】

図21に示されるように、このような強誘電性混合液晶を用いると、低電圧駆動かつ階調表示が可能となることがわかる。本願発明の液晶表示装置には、このような電気光学特性を示す強誘電性液晶も用いることができる。

【0212】

また、ある温度域において反強誘電相を示す液晶を反強誘電性液晶(AFLC)という。反強誘電性液晶を有する混合液晶には、電場に対して透過率が連続的に変化する電気光学応答特性を示す、無しきい値反強誘電性混合液晶と呼ばれるものがある。この無しきい値反強誘電性混合液晶は、いわゆるV字型の電気光学応答特性を示すものがあり、その駆動電圧が約±2.5V程度(セル厚約1μm〜2μm)のものも見出されている。

【0213】

また、一般に、無しきい値反強誘電性混合液晶は自発分極が大きく、液晶自体の誘電率が高い。このため、無しきい値反強誘電性混合液晶を液晶表示装置に用いる場合には、画素に比較的大きな保持容量が必要となってくる。よって、自発分極が小さな無しきい値反強誘電性混合液晶を用いるのが好ましい。

【0214】

なお、このような無しきい値反強誘電性混合液晶を本願発明の液晶表示装置に用いることによって低電圧駆動が実現されるので、低消費電力化が実現される。

【0215】

なお、本実施例に示す液晶は、実施例1〜4のいずれの構成を有する液晶表示装置においても用いることが可能である。

【0216】

〔実施例12〕

本願発明の電気光学装置や半導体回路は電気器具の表示部や信号処理回路として用いることができる。そのような電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター、プロジェクションTV、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置などが挙げられる。それら電気器具の具体例を図22〜23に示す。

【0217】

図22(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示部2004、操作スイッチ2005、アンテナ2006で構成される。本願発明の電気光学装置は表示部2004に、本願発明の半導体回路は音声出力部2002、音声入力部2003またはCPUやメモリ等に用いることができる。

【0218】

図22(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明の電気光学装置は表示部2102に、本願発明の半導体回路は音声入力部2103またはCPUやメモリ等に用いることができる。

【0219】

図22(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205で構成される。本願発明の電気光学装置は表示部2205に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0220】

図22(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303で構成される。本願発明の電気光学装置は表示部2302に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0221】

図22(E)はリアプロジェクター(プロジェクションTV)であり、本体2401、光源2402、電気光学装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本発明は電気光学装置2403に用いることができ、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0222】

図22(F)はフロントプロジェクターであり、本体2501、光源2502、電気光学装置2503、光学系2504、スクリーン2505で構成される。本発明は電気光学装置2502に用いることができ、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0223】

図23(A)はパーソナルコンピュータであり、本体2601、映像入力部2602、表示部2603、キーボード2604等を含む。本願発明の電気光学装置は表示部2603に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0224】

図23(B)は電子遊戯機器(ゲーム機器)であり、本体2701、記録媒体2702、表示部2703及びコントローラー2704を含む。この電子遊技機器から出力された音声や映像は筐体2705及び表示部2706を含む表示ディスプレイにて再生される。コントローラー2704と本体2701との間の通信手段または電子遊技機器と表示ディスプレイとの間の通信手段は、有線通信、無線通信もしくは光通信が使える。本実施例では赤外線をセンサ部2707、2708で検知する構成となっている。本願発明の電気光学装置は表示部2703、2706に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0225】

図23(C)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤー(画像再生装置)であり、本体2801、表示部2802、スピーカ部2803、記録媒体2804及び操作スイッチ2805を含む。なお、この画像再生装置は記録媒体としてDVD(Digital VersatileDisc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2802やCPUやメモリ等に用いることができる。

【0226】

図23(D)はデジタルカメラであり、本体2901、表示部2902、接眼部2903、操作スイッチ2904、受像部(図示せず)を含む。本願発明は表示部2902やCPUやメモリ等に用いることができる。

【0227】

なお、図22(E)のリアプロジェクターや図22(F)のフロントプロジェクターに用いることのできる光学エンジンについての詳細な説明を図24に示す。なお、図24(A)は光学エンジンであり、図24(B)は光学エンジンに内蔵される光源光学系である。

【0228】

図24(A)に示す光学エンジンは、光源光学系3001、ミラー3002、3005〜3007、ダイクロイックミラー3003、3004、光学レンズ3008a〜3008c、プリズム3011、液晶表示装置3010、投射光学系3012を含む。投射光学系3012は、投射レンズを備えた光学系である。本実施例は液晶表示装置3010を三つ使用する三板式の例を示したが、単板式であってもよい。また、図24(A)中において矢印で示した光路には、光学レンズ、偏光機能を有するフィルム、位相差を調節するためのフィルムもしくはIRフィルム等を設けてもよい。

【0229】

また、図24(B)に示すように、光源光学系3001は、光源3013、3014、合成プリズム3015、コリメータレンズ3016、3020、レンズアレイ3017、3018、偏光変換素子3019を含む。なお、図24(B)に示した光源光学系は光源を2つ用いたが、一つでも良いし、三つ以上としてもよい。また、光源光学系の光路のどこかに、光学レンズ、偏光機能を有するフィルム、位相差を調節するフィルムもしくはIRフィルム等を設けてもよい。

【0230】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することが可能である。また、本実施例の電気器具は実施例1〜11のどのような組み合わせからなる構成を用いても実現することができる。

【0231】

【発明の効果】

本発明を実施することでNTFTの信頼性を高めることができる。従って、厳しい信頼性が要求される高い電気特性(特に高いモビリティ)を有するNTFTの信頼性を確保することが可能となった。また同時に、特性バランスに優れたNTFTとPTFTとを組み合わせてCMOS回路を形成することで、信頼性が高く且つ優れた電気特性を示す半導体回路を形成できる。

【0232】

さらに、本願発明では、同一基板上において動作電圧の異なる回路ごとに第2の不純物領域および/または第3の不純物領域の長さを最適化して異ならせる。こうすることにより、高速動作を要求する回路にはそれに見合った動作速度を有する回路を形成し、耐圧特性の良さを要求する回路にはそれに見合った耐圧特性を有する回路を形成することができる。

【0233】

従って、回路の種類に応じた構造のNTFT(特にCMOS回路として配置される場合)を適切に配置することで、回路の性能を最大限に引き出すことが可能となり、高い信頼性と高い動作性能を有する半導体回路(または電気光学装置)を実現することができる。

【0234】

また、以上のような電気光学装置や半導体回路を部品として搭載した電気器具の性能向上や信頼性向上を図ることが可能となる。

【図面の簡単な説明】

【図1】 AM−LCDの回路配置を説明するための図。

【図2】 AM−LCDの回路の断面構造を示す図。

【図3】 NTFTの作製工程を示す図。

【図4】 NTFTの作製工程を示す図。

【図5】 NTFTの断面構造を示す図。

【図6】 NTFTの断面構造を示す図。

【図7】 NTFTの断面構造を示す図。

【図8】 AM−LCDの外観を示す図。

【図9】 CMOS回路の断面構造を示す図。

【図10】 CMOS回路の作製工程を示す図。

【図11】 電気器具の一例を示す図。

【図12】 シミュレーション結果を示す図。

【図13】 バイアスパワー密度とテーパー角の関係を示す図。

【図14】 CF4流量とテーパー角の関係を示す図。

【図15】 W/レジスト選択比とテーパー角の関係を示す図。

【図16】 EL表示装置の上面構造及び断面構造を示す図。

【図17】 EL表示装置の断面構造を示す図。

【図18】 EL表示装置の上面構造及び回路構成を示す図。

【図19】 EL表示装置の断面構造を示す図。

【図20】 EL表示装置の回路構成を示す図。

【図21】 液晶の電気光学特性を示す図。

【図22】 電気器具の一例を示す図。

【図23】 電気器具の一例を示す図。

【図24】 光学エンジンの構成を示す図。

Claims (5)

- 第1の薄膜トランジスタと第2の薄膜トランジスタとを有し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとは、それぞれ、半導体層と、前記半導体層上のゲート絶縁膜と、前記ゲート絶縁膜上のゲート電極とを含み、

前記半導体層は、チャネル形成領域と、n型不純物が添加された一対の第1の不純物領域と、n型不純物が添加された一対の第2の不純物領域と、n型不純物が添加された一対の第3の不純物領域とを有し、

前記ゲート電極は、端部にテーパー部を有し、

一対の前記第2の不純物領域は、前記チャネル形成領域を間に挟んで設けられ、

一対の前記第3の不純物領域は、前記チャネル形成領域及び一対の前記第2の不純物領域を間に挟んで設けられ、

一対の前記第1の不純物領域は、前記チャネル形成領域、一対の前記第2の不純物領域、及び一対の前記第3の不純物領域を間に挟んで設けられ、

一対の前記第2の不純物領域は、前記ゲート電極のテーパー部と重なり、

一対の前記第3の不純物領域は、前記ゲート電極と重ならず、

一対の前記第1の不純物領域は、一対の前記第2の不純物領域及び一対の前記第3の不純物領域よりもn型不純物の濃度が高く、ソース領域又はドレイン領域として機能し、

前記第1の薄膜トランジスタに含まれる前記第2の不純物領域のチャネル長方向の長さと、前記第2の薄膜トランジスタに含まれる前記第2の不純物領域のチャネル長方向の長さとは異なることを特徴とする半導体装置。 - 第1の薄膜トランジスタと第2の薄膜トランジスタとを有し、

前記第1の薄膜トランジスタと前記第2の薄膜トランジスタとは、それぞれ、半導体層と、前記半導体層上のゲート絶縁膜と、前記ゲート絶縁膜上のゲート電極とを含み、

前記半導体層は、チャネル形成領域と、n型不純物が添加された一対の第1の不純物領域と、n型不純物が添加された一対の第2の不純物領域と、n型不純物が添加された一対の第3の不純物領域とを有し、

前記ゲート電極は、端部にテーパー部を有する第1のゲート電極と、前記第1のゲート電極上の第2のゲート電極とを含み、

前記第2のゲート電極のチャネル長方向の長さは前記第1のゲート電極のチャネル長方向の長さよりも短く、

前記第1のゲート電極は、前記チャネル形成領域及び一対の前記第2の不純物領域と重なり、

前記第2のゲート電極は、前記第1のゲート電極及び前記チャネル形成領域と重なり、

一対の前記第2の不純物領域は、前記チャネル形成領域を間に挟んで設けられ、

一対の前記第3の不純物領域は、前記チャネル形成領域及び一対の前記第2の不純物領域を間に挟んで設けられ、

一対の前記第1の不純物領域は、前記チャネル形成領域、一対の前記第2の不純物領域、及び一対の前記第3の不純物領域を間に挟んで設けられ、

一対の前記第2の不純物領域は、前記第1のゲート電極のテーパー部と重なり、

一対の前記第3の不純物領域は、前記第1のゲート電極と重ならず、

一対の前記第1の不純物領域は、一対の前記第2の不純物領域及び一対の前記第3の不純物領域よりもn型不純物の濃度が高く、ソース領域又はドレイン領域として機能し、

前記第1の薄膜トランジスタに含まれる前記第2の不純物領域のチャネル長方向の長さと、前記第2の薄膜トランジスタに含まれる前記第2の不純物領域のチャネル長方向の長さとは異なることを特徴とする半導体装置。 - 請求項2において、

前記第1のゲート電極は、クロム膜、タンタル膜、タンタルを主成分とする薄膜、又は リンを含有するn型のシリコン膜で形成されることを特徴とする半導体装置。 - 請求項2において、

前記第2のゲート電極は、アルミニウム膜、銅膜、アルミニウム又は銅を主成分とする薄膜、クロム膜、タンタル膜、窒化タンタル膜、チタン膜、タングステン膜、モリブデン膜、リンを含有するn型のシリコン膜、タングステン−モリブデン膜、又はタンタル−モリブデン膜で形成されることを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一項に記載の半導体装置を用いていることを特徴とする電気器具。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33179499A JP4159713B2 (ja) | 1998-11-25 | 1999-11-22 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP10-333665 | 1998-11-25 | ||

| JP33366598 | 1998-11-25 | ||

| JP33179499A JP4159713B2 (ja) | 1998-11-25 | 1999-11-22 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005301223A Division JP4160072B2 (ja) | 1998-11-25 | 2005-10-17 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000223714A JP2000223714A (ja) | 2000-08-11 |

| JP2000223714A5 JP2000223714A5 (ja) | 2005-12-02 |

| JP4159713B2 true JP4159713B2 (ja) | 2008-10-01 |

Family

ID=26573968

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33179499A Expired - Fee Related JP4159713B2 (ja) | 1998-11-25 | 1999-11-22 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4159713B2 (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2256808A2 (en) | 1999-04-30 | 2010-12-01 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device and manufacturing method therof |

| JP4850328B2 (ja) * | 2000-08-29 | 2012-01-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5046452B2 (ja) * | 2000-10-26 | 2012-10-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2002151698A (ja) * | 2000-11-14 | 2002-05-24 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| TW525216B (en) | 2000-12-11 | 2003-03-21 | Semiconductor Energy Lab | Semiconductor device, and manufacturing method thereof |

| JP4737828B2 (ja) * | 2000-12-21 | 2011-08-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4926321B2 (ja) * | 2001-01-24 | 2012-05-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4939690B2 (ja) * | 2001-01-30 | 2012-05-30 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4801262B2 (ja) * | 2001-01-30 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4693257B2 (ja) * | 2001-02-21 | 2011-06-01 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| SG117406A1 (en) | 2001-03-19 | 2005-12-29 | Miconductor Energy Lab Co Ltd | Method of manufacturing a semiconductor device |

| JP4338934B2 (ja) * | 2001-03-27 | 2009-10-07 | 株式会社半導体エネルギー研究所 | 配線の作製方法 |

| JP4926329B2 (ja) | 2001-03-27 | 2012-05-09 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法、電気器具 |

| SG116443A1 (en) | 2001-03-27 | 2005-11-28 | Semiconductor Energy Lab | Wiring and method of manufacturing the same, and wiring board and method of manufacturing the same. |

| KR100983525B1 (ko) | 2003-12-26 | 2010-09-24 | 삼성전자주식회사 | 상보형 박막트랜지스터 형성방법과 이에 의한 상보형박막트랜지스터 |

| JP2006003493A (ja) * | 2004-06-16 | 2006-01-05 | Nikon Corp | 形状転写方法 |

| US8570455B2 (en) | 2008-04-02 | 2013-10-29 | Nlt Technologies, Ltd. | Semiconductor device, semiconductor device manufacturing method, liquid crystal display device and electronic apparatus |

| JP5520911B2 (ja) * | 2011-10-12 | 2014-06-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9786793B2 (en) | 2012-03-29 | 2017-10-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising oxide semiconductor layer including regions with different concentrations of resistance-reducing elements |

-

1999

- 1999-11-22 JP JP33179499A patent/JP4159713B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000223714A (ja) | 2000-08-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100570888C (zh) | 半导体器件 | |

| US7244962B2 (en) | Method of manufacturing semiconductor devices | |

| JP4531175B2 (ja) | 半導体装置の作製方法 | |

| JP4159713B2 (ja) | 半導体装置 | |

| US7064020B2 (en) | Method of manufacturing a semiconductor device having a gate electrode with a three layer structure | |

| US9214532B2 (en) | Ferroelectric liquid crystal display device comprising gate-overlapped lightly doped drain structure | |

| JP3901893B2 (ja) | 半導体装置およびその作製方法 | |

| JP4583529B2 (ja) | 半導体装置およびその作製方法 | |

| JP4536187B2 (ja) | 半導体装置およびその作製方法 | |

| JP4641582B2 (ja) | 半導体装置の作製方法 | |

| JP4558121B2 (ja) | 半導体装置及びその作製方法 | |

| JP4536186B2 (ja) | 半導体装置の作製方法 | |

| US20120074418A1 (en) | Semiconductor device | |

| JP3859915B2 (ja) | 半導体装置の作製方法 | |

| JP4583716B2 (ja) | 半導体装置 | |

| JP4850326B2 (ja) | 半導体装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP4160072B2 (ja) | 半導体装置の作製方法 | |

| JP3913689B2 (ja) | 半導体装置及びその作製方法 | |

| JP4558707B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051017 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051017 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060403 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080129 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080324 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080715 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080716 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4159713 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130725 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |