JP4149441B2 - 集積された突入電流リミッタ回路および方法 - Google Patents

集積された突入電流リミッタ回路および方法 Download PDFInfo

- Publication number

- JP4149441B2 JP4149441B2 JP2004551488A JP2004551488A JP4149441B2 JP 4149441 B2 JP4149441 B2 JP 4149441B2 JP 2004551488 A JP2004551488 A JP 2004551488A JP 2004551488 A JP2004551488 A JP 2004551488A JP 4149441 B2 JP4149441 B2 JP 4149441B2

- Authority

- JP

- Japan

- Prior art keywords

- inrush current

- circuit

- fault

- mirror transistor

- current limiter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title description 2

- 239000000758 substrate Substances 0.000 claims description 21

- 239000004065 semiconductor Substances 0.000 claims description 17

- 238000001514 detection method Methods 0.000 claims description 16

- 238000004891 communication Methods 0.000 claims description 8

- 230000004044 response Effects 0.000 claims description 8

- 238000005070 sampling Methods 0.000 claims 2

- 238000012544 monitoring process Methods 0.000 claims 1

- 239000003990 capacitor Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 6

- 230000010355 oscillation Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 3

- 230000001351 cycling effect Effects 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000002939 deleterious effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H9/00—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection

- H02H9/02—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection responsive to excess current

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H9/00—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection

- H02H9/001—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection limiting speed of change of electric quantities, e.g. soft switching on or off

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H9/00—Emergency protective circuit arrangements for limiting excess current or voltage without disconnection

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02H—EMERGENCY PROTECTIVE CIRCUIT ARRANGEMENTS

- H02H3/00—Emergency protective circuit arrangements for automatic disconnection directly responsive to an undesired change from normal electric working condition with or without subsequent reconnection ; integrated protection

- H02H3/006—Calibration or setting of parameters

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Emergency Protection Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Protection Of Static Devices (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

Description

Claims (5)

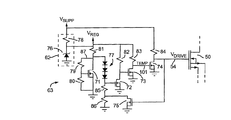

- センス電流から生成された制御信号に応答して動作するミラー・トランジスタであって、供給電圧に結合された第1ソース、前記供給電圧の負荷電流を出力ノードへルートするための共通ドレイン、および、前記負荷電流をサンプリングして前記センス電流を生成するための第2ソースを有するミラー・トランジスタと、

第1フォールト条件に応答して前記ミラー・トランジスタを不能にするフォールト保護回路であって、前記フォールト保護回路は、フォールト・スレショルド信号を生成するために形成され、かつ、前記突入電流リミッタ回路の外部のコンポーネントを用いて、前記フォールト・スレショルド信号の値を修正するために前記フォールト・スレショルド信号を突入電流リミッタ回路の第1外部リードに結合するために形成されるフォールト保護回路と、

前記突入電流リミッタ回路の外部で発生するフォールト条件を表わすフォールト信号を受信するために前記第1外部リードに結合され、前記フォールト信号を使用して前記ミラー・トランジスタを不能にするためのフォールト通信回路と、

から構成されることを特徴とする突入電流リミッタ回路。 - 前記フォールト保護回路を形成するための第1表面、および、前記ミラー・トランジスタの前記共通ドレインを形成するための第2表面、を有する半導体基板と、

検出回路であって、

前記フォールト保護回路、および、

第2フォールト条件を前記ミラー・トランジスタの温度としてモニタするために前記半導体基板上に形成された熱センサ、

を含む検出回路と、をさらに含み、

前記半導体基板の前記温度が予め決められた温度スレショルドよりも高いとき、前記熱センサがシャットダウン信号を生成する、

ことを特徴とする請求項1記載の前記突入電流リミッタ回路。 - 前記供給電圧をモニタするために前記突入電流リミッタ回路の第2外部リードに結合された不足電圧検出器をさらに含むことを特徴とする請求項1記載の突入電流リミッタ回路。

- 制御信号に応答して動作するための共通ゲートを有し、かつ、供給電圧に結合された電力ソース、負荷電流を供給するための共通ドレイン、および、前記負荷電流をサンプリングしてセンス電流を生成するためのセンシング・ソースを有する第1ミラー・トランジスタと、

第1過電圧スレショルド信号を生成するために形成され、前記供給電圧が第1過電圧スレショルド信号よりも大きいときに前記第1ミラー・トランジスタを不能にするために結合された第1検出回路であって、前記第1検出回路は、前記突入電流リミッタの第1外部リードに結合された入力を有し、かつ、前記第1過電圧スレショルド信号を前記第1外部リードに結合し前記第1過電圧スレショルド信号の値を外部から修正するために形成される、第1検出回路と、

フォールト条件に応答して前記第1ミラー・トランジスタを不能にし、かつ、シャットダウン信号を生成するために前記第1外部リードに結合された第1フォールト保護回路と、

から構成されることを特徴とする突入電流リミッタ。 - 前記第1検出回路および前記第1フォールト保護回路を形成するための第1表面、および、前記第1ミラー・トランジスタの前記共通ドレインを形成するための第2表面を有する第1半導体基板と、

第2半導体基板と、

前記第2半導体基板の第1表面上に形成され、かつ、前記第1ミラー・トランジスタの前記電力ソースおよび前記センシング・ソースにそれぞれ結合された電力ソースおよびセンシング・ソース、および、前記第2半導体基板の第2表面上に形成された共通ドレインを有する第2ミラー・トランジスタと、

前記供給電圧が第2過電圧スレショルド信号よりも大きいときに前記第2ミラー・トランジスタを不能にするために前記第2半導体基板の前記第1表面上に形成され、かつ、前記第2過電圧スレショルド信号の値を外部から修正するために前記突入電流リミッタ回路の第3外部リードに結合された入力を有する第2検出回路と、

前記シャットダウン信号で前記第2ミラー・トランジスタを不能にするために前記第1外部リードに結合された入力を有する第2フォールト保護回路と、

をさらに含むことを特徴とする請求項4記載の突入電流リミッタ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/291,015 US6865063B2 (en) | 2002-11-12 | 2002-11-12 | Integrated inrush current limiter circuit and method |

| PCT/US2003/030918 WO2004045038A1 (en) | 2002-11-12 | 2003-10-01 | Integrated inrush current limiter circuit and method |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006508628A JP2006508628A (ja) | 2006-03-09 |

| JP2006508628A5 JP2006508628A5 (ja) | 2006-08-31 |

| JP4149441B2 true JP4149441B2 (ja) | 2008-09-10 |

Family

ID=32229177

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004551488A Expired - Fee Related JP4149441B2 (ja) | 2002-11-12 | 2003-10-01 | 集積された突入電流リミッタ回路および方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6865063B2 (ja) |

| JP (1) | JP4149441B2 (ja) |

| KR (1) | KR100979086B1 (ja) |

| CN (1) | CN100438252C (ja) |

| AU (1) | AU2003277137A1 (ja) |

| WO (1) | WO2004045038A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8173348B2 (en) | 2006-06-27 | 2012-05-08 | Jsr Corporation | Method of forming pattern and composition for forming of organic thin-film for use therein |

Families Citing this family (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3957430B2 (ja) * | 1998-09-18 | 2007-08-15 | シャープ株式会社 | 液晶表示装置 |

| TWI243230B (en) * | 2004-07-16 | 2005-11-11 | Delta Electronics Inc | Hot-swap circuit system for fan tray |

| EP1797625B1 (en) * | 2004-09-28 | 2010-06-09 | Freescale Semiconductor Inc. | Power supply apparatus with overload protection |

| US7342433B2 (en) * | 2004-11-09 | 2008-03-11 | Fultec Semiconductor, Inc. | Apparatus and method for enhanced transient blocking |

| US7369387B2 (en) * | 2004-11-09 | 2008-05-06 | Fultec Semiconductor, Inc. | Apparatus and method for temperature-dependent transient blocking |

| US7646576B2 (en) * | 2004-11-09 | 2010-01-12 | Bourns, Inc. | Apparatus and method for high-voltage transient blocking using low voltage elements |

| JP4594064B2 (ja) * | 2004-12-20 | 2010-12-08 | フリースケール セミコンダクター インコーポレイテッド | サージ電流抑制回路及び直流電源装置 |

| US7492566B2 (en) * | 2005-01-14 | 2009-02-17 | Bourns, Inc. | Low resistance transient blocking unit |

| US20060158812A1 (en) * | 2005-01-14 | 2006-07-20 | Harris Richard A | Transient blocking unit having shunt for over-voltage protection |

| US7342440B2 (en) | 2005-03-04 | 2008-03-11 | Infineon Technologies Austria Ag | Current regulator having a transistor and a measuring resistor |

| DE102005010013B4 (de) * | 2005-03-04 | 2011-07-28 | Infineon Technologies Austria Ag | Stromregler mit einem Transistor und einem Messwiderstand |

| US20060238936A1 (en) * | 2005-04-25 | 2006-10-26 | Blanchard Richard A | Apparatus and method for transient blocking employing relays |

| US20060250736A1 (en) * | 2005-05-06 | 2006-11-09 | Harris Richard A | Transient blocking apparatus with electrostatic discharge protection |

| DE102005024634A1 (de) * | 2005-05-30 | 2006-12-07 | Siemens Ag | Schutzschaltung für ein Halbleiterschaltelement und eine Steuerschaltung sowie Verfahren zum Schutz eines Halbleiterschaltelements und einer Steuerschaltung |

| US7576962B2 (en) * | 2005-06-16 | 2009-08-18 | Bourns, Inc. | Transient blocking apparatus with reset |

| US20070035906A1 (en) * | 2005-08-11 | 2007-02-15 | Harris Richard A | Transient blocking unit |

| US7890232B2 (en) * | 2005-08-23 | 2011-02-15 | Fujitsu Ten Limited | Airbag system |

| DE102005039867B4 (de) * | 2005-08-23 | 2016-04-07 | Power Systems Technologies Gmbh | Eingangsschaltung für ein Schaltnetzteil |

| US7679876B2 (en) * | 2006-05-22 | 2010-03-16 | Mediatek Singapore Pte Ltd. | Current limiter system, circuit and method for limiting current |

| US7821750B2 (en) * | 2006-08-30 | 2010-10-26 | Leadtrend Technology Corp. | Voltage converter for preventing switch device from being damaged by voltage spike by utilizing protection circuit |

| DE102006055867A1 (de) * | 2006-11-23 | 2008-06-05 | IHP GmbH - Innovations for High Performance Microelectronics/Institut für innovative Mikroelektronik | Integrierte Schaltung mit Strahlungsschutz |

| TWI351093B (en) * | 2007-09-27 | 2011-10-21 | Univ Nat Chiao Tung | Electrostatic discharge protection device and integrated circuit utilizing the same |

| JP2009169785A (ja) * | 2008-01-18 | 2009-07-30 | Seiko Instruments Inc | ボルテージレギュレータ |

| CN101594046B (zh) * | 2008-05-29 | 2011-08-10 | 洋鑫科技股份有限公司 | 突入电流限制器 |

| US8300373B2 (en) * | 2008-06-26 | 2012-10-30 | Bourns, Inc. | Voltage triggered transient blocking unit |

| TWI397231B (zh) * | 2008-08-19 | 2013-05-21 | Anpec Electronics Corp | 嵌制電源熱插拔所造成電壓突波之電路及相關晶片 |

| KR20100103979A (ko) * | 2009-03-16 | 2010-09-29 | 삼성전자주식회사 | 단말기의 전원 공급에 따른 시스템 제어 방법 및 장치 |

| US7940505B1 (en) | 2009-12-01 | 2011-05-10 | Texas Instruments Incorporated | Low power load switch with protection circuitry |

| WO2011068517A1 (en) * | 2009-12-04 | 2011-06-09 | Hewlett-Packard Development Company, L.P. | Circuitry for hot-swappable circuit boards |

| US8947064B2 (en) | 2011-09-20 | 2015-02-03 | Infineon Technologies Austria Ag | System and method for driving an electronic switch dependent on temperature |

| US8878391B2 (en) | 2012-01-10 | 2014-11-04 | Schweitzer Engineering Laboratories, Inc | System, apparatus, and method for reducing inrush current in a three-phase transformer |

| CN102594572B (zh) * | 2012-01-21 | 2016-07-13 | 华为技术有限公司 | 一种抗浪涌的网络设备 |

| JP5875426B2 (ja) * | 2012-03-22 | 2016-03-02 | 富士通テン株式会社 | センサ信号処理装置、および車載型電子制御装置 |

| WO2014153151A2 (en) * | 2013-03-14 | 2014-09-25 | Innovolt, Inc. | Systems and methods for detecting and determiniing sources of power disturbances in connection with effective remediation |

| CN104253416A (zh) * | 2013-06-28 | 2014-12-31 | 鸿富锦精密电子(天津)有限公司 | 热保护电路 |

| US9735768B2 (en) * | 2013-07-31 | 2017-08-15 | Fairchild Semiconductor Corporation | Load balancing in discrete devices |

| EP3158415B1 (en) * | 2014-06-23 | 2023-05-10 | Gridbridge, Inc. | Highly flexible, electrical distribution grid edge energy manager and router |

| US9966836B1 (en) * | 2016-10-18 | 2018-05-08 | The Boeing Company | Systems and methods for a dual function inrush limiting circuit |

| US9819191B1 (en) * | 2016-11-15 | 2017-11-14 | Infineon Technologies Ag | Maximum power point tracking for low power energy harvesting |

| DE102017125726A1 (de) * | 2017-11-03 | 2019-05-09 | Infineon Technologies Austria Ag | Elektronische Schaltung mit Unterspannungsabschaltfunktion |

| US10254812B1 (en) | 2017-12-13 | 2019-04-09 | Cypress Semiconductor Corporation | Low inrush circuit for power up and deep power down exit |

| DE112020004328T5 (de) * | 2019-09-12 | 2022-06-02 | Rohm Co., Ltd. | Überstromschutzschaltung |

| DE102020131060A1 (de) * | 2020-11-24 | 2022-05-25 | Infineon Technologies Ag | Intelligenter elektronischer schalter |

| TWI762133B (zh) * | 2020-12-30 | 2022-04-21 | 致茂電子股份有限公司 | 湧浪電流抑制電路 |

| US11996688B2 (en) | 2021-05-12 | 2024-05-28 | Schweitzer Engineering Laboratories, Inc. | Method of controlled switching for transformers using transformer residual flux |

| US12048076B2 (en) * | 2021-06-22 | 2024-07-23 | Goodrich Corporation | System and method for inrush current control with combinational load drive configuration |

| US12313476B2 (en) * | 2021-07-01 | 2025-05-27 | Microchip Technology Incorporated | Temperature sensor integrated in a transistor array |

| CN113541252B (zh) * | 2021-07-16 | 2025-04-08 | 中磊电子(苏州)有限公司 | 物联网装置及其电池供电电路 |

| SE2250372A1 (en) * | 2022-03-25 | 2022-12-08 | Fingerprint Cards Anacatum Ip Ab | Fingerprint sensor with controllable current limiter |

| US12316112B2 (en) | 2022-07-12 | 2025-05-27 | Schweitzer Engineering Laboratories, Inc. | Breaker control units and related systems and methods |

| CN115240935B (zh) * | 2022-07-27 | 2024-08-09 | 成都顺康三森电子有限责任公司 | 一种抗高浪涌电流能力的ntc元件组成物及其制备方法 |

| WO2024072003A1 (ko) * | 2022-09-30 | 2024-04-04 | 삼성전자 주식회사 | 복수의 배터리들을 포함하는 전자 장치와 이의 동작 방법 |

| US20250183649A1 (en) * | 2023-12-05 | 2025-06-05 | International Business Machines Corporation | Programmable power dissipation-controlled electronic circuit breaker for high voltage distribution |

| CN117650493B (zh) * | 2024-01-30 | 2024-04-05 | 深圳智锐通科技有限公司 | 一种主板热插拔保护电路 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3597655A (en) * | 1970-01-26 | 1971-08-03 | Raytheon Co | Overvoltage protective circuit for constant voltage-current crossover network |

| JPH0666472B2 (ja) * | 1987-06-22 | 1994-08-24 | 日産自動車株式会社 | 過電流保護機能を備えたmosfet |

| JPH0369159A (ja) * | 1989-08-08 | 1991-03-25 | Nec Corp | 半導体装置 |

| JP3063167B2 (ja) * | 1989-12-29 | 2000-07-12 | 日本電気株式会社 | 電流検出端子付mos fetおよびその製造方法 |

| JP2856853B2 (ja) * | 1990-07-03 | 1999-02-10 | 株式会社東芝 | 半導体装置 |

| SE469731B (sv) * | 1991-04-02 | 1993-08-30 | Asea Brown Boveri | Digital anpassningsenhet |

| JP3377803B2 (ja) * | 1991-07-08 | 2003-02-17 | テキサス インスツルメンツ インコーポレイテツド | 温度依存限流回路および限流方法 |

| JPH05146057A (ja) * | 1991-11-18 | 1993-06-11 | Nec Ibaraki Ltd | 活線挿抜回路 |

| JPH06276673A (ja) * | 1993-03-15 | 1994-09-30 | Sumitomo Electric Ind Ltd | 突入電流制限回路 |

| JP3095102B2 (ja) * | 1993-06-18 | 2000-10-03 | エヌイーシーワイヤレスネットワークス株式会社 | 突入電流防止回路 |

| US5488533A (en) * | 1994-02-07 | 1996-01-30 | International Business Machines Corporation | Methods and apparatus for isolating a power network from a load during an overcurrent condition |

| US5581433A (en) * | 1994-04-22 | 1996-12-03 | Unitrode Corporation | Electronic circuit breaker |

| TW265482B (ja) * | 1994-06-01 | 1995-12-11 | Siemens Akitengesellschaft | |

| US5684663A (en) * | 1995-09-29 | 1997-11-04 | Motorola, Inc. | Protection element and method for protecting a circuit |

| US5761020A (en) * | 1996-01-29 | 1998-06-02 | International Rectifier Corporation | Fast switching smartfet |

| US5869969A (en) * | 1996-11-13 | 1999-02-09 | Northern Telecom Limited | Battery charger/rectifier voltage temperature compensation circuit including protection and diagnostic scheme |

| US6009008A (en) * | 1997-03-31 | 1999-12-28 | International Rectifier Corporation | Soft strat bridge rectifier circuit |

| JP3684866B2 (ja) * | 1998-10-16 | 2005-08-17 | 株式会社日立製作所 | 導通,遮断制御装置 |

| EP1122853B1 (en) * | 1999-12-31 | 2007-07-04 | Nokia Corporation | Method and apparatus for protection of batteries |

| FI20002165L (fi) * | 2000-10-02 | 2002-07-22 | Smartconnection Oy | Sähkötaulu ja varoke |

| US6768623B1 (en) * | 2000-11-17 | 2004-07-27 | Texas Instruments Incorporated | IC excess current detection scheme |

| US6917504B2 (en) * | 2001-05-02 | 2005-07-12 | Supertex, Inc. | Apparatus and method for adaptively controlling power supplied to a hot-pluggable subsystem |

-

2002

- 2002-11-12 US US10/291,015 patent/US6865063B2/en not_active Expired - Lifetime

-

2003

- 2003-10-01 AU AU2003277137A patent/AU2003277137A1/en not_active Abandoned

- 2003-10-01 KR KR1020057008550A patent/KR100979086B1/ko not_active Expired - Fee Related

- 2003-10-01 JP JP2004551488A patent/JP4149441B2/ja not_active Expired - Fee Related

- 2003-10-01 WO PCT/US2003/030918 patent/WO2004045038A1/en active Application Filing

- 2003-10-01 CN CNB200380102951XA patent/CN100438252C/zh not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8173348B2 (en) | 2006-06-27 | 2012-05-08 | Jsr Corporation | Method of forming pattern and composition for forming of organic thin-film for use therein |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100438252C (zh) | 2008-11-26 |

| AU2003277137A1 (en) | 2004-06-03 |

| US6865063B2 (en) | 2005-03-08 |

| KR100979086B1 (ko) | 2010-08-31 |

| US20040090726A1 (en) | 2004-05-13 |

| CN1711665A (zh) | 2005-12-21 |

| JP2006508628A (ja) | 2006-03-09 |

| HK1084511A1 (zh) | 2006-07-28 |

| WO2004045038A1 (en) | 2004-05-27 |

| KR20050070127A (ko) | 2005-07-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4149441B2 (ja) | 集積された突入電流リミッタ回路および方法 | |

| JP4188321B2 (ja) | 集積突入電流リミッタ回路および方法 | |

| US6674657B2 (en) | Overvoltage-protective device for power system, AC/DC converter and DC/DC converter constituting the power system | |

| EP1671408B1 (en) | Power switch structure and method | |

| EP3855624A1 (en) | Overvoltage protection circuit and device | |

| US5951660A (en) | Current control interface arrangement | |

| KR20140042466A (ko) | 클램핑 회로, 이를 포함하는 반도체 장치 및 반도체 장치의 클램핑 방법 | |

| MXPA05004097A (es) | Conmutador de energia controlado por barra colectora. | |

| CN100480943C (zh) | 电压调节器 | |

| CN1663091B (zh) | 受保护的双电压微电路电源设备 | |

| US6618230B2 (en) | Electrostatic discharge cell of integrated circuit | |

| US8422185B2 (en) | Method and device for delaying activation timing of output device | |

| JP6177939B2 (ja) | 半導体集積回路装置 | |

| US20230138437A1 (en) | Electrostatic discharge protection circuit | |

| US20070035906A1 (en) | Transient blocking unit | |

| KR101060141B1 (ko) | 전지 보호 방법 및 그의 구조 | |

| JP6332601B2 (ja) | 半導体集積回路装置 | |

| JP5143096B2 (ja) | 保護回路 | |

| JP4110701B2 (ja) | 過電圧保護回路 | |

| HK1084511B (en) | Integrated inrush current limiter circuit | |

| HK1078993B (en) | Integrated inrush current limiter circuit and method | |

| HK1099628B (en) | Method for regulating temperature and circuit therefor | |

| HK1099628A1 (en) | Method for regulating temperature and circuit therefor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060713 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060713 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070615 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080623 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080625 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110704 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4149441 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110704 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120704 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130704 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |