JP4115045B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4115045B2 JP4115045B2 JP18878799A JP18878799A JP4115045B2 JP 4115045 B2 JP4115045 B2 JP 4115045B2 JP 18878799 A JP18878799 A JP 18878799A JP 18878799 A JP18878799 A JP 18878799A JP 4115045 B2 JP4115045 B2 JP 4115045B2

- Authority

- JP

- Japan

- Prior art keywords

- address

- memory cell

- spare

- signal

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/70—Masking faults in memories by using spares or by reconfiguring

- G11C29/78—Masking faults in memories by using spares or by reconfiguring using programmable devices

- G11C29/781—Masking faults in memories by using spares or by reconfiguring using programmable devices combined in a redundant decoder

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/70—Masking faults in memories by using spares or by reconfiguring

- G11C29/78—Masking faults in memories by using spares or by reconfiguring using programmable devices

- G11C29/835—Masking faults in memories by using spares or by reconfiguring using programmable devices with roll call arrangements for redundant substitutions

Description

【発明の属する技術分野】

この発明は、半導体記憶装置に関し、より特定的には、冗長回路(スペア)を搭載し、不良メモリセルを救済置換できるような回路構成を持つ冗長回路付半導体記憶装置に関するものである。

【0002】

【従来の技術】

冗長回路付半導体記憶装置は、不良ビットが内在する半導体記憶装置内のメモリセル列または行を、予備として形成しておいた冗長回路(以後スペアと呼ぶ)と置換することで、不良品を救済し良品とすることが可能である。

【0003】

一般的には、冗長回路内に複数本形成した溶断可能な配線(以後フューズと呼ぶ)を、微細配線を溶断加工する装置(以後レーザトリマと呼ぶ)を用いて選択的にレーザ光線を照射し切断することで、置換したい不良メモリセル列または行だけに対して冗長回路を適用できるようにしている。以後このような方式をレーザトリミング方式と呼ぶ。

【0004】

不良メモリセル列または行を置換するためにはレーザトリマを使わない他の方法もある。フューズに対し高電圧を外部から印加することにより抵抗体であるフューズを電気的に加熱切断する方法である。以後この方法を電気フューズ方式と呼び、使用するフューズのことを電気フューズと呼ぶ。電気フューズ方式の場合、半導体装置をパッケージングした後でも、外部から高電圧を印加して電気フューズを切断できるため、最終的な良品歩留まりを高めることが可能である。レーザトリミング方式の場合では、レーザ光線をフューズに照射することができないためパッケージング後には救済置換を実施できない。

【0005】

図13は、従来の冗長回路を搭載した半導体記憶装置の内部構成を示す図であり、主としてスペアがどのようにして選択されるかをブロック図で示したものである。

【0006】

冗長回路付半導体記憶装置を外部試験装置(テスタ等)を使って試験することで、不良ビットを含んだメモリセル行または列が半導体記憶装置のどの位置に存在するか、すなわち不良ビットのアドレスがどこであるかを認識することが可能であることは広く知られている。

【0007】

図13を参照して、従来の半導体記憶装置は、メインメモリセル352と、アドレス信号ADを受けてデコードしメインメモリセル352中の対応するアドレスのメモリセルを選択するためのメインアドレスデコーダ350と、不良メモリセルを救済時にフューズ選択アドレス信号BSELを受けてデコードして、通常動作時にはアドレスストローブ信号/ASを受けてフューズ選択信号BSIGを出力するフューズ選択回路344と、アドレス信号ADおよびフューズ選択信号BSIGを受けてスペアセレクト信号を出力する冗長回路プログラムフューズ346と、スペアセレクト信号を受けてメインアドレスデコーダ350を非活性化するデコーダ非活性化回路348と、スペアセレクト信号を受けてデコードするスペアアドレスデコーダ354と、スペアアドレスデコーダによって対応する部分が活性化されるスペアメモリセル356とを含む。

【0008】

不良メモリセルのアドレスをスペアメモリセル356に置換して救済する場合は、冗長回路プログラムフューズ346に不良ビットに対応するアドレス情報を記憶させる(プログラムする)ことで不良ビットの救済が実現可能となる。不良ビットに対応するアドレス情報を記憶させるためには、アルミやポリシリコン等の配線材料によって形成された複数のフューズを、レーザトリミング方式の場合はレーザ光線にて、電気フューズ方式の場合はフューズ両端に高電圧を印加することによって選択的に切断することが行なわれる。

【0009】

半導体記憶装置内のメインメモリセル352に外部からアクセスするためには、アドレス信号ADを外部から印加し、メインアドレスデコーダ350を介して所望のメインメモリセル行または列にアクセスする。

【0010】

一方、メインメモリセル352内に不良があったためにスペアメモリセル356に置換するときは、冗長回路プログラムフューズ346に不良メモリセルのアドレスに対応する情報が記録される。アドレスが外部より入力されると、冗長回路プログラムフューズ346に記録された情報対応するアドレスと入力されたアドレスとのアドレス比較がなされる。このアドレス比較の結果が一致である場合には、スペアが使用されるとみなされて、スペアセレクト信号SPSELが冗長回路プログラムフューズ346から出力される。

【0011】

なお、デコーダ非活性化回路348は、スペアが選択されてスペアセレクト信号SPSELが出力された場合に、非活性化信号をメインアドレスデコーダ350に対して出力しメインアドレスデコーダ350を非活性化することでメインメモリセル352をアクセスしないようにするものである。

【0012】

スペアセレクト信号SPSELは、スペアアドレスデコーダ354によってデコードされ、その結果に基づきスペアメモリセル356が選択される。

【0013】

以上により、特定のアドレス(置換したいアドレス)が入力された場合にスペアへの置換が可能となる。

【0014】

次に、複数本あるスペアの選択方法と置換アドレスの記憶方法について説明する。

【0015】

図14は、スペアの選択方法を説明するための簡略的なブロック図である。

図14では、説明の簡単のためメインメモリセル356のアドレス空間が2ビット分すなわち4アドレスであり、スペア本数が2ビット分すなわち4本である場合を例にして説明する。スペアは4本であるため、スペアセレクト信号SPSEL0〜SPSEL3の4つの信号があり、各々がスペアメモリセル360、361、362、363に対応している。たとえば、スペアメモリセル362を選択したい場合には、スペアセレクト信号SPSEL2が活性化される。

【0016】

4つのスペアメモリセル360〜363のいずれのメモリセルに接続させるかを指定するためには、外部あるいは半導体記憶装置内部で発生されるフューズ選択アドレス信号BSELが使用される。この例では、スペアが4つあるため、フューズ選択アドレス信号BSELが2ビットの信号BSEL0、BSEL1を含む。

【0017】

フューズ選択アドレス信号BSELは、フューズ選択デコーダ344によりスペアメモリセルに対応する4つの信号にデコードされる。このフューズ選択信号BSIGは4つの信号ビットBSIG0、BSIG1、BSIG2、BSIG3を含んでおり、最初に置換アドレスを記憶させる場合にはBSIG0が印加され、第2番目の置換アドレスが記憶させる場合には、BSIG1が印加され、第3、第4番目に置換アドレスを記憶させる場合には、BSIG2、BSIG3の順番に冗長置換回路プログラムフューズ346に印加される。つまり、第1回目にフューズ選択が行なわれる場合には、フューズ選択アドレス信号の内容は、BSEL0=0,BSEL1=0となっており、その場合には、フューズ選択信号BSIG0=HとなりBSIG1〜BSIG3=Lとなる。

【0018】

【発明が解決しようとする課題】

救済後の別工程すなわちパッケージング後の工程等で新たに発生した不良ビットを、未使用のスペアを使って追加で置換し救済したい場合がある。従来の電気フューズ方式を用いた冗長回路付半導体記憶装置では、1回目に置換した冗長回路のスペアの使用情報を半導体記憶装置の内部または外部記憶装置等に記憶させておかなければ、2回目の置換をした場合に、1回目の置換で使用したスペアアドレスと同じスペアアドレスを多重選択してしまう等により、救済できるケースでも救済できないという不具合が生じてしまう問題があった。

【0019】

使用した冗長回路のスペア情報を半導体記憶装置内部に記憶しておく場合は、記憶情報が消去されないように、たとえばフラッシュメモリや強誘電体メモリ等の不揮発性メモリセルを使って記憶させておく手段が考えられるが、不揮発性メモリを組込むために多くの追加回路を必要とし、ひいては半導体記憶装置の面積が増加してしまう。

【0020】

一方、外部記憶装置に記憶させておく等の手段の場合には、スペア使用情報の他に半導体装置それぞれのチップに対応する識別情報をも覚えておかなければならない。この場合、パッケージングの後にでもチップとスペア使用情報との対応づけが正しくできるように手段を講ずる必要があるため、認識処理工程等の追加が必要となり、半導体記憶装置の価格高騰に繋がる。

【0021】

この発明の目的は、2度目のスペア置換工程において、使用するスペアが重複しないようなスペアアドレスの選択を優先的に行なうことができる半導体記憶装置を提供することである。

【0022】

【課題を解決するための手段】

請求項1に記載の半導体記憶装置は、正規メモリセル領域を備え、正規メモリセル領域は、複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、正規メモリセル領域に対応して設けられ、アドレス信号を受けて正規メモリセル群のいずれかを選択するメインアドレスデコーダと、スペアメモリセル領域とをさらに備え、スペアメモリセル領域は、正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けてスペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、スペアメモリセル群と置換する正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、アドレス信号が置換アドレスと一致するときはメインアドレスデコーダを非活性化し、スペアアドレス信号を出力する置換制御回路とをさらに備え、置換制御回路は、複数のスペアメモリセル群にそれぞれ対応して設けられ、置換アドレスデータを保持する複数のアドレス設定部と、設定部選択信号に応じて複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、設定部選択回路は、正規メモリセル群をスペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、設定部選択信号に対する複数のアドレス設定部の使用優先順を保持回路の保持情報に応じて決定する。

【0023】

請求項1に記載の半導体記憶装置の設定部選択回路は、設定部選択信号を受けて保持回路の保持情報が置換未実施に対応するときはそのまま出力し、保持回路の保持情報が置換実施済に対応するときは設定部選択信号の各信号ビットを反転させて出力する変換回路と、変換回路の出力を受けてデコードし複数のアドレス設定部のいずれかを選択する設定部選択デコーダとをさらに有する。

【0024】

請求項2に記載の半導体記憶装置は、請求項1に記載の半導体記憶装置の構成に加えて、変換回路は、設定部選択信号の各信号ビットを反転させる相補アドレス発生回路と、設定部選択信号と相補アドレス発生回路の出力とを受けて保持回路の保持情報に応じていずれか一方を選択して設定部選択デコーダに出力する選択回路とを有する。

【0025】

請求項3に記載の半導体記憶装置は、請求項2に記載の半導体記憶装置の構成に加えて、相補アドレス発生回路は、設定部選択信号の各信号ビットをそれぞれ入力に受ける複数のインバータを有し、保持回路は、置換動作の終了時に電極間に所定の高電圧が与えられ電極間が導通状態となり保持回路の保持情報を保持するアンチフューズを有し、選択回路は、アンチフューズの電極間の導通状態に応じて設定部選択信号と相補アドレス発生回路の出力のいずれか一方を選択して出力する。

【0026】

請求項4に記載の半導体記憶装置は、請求項2に記載の半導体記憶装置の構成に加えて、相補アドレス発生回路は、設定部選択信号の各信号ビットをそれぞれ入力に受ける複数のインバータを有し、保持回路は、置換動作の終了時に電極間に所定の高電圧が与えられ電極間が非導通状態となり保持回路の保持情報を保持する電気フューズを有し、選択回路は、電気フューズの電極間の導通状態に応じて設定部選択信号と相補アドレス発生回路の出力のいずれか一方を選択して出力する。

【0027】

請求項5に記載の半導体記憶装置は、正規メモリセル領域を備え、正規メモリセル領域は、複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、正規メモリセル領域に対応して設けられ、アドレス信号を受けて正規メモリセル群のいずれかを選択するメインアドレスデコーダと、スペアメモリセル領域とをさらに備え、スペアメモリセル領域は、正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けてスペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、スペアメモリセル群と置換する正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、アドレス信号が置換アドレスと一致するときはメインアドレスデコーダを非活性化し、スペアアドレス信号を出力する置換制御回路とをさらに備え、置換制御回路は、複数のスペアメモリセル群にそれぞれ対応して設けられ、置換アドレスデータを保持する複数のアドレス設定部と、設定部選択信号に応じて複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、設定部選択回路は、正規メモリセル群をスペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、設定部選択信号に対する複数のアドレス設定部の使用優先順を保持回路の保持情報に応じて決定する。設定部選択回路は、設定部選択信号を受けてデコードする設定部選択デコーダと、保持回路の保持情報が置換未実施に対応するときはそのまま出力し、保持回路の保持情報が置換実施済に対応するときは設定部選択デコーダの出力信号の各信号ビットの順番を入れ替えて出力する順番入換回路とをさらに含む。

【0028】

請求項6に記載の半導体記憶装置は、請求項5に記載の半導体記憶装置の構成において、順番入換回路は、設定部選択デコーダの出力信号がnビットの信号であるときに、上位から数えて第kビット目が活性化されると順番入換回路のnビットの出力信号の下位から数えて第kビット目を活性化させる動作と、上位から数えて第kビット目が活性化されると順番入換回路のnビットの出力信号の上位から数えて第kビット目を活性化させる動作とのいずれかを保持回路の保持情報に応じて選択して実行する(nは自然数、kはn以下の自然数)。

【0029】

請求項7に記載の半導体記憶装置は、請求項6に記載の半導体記憶装置の構成に加えて、保持回路は、置換動作の終了時に電極間に所定の高電圧が与えられ電極間が導通状態となり保持回路の保持情報を保持するアンチフューズを有する。

【0030】

請求項8に記載の半導体記憶装置は、請求項6に記載の半導体記憶装置の構成に加えて、保持回路は、置換動作の終了時に電極間に所定の高電圧が与えられ電極間が非導通状態となり保持回路の保持情報を保持する電気フューズを有する。

【0031】

請求項9に記載の半導体記憶装置は、正規メモリセル領域を備え、正規メモリセル領域は、複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、正規メモリセル領域に対応して設けられ、アドレス信号を受けて正規メモリセル群のいずれかを選択するメインアドレスデコーダと、スペアメモリセル領域とをさらに備え、スペアメモリセル領域は、正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けてスペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、スペアメモリセル群と置換する正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、アドレス信号が置換アドレスと一致するときはメインアドレスデコーダを非活性化し、スペアアドレス信号を出力する置換制御回路とをさらに備え、置換制御回路は、複数のスペアメモリセル群にそれぞれ対応して設けられ、置換アドレスデータを保持する複数のアドレス設定部と、設定部選択信号に応じて複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、設定部選択回路は、正規メモリセル群をスペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、設定部選択信号に対する複数のアドレス設定部の使用優先順を保持回路の保持情報に応じて決定する。保持回路の保持情報は、ウエハ状態において置換動作が終了したときに所定の初期状態から反転され、パッケージ状態において置換動作を再度実施するために置換アドレスデータを入力する第1の端子群と、パッケージ状態において置換動作を再度実施するために設定部選択信号を入力する第2の端子群とをさらに備え、各アドレス設定部は、設定部選択信号および置換アドレスデータに応じて選択され、置換アドレスデータに対応する情報を保持する複数のアドレスビット設定部を有する。

【0034】

【発明の実施の形態】

以下において本発明の実施の形態について図面を参照して詳しく説明する。なお、図中同一符号は同一または相当部分を示す。

【0035】

[実施の形態1]

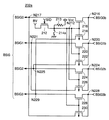

図1は、本発明の実施の形態1の半導体記憶装置1の構成を示す概略ブロック図である。

【0036】

図1を参照して、半導体記憶装置1は、制御信号ext./RAS、ext./CAS、ext./WEをそれぞれ受ける制御信号入力端子2〜6と、アドレス入力端子群8と、データ信号を入力する入力端子Dinと、データ信号を出力する出力端子Doutと、接地電位Vssが与えられる接地端子12と、電源電位Ext.Vccが与えられる電源端子10とを備える。

【0037】

半導体記憶装置1は、さらに、クロック発生回路22と、行および列置換制御回路24と、行デコーダ26と、列デコーダ28と、センスアンプ+入出力制御回路30と、メモリセルアレイ32と、ゲート回路18と、データ入力バッファ20およびデータ出力バッファ34とを備える。

【0038】

クロック発生回路22は、制御信号入力端子2、4を介して外部から与えられる外部行アドレスストローブ信号ext./RASと外部列アドレスストローブ信号ext./CASとに基づいた所定の動作モードに相当する制御クロックを発生し、半導体記憶装置全体の動作を制御する。

【0039】

行および列置換制御回路24は、外部から与えられるアドレス信号A0〜Ai(iは自然数)に基づいて生成したアドレス信号を行デコーダ26および列デコーダ28に与える。

【0040】

行デコーダ26と列デコーダ28とによって指定されたメモリセルアレイ32中のメモリセルは、センスアンプ+入出力制御回路30とデータ入力バッファ20またはデータ出力バッファ22とを介して入力端子Dinまたは出力端子Doutを通じて外部とデータをやり取りする。

【0041】

半導体記憶装置1は、さらに、不良メモリセルを救済するためのスペア列31と、スペア列を選択するためのスペア列デコーダ29と、不良メモリセルを救済するためのスペア行33と、スペア行33を選択するためのスペア行デコーダ27とを備える。

【0042】

図1に示した半導体記憶装置1は、代表的な一例であり、たとえば同期型半導体記憶装置(SDRAM)にも本発明は適用可能である。

【0043】

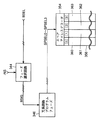

図2は、図1に示した行および列置換制御回路24の構成を説明するためのブロック図である。

【0044】

図2を参照して、行および列置換制御回路24は、置換すべきアドレスを記憶させるフューズを選択するために与えられるフューズ選択アドレス信号BSELを受け第1回目の置換実施時にはそのまま出力し、第2回目の置換実施時には相補アドレスを出力する相補アドレス発生回路42と、相補アドレス発生回路の出力およびアドレスストローブ信号/ASに応じてフューズ選択信号BSIGを出力するフューズ選択回路44と、外部から与えられるアドレス信号ADおよびフューズ選択信号BSIGに応じてスペアセレクト信号SPSELを出力する置換アドレス設定回路46と、スペアセレクト信号SPSELが活性化されたときにメインアドレスデコーダ50を非活性化するデコーダ非活性化回路48とを含む。スペアセレクト信号SPSELが活性化されると、スペアアドレスデコーダはスペアセレクト信号SPSELをデコードし、対応するスペアメモリセル56を活性化する。尚、説明の簡単のため図2は行系の制御、列系の制御に分離していないが、実際は、行デコーダ、列デコーダに対応して図2に示したブロックがそれぞれ設けられる。

【0045】

図3は、図2における相補アドレス発生回路42の構成を示す回路図である。

図3を参照して、相補アドレス発生回路42は、フューズ選択アドレス信号BSEL0を受けて信号BSEL0aを出力する回路42#0と、フューズ選択アドレス信号BSEL1を受けて信号BSEL1aを出力する回路42#1とを含む。

【0046】

回路42#0は、第1回目の冗長置換が終了した際に識別信号SIDをゲートに受けて活性化され高電圧BVをノードN1に伝達するNチャネルMOSトランジスタ68と、電源電位Vccが与えられる電源ノードとノードN1との間に接続される抵抗67と、ノードN1と接地ノードとの間に接続されるアンチフューズ66とを含む。

【0047】

置換するアドレスを記憶するため、特定のフューズに対しレーザ光線や電気信号を印加し、電気的性質を変えることをブローという。アンチフューズは電気フューズの一種であるが、ブローすることで電極間が導通する性質を持つ。

【0048】

アンチフューズ66は、特開平7−37984号公報に示されるように、プログラム前に高抵抗を有し、適当な電圧を印加すると低抵抗へとその導通状態を変化させる要素である。アンチフューズは、キャパシタ型の構造を有しており、たとえば、アルミニウムのような2個の導電層の間に二酸化ケイ素のような薄い絶縁層を挟んだものである。そのままではキャパシタすなわちオープン回路であるが、高電圧を印加してブローすると絶縁層に導電性のパスが発生し、数kΩ程度の抵抗値を持つ抵抗素子となる。

【0049】

すなわち、高電圧BVがノードN1に与えられると、アンチフューズ66は導通し以後ノードN1は接地ノードとほぼ等しい電位となる。したがって、ノードN1は、第1回目のフューズのブローが実施されるときにはHレベルであるが、第1回目のフューズのブローが完了したときにブローされるため、第2回目のフューズのブローが必要になった場合にはノードN1はLレベルとなっている。

【0050】

回路42#0は、さらに、ノードN2とノードN3との間に接続されゲートにノードN1が接続されるNチャネルMOSトランジスタ62と、ノードN2に与えられるフューズ選択アドレス信号BSEL0を受けて反転しノードN4に出力するインバータ70と、ノードN4とノードN3との間に接続されゲートにノードN1が接続されるPチャネルMOSトランジスタ64とを含む。

【0051】

ノードN3からは、相補アドレス発生回路42の出力である信号BSEL0aが出力される。

【0052】

図3では、フューズ選択アドレス信号BSELが含む2ビットの信号のうちフューズ選択アドレス信号BSEL0についてのみ詳細を示したが、フューズ選択アドレス信号BSEL1についても同様な回路42#1が設けられており、対応して信号BSEL1aが出力される。この場合に、ノードN1の電位を決定する抵抗67、アンチフューズ66、NチャネルMOSトランジスタ68は、回路42#0、回路42#1の共用にしてもかまわない。

【0053】

第1回目のフューズブロー時においては、ノードN1はHレベルであるため、NチャネルMOSトランジスタ62が導通し、ノードN2に与えられたフューズ選択アドレス信号BSEL0はそのままノードN3に伝達される。一方、第2回目のフューズブロー時においては、ノードN1は、先に説明したようにLレベルとなっているため、NチャネルMOSトランジスタ62は非導通状態であり、代わりにノードN4とノードN3との間に接続されるPチャネルMOSトランジスタ64が導通状態となるため、フューズ選択アドレス信号BSEL0はインバータ70によって反転される。つまり、信号BSEL0aはフューズ選択アドレス信号BSEL0の反転された信号となる。

【0054】

図4は、図2におけるフューズ選択回路44の構成を示す回路図である。

図4を参照して、フューズ選択回路44は、相補アドレス発生回路42の出力信号である信号BSEL0a、BSEL1aを受けてデコードするフューズ選択デコーダ82と、行または列アドレスのストローブ信号/ASを受けて反転するインバータ84と、フューズ選択デコーダ82の出力信号BSIG0aとインバータ84の出力とを受けてフューズ選択信号BSIG0を出力するOR回路86と、フューズ選択デコーダ82の出力信号BSIG1aとインバータ84の出力信号とを受けてフューズ選択信号BSIG1を出力するOR回路88と、フューズ選択デコーダ82の出力信号BSIG2aとインバータ84の出力信号とを受けてフューズ選択信号BSIG2を出力するOR回路90と、フューズ選択デコーダ82の出力信号BSIG3aとインバータ84の出力信号とを受けてフューズ選択信号BSIG3を出力するOR回路92とを含む。

【0055】

フューズ選択デコーダ82は、信号BSEL0a、BSEL1aを受けてデコードし、出力信号BSIG0a〜BSIG3aのいずれかを活性化する。NOR回路86〜92は、外部から行または列アドレスが入力されるときには、ストローブ信号/ASの活性化に応じてフューズ選択信号BSIG0〜BSIG3をすべて活性化し、ストローブ信号/ASが非活性化されているときは、外部から与えられるフューズ選択アドレス信号BSELに対応してデコードされた信号BSIG0a〜BSIG3aをフューズ選択信号BSIG0〜BSIG3として出力する。

【0056】

図5は、図2に示した置換アドレス設定回路46の構成を示す回路図である。図5を参照して、置換アドレス設定回路46は、アドレス信号A0に対応して設けられ、フューズ選択信号BSIG0が活性化されたときに高電圧BVによって内部にアドレス情報がプログラムされる設定部112と、アドレス/A0に対応して設けられフューズ選択信号BSIG0が活性化されたときに高電圧BVによって内部にアドレス情報が設定される設定部110と、アドレス信号A1に対応して設けられフューズ選択信号BSIG0が活性化されたときに高電圧BVによって内部にアドレス情報が設定される設定部108と、アドレス信号/A1に対応して設けられフューズ選択信号BSIG0が活性化されたときに高電圧BVによって内部にアドレス情報が設定される設定部106と、電源電位Vccが与えられる電源ノードとノードN104との間に接続される抵抗102と、ノードN104にゲートが接続されスペアセレクト信号SPSEL0をスペアアドレスデコーダ54に伝達するNチャネルMOSトランジスタ104とを含む。

【0057】

設定部112は、アドレス信号A0によって活性化され高電圧BVを伝達するNチャネルMOSトランジスタ112aと、フューズ選択信号BSIG0によって活性化され通常動作時には電源電位Vccを伝達し置換情報設定時にはNチャネルMOSトランジスタ112aによって伝達される高電圧BVをノードN112に伝達するNチャネルMOSトランジスタ112bと、ノードN112と接地ノードとの間に接続されるアンチフューズ112dと、ノードN104と接地ノードとの間に直列に接続されるNチャネルMOSトランジスタ112c、112eとを含む。

【0058】

NチャネルMOSトランジスタ112cのゲートはノードN112に接続され、NチャネルMOSトランジスタ112eのゲートにはアドレス信号A0が与えられる。

【0059】

設定部110は、アドレス信号/A0によって活性化され高電圧BVを伝達するNチャネルMOSトランジスタ110aと、フューズ選択信号BSIG0によって活性化され通常動作時には電源電位Vccを伝達し置換情報設定時にはNチャネルMOSトランジスタ110aによって伝達される高電圧BVをノードN110に伝達するNチャネルMOSトランジスタ110bと、ノードN110と接地ノードとの間に接続されるアンチフューズ110dと、ノードN104と接地ノードとの間に直列に接続されるNチャネルMOSトランジスタ110c、110eとを含む。

【0060】

NチャネルMOSトランジスタ110cのゲートはノードN110に接続され、NチャネルMOSトランジスタ110eのゲートにはアドレス信号/A0が与えられる。

【0061】

設定部108は、アドレス信号A1によって活性化され高電圧BVを伝達するNチャネルMOSトランジスタ108aと、フューズ選択信号BSIG0によって活性化され通常動作時には電源電位Vccを伝達し置換情報設定時にはNチャネルMOSトランジスタ108aによって伝達される高電圧BVをノードN108に伝達するNチャネルMOSトランジスタ108bと、ノードN108と接地ノードとの間に接続されるアンチフューズ108dと、ノードN104と接地ノードとの間に直列に接続されるNチャネルMOSトランジスタ108c、108eとを含む。

【0062】

NチャネルMOSトランジスタ108cのゲートはノードN108に接続され、NチャネルMOSトランジスタ108eのゲートにはアドレス信号A1が与えられる。

【0063】

設定部106は、アドレス信号/A1によって活性化され高電圧BVを伝達するNチャネルMOSトランジスタ106aと、フューズ選択信号BSIG0によって活性化され通常動作時には電源電位Vccを伝達し置換情報設定時にはNチャネルMOSトランジスタ106aによって伝達される高電圧BVをノードN106に伝達するNチャネルMOSトランジスタ106bと、ノードN106と接地ノードとの間に接続されるアンチフューズ106dと、ノードN104と接地ノードとの間に直列に接続されるNチャネルMOSトランジスタ106c、106eとを含む。

【0064】

NチャネルMOSトランジスタ106cのゲートはノードN106に接続され、NチャネルMOSトランジスタ106eのゲートにはアドレス信号/A1が与えられる。

【0065】

フューズがブローされていない場合は、フューズ選択信号BSIG0がHレベルとなり、設定部106〜112が選択される。応じてNチャネルMOSトランジスタ106b、108b、110b、112bが導通状態になると、電源電位VccがノードN106、N108、N110、N112に与えられるため、応じてNチャネルMOSトランジスタ106c、108c、110c、112cはすべて導通状態となる。

【0066】

そして、NチャネルMOSトランジスタ106e、108e、110e、112eのいずれかは必ずアドレス情報に応じて導通状態となるため、ノードN104の電位は接地状態となり、その結果NチャネルMOSトランジスタ104は非導通状態となり、スペアセレクト信号SPSEL0はスペアアドレスデコーダ54には出力されない。つまりアンチフューズをブローする前は、スペアデコーダ54は使用されない。これに伴い、図2におけるデコーダ非活性化回路48からの非活性化信号も出力されないため、メインアドレスデコーダ50はアドレス信号に応じてメインメモリセル52を選択する。

【0067】

置換アドレスを記憶させる際には、複数本あるアンチフューズを選択的に高電圧で切断する。例として、置換したいメインメモリセルアドレス2番地(A0=0,A1=1)を、フューズ選択信号BSIG0を用いてスペアメモリセルに記憶させる場合を説明する。図5において、アドレス信号A0,/A0,A1,/A1はアドレス2番地を選択する場合にはそれぞれ(L,H,H,L)のレベルになる。すると、NチャネルMOSトランジスタ112e,110e,108e,106eはそれぞれ非導通,導通,導通,非導通の状態となる。同様に、NチャネルMOSトランジスタ112a,110a,108a,106aはそれぞれ非導通,導通,導通,非導通の状態となる。

【0068】

一方、フューズ選択アドレス信号BSELは、このため、BSEL0=0,BSEL1=0に設定すると、図4に示したフューズ選択デコーダによってデコードされた結果、フューズ選択信号BSIG0が選択され活性化状態となり、それが図5に示す置換アドレス設定回路46に入力される。

【0069】

応じて、NチャネルMOSトランジスタ112b、110b、108b、106bはすべて導通状態となる。

【0070】

このときに、アンチフューズをブローするに足る高電圧(たとえば6ボルト)を高電圧BVとして印加することで、先に述べた導通状態となっているNチャネルMOSトランジスタ110a,108aおよび110b,108bを介してアンチフューズ110d,108dに高電圧BVが印加される。このためアンチフューズ110d,108dはブローされ導通状態となる。

【0071】

すると、ノードN110、ノードN108は常にLレベルとなるため、NチャネルMOSトランジスタ110c、108cは導通することはなくなる。このことで、置換アドレスを記憶させたことになる。

【0072】

以後、この半導体記憶装置に対しては、先に説明した置換したアドレス2番地(A0=0,A1=1)が印加されたときのみ、ノードN104は接地電位に結合されずHレベルとなるため、スペアアドレスデコーダ54にスペアセレクト信号SPSEL0が印加されることになる。このときには対応するスペアメモリセルが選択されて図2に示したデコーダ非活性化回路48の働きによりメインアドレスデコーダ50はアドレス信号を受付けなくなるのである。

【0073】

図5に示したような置換アドレス設定回路46は、レーザによるヒューズの切断が必要ないため、外部から端子に与える電気信号のみで置換アドレスの設定を行なうことが可能である。したがって、ウエハ状態での置換実施後にパッケージに封止された後にも再度置換を行なうことができる。

【0074】

なお、図5は、フューズ選択信号BSIG0に対応して設けられる設定部についてのみ示したが、フューズ選択信号BSIG1〜BSIG3に対応して同様な構成の設定部が設けられる。

【0075】

図6は、実施の形態1において第1回目のフューズブロー時にフューズ選択アドレス信号BSEL0が入力されるとどのフューズ選択信号BSIGが活性化されるかを示した図である。

【0076】

図6を参照して、フューズ選択アドレス信号BSEL0が(BSEL1,BSEL0)=(0,0)の場合には、フューズ選択信号BSIG0が活性化され他のフューズ選択信号は非活性化状態にあることを示す。また、(BSEL1,BSEL0)=(0,1)の場合には、フューズ選択信号BSIG1が活性化され他のフューズ選択信号は非活性化される。(BSEL1,BSEL0)=(1,0)の場合には、フューズ選択信号BSIG2が活性化され他のフューズ選択信号は非活性化される。(BSEL1,BSEL0)=(1,1)の場合には、フューズ選択信号BSIG3が活性化され他のフューズ選択信号は非活性化される。

【0077】

図7は、第2回目の置換が実施される際のフューズ選択アドレス信号BSELとフューズ選択信号との対応を示した図である。

【0078】

第2回目の置換が実施される際には、図3に示したインバータ70によってフューズ選択アドレス信号が反転されその後図2に示したフューズ選択回路44によってデコードが実施されるため(BSEL1,BSEL0)=(0,0)の場合はフューズ選択信号BSIG3が活性化される。

【0079】

(BSEL1,BSEL0)=(0,1)の場合には、フューズ選択信号BSIG2が活性化される。(BSEL1,BSEL0)=(1,0)の場合には、フューズ選択信号BSIG1が活性化される。(BSEL1,BSEL0)=(1,1)の場合には、フューズ選択信号BSIG0が活性化される。

【0080】

つまり、図6、図7でわかるように、第1回目の救済時のフューズ選択信号はフューズ選択アドレス信号が増加するに従ってBSIG0、BSIG1、BSIG2、BSIG3の順番で活性化される。そして、2回目の救済時においては、この順番は反転しフューズ選択信号BSIG3、BSIG2、BSIG1、BSIG0の順番で活性化されるようになる。

【0081】

このことで、2回目の救済の場合には、未使用のスペアメモリセルを優先的に使用して置換することが可能である。なお、1回目の救済ですべてのスペアを使用した場合や、2回目に使用するスペアの本数が残りのスペアの本数よりも多いケースがあるが、これはもともと2回目の置換では救済できない場合なので、アドレスが多重選択される等で救済できないのもやむを得ない。この場合は後工程における検査において不良と判定され、その半導体記憶装置は出荷の対象から除外される。

【0082】

このような構成にすることにより、1回目に置換した冗長回路のスペアの使用情報を半導体記憶装置内または外部の記憶装置等に記憶させておかなくても、2回目の置換が必要な場合になったときにスペアの多重選択により救済可能な半導体記憶装置を不良品にしてしまうということはなくなる。

【0083】

[実施の形態1の変形例]

図8は、実施の形態1の変形例における相補アドレス発生回路42aの構成を示す回路図である。

【0084】

図8を参照して、相補アドレス発生回路42aは、図3に示した相補アドレス発生回路42の構成においてアンチフューズ66に代えてフューズ素子66aを含む。他の部分は図3に示した相補アドレス発生回路42と同様の構成を有するため説明は繰返さない。

【0085】

フューズ素子66aは、ブローされる前は抵抗体である。ブロー時に高電圧が電極間に印加されると、フューズ素子66aは電流が流れ、加熱により切断される。抵抗67をフューズ素子66aに比して十分抵抗を高く設定しておけば、ノードN1はブロー前はLレベル、ブロー後はHレベルになるので、実施の形態1の場合と同様ブロー前後で信号BSEL0aの極性は反転する。

【0086】

このようにしても、実施の形態1と同様、パッケージング後にさらにスペアと置換する第2回目の置換を実施する場合においても、1回目に使用したスペアとの多重選択により、救済可能な半導体記憶装置を不良にしてしまうということはなくなる。

【0087】

[実施の形態2]

図9は、実施の形態2における置換制御回路24aの構成を示すブロック図である。

【0088】

図9を参照して、置換制御回路24aは、フューズ選択回路44、相補アドレス発生回路42に代えて、フューズ選択回路44aとその後段に相補アドレス発生回路202とを備える点が図2に示した置換制御回路24と異なる。他の構成は図2に示した置換制御回路24と同様であるので説明は繰返さない。

【0089】

図10は、図9におけるフューズ選択回路44aの構成を示す回路図である。

図10を参照して、フューズ選択回路44aは、図4に示したフューズ選択回路44の構成において、フューズ選択デコーダがフューズ選択信号BSEL0、BSEL1を受けて、OR回路86、88、90、92が信号BSIG0b、BSIG1b、BSIG2b、BSIG3bを出力する点が異なるが、他の構成は同様であるので説明は繰返さない。

【0090】

図11は、図9における相補アドレス発生回路202の構成を示す回路図である。

【0091】

図11を参照して、相補アドレス発生回路202は、識別信号SIDによって活性化されて高電圧BVをノードN212に伝達するNチャネルMOSトランジスタ212と、ノードN212と接地ノードとの間に接続されるアンチフューズ214と、電源電位Vccが与えられる電源ノードとノードN212との間に接続される抵抗213とを備える。第1回目のフューズブロー終了後に識別信号SIDが活性化されると、高電圧BVがノードN212に印加されるためアンチフューズ214はブローされ非導通状態から導通状態になりその後ノードN212がLになる。

【0092】

相補アドレス発生回路202は、さらに、ゲートがノードN212に接続されノードN216とノードN217との間に接続されるNチャネルMOSトランジスタ216と、ゲートがノードN212に接続されノードN216とノードN229との間に接続されるPチャネルMOSトランジスタ218と、ゲートにノードN212が接続されノードN220とノードN221との間に接続されるNチャネルMOSトランジスタ220と、ゲートにノードN212が接続されノードN220とノードN225との間に接続されるPチャネルMOSトランジスタ222と、ノードN212にゲートが接続されノードN224とノードN225との間に接続されるNチャネルMOSトランジスタ224と、ノードN212にゲートが接続されノードN224とノードN221との間に接続されるPチャネルMOSトランジスタ226と、ゲートがノードN212に接続されノードN228とノードN229との間に接続されるNチャネルMOSトランジスタ228と、ノードN212にゲートが接続されノードN228とノードN217との間に接続されるPチャネルMOSトランジスタ230とを含む。

【0093】

ノードN216、N220、N224、N228には図9に示したフューズ選択回路44aの出力であるフューズ選択信号BSIG0b、BSIG1b、BSIG2b、BSIG3bがそれぞれ与えられる。また、ノードN217、N221、N225、N229からは図9に示した置換アドレス設定回路46に対してそれぞれフューズ選択信号BSIG0、BSIG1、BSIG2、BSIG3が出力される。

【0094】

実施の形態2においては、1回目の置換と2回目の置換の識別はアンチフューズ214の状態によって判別が可能となる。まず1回目の置換の場合は、アンチフューズ214はブローされていないため、ノードN212の電位は抵抗213を介して電源電位VccにされるためNチャネルMOSトランジスタ216、220、224、228はすべて導通状態となり、一方PチャネルMOSトランジスタ218、222、226、230は非導通状態となる。したがって、図9におけるフューズ選択回路44aの出力である信号BSIG0b〜BSIG3bは、そのままBSIG0〜BSIG3として置換アドレス設定回路46に与えられる。このときの対応関係は図6に示した場合と同様となる。一方、第1回目の救済に必要な置換処理がすべて終わった後には、外部試験装置または図示しない内部回路において識別信号SIGが活性化されて応じてアンチフューズをブローするに足る高電圧たとえば6ボルトが高電圧BVとしてアンチフューズの一方の電極に与えられる。応じてアンチフューズ214はブローされて導通状態となりノードN212の電位は以後Lレベルとなる。

【0095】

2回目の置換の際は、ノードN212の電位がLレベルであるため、NチャネルMOSトランジスタ216、220、224、228は非導通状態となり、一方PチャネルMOSトランジスタ218、222、226、230が導通状態となる。すなわち、フューズ選択信号BSIGの出力先が変更され実施の形態1における図7に示した対応関係と同様の出力がされるようになる。

【0096】

実施の形態2に示した冗長回路付半導体記憶装置においても、パッケージング後にさらにスペアと置換する第2回目の置換を実施する場合においても、1回目に使用したスペアとの多重選択により、救済可能な半導体記憶装置を不良にしてしまうということはなくなる。

【0097】

なお、図11においてはNチャネルMOSトランジスタ216、220、224、228およびPチャネルMOSトランジスタ218、222、226、230による接続切換回路によりフューズ選択信号の順序を入れ替えたが、論理回路やROM等によって同様に対応関係を変更することも可能である。

【0098】

[実施の形態2の変形例]

図12は、実施の形態2の変形例における相補アドレス発生回路202aの構成を示す回路図である。

【0099】

図12を参照して、相補アドレス発生回路202aは、図11に示した相補アドレス発生回路202の構成においてアンチフューズ214に代えてフューズ素子214aを含む。他の部分は図11に示した相補アドレス発生回路202と同様の構成を有するため説明は繰返さない。

【0100】

フューズ素子214aは、ブローされる前は抵抗体である。ブロー時に高電圧が電極間に印加されると、フューズ素子214aには電流が流れ、加熱により切断される。抵抗213をフューズ素子214aに比して十分抵抗を高く設定しておけば、ノードN212はブロー前はLレベル、ブロー後はHレベルになるので、実施の形態2の場合と同様ブロー前後で信号BSIG0の順番は入れ替わる。

【0101】

このようにしても、実施の形態2と同様、パッケージング後にさらにスペアと置換する第2回目の置換を実施する場合においても、1回目に使用したスペアとの多重選択により、救済可能な半導体記憶装置を不良にしてしまうということはなくなる。

【0102】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0103】

【発明の効果】

請求項1,5,9に記載の半導体記憶装置は、スペア置換工程を再度実施する場合において、使用するスペアが重複しないようなスペアアドレスの選択を優先的に行なうことができる。

【0104】

請求項2に記載の半導体記憶装置は、請求項1に記載の半導体記憶装置が奏する効果に加えて、2度目のスペア置換工程において、使用するスペアが重複しないようなスペアアドレスの変換を実施することができる。

【0105】

請求項3,4に記載の半導体記憶装置は、請求項2に記載の半導体記憶装置が奏する効果に加えて、1度目のスペア置換工程が施されたことを半導体記憶装置の内部に記録しておくことが可能である。

【0106】

請求項6に記載の半導体記憶装置は、請求項5に記載の半導体記憶装置が奏する効果に加えて、2度目のスペア置換工程において、使用するスペアが重複しないようなスペア選択信号の入換を実施することができる。

【0107】

請求項7,8に記載の半導体記憶装置は、請求項6に記載の半導体記憶装置が奏する効果に加えて、1度目のスペア置換工程が施されたことを半導体記憶装置の内部に記録しておくことが可能である。

【0108】

請求項9に記載の半導体記憶装置は、さらに、パッケージ状態においても、再度スペア置換工程を実施することが可能である。

【図面の簡単な説明】

【図1】 本発明の実施の形態1の半導体記憶装置1の構成を示す概略ブロック図である。

【図2】 図1に示した行および列置換制御回路24の構成を説明するためのブロック図である。

【図3】 図2における相補アドレス発生回路42の構成を示す回路図である。

【図4】 図2におけるフューズ選択回路44の構成を示す回路図である。

【図5】 図2に示した置換アドレス設定回路46の構成を示す回路図である。

【図6】 実施の形態1において第1回目のフューズブロー時にフューズ選択アドレス信号BSEL0が入力されるとどのフューズ選択信号BSIGが活性化されるかを示した図である。

【図7】 第2回目の置換が実施される際のフューズ選択アドレス信号BSELとフューズ選択信号との対応を示した図である。

【図8】 図3に示した相補アドレス発生回路42の他の構成例である、相補アドレス発生回路42aの構成を示す回路図である。

【図9】 実施の形態2における置換制御回路24aの構成を示すブロック図である。

【図10】 図9におけるフューズ選択回路44aの構成を示す回路図である。

【図11】 図9における相補アドレス発生回路202の構成を示す回路図である。

【図12】 実施の形態2の変形例における相補アドレス発生回路202aの構成を示す回路図である。

【図13】 従来の冗長回路を搭載した半導体記憶装置の内部構成を示す図であり、主としてスペアがどのようにして選択されるかを示したブロック図である。

【図14】 スペアの選択方法を説明するための簡略的なブロック図である。

【符号の説明】

1 半導体記憶装置、18 ゲート回路、20 データ入力バッファ、22 クロック発生回路、24 行および列置換制御回路、26 行デコーダ、27 スペア行デコーダ、28 列デコーダ、29 スペア列デコーダ、30 センスアンプ+入出力制御回路、31 スペア列、32 メモリセルアレイ、33 スペア行、34 データ出力バッファ、42 相補アドレス発生回路、44 フューズ選択回路、46 置換アドレス設定回路、48 デコーダ非活性化回路、50 メインアドレスデコーダ、52 メインメモリセル、54 スペアアドレスデコーダ、56 スペアメモリセル、62,68,104,106a〜112a,106b〜112b,106c〜112c,106e〜112e,216,220,224,228 NチャネルMOSトランジスタ、64,218,222,226,230 PチャネルMOSトランジスタ、66,106d〜112d,214 アンチフューズ、67,102,213 抵抗、70,84 インバータ、86〜92 OR回路、106〜112 設定回路、202 相補アドレス発生回路。

Claims (9)

- 正規メモリセル領域を備え、

前記正規メモリセル領域は、

複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、

前記正規メモリセル領域に対応して設けられ、アドレス信号を受けて前記正規メモリセル群のいずれかを選択するメインアドレスデコーダと、

スペアメモリセル領域とをさらに備え、

前記スペアメモリセル領域は、

前記正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、

前記スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けて前記スペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、

前記スペアメモリセル群と置換する前記正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、前記アドレス信号が前記置換アドレスと一致するときは前記メインアドレスデコーダを非活性化し、前記スペアアドレス信号を出力する置換制御回路とをさらに備え、

前記置換制御回路は、

前記複数のスペアメモリセル群にそれぞれ対応して設けられ、前記置換アドレスデータを保持する複数のアドレス設定部と、

設定部選択信号に応じて前記複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、

前記設定部選択回路は、

前記正規メモリセル群を前記スペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、前記設定部選択信号に対する前記複数のアドレス設定部の使用優先順を前記保持回路の保持情報に応じて決定し、

前記設定部選択回路は、

前記設定部選択信号を受けて前記保持回路の保持情報が置換未実施に対応するときはそのまま出力し、前記保持回路の保持情報が置換実施済に対応するときは前記設定部選択信号の各信号ビットを反転させて出力する変換回路と、

前記変換回路の出力を受けてデコードし前記複数のアドレス設定部のいずれかを選択する設定部選択デコーダとをさらに有する、半導体記憶装置。 - 前記変換回路は、

前記設定部選択信号の各信号ビットを反転させる相補アドレス発生回路と、

前記設定部選択信号と前記相補アドレス発生回路の出力とを受けて前記保持回路の保持情報に応じていずれか一方を選択して前記設定部選択デコーダに出力する選択回路とを有する、請求項1に記載の半導体記憶装置。 - 前記相補アドレス発生回路は、

前記設定部選択信号の各信号ビットをそれぞれ入力に受ける複数のインバータを有し、

前記保持回路は、

前記置換動作の終了時に電極間に所定の高電圧が与えられ電極間が導通状態となり前記保持回路の保持情報を保持するアンチフューズを有し、

前記選択回路は、前記アンチフューズの電極間の導通状態に応じて前記設定部選択信号と前記相補アドレス発生回路の出力のいずれか一方を選択して出力する、請求項2に記載の半導体記憶装置。 - 前記相補アドレス発生回路は、

前記設定部選択信号の各信号ビットをそれぞれ入力に受ける複数のインバータを有し、

前記保持回路は、

前記置換動作の終了時に電極間に所定の高電圧が与えられ電極間が非導通状態となり前記保持回路の保持情報を保持する電気フューズを有し、

前記選択回路は、前記電気フューズの電極間の導通状態に応じて前記設定部選択信号と前記相補アドレス発生回路の出力のいずれか一方を選択して出力する、請求項2に記載の半導体記憶装置。 - 正規メモリセル領域を備え、

前記正規メモリセル領域は、

複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、

前記正規メモリセル領域に対応して設けられ、アドレス信号を受けて前記正規メモリセル群のいずれかを選択するメインアドレスデコーダと、

スペアメモリセル領域とをさらに備え、

前記スペアメモリセル領域は、

前記正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、

前記スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けて前記スペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、

前記スペアメモリセル群と置換する前記正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、前記アドレス信号が前記置換アドレスと一致するときは前記メインアドレスデコーダを非活性化し、前記スペアアドレス信号を出力する置換制御回路とをさらに備え、

前記置換制御回路は、

前記複数のスペアメモリセル群にそれぞれ対応して設けられ、前記置換アドレスデータを保持する複数のアドレス設定部と、

設定部選択信号に応じて前記複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、

前記設定部選択回路は、

前記正規メモリセル群を前記スペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、前記設定部選択信号に対する前記複数のアドレス設定部の使用優先順を前記保持回路の保持情報に応じて決定し、

前記設定部選択回路は、

前記設定部選択信号を受けてデコードする設定部選択デコーダと、

前記保持回路の保持情報が置換未実施に対応するときはそのまま出力し、前記保持回路の保持情報が置換実施済に対応するときは前記設定部選択デコーダの出力信号の各信号ビットの順番を入れ替えて出力する順番入換回路とをさらに含む、半導体記憶装置。 - 前記順番入換回路は、前記設定部選択デコーダの出力信号がnビットの信号であるときに、上位から数えて第kビット目が活性化されると前記順番入換回路のnビットの出力信号の下位から数えて第kビット目を活性化させる動作と、上位から数えて第kビット目が活性化されると前記順番入換回路のnビットの出力信号の上位から数えて第kビット目を活性化させる動作とのいずれかを前記保持回路の保持情報に応じて選択して実行する、請求項5に記載の半導体記憶装置(nは自然数、kはn以下の自然数)。

- 前記保持回路は、

前記置換動作の終了時に電極間に所定の高電圧が与えられ電極間が導通状態となり前記保持回路の保持情報を保持するアンチフューズを有する、請求項6に記載の半導体記憶装置。 - 前記保持回路は、

前記置換動作の終了時に電極間に所定の高電圧が与えられ電極間が非導通状態となり前記保持回路の保持情報を保持する電気フューズを有する、請求項6に記載の半導体記憶装置。 - 正規メモリセル領域を備え、

前記正規メモリセル領域は、

複数の正規メモリセルを各々が有する複数の正規メモリセル群を含み、

前記正規メモリセル領域に対応して設けられ、アドレス信号を受けて前記正規メモリセル群のいずれかを選択するメインアドレスデコーダと、

スペアメモリセル領域とをさらに備え、

前記スペアメモリセル領域は、

前記正規メモリセル群と置換して使用可能な、複数のスペアメモリセルを各々が有する複数のスペアメモリセル群を含み、

前記スペアメモリセル領域に対応して設けられ、スペアアドレス信号を受けて前記スペアメモリセル群のいずれかを選択するスペアアドレスデコーダと、

前記スペアメモリセル群と置換する前記正規メモリセル群の置換アドレスに対応する置換アドレスデータを保持し、前記アドレス信号が前記置換アドレスと一致するときは前記メインアドレスデコーダを非活性化し、前記スペアアドレス信号を出力する置換制御回路とをさらに備え、

前記置換制御回路は、

前記複数のスペアメモリセル群にそれぞれ対応して設けられ、前記置換アドレスデータを保持する複数のアドレス設定部と、

設定部選択信号に応じて前記複数のアドレス設定部のいずれかを選択する、設定部選択回路とを含み、

前記設定部選択回路は、

前記正規メモリセル群を前記スペアメモリセル群に置換する置換動作が実施されたことを不揮発的に保持する保持回路を有し、前記設定部選択信号に対する前記複数のアドレス設定部の使用優先順を前記保持回路の保持情報に応じて決定し、

前記保持回路の保持情報は、ウエハ状態において前記置換動作が終了したときに所定の初期状態から反転され、

パッケージ状態において前記置換動作を再度実施するために前記置換アドレスデータを入力する第1の端子群と、

パッケージ状態において前記置換動作を再度実施するために前記設定部選択信号を入力する第2の端子群とをさらに備え、

各前記アドレス設定部は、

前記設定部選択信号および前記置換アドレスデータに応じて選択され、前記置換アドレスデータに対応する情報を保持する複数のアドレスビット設定部を有する、半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18878799A JP4115045B2 (ja) | 1999-07-02 | 1999-07-02 | 半導体記憶装置 |

| US09/478,335 US6178125B1 (en) | 1999-07-02 | 2000-01-06 | Semiconductor memory device preventing repeated use of spare memory cell and repairable by cell substitution up to two times |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18878799A JP4115045B2 (ja) | 1999-07-02 | 1999-07-02 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001023393A JP2001023393A (ja) | 2001-01-26 |

| JP2001023393A5 JP2001023393A5 (ja) | 2005-11-04 |

| JP4115045B2 true JP4115045B2 (ja) | 2008-07-09 |

Family

ID=16229798

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18878799A Expired - Fee Related JP4115045B2 (ja) | 1999-07-02 | 1999-07-02 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6178125B1 (ja) |

| JP (1) | JP4115045B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3821637B2 (ja) * | 2000-08-24 | 2006-09-13 | 株式会社東芝 | 半導体集積回路装置 |

| JP2002073129A (ja) * | 2000-08-30 | 2002-03-12 | Mitsubishi Electric Corp | レーザトリミング用プログラム作成装置、方法、記録媒体およびレーザトリミング装置 |

| JP2003077291A (ja) * | 2001-09-03 | 2003-03-14 | Mitsubishi Electric Corp | 半導体集積回路装置 |

| KR100447224B1 (ko) * | 2001-09-20 | 2004-09-04 | 주식회사 하이닉스반도체 | 비휘발성 강유전체 메모리 장치의 칼럼 리페어 회로 |

| JP2004047017A (ja) * | 2002-07-15 | 2004-02-12 | Renesas Technology Corp | 救済回路付き半導体記憶装置 |

| JP2004220722A (ja) * | 2003-01-16 | 2004-08-05 | Renesas Technology Corp | 半導体記憶装置 |

| US6982911B2 (en) * | 2004-03-18 | 2006-01-03 | Infineon Technologies Ag | Memory device with common row interface |

| JP2009245511A (ja) | 2008-03-31 | 2009-10-22 | Nec Electronics Corp | 半導体記憶装置 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4959564A (en) * | 1989-01-06 | 1990-09-25 | Sgs-Thomson Microelectronics, Inc. | Sense amplifier power down circuitry for programmable logic device |

| US5367207A (en) | 1990-12-04 | 1994-11-22 | Xilinx, Inc. | Structure and method for programming antifuses in an integrated circuit array |

| JPH0554692A (ja) | 1991-08-22 | 1993-03-05 | Mitsubishi Electric Corp | 半導体記憶装置 |

-

1999

- 1999-07-02 JP JP18878799A patent/JP4115045B2/ja not_active Expired - Fee Related

-

2000

- 2000-01-06 US US09/478,335 patent/US6178125B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6178125B1 (en) | 2001-01-23 |

| JP2001023393A (ja) | 2001-01-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20180075922A1 (en) | Semiconductor device including fuse circuit | |

| US6940765B2 (en) | Repair apparatus and method for semiconductor memory device to be selectively programmed for wafer-level test or post package test | |

| US6704228B2 (en) | Semiconductor memory device post-repair circuit and method | |

| EP0591870B1 (en) | Improved fuse-programmable control circuit | |

| US4556975A (en) | Programmable redundancy circuit | |

| KR910001533B1 (ko) | 휴즈회로와 그내의 휴즈상태 검출회로를 갖는 반도체장치 | |

| JPH08235892A (ja) | 半導体メモリ装置の欠陥セル救済方法とその回路 | |

| JP2001273791A (ja) | 集積半導体メモリ | |

| US7146585B2 (en) | Programmable element latch circuit | |

| JPS59140700A (ja) | 集積回路メモリ用のデコード装置 | |

| US6208570B1 (en) | Redundancy test method for a semiconductor memory | |

| JP2002074980A (ja) | 半導体集積回路装置 | |

| US20050281076A1 (en) | Memory circuit comprising redundant memory areas | |

| JP4115045B2 (ja) | 半導体記憶装置 | |

| JP2003007081A (ja) | 半導体集積回路装置 | |

| US5764574A (en) | Method and apparatus for back-end repair of multi-chip modules | |

| JP3978591B2 (ja) | 半導体メモリ装置のカラムリペア回路及びカラムリペア方法 | |

| US7359264B2 (en) | Semiconductor memory device | |

| JP3673637B2 (ja) | 冗長回路を備えた半導体メモリ装置 | |

| US8116163B2 (en) | Semiconductor memory device | |

| US6275443B1 (en) | Latched row or column select enable driver | |

| US6373770B1 (en) | Integrated circuit memory devices with configurable block decoder circuits | |

| KR20040017690A (ko) | 불량 셀 구제 기능을 갖는 롬 메모리 장치 및 불량 셀구제 방법 | |

| US20080068905A1 (en) | Reparable semiconductor memory device | |

| KR100649970B1 (ko) | 리던던시 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050804 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050804 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080313 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080408 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080415 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110425 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120425 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130425 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140425 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |