JP4089340B2 - 電子装置、電気光学装置及び電子機器 - Google Patents

電子装置、電気光学装置及び電子機器 Download PDFInfo

- Publication number

- JP4089340B2 JP4089340B2 JP2002223166A JP2002223166A JP4089340B2 JP 4089340 B2 JP4089340 B2 JP 4089340B2 JP 2002223166 A JP2002223166 A JP 2002223166A JP 2002223166 A JP2002223166 A JP 2002223166A JP 4089340 B2 JP4089340 B2 JP 4089340B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- electro

- optical device

- data line

- conversion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000006243 chemical reaction Methods 0.000 claims description 182

- 238000005401 electroluminescence Methods 0.000 claims description 45

- 239000000758 substrate Substances 0.000 claims description 35

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 23

- 229910052710 silicon Inorganic materials 0.000 claims description 23

- 239000010703 silicon Substances 0.000 claims description 23

- 239000010409 thin film Substances 0.000 claims description 20

- 239000011368 organic material Substances 0.000 claims description 11

- 230000003287 optical effect Effects 0.000 claims description 3

- 230000005611 electricity Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 23

- 230000000694 effects Effects 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 230000014509 gene expression Effects 0.000 description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 3

- 230000005415 magnetization Effects 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 2

- 230000005294 ferromagnetic effect Effects 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 239000003086 colorant Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000005291 magnetic effect Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3291—Details of drivers for data electrodes in which the data driver supplies a variable data voltage for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、電流により駆動される電流駆動素子を備えた電子装置、電子光学装置及び電子機器に関する。

【0002】

【従来の技術】

近年、液晶を用いた表示装置(以下、ディスプレイという)は薄型表示装置として普及しつつある。このタイプのディスプレイは、CRTのディスプレイに比べて低消費電力で省スペースである。したがって、このようなディスプレイの利点を活かし、より低消費電力で、より省スペースのディスプレイを製造することが重要となる。

【0003】

また、このようなタイプの表示装置に、液晶ではなく電流駆動型発光素子を用いて表示を行うものがある。この電流駆動型発光素子は、液晶とは異なり、電流が供給されることにより発光する自発光素子であるため、バックライトが不要であり、低電力化という市場の要求に対応することができる。さらに高い視野角、高いコントラスト比等の面で優れた表示性能を有している。このような電流駆動型発光素子の中でもエレクトロルミネッセンス素子(Electroluminescent devices)は、大面積化、高精細化、フルカラー化を図ることができるので、ディスプレイには特に適している。

【0004】

このエレクトロルミネッセンス素子の中でも、有機エレクトロルミネッセンス素子(Organic Electroluminescent devices)は、高い量子効率のため注目されている。

【0005】

このような、有機エレクトロルミネッセンス素子を用いて表示を行う表示装置としては、例えば図21に示すような表示装置が提案されている。すなわち、この表示装置は、データ線Xと走査線Yとの交点に対応して画素回路が配置され、データドライバ51によってデータ線を駆動し、走査ドライバ52によって走査線Yを駆動するようになっている。

【0006】

前記画素回路55は、図22に示すように、例えば、2つのトランジスタ61,62と、データ保持用の容量素子63と、有機エレクトロルミネッセンス素子64とから構成されている。そして、走査線Yによってトランジスタ61のスイッチング動作を行ってデータ線Xから供給されたデータ信号を電荷として容量素子63に保持し、この容量素子63で保持された電荷によりトランジスタ62が導通状態となり、データ信号に対応する電流量が有機エレクトロルミネッセンス素子64に供給され、有機エレクトロルミネッセンス素子64が発光する。

【0007】

【発明が解決しようとする課題】

ところで、例えば、有機エレクトロルミネッセンス素子などのように電流駆動型素子は電圧よりも電流で制御するほうがより容易である。これは、有機エレクトロルミネッセンス素子は電流量に対して輝度が決定されるので、データ信号として電流を用いたほうがより制御が正確であるためである。

【0008】

そこで、本発明の重要な目的の一つは、データ信号に対する電流量をデータ線あるいは導通線に出力することにより、電流駆動素子を流れる電流量が決定される電子装置、電気光学装置及び電子機器を提供することである。

【0009】

【課題を解決するための手段】

上記目標を達成するために、本発明の第1の電子装置は、通電線と、当該通電線に接続された複数の単位回路と、前記通電線に接続され且つ当該通電線に流れる電流の電流量に基づいてゲート電圧が設定されるトランジスタと、を備えることを特徴としている。係る電子装置の例として、例えば、MRAM(Magnetoresistive RAM)セル、有機エレクトロルミネッセンス素子、またはレーザーダイオードを備えた電子装置を挙げることができる。

【0010】

また、第2の電子装置は、上記の電子装置において、前記トランジスタのゲート電極は、当該トランジスタのソース端又はドレイン端と接続されていることを特徴としている。本明細書を通して、「前記トランジスタのゲート電極とソース端又はドレイン端が接続されている」とは、ソース端又はドレイン端とゲート電極との間にトランジスタ、ダイオードなどの抵抗素子などが接続されている場合をも含んでいる。

【0011】

本発明の第1及び第2の電子装置では、通電線に接続されたトランジスタのゲート電圧は、この通電線に流れる電流量に基づいて設定されることとなる。

また、本発明の第3の電子装置は、通電線と、当該通電線に接続された複数の単位回路と、前記通電線に接続され且つ当該通電線に流れる電流の電流量に基づいてゲート電圧が設定される第1のトランジスタと、を備えた電子装置であって、前記単位回路は、前記第1のトランジスタとカレントミラーを構成する第2のトランジスタを有することを特徴としている。

【0012】

また、本発明の第4の電子装置は、上記の電子装置において、前記第1のトランジスタのゲート電極は、当該第1のトランジスタのソース端又はドレイン端と接続されていることを特徴としている。

【0013】

本発明の第3及び第4の電子装置では、通電線に接続された第1のトランジスタのゲート電圧は、この通電線に流れる電流量に基づいて設定され、第1のトランジスタのゲート電圧に基づいて第2のトランジスタに流れる電流量が設定される。

【0014】

本発明の第5の電子装置は、通電線と、当該通電線に接続された複数の単位回路と、前記通電線に接続され、且つ、当該通電線に流れる電流の電流量に基づいてゲート電圧が設定される第1のトランジスタと、を備えた電子装置であって、前記単位回路は、その導電型がp型であって、前記第1のトランジスタとカレントミラーを構成する第2のトランジスタを有することを特徴としている。これによれば、第2のトランジスタに電子素子を接続した電子デバイスを形成するとき、その電子デバイスの特性に基づいて、係る電子装置を容易に形成することができる。

【0015】

また、本発明の第6の電子装置は、上記の電子装置において、前記第1のトランジスタのゲート電極は当該第1のトランジスタのソース端又はドレイン端と接続されていることを特徴としている。

【0016】

本発明の第7の電子装置は、通電線と、当該通電線に接続された複数の単位回路と、前記通電線に接続され、且つ、当該通電線に流れる電流の電流量に基づいてゲート電圧が設定される第1のトランジスタと、を備えた電子装置であって、前記単位回路は、前記第1のトランジスタとカレントミラーを構成する第2のトランジスタを有し、前記第2のトランジスタは、その利得係数を前記通電線に流れる電流の電流量より大きな電流量を生成するように設定したことを特徴としている。これによれば、第2のトランジスタにて生成される電流の電流量を通電線に流れる電流の電流量より大きくすることができる。

【0017】

また、本発明の第8の電子装置は、通電線と、当該通電線に接続された複数の単位回路と、前記通電線に接続され、且つ、当該通電線に流れる電流の電流量に基づいてゲート電圧が設定される第1のトランジスタと、を備えた電子装置であって、前記単位回路は、前記第1のトランジスタとカレントミラーを構成する第2のトランジスタを有し、前記第2のトランジスタは、その利得係数を前記通電線に流れる電流の電流量より小さな電流量を生成するように設定したことを特徴としている。これによれば、第2のトランジスタにて生成される電流の電流量を通電線に流れる電流の電流量より小さくすることができる。

【0018】

また、本発明の第9の電子装置は、上記の電子装置において、前記第1のトランジスタのゲート電極は当該第1のトランジスタのソース端又はドレイン端と接続されていることを特徴としている。

【0019】

また、本発明の第1の電気光学装置は、データ線と、電気光学素子を有し且つ前記データ線に接続される複数の単位回路と、前記データ線に接続され、当該データ線に流れる電流の電流量によりゲート電圧が設定されるトランジスタと、を備えることを特徴としている。

【0020】

また、本発明の第2の電気光学装置は、上記の電気光学装置おいて、走査線をさらに備え、前記複数の単位回路のそれぞれは、前記電気光学素子に電気的に接続された駆動トランジスタと、ゲート電極が前記走査線に接続されたスイッチングトランジスタ、と有し、前記データ線を介してデータ信号が前記複数の単位回路に供給されることを特徴としている。

【0021】

また、本発明の第3の電気光学装置は、上記の電気光学装置において、前記スイッチングトランジスタのソース端又はドレイン端は、前記駆動トランジスタのゲート電極に接続されていることを特徴としている。

【0022】

また、本発明の第4の電気光学装置は、上記の電気光学装置において、前記データ信号は、デジタル−アナログ変換回路で生成されたアナログ量を有する電流であることを特徴としている。

【0023】

また、本発明の第5の電気光学装置は、上記の電気光学装置において、前記トランジスタと前記駆動トランジスタとは、カレントミラーを構成することを特徴としている。

【0024】

また、本発明の第6の電気光学装置は、上記の電気光学装置において、前記データ線に接続される第1の電源の電圧値と、前記電気光学素子と前記駆動トランジスタを介して接続される第2の電源の電圧値とは、所定の比率となるように設定されることを特徴としている。

【0025】

また、本発明の第7の電気光学装置は、上記の電気光学装置において、前記トランジスタは、前記デジタル−アナログ変換回路と前記データ線との間に配置されていることを特徴としている。

【0026】

また、本発明の第8の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記トランジスタとの間に前記データ線が配置されていることを特徴としている。

【0027】

また、本発明の第9の電気光学装置は、上記の電気光学装置において、前記トランジスタと前記デジタル-アナログ変換回路と前記データ線とは同一基体上に形成されていることを特徴としている。

【0028】

また、本発明の第10の電気光学装置は、上記の電気光学装置において、前記データ線と前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴としている。

【0029】

また、本発明の第11の電気光学装置は、上記の電気光学装置において、前記データ線と前記トランジスタとは同一基体上に形成されていることを特徴としている。

【0030】

また、本発明の第12の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記トランジスタとは同一基体上に形成されていることを特徴としている。

【0031】

上記の電気光学装置において「基体」の例としては、ガラス基板、石英基板、またはシリコン基板などを挙げることができる。

また、本発明の第13の電気光学装置は、上記の電気光学装置において、前記トランジスタと前記単位回路に含まれるトランジスタと、は薄膜トランジスタで構成されていることを特徴としている。

【0032】

上記の本発明の第13の電気光学装置においては前記単位回路に含まれるトランジスタが薄膜トランジスタである場合は、ガラス基板など基体上に、前記トランジスタと、前記単位回路に含まれるトランジスタが薄膜トランジスタと、を一体形成することができる。

【0033】

また、本発明の第14の電気光学装置は、上記の電気光学装置において、前記トランジスタは、シリコンベースのMOSトランジスタで構成されていることを特徴としている。薄膜トランジスタに比べて、シリコンベースのMOSトランジスタは、そのトランジスタ特性の制御が容易であり、トランジスタ特性のバラツキを低減することができる。前記トランジスタがシリコンベースのMOSトランジスタであり、前記単位回路が薄膜トランジスタにより構成されている場合は、外付のデータ線ICドライバ内に配置することが可能であるが、前記トランジスタをウェハ上で作製し、前記トランジスタを前記単位回路を載置する基体上に再配置することも可能である。

【0034】

なお、駆動トランジスタは電気光学素子に電気的に接続されていればよく、例えばこれらの間に他のトランジスタが接続されていてもよい。

また、本発明の第15の電気光学装置は、上記の電気光学装置において、前記電気光学素子に供給される電流量を設定するための、前記データ線を流れる電流量は、前記電気光学素子に供給される電流量以上であることを特徴とする。電気光学素子に供給するための電流量が低い場合、それに対応する電流をデータ線に出力して前記トランジスタのゲート電圧を設定するのに時間を要するが、電気光学素子に供給する電流量以上の電流量をデータ線に流すことにより、前記トランジスタのゲート電圧を設定する時間を速くすることができる。

【0035】

また、本発明の第16の電気光学装置は、上記の電気光学装置において、前記電気光学素子に供給される電流量を設定するための、前記データ線を流れる電流量は、前記電気光学素子に供給される電流量以下であることを特徴とする。

【0036】

前記電気光学素子に供給される電流量を設定するために、前記データ線に出力する電流量を、前記電気光学素子に供給される電流量以下にすることにより消費電力を低減することができる。

【0037】

本発明の第17の電気光学装置は、データ線と、前記データ線と接続され、当該データ線に流れるデータ信号の電流量によりゲート電圧が設定される変換トランジスタと、電気光学素子と、当該電気光学素子と電気的に接続され且つその導電型がp型である駆動トランジスタと、を有する単位回路とを備えたことを特徴としている。

【0038】

本発明の第17の電気光学装置では、新たな電源追加を伴わずに変換トランジスタ及び駆動トランジスタを十分にオンすることが可能となる。

また、本発明の第18の電気光学装置は、走査線をさらに備え、前記各単位回路のそれぞれは、ゲート電極が前記走査線に接続されたスイッチングトランジスタを有し、前記データ線を介してデータ信号が前記複数の単位回路に供給されることを特徴としている。

【0039】

また、本発明の第19の電気光学装置は、上記の電気光学装置において、前記スイッチングトランジスタのソース端又はドレイン端は、前記駆動トランジスタのゲート電極に接続されていることを特徴としている。

【0040】

また、本発明の第20の電気光学装置は、上記の電気光学装置において、前記データ信号は、デジタル−アナログ変換回路で生成されたアナログ量を有する電流であることを特徴としている。

【0041】

また、本発明の第21の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと前記駆動トランジスタとは、カレントミラーを構成することを特徴としている。

【0042】

また、本発明の第22の電気光学装置は、上記の電気光学装置において、前記変換トランジスタは、前記デジタル−アナログ変換回路と前記データ線との間に配置されていることを特徴としている。

【0043】

また、本発明の第23の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記変換トランジスタとの間に前記データ線が配置されていることを特徴としている。

【0044】

また、本発明の第24の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと前記デジタル-アナログ変換回路と前記データ線とは同一基体上に形成されていることを特徴としている。

【0045】

また、本発明の第25の電気光学装置は、上記の電気光学装置において、前記データ線と前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴としている。

【0046】

また、本発明の第26の電気光学装置は、上記の電気光学装置において、前記データ線と前記変換トランジスタとは同一基体上に形成されていることを特徴としている。

【0047】

また、本発明の第27の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記変換トランジスタとは同一基体上に形成されていることを特徴としている。

【0048】

上記の電気光学装置において、「基体」の例としては、ガラス基板、石英基板、またはシリコン基板などを挙げることができる。

また、本発明の第28の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと、前記単位回路に含まれる前記スイッチングトランジスタ及び前記駆動トランジスタとは、薄膜トランジスタで構成されていることを特徴としている。

【0049】

また、本発明の第29の電気光学装置は、上記の電気光学装置において、前記変換トランジスタは、シリコンベースのMOSトランジスタで構成されていることを特徴としている。薄膜トランジスタに比べて、シリコンベースのMOSトランジスタは、そのトランジスタ特性の制御が容易であり、トランジスタ特性のバラツキを低減することができる。前記変換トランジスタがシリコンベースのMOSトランジスタであり、前記単位回路が薄膜トランジスタにより構成されている場合は、外付のデータ線ICドライバ内に配置することが可能であるが、前記変換トランジスタをウェハ上で作製し、前記変換トランジスタを前記単位回路を載置する基体上に再配置することも可能である。

【0050】

なお、駆動トランジスタは電気光学素子に電気的に接続されていればよく、例えばこれらの間に他のトランジスタが接続されていてもよい。

本発明の第30の電気光学装置は、データ線と、前記データ線と接続され、当該データ線に流れるデータ信号の電流量によりゲート電圧が設定される変換トランジスタと、前記変換トランジスタとカレントミラー回路を構成し、前記データ線に流れるデータ信号の電流量により大きな電流量を生成するようにその利得係数が設定された駆動トランジスタと、前記駆動トランジスタと電気的に接続された電気光学素子と、を有する単位回路とを備えたことを特徴としている。

【0051】

本発明の第30の電気光学装置では、電気光学素子に供給するための電流量が低い場合、それに対応する電流をデータ線に出力して前記変換トランジスタのゲート電圧を設定するのに時間を要するが、電気光学素子に供給する電流量以上の電流量をデータ線に流すことにより、前記変換トランジスタのゲート電圧を設定する時間を速くすることができる。

【0052】

本発明の第31の電気光学装置は、データ線と、前記データ線と接続され、当該データ線に流れるデータ信号の電流量によりゲート電圧が設定される変換トランジスタと、前記変換トランジスタとカレントミラー回路を構成し、前記データ線に流れるデータ信号の電流量により小さな電流量を生成するようにその利得係数が設定された駆動トランジスタと、前記駆動トランジスタと電気的に接続された電気光学素子と、を有する単位回路とを備えたことを特徴としている。

【0053】

本発明の第31の電気光学装置では、前記電気光学素子に供給される電流量を設定するために、前記データ線に出力する電流量を、前記電気光学素子に供給される電流量以下にすることにより消費電力を低減することができる。

【0054】

本発明の第32の電気光学装置は、上記の電気光学装置において、走査線をさらに備え、前記複数の単位回路のそれぞれは、ゲート電極が前記走査線に接続されたスイッチングトランジスタを有し、前記データ線を介してデータ信号が前記複数の単位回路に供給されることを特徴としている。

【0055】

本発明の第33の電気光学装置は、上記の電気光学装置において、前記スイッチングトランジスタのソース端又はドレイン端は、前記駆動トランジスタのゲート電極に接続されていることを特徴としている。

【0056】

また、本発明の第34の電気光学装置は、上記の電気光学装置において、前記データ信号は、デジタル−アナログ変換回路で生成されたアナログ量を有する電流であることを特徴としている。

【0057】

また、本発明の第35の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと前記駆動トランジスタとは、カレントミラーを構成することを特徴としている。

【0058】

また、本発明の第36の電気光学装置は、上記の電気光学装置において、前記変換トランジスタは、前記デジタル−アナログ変換回路と前記データ線との間に配置されていることを特徴としている。

【0059】

また、本発明の第37の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記変換トランジスタとの間に前記データ線が配置されていることを特徴としている。

【0060】

また、本発明の第38の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと前記デジタル-アナログ変換回路と前記データ線とは同一基体上に形成されている。

【0061】

また、本発明の第39の電気光学装置は、上記の電気光学装置において、前記データ線と前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴としている。

【0062】

また、本発明の第40の電気光学装置は、上記の電気光学装置において、前記データ線と前記変換トランジスタとは同一基体上に形成されていることを特徴としている。

【0063】

また、本発明の第41の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記変換トランジスタとは同一基体上に形成されていることを特徴としている。

【0064】

また、本発明の第42の電気光学装置は、上記の電気光学装置において、前記変換トランジスタと、前記単位回路に含まれる前記スイッチングトランジスタ及び前記駆動トランジスタとは、薄膜トランジスタで構成されていることを特徴としている。

【0065】

また、本発明の第43の電気光学装置は、上記の電気光学装置において、前記変換トランジスタは、シリコンベースのMOSトランジスタで構成されていることを特徴としている。

【0066】

本発明の第44の電気光学装置は、複数の第1単位回路と複数の第2単位回路を含む複数の単位回路を備えた電気光学装置において、前記複数の第1単位回路のそれぞれは、第1有機エレクトロルミネッセンス素子と、該第1有機エレクトロルミネッセンス素子に接続される第1駆動トランジスタを有し、前記複数の第2単位回路のそれぞれは、前記第1有機エレクトロルミネッセンス素子とは異なる色で発光する第2有機エレクトロルミネッセンス素子と、該第2有機エレクトロルミネッセンス素子に接続される第2駆動トランジスタを有し、前記複数の第1単位回路に接続された第1データ線と、前記第1データ線に接続され、前記第1有機エレクトロルミネッセンス素子の駆動レンジに応じた利得係数を有し、前記第1駆動トランジスタとカレントミラーを構成する第1変換トランジスタと、前記複数の第2単位回路に接続された第2データ線と、前記第2データ線に接続され、前記第2有機エレクトロルミネッセンス素子の駆動レンジに応じた利得係数を有し、前記第2駆動トランジスタとカレントミラーを構成する第2変換トランジスタと、を備え、前記第1変換トランジスタは、前記複数の第1単位回路に対して共通に設けられており、前記第2変換トランジスタは、前記複数の第2単位回路に対して共通に設けられていることを特徴とする。電気光学装置の回路構成を、駆動レンジが異なる電気光学素子の特性に合わせて形成をする必要はなく、全て同じ特性の回路で構成することができる。

【0067】

また、本発明の第45の電気光学装置は、上記の電気光学装置において、前記第1有機エレクトロルミネッセンス素子は、赤、緑及び青色を発光する有機材料から選ばれた1つの有機材料で形成された発光層を有し、前記第2有機エレクトロルミネッセンス素子は、赤、緑及び青色を発光する有機材料から選ばれ、かつ、前記第1有機エレクトロルミネッセンス素子を構成する有機材料とは異なる、1つの有機材料で形成された発光層を有することを特徴としている。

【0068】

また、本発明の第46の電気光学装置は、上記の電気光学装置において、走査線をさらに備え、前記複数の単位回路のそれぞれは、ゲート電極が前記走査線に接続されていたスイッチングトランジスタを有し、前記スイッチングトランジスタのソース端又はドレイン端は、前記第1又は第2駆動トランジスタのゲート電極に接続されていることを特徴としている。

【0069】

また、本発明の第47の電気光学装置は、上記の電気光学装置において、前記第1データ線又は前記第2データ線に供給されるデータ信号は、デジタル−アナログ変換回路で生成されたアナログ量を有する電流であることを特徴としている。

【0070】

本発明の第48の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタは、前記デジタル−アナログ変換回路と前記第1データ線との間に配置され、前記第2変換トランジスタは、前記デジタル−アナログ変換回路と前記第2データ線との間に配置されていることを特徴としている。

【0071】

本発明の第49の電気光学装置は、上記の電気光学装置において、前記デジタル-アナログ変換回路と前記第1変換トランジスタとの間に前記第1データ線が配置され、前記デジタル-アナログ変換回路と前記第2変換トランジスタとの間に前記第2データ線が配置されていることを特徴としている。

【0072】

本発明の第50の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタ、前記第2変換トランジスタ、前記デジタル-アナログ変換回路、前記第1及び第2データ線は同一基体上に形成されていることを特徴としている。

【0073】

本発明の第51の電気光学装置は、上記の電気光学装置において、前記第1及び第2データ線と前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴とする。

【0074】

本発明の第52の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタ、前記第2変換トランジスタ、及び前記第1及び第2データ線は同一基体上に形成されていることを特徴とする。

【0075】

本発明の第53の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタ、前記第2変換トランジスタ、及び前記デジタル - アナログ変換回路とは同一基体上に形成されていることを特徴としている。

【0076】

本発明の第54の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタ、前記第2変換トランジスタ、前記第1駆動トランジスタ、及び前記第2駆動トランジスタとは、薄膜トランジスタで構成されていることを特徴としている。

【0077】

本発明の第55の電気光学装置は、上記の電気光学装置において、前記第1変換トランジスタ及び前記第2変換トランジスタは、シリコンベースのMOSトランジスタで構成されていることを特徴としている。

本発明の電気光学装置は、上記の電気光学装置であって、前記第1データ線を駆動する第1ドライバと、前記第2データ線を駆動する第2ドライバと、をさらに備え、前記第1及び第2ドライバは、同じ特性の回路で構成されることを特徴としている。

本発明の電気光学装置は、上記の電気光学装置であって、前記第1駆動トランジスタを流れる電流と前記第1データ線に流れる電流とが非線形関係となるように設定され、前記第2駆動トランジスタを流れる電流と前記第2データ線に流れる電流とが非線形関係となるように設定されてなることを特徴としている。

【0078】

また、本発明の第56の電気光学装置は、上記の電気光学装置において、前記電気光学素子は有機エレクトロルミネッセンス素子であることを特徴としている。

【0079】

さらに、本発明の電子機器は、上記の電気光学装置を、表示部として利用したことを特徴としている。

【0080】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて説明する。

まず、第1の実施の形態を説明する。

【0081】

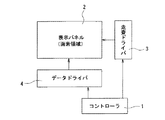

図1は、第1の実施の形態における電気光学装置を適用した表示装置の概略構成を示すブロック図である。この表示装置は、ディスプレイに表示するデータや、表示に関するデータを生成するコントローラ1を有し、このコントローラ1は、表示パネル2に含まれるトランジスタのゲート電極に接続された走査線を駆動する走査ドライバ3と、表示パネル2に含まれるトランジスタのソースまたはドレインに接続されたデータ線を駆動するデータドライバ4と、を制御する。

【0082】

コントローラ1は、また、走査線とデータ線との駆動タイミングのタイミング制御を行う。

表示パネル2は、図2に示すように、走査ドライバ3によって駆動される複数の走査線Ynと、データドライバ4によって駆動される複数のデータ線Xmが直交して配線され、これらの交点に対応して、画素回路10が設けられている。

【0083】

図2に示すように、各データ線Xmを駆動するドライバ4aとは逆側の端部に電源Vxが配置され、電源Vxとデータ線Xmとの間に変換トランジスタ12が接続されている。変換トランジスタ12はダイオード接続されたp型トランジスタである。変換トランジスタ12のゲート電圧はドライバ4aを介してデータ信号に応じてデータ線Xmに出力された電流量に基づいて設定される。

【0084】

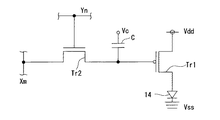

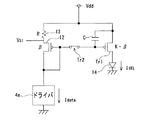

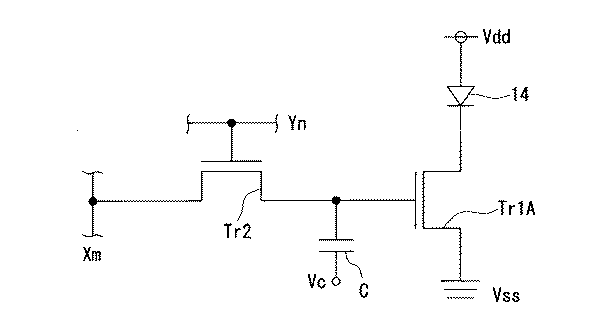

そして、前記画素回路10は、図3に示すように、電気光学素子としての有機エレクトロルミネッセンス素子14と、有機エレクトロルミネッセンス素子14を駆動するための駆動用トランジスタTr1と、前記駆動用トランジスタTr1を駆動するための制御用トランジスタTr2と、データ線Xmのデータを保持するための容量素子Cとから構成されている。

【0085】

本実施形態では、前記各トランジスタTr1及びTr2、及び変換トランジスタ12は、TFT(薄膜トランジスタ:Thin Film Transistor)であり、これら各画素回路10、データ線Xm、走査線Yn及び変換トランジスタ12は、絶縁基板上に一体に形成されている。

【0086】

また、駆動用トランジスタTr1は、例えばpチャネル型トランジスタであり、駆動用トランジスタTr1の一端は電源Vddが接続され、他端は有機エレクトロルミネッセンス素子14が接続され、有機エレクトロルミネッセンス素子14の他端は接地電位Vssに接続されている。さらに、この駆動用トランジスタTr1は、変換トランジスタ12と駆動用トランジスタTr1とはカレントミラーを構成している。

【0087】

一方、制御用トランジスタTr2は、例えばnチャネル型トランジスタで構成され、その一端はデータ線Xmに接続され、他端は駆動用トランジスタTr1のゲート電極及び容量素子Cに接続されている。また、制御用トランジスタTr2のゲート電極は、走査線Ynと接続されている。

【0088】

容量素子Cの一端は電源Vcに接続されている。この電源Vcは、例えば,駆動電源Vddの電位、或いは接地電位Vss或いは任意の電位に設定される。

このような構成にすることによって、走査線駆動信号によって制御用トランジスタTr2が導通状態となったとき、データ線Xmの電位に応じた電荷が容量素子Cに蓄えられ、この電荷によって駆動用トランジスタTr1が導通状態となり、容量素子Cに蓄えられた電荷量に応じた電流量が有機エレクトロルミネッセンス素子14に供給される。

【0089】

本実施形態のデータ線Xm、画素回路10、変換トランジスタ12、駆動用トランジスタTr1、制御用トランジスタTr2、電源Vx、及び電源Vddは、それぞれ特許請求の範囲における通電線及びデータ線、単位回路、トランジスタまたは第1のトランジスタ、第2のトランジスタまたは駆動トランジスタ、スイッチングトランジスタ、第1の電源、及び第2の電源に対応している。なお、特許請求の範囲におけるデジタル−アナログ変換回路はデータドライバ4に含まれている。

【0090】

変換トランジスタ12と駆動用トランジスタTr1との特性比または電源Vddの電位などを任意に設定することによって、データ線Xmに出力される電流量を制御することができる。すなわち、Vdd=Vxとした場合、変換トランジスタ12の利得係数を駆動用トランジスタTr1の利得係数より高く設定すれば、データ線Xmに出力する電流量を高くすることができるため、容量素子Cに高速で電荷を蓄積することができる。一方、変換トランジスタ12の利得係数を駆動用トランジスタTr1の利得係数より低く設定すれば、データ線Xmに出力する電流量を低くすることができるため、消費電力を低減することができる。

【0091】

例えば、駆動用トランジスタTr1の変換トランジスタ12に対する特性比が画素領域2で均一であれば、データ線Xmに出力される電流量に対して所定の電流量が有機エレクトロルミネッセンス素子14に供給されることになる。その結果、面内輝度を均一に制御することができ、表示品位を向上させることができる。

【0092】

また、変換トランジスタ12は同一データ線に接続される各画素回路10に対して共通であり、各画素回路10の駆動用トランジスタTr1と共通の変換トランジスタ12とがカレントミラー回路をなしているので、各画素回路10毎に変換トランジスタ12を設ける必要がなく、画素回路10を構成する素子数を削減することができる。

【0093】

なお、上記第1の実施の形態においては、画素回路10において制御用トランジスタTr2を、その導電型がn型であるnチャネル型トランジスタで構成した場合について説明したが、これに限らず、その導電型がp型であるpチャネル型トランジスタで構成してもよいことはいうまでもない。

【0094】

また、上記第1の実施の形態において、変換トランジスタ12及び駆動用トランジスタTr1をそれぞれ、pチャネル型トランジスタで構成した。ここで、変換トランジスタ12及び駆動用トランジスタTr1のソースはそれぞれ電源Vx、電源Vddに接続されている。変換トランジスタ12及び駆動用トランジスタTr1のしきい値電圧が等しくVthであるとき、電源Vx、電源Vddの電圧値がVth以上であれば変換トランジスタ12及び駆動用トランジスタTr1を十分にオンさせるためには、両トランジスタのドレインがとりうる電圧値以下にゲート電圧を設定すれば良いことになる。両トランジスタのドレインがとりうる電圧値とはすなわち接地電位Vssであるので、両トランジスタのゲート電圧にVss相当の電圧値を印可すれば、十分なオン状態が得られることになる。仮に変換トランジスタ12及び駆動用トランジスタTr1をnチャネル型トランジスタで構成した場合には、両トランジスタを十分にオンするためにはゲート電圧としてVx+Vth及びVdd+Vthを印可する必要がある。このことは新たな電源の追加を意味し、表示装置のコスト増をまねく。

【0095】

また、上記第1の実施の形態において、走査ドライバ3及びデータドライバ4は、薄膜トランジスタ或いはシリコンベースもMOSトランジスタの何れで構成されていても良い。走査ドライバ3及びデータドライバ4が、薄膜トランジスタである場合、これらのドライバをガラス基板などの絶縁基板上に一体に形成することができる。走査ドライバ3及びデータドライバ4が、シリコンベースMOSトランジスタで構成されている場合は、通常、これらのトランジスタは外付のICドライバとなるが、絶縁基板上にこれらのドライバを再配置することも可能である。

【0096】

次に、本発明の第2の実施の形態を説明する。

この第2の実施の形態は、上記第1の実施の形態において、画素領域2の構成が異なる以外は、上記第1の実施の形態と同様であるので、同一部には同一符号を付与しその詳細な説明は省略する。

【0097】

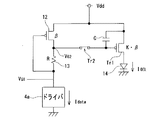

図4に示すように、変換トランジスタ12が各データ線Xmのデータドライバ4側に配置されている。

そして、変換トランジスタ12は上記第1の実施の形態と同様にダイオード接続され、そのゲート電極とドレイン電極とがデータ線Xmに接続され、ソース電極は電源VDに接続されている。

【0098】

データドライバ4により各データ線Xmに出力された電流量に基づいて変換トランジスタ12のゲート電圧が設定される。このゲート電圧に基づいて有機エレクトロルミネッセンス素子14に供給される電流量が決定される。第2の実施の形態の場合も上記第1の実施の形態と同様の作用効果を得ることができる。

【0099】

なお、データドライバ4は薄膜トランジスタで構成しても良いが、シリコンベースのMOSトランジスタで構成しても良い。変換トランジスタ12は薄膜トランジスタであっても良いし、シリコンベースのMOSトランジスタであっても良い。変換トランジスタ12がシリコンベースのMOSトランジスタである場合は、変換トランジスタ12とデータドライバ4とをICドライバとして一体化することも可能である。変換トランジスタ12がシリコンベースのMOSトランジスタである場合は、変換トランジスタ12毎のトランジスタ特性を均一化することもできるので、有機エレクトロルミネッセンス素子14に供給する電流量をより精密に制御することが可能である。

【0100】

次に第3の実施の形態を説明する。

この第3の実施の形態は、上記第1の実施の形態において、画素領域2の構成が異なる以外は上記第1の実施の形態と同様であるので、同一部には同一符号を付与しその詳細な説明は省略する。

【0101】

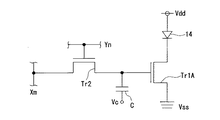

この第3の実施の形態における画素領域2Bは、図5に示すように、電源Vx側にデータドライバ4が設けられ、データ線Xmのデータドライバ4と逆側の端部に、変換トランジスタ12が配置されている。この変換トランジスタ12は、nチャネル型トランジスタである。

【0102】

そして、第3の実施の形態における画素回路10Aは、図6に示すように構成されている。すなわち、第3の実施の形態における駆動用トランジスタTr1Aは、nチャネル型トランジスタで構成され、電源Vddと駆動用トランジスタTr1Aとの間に、有機エレクトロルミネッセンス素子14が配置されている。そして、駆動用トランジスタTr1Aのゲート電極と、制御用トランジスタTr2の一端とが接続されている。

【0103】

なお、この場合も、電源Vcは、電源Vddの電位、或いは接地電位Vss或いは任意の電位に設定されている。

そして、データドライバ4を介して各データ線Xmに出力された、データ信号に応じた電流量に基づいて、変換トランジスタ12のゲート電圧が設定される。そして、このゲート電圧に対応した電荷量が容量素子Cに蓄積される。この電荷量に基づいて駆動用トランジスタTr1Aが導通状態となり、有機エレクトロルミネッセンス素子14に電流が供給される。

【0104】

したがって、この場合も上記第1の実施の形態と同様な作用効果を得ることができる。

なお、この場合も、上記第1の実施の形態と同様に、走査ドライバ3及びデータドライバ4は、薄膜トランジスタで構成されていても良いし、シリコンベースのMOSトランジスタで構成されていても良い。

【0105】

また、画素回路10Aを構成する制御用トランジスタTr2は、nチャネル型及びpチャネル型の何れのトランジスタを用いてもよい。

次に、第4の実施の形態を説明する。

【0106】

この第4の実施の形態は、上記第3の実施の形態において、画素領域2の構成が異なる以外は、上記第3の実施の形態と同様であるので、同一部には同一符号を付与し、その詳細な説明は省略する。

【0107】

すなわち、この第4の実施の形態における画素領域2Cは、図7に示すように、データ線Xm及び走査線Ynの交点に対応して画素回路10Aが設けられ、変換トランジスタ12は、各データ線Xmのデータドライバ4側に設けられ、データドライバ4と隣接して配置されている。

【0108】

そして、変換トランジスタ12は上記第3の実施の形態と同様にダイオード接続されている。

走査ドライバ3において走査線Y1を駆動し、データドライバ4によりデータ線Xmに出力された、データ信号に対応した電流量に基づいて変換トランジスタ12のゲート電圧が設定され、このゲート電圧に対応した電荷量が容量素子に蓄積される。この蓄積された電荷量に基づいて、駆動用トランジスタTr1Aが導通状態となり、有機エレクトロルミネッセンス素子14に電流が供給される。

【0109】

なお、この場合も、データドライバ4は薄膜トランジスタにより構成されていても良いし、また、シリコンベースのMOSトランジスタにより構成されても良いが、シリコンベースのMOSトランジスタの方がより高い精度で電流量を制御するには適している場合がある。

【0110】

次に第5の実施の形態を説明する。

この第5の実施の形態は、上記第2の実施の形態において、データ線Xmに出力される電流量と、画素回路10の有機エレクトロルミネッセンス素子14に供給する電流量の比を変化させるようにしたものである。

【0111】

画素領域2Aとデータドライバ4との間に電流電圧変換回路5が介挿されている。この電流電圧変換回路5は、図8に示すように、データ線Xmにドレイン端、ソース端に駆動電源VDが接続された変換トランジスタ12と、データ線Xmとドレイン端との接続点と、ドライバ4aとの間に介挿された抵抗13と、から構成され、抵抗13とドライバ4aとの間の電位が変換トランジスタ12のゲート電極に接続されている。

【0112】

ここで、例えば、駆動電源VD=駆動電源Vddであるとすると、各画素回路10及び電流電圧変換回路5は、図9のように表すことができる。

前記変換トランジスタ12のしきい値電圧と駆動用トランジスタTr1のしきい値電圧とが等しく、各トランジスタがそれぞれ飽和領域で動作しているとき、これらの間には次式(1)〜(3)が成り立つ。

【0113】

なお、式中の、Idataはドライバ4aの出力電流量、βはトランジスタの電流供給能力を示す係数(利得係数)、VG1は抵抗13とドライバ4aとの間の電位、VTHは変換トランジスタ12及び駆動用トランジスタTr1のしきい値電圧、IOELは有機エレクトロルミネッセンス素子14に供給される電流値、kはIdataとIOELとの電流比を表す定数、VG2は変換トランジスタ12と抵抗13との間の電位、Rは抵抗13の抵抗値である。

【0114】

Idata=(1/2)・β・(Vdd−VG1−VTH)2・・・(1)

IOEL=(1/2)・kβ・(Vdd−VG2−VTH)2・・・(2)

VG2−VG1=R・Idata・・・(3)

これら(1)〜(3)式から、次式(4)を得ることができる。

【0115】

【数1】

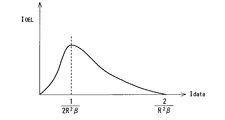

したがって、(4)式から、IdataとIOELとの関係を、図10の特性図ように設定することができるので、図10において、例えば、1/(2R2・β)≦Idata≦2/(R2・β)の範囲を用いるようにすれば、Idataの変化とIOELの変化とを逆向きに設定することができる。

【0116】

なお、この場合も、走査ドライバ3、データドライバ4及び電流電圧変換回路5を薄膜トランジスタまたはシリコンベースのMOSトランジスタの何れで構成されていてもよく、また、データドライバ4と電流電圧変換回路5とを一体に形成するようにしてもよい。

【0117】

次に、本発明の第6の実施の形態を説明する。

この第6の実施の形態は、図11に示すように、電源Vxと画素領域2Cとの間に、データドライバ4及び電流電圧変換回路5Aが介挿されている。

【0118】

前記画素領域2Cは、データ線Xm及び走査線Ynの交点に対応して画素回路10Aが配置されて構成されている。

前記電流電圧変換回路5Aは、図11に示すように、nチャネル型の変換トランジスタ12と抵抗13とから構成され、変換トランジスタ12のソース端は電源Vsに接続され、ドレイン端はデータ線Xmに接続されている。そして、データ線Xmとドレイン端との接続点と、ドライバ4aとの間に変換トランジスタ12のゲート電極が接続されている。さらに、データ線Xmのゲート電極の接続点とドレイン電極の接続点との間に抵抗13が介挿されている。

【0119】

したがって、この場合も、上記第5の実施の形態と同様の動作となり、第5の実施の同様の作用効果を得ることができる。

次に、本発明の第7の実施の形態を説明する。

【0120】

この第7の実施の形態は、図12に示すように、画素領域2Aとデータドライバ4との間に電流電圧変換回路5Bが介挿されている。

前記画素領域2Aは、データ線Xm及び走査線Ynの交点に対応して配置された画素回路10により構成されている。

【0121】

電流電圧変換回路5Bは、図12に示すように、pチャネル型の変換トランジスタ12と、抵抗13とから構成され、変換トランジスタ12のソース端とデータ線Xmとが接続され、そのドレイン電極と駆動電源VDとの間に抵抗13が介挿されている。そして、データ線Xmのソース端の接続点と、ドライバ4aとの間に変換トランジスタ12のゲート電極が接続されている。

【0122】

ここで、例えば、電源VD=電源Vddであるとすると、各画素回路10及び電流電圧変換回路5は、図13のように表すことができる。

そして、前記変換トランジスタ12のしきい値電圧と駆動用トランジスタTr1のしきい値電圧とが等しく、各トランジスタがそれぞれ飽和領域で動作しているとき、これらの間には次式(5)〜(7)が成り立つ。

【0123】

なお、式中の、Idataはドライバ4aの出力電流量、βはトランジスタの電流供給能力を示す係数(利得係数)、VS1は抵抗13とドライバ4aとの間の電位、VTHは変換トランジスタ12及び駆動用トランジスタTr1のしきい値電圧、IOELは有機エレクトロルミネッセンス素子14に供給される電流値、kはIdataとIOELとの電流比を表す定数、Rは抵抗13の抵抗値である。

【0124】

Idata=(1/2)・β・(VS1−VG−VTH)2・・・(5)

IOEL=(1/2)・kβ・(Vdd−VG−VTH)2・・・(6)

Vdd−VS1=R・Idata・・・(7)

これら(5)〜(7)式から、次式(8)を得ることができる。

【0125】

【数2】

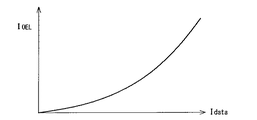

したがって(8)式から、IdataとIOELとの関係は、図14の特性図のように表すことができる。よって、ΔIdataとΔIOELとの間に、非線形関係をもたせることができ、出力電流量Idataの変化に対してΔIOELをより大きく変化させることができる。

【0126】

次に、本発明の第8の実施の形態を説明する。

この第8の実施の形態は、図15に示すように、データドライバ4と画素領域2Cとの間に、電流電圧変換回路5Cが介挿されている。

【0127】

前記画素領域2Cは、データ線Xmと走査線Ynとの交点に対応して配置された画素回路10Aにより構成されている。

電流電圧変換回路5Cは、図15に示すように、nチャネル型の変換トランジスタ12と抵抗13とから構成され、変換トランジスタ12のドレイン端は、データ線Xmに接続され、そのソースと電源Vsとの間に抵抗13が介挿されている。また、データ線Xmの変換トランジスタ12のドレイン端との接続点と、ドライバ4aとの間に変換トランジスタ12のゲート電極が接続されている。

【0128】

したがって、この場合も、上記第7の実施の形態と同様であって、ドライバ4aの出力電流量に対し、画素回路10Aの駆動用トランジスタTr1Aを流れる電流量は大きくなるから、第7の実施の形態と同様な作用効果を得ることができる。

【0129】

なお、前記第5乃至第8の実施の形態において、電流電圧変換回路5は、薄膜トランジスタにより構成されても良く、また、シリコンベースのMOSトランジスタにより構成されていても良い。また、データドライバ4と電流電圧変換回路5とを一体に形成するようにしても良い。

【0130】

次に、本発明の第9の実施の形態を説明する。

この第9の実施の形態は、本発明に係る電気光学装置をフルカラーのディスプレイに適用した場合である。尚、この第9の実施の形態では、上記第1の実施の形態において、画素領域2の構成が異なる以外は上記第1の実施の形態と同様であるので、同一部または同一符号を付し、その詳細な説明は省略する。

【0131】

図16は、第9の実施の形態における表示装置の要部の概略構成を示すブロック図である。図16に示すように、画素領域2Dは、走査線Ynに沿って、赤色、緑色及び青色の光を発光する有機材料で構成された発光層を有する各色用有機エレクトロルミネッセンス素子14R,14G,14Bを有する赤、緑色及び青色用画素回路10R,10G,10Bが、順次繰り返されて設けられている。また、前記画素領域2Dは、各データ線Xmに沿って同色の画素回路10R,10G,10Bがそれぞれ設けられている。つまり、赤色用画素回路10Rは、データ線X1,X4,X7,・・・と接続されている。緑色用画素回路10Gは、データ線X2,X5,X8,・・・と接続されている。青色用画素回路10Bは、青用データ線X3,X6,X9,・・・と接続されている。

【0132】

そして、赤色用画素回路10Rと接続された前記データ線X1,X4,X7,・・・は、赤色用変換トランジスタ12Rと接続されている。赤色用変換トランジスタ12Rは、前記赤色用の有機エレクトロルミネッセンス素子14Rが発光する駆動レンジとしての電流レンジを生成するようにその利得係数が設定されている。赤色用変換トランジスタ12Rは、同赤色用変換トランジスタ12Rを駆動させるための電圧を供給する赤色用電源VxRに接続されている。また、各赤色用画素回路10Rと接続された前記データ線X1,X4,X7,・・・は、前記赤色用電源VxRとは逆側の端部に配置された、同データ線X1,X4,X7,・・・を駆動する赤色用ドライバ4aRにそれぞれ接続されている。すなわち、赤色用ドライバ4aRと赤色用変換トランジスタ12Rとの間に前記データ線X1,X4,X7,・・・が配置されている。

【0133】

緑色用画素回路10Gと接続された前記データ線X2,X5,X8,・・・は、緑色用変換トランジスタ12Gと接続されている。緑色用変換トランジスタ12Gは、前記緑色用の有機エレクトロルミネッセンス素子14Gが発光する駆動レンジとしての電流レンジを生成するようにその利得係数が設定されている。緑色用変換トランジスタ12Gは、同緑色用変換トランジスタ12Gを駆動させるための電圧を供給する緑色用電源VxGに接続されている。また、各緑色用画素回路10Gと接続された前記データ線X2,X5,X8,・・・は、前記緑色用電源VxGとは逆側の端部に配置された、同前記データ線X2,X5,X8,・・・を駆動する緑色用ドライバ4aGにそれぞれ接続されている。すなわち、緑色用ドライバ4aGと緑色用変換トランジスタ12Gとの間に前記データ線X2,X5,X8,・・・が配置されている。

【0134】

青色用画素回路10Bと接続された前記データ線X3,X6,X9,・・・は、青色用変換トランジスタ12Bと接続されている。青色用変換トランジスタ12Bは、前記青色用の有機エレクトロルミネッセンス素子14Bが発光する駆動レンジとしての電流レンジを生成するようにその利得係数が設定されている。青色用変換トランジスタ12Bは、同青色用変換トランジスタ12Bを駆動させるための電圧を供給する青色用電源VxBに接続されている。また、各青色用画素回路10Bと接続された前記データ線X3,X6,X9,・・・は、前記青色用電源VxBとは逆側の端部に配置された、同前記データ線X3,X6,X9,・・・を駆動する青色用ドライバ4aBにそれぞれ接続されている。すなわち、青色用ドライバ4aBと青色用変換トランジスタ12Bとの間に前記データ線X3,X6,X9,・・・が配置されている。

【0135】

尚、前記赤、緑及び青色用変換トランジスタ12R,12G,12Bは、それぞれ、pチャネル型トランジスタである。

そして、このように構成された画素領域2Dを有する電気光学装置においては、前記したように、各色用変換トランジスタ12R,12G,12Bのそれぞれの利得係数を調整することによって、各色用の有機エレクトロルミネッセンス素子14R,14G,14Bを発光させる電流レンジを調整することができる。

【0136】

従って、各色用ドライバ4aR,4aG,4aBは、各色用の有機エレクトロルミネッセンス素子14R,14G,14Bの特性に合わせてそれぞれの特性の異なる回路形成をする必要はなく、全て同じ特性の回路で構成することができる。ここで、図15における変換トランジスタ12R,12G,12Bの配置場所については、本実施形態で示した場所に限定されるものではなく、例えば、第2〜第8の実施の形態で示した配置を適用することも可能である。

【0137】

なお、上記各実施の形態においては、走査ドライバ3及びデータドライバ4を薄膜トランジスタにより構成されていても良く、またシリコンベースのMOSトランジスタにより構成されていても良い。

【0138】

また、上記各実施の形態において、画素回路10又は10Aをマトリクス状に配置した表示装置に適用した場合について説明したが、どのような形状に配置した場合であっても適用することができる。

【0139】

また、上記各実施の形態においては、有機エレクトロルミネッセンス素子を用いた場合について説明したが、これに限るものではなく、例えば発光ダイオード(LED)、レーザーダイオード(LD)、FE(Field emission)素子等の電流駆動により発光する素子を備えた電子装置に対しても、本発明に係る回路構成は適用することができる。これ以外に磁気抵抗RAM(Magnetoresistive RAM)などの非発光型の電流駆動素子を備えた電子装置に対しても本発明に係る回路構成にも適用することができる。

【0140】

磁気抵抗RAMは、例えば、図17に示すように、強磁性金属層からなる2つの電極21及び22間に、絶縁体からなる障壁層23が介挿されて構成されている。そして、前記電極21及び22巻に、前記障壁層23を介してトンネル電流を流したときに、このトンネル電流の大きさが上下の強磁性金属の磁化の向きによって変化することを利用して、記憶を行うようにしたものである。つまり、一方の電極22を基準層としてその磁化の向きを固定し、他方の電極21をデータ記録層とする。そして、書き込み電極24に電流を流し、これによって発生する磁界により、データ記録層としての電極21の磁化の向きを変えることによって情報の記録を行う。そして、記録情報の読み出しを行う場合には、書き込み電極24に逆方向の電流を流し、このときのトンネル抵抗の変化を電気的に読み出すことによって行っている。

【0141】

また、前記有機エレクトロルミネッセンス装置としては、例えば、モバイル型のパーソナルコンピュータ、携帯電話、ディジタルスチルカメラ等に適用することができる。

【0142】

図18は、モバイル型のパーソナルコンピュータの構成を示す斜視図である。

図18において、パーソナルコンピュータ100は、キーボード102を備えた本体部104と、前述の電気光学装置が適用された有機エレクトロルミネッセンス装置からなる表示ユニット106とから構成されている。

【0143】

図19は、携帯電話の斜視図である。図19において、携帯電話200は、複数の操作ボタン202の他、受話口204、送話口206と共に、前述の電気光学装置が適用された有機エレクトロルミネッセンス装置からなる表示パネル208を備えている。

【0144】

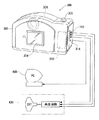

図20は、ディジタルスチルカメラ300の構成を示す斜視図である。なお、外部機器との接続についても簡易的に示している。

通常のカメラは、被写体の光像によってフィルムを感光するのに対してディジタルスチルカメラ300は被写体の光像をCCD(Charge coupled device)等の撮像素子により光電変換して撮像信号を生成するものである。ここで、ディジタルスチルカメラ300におけるケース302の背面には、上述した電気光学装置が適用された有機エレクトロルミネッセンス装置からなる表示パネル304が設けられ、CCDによる撮像信号に基づいて、表示を行う構成となっている。このため、表示パネル304は、被写体を表示するファインダとして機能する。また、ケース302の観察側(図においては裏面側)には、光学レンズやCCD等を含んだ受光ユニット306が設けられている。

【0145】

ここで、撮像者が表示パネル304に表示された被写体像を確認して、シャッタボタン308を押下すると、その時点におけるCCDの撮像信号が、回路基板310のメモリに転送・格納される。また、このディジタルスチルカメラ300にあっては、ケース302の側面にビデオ信号出力端子312と、データ通信用の入出力端子314とが設けられている。そして、図に示されるように、前者のビデオ信号出力端子312には、テレビモニタ430が、また、後者のデータ通信用の入出力端子314にはパーソナルコンピュータ440が、それぞれ必要に応じて接続される。さらに、所定の操作によって、回路基板310のメモリに格納された撮像信号が、テレビモニタ430や、パーソナルコンピュータ440に出力される構成となっている。

【0146】

なお、電子機器としては、図18のパーソナルコンピュータや、図19の携帯電話、図20のディジタルスチルカメラの他にも、テレビ、ビューファインダ型及びモニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等を挙げることができる。そして、これらの各種電子機器に表示部として、上述した電気光学装置からなる表示装置が適用可能なのはいうまでもない。

【0147】

【発明の効果】

本発明によれば、電流駆動による電気光学素子の駆動制御をより高精度に行い且つ構成素子数の低減を図ることができる。

【図面の簡単な説明】

【図1】 本発明を適用した表示装置の概略構成を示すブロック図である。

【図2】 本発明の第1の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図3】 第1の実施の形態における画素回路の一例を示す回路図である。

【図4】 第2の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図5】 第3の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図6】 第3の実施の形態における画素回路の一例を示す回路図である。

【図7】 第4の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図8】 第5の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図9】 第5の実施の形態の動作説明に供する回路図である。

【図10】 第5の実施の形態の動作説明に供する説明図である。

【図11】 第6の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図12】 第7の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図13】 第7の実施の形態の動作説明に供する回路図である。

【図14】 第7の実施の形態の動作説明に供する説明図である。

【図15】 第8の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図16】 第9の実施の形態における表示装置の要部の概略構成を示すブロック図である。

【図17】 本発明に係る電気光学装置を適用した磁気抵抗RAMの概略構成を示す構成図である。

【図18】 本発明に係る電気光学装置を適用した電子機器の一例たるパーソナルコンピュータの構成を示す斜視図である。

【図19】 本発明に係る電気光学装置を適用した電子機器の一例たる携帯電話の構成を示す斜視図である。

【図20】 本発明に係る電気光学装置を適用した電子機器の一例たるディジタルスチルカメラの背面側の構成を示す斜視図である。

【図21】 従来の表示装置の一例を示すブロック図である。

【図22】 従来の画素回路の一例を示す回路図である。

【符号の説明】

1 コントローラ

2、2A、2B、2C、2D 画素領域

3 走査ドライバ

4 データドライバ

4a ドライバ

5、5A、5B、5C 電流電圧変換回路

10、10A 画素回路

12 変換トランジスタ

13 抵抗

14 有機エレクトロルミネッセンス素子

Claims (15)

- 複数の第1単位回路と複数の第2単位回路を含む複数の単位回路を備えた電気光学装置において、

前記複数の第1単位回路のそれぞれは、第1有機エレクトロルミネッセンス素子と、該第1有機エレクトロルミネッセンス素子に接続される第1駆動トランジスタを有し、

前記複数の第2単位回路のそれぞれは、前記第1有機エレクトロルミネッセンス素子とは異なる色で発光する第2有機エレクトロルミネッセンス素子と、該第2有機エレクトロルミネッセンス素子に接続される第2駆動トランジスタを有し、

前記複数の第1単位回路に接続された第1データ線と、

前記第1データ線に接続され、前記第1有機エレクトロルミネッセンス素子の駆動レンジに応じた利得係数を有し、前記第1駆動トランジスタとカレントミラーを構成する第1変換トランジスタと、

前記複数の第2単位回路に接続された第2データ線と、

前記第2データ線に接続され、前記第2有機エレクトロルミネッセンス素子の駆動レンジに応じた利得係数を有し、前記第2駆動トランジスタとカレントミラーを構成する第2変換トランジスタと、

を備え、

前記第1変換トランジスタは、前記複数の第1単位回路に対して共通に設けられており、

前記第2変換トランジスタは、前記複数の第2単位回路に対して共通に設けられていることを特徴とする電気光学装置。 - 前記第1有機エレクトロルミネッセンス素子は、赤、緑及び青色を発光する有機材料から選ばれた1つの有機材料で形成された発光層を有し、

前記第2有機エレクトロルミネッセンス素子は、赤、緑及び青色を発光する有機材料から選ばれ、かつ、前記第1有機エレクトロルミネッセンス素子を構成する有機材料とは異なる、1つの有機材料で形成された発光層を有することを特徴とする請求項1に記載の電気光学装置。 - 走査線をさらに備え、

前記複数の単位回路のそれぞれは、ゲート電極が前記走査線に接続されていたスイッチングトランジスタを有し、

前記スイッチングトランジスタのソース端又はドレイン端は、前記第1又は第2駆動トランジスタのゲート電極に接続されていることを特徴とする請求項1又は2に記載の電気光学装置。 - 前記第1データ線又は前記第2データ線に供給されるデータ信号は、デジタル−アナログ変換回路で生成されたアナログ量を有する電流であることを特徴とする請求項1乃至3の何れかに記載の電気光学装置。

- 前記第1変換トランジスタは、前記デジタル−アナログ変換回路と前記第1データ線との間に配置され、

前記第2変換トランジスタは、前記デジタル−アナログ変換回路と前記第2データ線との間に配置されていることを特徴とする請求項4に記載の電気光学装置。 - 前記デジタル-アナログ変換回路と前記第1変換トランジスタとの間に前記第1データ線が配置され、前記デジタル-アナログ変換回路と前記第2変換トランジスタとの間に前記第2データ線が配置されていることを特徴とする請求項4に記載の電気光学装置。

- 前記第1変換トランジスタ、前記第2変換トランジスタ、前記デジタル-アナログ変換回路、前記第1及び第2データ線は同一基体上に形成されていることを特徴とする請求項4乃至6の何れかに記載の電気光学装置。

- 前記第1及び第2データ線と前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴とする請求項4乃至6の何れかに記載の電気光学装置。

- 前記第1変換トランジスタ、前記第2変換トランジスタ、及び前記第1及び第2データ線は同一基体上に形成されていることを特徴とする請求項4乃至6の何れかに記載の電気光学装置。

- 前記第1変換トランジスタ、前記第2変換トランジスタ、及び前記デジタル-アナログ変換回路とは同一基体上に形成されていることを特徴とする請求項4乃至6の何れかに記載の電気光学装置。

- 前記第1変換トランジスタ、前記第2変換トランジスタ、前記第1駆動トランジスタ、及び前記第2駆動トランジスタとは、薄膜トランジスタで構成されていることを特徴とする請求項1乃至10の何れかに記載の電気光学装置。

- 前記第1変換トランジスタ及び前記第2変換トランジスタは、シリコンベースのMOSトランジスタで構成されていることを特徴とする請求項1乃至10の何れかに記載の電気光学装置。

- 前記第1データ線を駆動する第1ドライバと、

前記第2データ線を駆動する第2ドライバと、

をさらに備え、

前記第1及び第2ドライバは、同じ特性の回路で構成されることを特徴とする請求項1乃至12の何れかに記載の電気光学装置。 - 前記第1駆動トランジスタを流れる電流と前記第1データ線に流れる電流とが非線形関係となるように設定され、

前記第2駆動トランジスタを流れる電流と前記第2データ線に流れる電流とが非線形関係となるように設定されてなることを特徴とする請求項1乃至13の何れかに記載の電気光学装置。 - 請求項1乃至14の何れかに記載の電気光学装置を、表示部として利用したことを特徴とする電子機器。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002223166A JP4089340B2 (ja) | 2001-08-02 | 2002-07-31 | 電子装置、電気光学装置及び電子機器 |

| US10/207,965 US7102600B2 (en) | 2001-08-02 | 2002-07-31 | System and method for manufacturing a electro-optical device |

| CNB021429219A CN100403374C (zh) | 2001-08-02 | 2002-08-02 | 电子装置、电-光装置和电子设备 |

| TW091117485A TWI272568B (en) | 2001-08-02 | 2002-08-02 | Electronic device, electric optic device, and electronic instrument |

| KR10-2002-0045776A KR100515772B1 (ko) | 2001-08-02 | 2002-08-02 | 전자 장치, 전기 광학 장치 및 전자 기기 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001235385 | 2001-08-02 | ||

| JP2001-235385 | 2001-08-02 | ||

| JP2002223166A JP4089340B2 (ja) | 2001-08-02 | 2002-07-31 | 電子装置、電気光学装置及び電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007097088A Division JP4858274B2 (ja) | 2001-08-02 | 2007-04-03 | 電子装置、電気光学装置及び電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003131618A JP2003131618A (ja) | 2003-05-09 |

| JP4089340B2 true JP4089340B2 (ja) | 2008-05-28 |

Family

ID=26619862

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002223166A Expired - Lifetime JP4089340B2 (ja) | 2001-08-02 | 2002-07-31 | 電子装置、電気光学装置及び電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7102600B2 (ja) |

| JP (1) | JP4089340B2 (ja) |

| KR (1) | KR100515772B1 (ja) |

| CN (1) | CN100403374C (ja) |

| TW (1) | TWI272568B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007233399A (ja) * | 2001-08-02 | 2007-09-13 | Seiko Epson Corp | 電子装置、電気光学装置及び電子機器 |

| US8603239B2 (en) | 2000-03-14 | 2013-12-10 | James Hardie Technology Limited | Fiber cement building materials with low density additives |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3875470B2 (ja) * | 2000-08-29 | 2007-01-31 | 三星エスディアイ株式会社 | ディスプレイの駆動回路及び表示装置 |

| JP3918642B2 (ja) * | 2002-06-07 | 2007-05-23 | カシオ計算機株式会社 | 表示装置及びその駆動方法 |

| US20050212448A1 (en) * | 2002-11-20 | 2005-09-29 | Makoto Shibusawa | Organic EL display and active matrix substrate |

| JP4066849B2 (ja) * | 2003-02-28 | 2008-03-26 | セイコーエプソン株式会社 | 電流生成回路、電気光学装置および電子機器 |

| JP2004294865A (ja) * | 2003-03-27 | 2004-10-21 | Sanyo Electric Co Ltd | 表示回路 |

| JP4623939B2 (ja) * | 2003-05-16 | 2011-02-02 | 株式会社半導体エネルギー研究所 | 表示装置 |

| TWI253614B (en) * | 2003-06-20 | 2006-04-21 | Sanyo Electric Co | Display device |

| KR100520827B1 (ko) * | 2003-06-21 | 2005-10-12 | 엘지.필립스 엘시디 주식회사 | 일렉트로 루미네센스 표시패널의 구동장치 및 구동방법과일렉트로 루미네센스 표시장치의 제조방법 |

| GB0316482D0 (en) * | 2003-07-15 | 2003-08-20 | Koninkl Philips Electronics Nv | Active matrix array device |

| JP4589614B2 (ja) * | 2003-10-28 | 2010-12-01 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| DE10360816A1 (de) | 2003-12-23 | 2005-07-28 | Deutsche Thomson-Brandt Gmbh | Schaltung und Ansteuerverfahren für eine Leuchtanzeige |

| CN100472812C (zh) * | 2003-12-24 | 2009-03-25 | 汤姆森特许公司 | 图像显示屏幕与控制该屏幕的方法 |

| JP4816630B2 (ja) * | 2004-01-05 | 2011-11-16 | セイコーエプソン株式会社 | データ線駆動回路、電気光学装置および電子機器 |

| JP2005222030A (ja) * | 2004-01-05 | 2005-08-18 | Seiko Epson Corp | データ線駆動回路、電気光学装置および電子機器 |

| JP4036210B2 (ja) * | 2004-05-24 | 2008-01-23 | セイコーエプソン株式会社 | 電流供給回路、電流供給装置、電圧供給回路、電圧供給装置、電気光学装置、及び電子機器 |

| TWI334126B (en) * | 2007-07-17 | 2010-12-01 | Au Optronics Corp | Voltage adjusting circuit, method, and display apparatus having the same |

| TWI391891B (zh) * | 2008-06-06 | 2013-04-01 | Holtek Semiconductor Inc | 顯示器面板驅動器 |

| CN103440846A (zh) * | 2013-08-29 | 2013-12-11 | 京东方科技集团股份有限公司 | 像素驱动单元及其驱动方法、像素电路 |

| US9904251B2 (en) * | 2015-01-15 | 2018-02-27 | Electronics And Telecommunications Research Institute | Holographic display apparatus and method of driving the same |

| JP6822269B2 (ja) * | 2017-03-29 | 2021-01-27 | コニカミノルタ株式会社 | 光書き込み装置及び画像形成装置 |

| CN107846759B (zh) * | 2017-12-12 | 2024-01-05 | 上海灿瑞科技股份有限公司 | 一种led驱动芯片 |

| CN114974126B (zh) * | 2022-06-29 | 2024-11-19 | 武汉天马微电子有限公司 | 显示面板及其驱动方法、显示装置 |

| WO2024023966A1 (ja) * | 2022-07-27 | 2024-02-01 | シャープディスプレイテクノロジー株式会社 | 表示装置 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4967192A (en) * | 1987-04-22 | 1990-10-30 | Hitachi, Ltd. | Light-emitting element array driver circuit |

| DE68921020T2 (de) * | 1988-05-20 | 1995-06-29 | Mitsubishi Electric Corp | Integrierte MOS-Schaltung zum Steuern von lichtermittierenden Dioden. |

| US4996523A (en) * | 1988-10-20 | 1991-02-26 | Eastman Kodak Company | Electroluminescent storage display with improved intensity driver circuits |

| US5336879A (en) | 1993-05-28 | 1994-08-09 | David Sarnoff Research Center, Inc. | Pixel array having image forming pixel elements integral with peripheral circuit elements |

| US5814980A (en) * | 1996-09-03 | 1998-09-29 | International Business Machines Corporation | Wide range voltage regulator |

| US6529178B1 (en) | 1997-02-17 | 2003-03-04 | Seiko Epson Corporation | Current-driven emissive display device, method for driving the same, and method for manufacturing the same |

| US5903246A (en) | 1997-04-04 | 1999-05-11 | Sarnoff Corporation | Circuit and method for driving an organic light emitting diode (O-LED) display |

| US5952789A (en) | 1997-04-14 | 1999-09-14 | Sarnoff Corporation | Active matrix organic light emitting diode (amoled) display pixel structure and data load/illuminate circuit therefor |

| US6229506B1 (en) | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| US6175345B1 (en) * | 1997-06-02 | 2001-01-16 | Canon Kabushiki Kaisha | Electroluminescence device, electroluminescence apparatus, and production methods thereof |

| KR100244216B1 (ko) * | 1997-12-16 | 2000-02-01 | 구자홍 | 디스플레이 소자의 구동회로 |

| KR100259287B1 (ko) * | 1997-12-16 | 2000-06-15 | 구자홍 | 디스플레이 소자의 그레이 스케일 레벨 제어장치 |

| JP3252897B2 (ja) | 1998-03-31 | 2002-02-04 | 日本電気株式会社 | 素子駆動装置および方法、画像表示装置 |

| US6160436A (en) * | 1998-04-17 | 2000-12-12 | Advanced Micro Devices, Inc. | Driver with switchable gain |

| GB9812739D0 (en) | 1998-06-12 | 1998-08-12 | Koninkl Philips Electronics Nv | Active matrix electroluminescent display devices |

| JP3315652B2 (ja) * | 1998-09-07 | 2002-08-19 | キヤノン株式会社 | 電流出力回路 |

| US6384804B1 (en) * | 1998-11-25 | 2002-05-07 | Lucent Techonologies Inc. | Display comprising organic smart pixels |

| JP2000227771A (ja) * | 1998-12-01 | 2000-08-15 | Sanyo Electric Co Ltd | カラーel表示装置 |

| JP4505868B2 (ja) | 1999-03-12 | 2010-07-21 | 双葉電子工業株式会社 | 電界放出型表示装置の輝度補償回路 |

| KR100556480B1 (ko) | 1999-05-13 | 2006-03-03 | 엘지전자 주식회사 | 평면 디스플레이소자의 전류제어 장치 |

| KR100327374B1 (ko) | 2000-03-06 | 2002-03-06 | 구자홍 | 액티브 구동 회로 |

| KR100335062B1 (ko) * | 2000-04-14 | 2002-05-03 | 구자홍 | 유기 el 패널의 휘도 조절 회로 |

| US20020030647A1 (en) * | 2000-06-06 | 2002-03-14 | Michael Hack | Uniform active matrix oled displays |

| KR100344810B1 (ko) * | 2000-07-26 | 2002-07-20 | 엘지전자주식회사 | 고전압소자를 이용한 전류구동회로 |

| KR100370033B1 (ko) * | 2000-10-24 | 2003-01-30 | 엘지전자 주식회사 | 발광소자의 구동 제어회로 |

-

2002

- 2002-07-31 JP JP2002223166A patent/JP4089340B2/ja not_active Expired - Lifetime

- 2002-07-31 US US10/207,965 patent/US7102600B2/en not_active Expired - Lifetime

- 2002-08-02 TW TW091117485A patent/TWI272568B/zh not_active IP Right Cessation

- 2002-08-02 CN CNB021429219A patent/CN100403374C/zh not_active Expired - Lifetime

- 2002-08-02 KR KR10-2002-0045776A patent/KR100515772B1/ko not_active Expired - Lifetime

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8603239B2 (en) | 2000-03-14 | 2013-12-10 | James Hardie Technology Limited | Fiber cement building materials with low density additives |

| JP2007233399A (ja) * | 2001-08-02 | 2007-09-13 | Seiko Epson Corp | 電子装置、電気光学装置及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100403374C (zh) | 2008-07-16 |

| US20030067455A1 (en) | 2003-04-10 |

| TWI272568B (en) | 2007-02-01 |

| JP2003131618A (ja) | 2003-05-09 |

| KR20030011718A (ko) | 2003-02-11 |

| US7102600B2 (en) | 2006-09-05 |

| CN1402214A (zh) | 2003-03-12 |

| KR100515772B1 (ko) | 2005-09-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4089340B2 (ja) | 電子装置、電気光学装置及び電子機器 | |

| US7098705B2 (en) | Electronic circuit, method of driving electronic circuit, electronic device, electro-optical device, method of driving electro-optical device, and electronic apparatus | |

| CN100511369C (zh) | 用于有机场致发光显示器的电流抽样电路 | |

| US7940239B2 (en) | Semiconductor device and display device utilizing the same | |

| CN100536631C (zh) | 电子电路及其驱动方法、电光学装置以及电子机器 | |

| JP4556354B2 (ja) | 駆動回路、装置、及び電子機器 | |

| JP3952953B2 (ja) | 電子回路、エレクトロルミネッセンス装置、及び電子機器 | |

| JP4628447B2 (ja) | 半導体装置 | |

| JP2004302211A (ja) | 画素回路、電気光学装置および電子機器 | |

| KR100524281B1 (ko) | 전자 회로, 전자 장치 및 전자 기기 | |

| JP2008052289A (ja) | 発光装置及び電子機器 | |

| JP3849466B2 (ja) | 駆動回路、電気光学装置、駆動回路の駆動方法、有機エレクトロルミネッセンス装置及び電子機器 | |

| JP4858274B2 (ja) | 電子装置、電気光学装置及び電子機器 | |

| JP4556814B2 (ja) | 装置、装置の駆動方法及び電子機器 | |

| JP2004219466A (ja) | 電子回路、エレクトロルミネッセンスディスプレイ装置、電気光学装置、電子機器、有機エレクトロルミネッセンス画素への電流供給を制御する方法、及び回路を駆動する方法 | |

| JP2006072377A (ja) | 回路、装置、及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050728 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070206 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070918 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080218 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4089340 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110307 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120307 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120307 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130307 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140307 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |