JP4087336B2 - 能動バイアス回路 - Google Patents

能動バイアス回路 Download PDFInfo

- Publication number

- JP4087336B2 JP4087336B2 JP2003518034A JP2003518034A JP4087336B2 JP 4087336 B2 JP4087336 B2 JP 4087336B2 JP 2003518034 A JP2003518034 A JP 2003518034A JP 2003518034 A JP2003518034 A JP 2003518034A JP 4087336 B2 JP4087336 B2 JP 4087336B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- source

- circuit

- power amplifier

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015556 catabolic process Effects 0.000 claims description 22

- 230000000903 blocking effect Effects 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 8

- 230000008859 change Effects 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 230000006641 stabilisation Effects 0.000 description 8

- 238000011105 stabilization Methods 0.000 description 8

- 238000000034 method Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 230000007423 decrease Effects 0.000 description 6

- 101100041249 Chlorobaculum tepidum (strain ATCC 49652 / DSM 12025 / NBRC 103806 / TLS) rub1 gene Proteins 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 101100041257 Chlorobaculum tepidum (strain ATCC 49652 / DSM 12025 / NBRC 103806 / TLS) rub2 gene Proteins 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 4

- 101150069431 rbr-2 gene Proteins 0.000 description 4

- 230000033228 biological regulation Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 101150111267 RBR1 gene Proteins 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/38—Transceivers, i.e. devices in which transmitter and receiver form a structural unit and in which at least one part is used for functions of transmitting and receiving

- H04B1/40—Circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/30—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters

- H03F1/301—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters in MOSFET amplifiers

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

Description

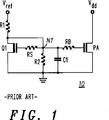

続している第1の抵抗R1は、第1のトランジスタQ1のバイアス電流を設定するためのものである。電力増幅器回路PAと第1および第2のトランジスタQ1,Q2とアースとの間のノードN1に接続している第2の抵抗R2は、降伏電圧を改善するためのものである。回路20も、RFブロッキング抵抗RbおよびRFデカップリング・キャパシタC1を有する。ブロッキング抵抗Rbおよびデカップリング・キャパシタC1は、RF信号がバイアス回路に進入するのを防止する。第1の設定抵抗RS1および第2の設定抵抗RS2は、RF・PA段と電流ミラー回路との間の漏洩電流による任意の電位差を設定するために使用される。第2の従来の電力増幅器回路20は、温度およびプロセスの変動をある程度補償することはできるが、回路20は、温度による電流の変動を補償し、高いRFドライブでのデバイアス効果に打ち勝つ十分な機能は持たない。さらに、第2の抵抗R2はすべての動作で非常に大量の電流を消費する。

めに、図面に好ましい実施形態を示す。しかし、本発明は図の正確な配置および手段に限定されない。

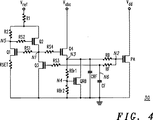

しているドレーンとを有する。第4のトランジスタQ4は、第2の基準電圧Vabcの供給を受けるために、第2の基準電圧源に接続しているドレーンと、第1のノードN1で第2のトランジスタQ2のソースおよび第1のトランジスタQ1のゲートに接続しているゲートとを有する。第1の基準電圧源が与える第1の基準電圧Vrefは、電力増幅器PAにバイアスをかけるために使用される出力電圧Vbiasを生成するために使用される調整用電圧である。第2の基準電圧源は、RF駆動条件下で電力増幅器PAに電流を供給するために使用される第2の基準電圧Vabcを与える。第1の基準電圧Vrefは、一定の電圧であっても可変電圧であってもよい。第2の基準電圧Vabcは、好適には、一定の電圧であることが好ましい。

動作安定化回路46は、1つまたはそれ以上のミラー(Miller)コンデンサを備えることができる。しかし、本発明の好ましい実施形態の場合には、動作安定化回路46は複数の抵抗を備える。より詳細に説明すると、動作安定化回路46は、第1のノードN1に接続している第1の端子と、第1のトランジスタQ1のゲートに接続している第2の端子を持つ第1の安定化抵抗RS1を含む。第2の安定化抵抗RS2は、第2のトランジスタQ2のゲートに接続している第1の端子と、第1のトランジスタQ1のドレーンと第2の抵抗R2の第2の端子との間の接続部により形成されている、第5のノードN5に接続している第2の端子を有する。第3の安定化抵抗RS3は、第3のトランジスタQ3のゲートに接続している第1の端子と、第6のノードN6に接続している第2の端子を有する。第6のノードN6は、フィードバック抵抗Rfの第2の端子とフィードバック・コンデンサCfとの間に位置している。第4の安定化抵抗RS4は、第1のノードN1に接続している第1の端子と、第4のトランジスタQ4のゲートに接続している第2の端子を有する。

ここで、

Idは、ドレーン電流であり、

κは、プロセス関連パラメータであり、

Vgsは、ゲート−ソース間電圧であり、

Vthは、しきい値電圧であり、

λは、チャネル変調パラメータであり、

Vdsは、ドレーン−ソース間電圧である。

∂Id/∂Vth=-2κ・(Vgs-Vth)・(1+λ・Vds) (2)

∂Id/∂Vgs=2κ・(Vgs-Vth)・(1+λ・Vds) (3)

さらに、IR2を表す下式を得ることができる。

事例1.温度変動

周囲温度が上昇すると、第3のトランジスタQ3のしきい値電圧Vthが低減する。式(2)から分かるように、しきい値電圧Vthが低減すると、Id3(すなわち、第3のトランジスタQ3のドレーン電流)は増大し、そのため、Id2も増大する。Id2が増大すると、Vd2が低減する。式(4)から分かるように、Vd2が低減すると、第2の抵抗R2を通る電流IR2が低減する。それ故、温度によるしきい値電圧Vthの変動は、PTAT電流源(Id2)およびCTAT電流源(IR2)を発生する。温度が上昇すると、Id2(PTAT電流源)が増大し、そのため電力増幅器PAを通る電流IPAが増大する。何故なら、IPAはId2のミラーであるからである。Id2の温度変化によるIPAの温度変化は、下式により表すことができる。

ここで、nは電力増幅器PAおよび第3のトランジスタQ3の全ゲート幅比である。

温度が上昇すると、IR2(CTAT電流源)が減少し、そのため、Id4が減少する。何故なら、ID4はIR2のミラーであるからである。Id4の温度変化は下式により表すことができる。

ここで、mはQ4およびQ1の全ゲート幅比である。

さらに、IR2の温度変化によるIPAの温度変化は、IR2の関数として入手することができる。その式は下記の通りである。

上記分析に基づいて、電力増幅器 PAバイアス電流を、温度によるIPAPTATおよびIPACTATの両方で調整することができる。テーブル1は、IPA特性上のR1およびR2変動の組合わせを示す。

RF駆動電力が増大すると、ゲート電流が増大し(すなわち、自己バイアス効果)、それによりRFブロッキング抵抗Rbの両端に電圧降下が起こる。このバイアス打ち消し効果により電力増幅器PAのトランスジューサ利得が低下し、それにより飽和出力電力およびPAEが低減する。RFブロッキング抵抗Rbの両端の電圧降下によりVgs3が低減する。式(1)から分かるように、Vgs3の電圧降下によりId2電流が低減し、それによりVd2が増大し、それによりIR2が増大する。IR2が増大すると、VRsetおよびId4が増大し、それによりVsetが増大し、それによりId4がさらに増大する。Vsetは第1のノードN1のところの電圧である。増大したId4は、RFブロッキング抵抗Rbの両端の電圧降下を補償するためにバイアス電圧Vbiasを押し上げる。

事例3.プロセスの変動

電流Id変動は、κ、λの変動よりVthの変動の影響を受けやすいので、κおよびλは一定であり、Vthの値はこの分析に対する通常の値よりも低いと仮定する。プロセスの変動によりVthの値が通常の値より低い場合には、Id2は、通常の値より高くなり、そのため、Vd2の値は通常の値より低くなる。Vd2が低減すると、IR2の値が通常の値より低くなり、Id4の値が通常の値より低くなる。Id4の値が低い場合には、

バイアス電圧Vbiasも低くなる。Vthが低い場合には、バイアス電圧Vbiasが通常の値より低くなり、Vthの値が高い場合には逆になる。バイアス電圧Vbiasおよびしきい値VthはIPAに対して反対の影響を持っているので、IPAの変動が低減する。

事例4.降伏電圧エンハンスメント・ネットワーク

電力増幅器PAのドレーン電圧が増大して降伏電圧に近づくと、QBRがオンになり、短絡したかまたは抵抗値が下がった状態になり、電力増幅器PAの降伏電圧が増大する。さらに、通常の動作状態の場合には、ネットワークは開ループのような動作をし、直流電力を消費しない。

Claims (3)

- 電力増幅器に接続されている能動バイアス回路であって、該電力増幅器が動作していない時に該電力増幅器へ流れる、零入力直流電流を広い温度範囲にわたってほぼ一定の値に維持するために、該電力増幅器に接続される第1および第2の電流ミラー回路を備え、該電力増幅器は、該第2の電流ミラー回路中の1つの素子であり、

前記第1の電流ミラー回路に第1の基準電圧Vrefを与えるための第1の基準電圧源と、

同第1の基準電圧源の第1の端子と、前記第1の電流ミラー回路中の第2のトランジスタのドレーンに接続している第2の端子と、に接続されている第1の抵抗R1からなる温度補償回路と、

前記第1の電流ミラー回路の第2のトランジスタに接続されている、第3のトランジスタからなる電流シンクと、

前記第1の電流ミラー回路に与えられる電圧を設定するために、第1のトランジスタのソースとアースとの間に接続している設定抵抗Rsetからなる電圧源調整回路と、を備え、

前記第1の電流ミラー回路が、

ソース、ドレーンおよびゲートを有する第1のトランジスタと、

前記第1のトランジスタのドレーンに接続しているゲートと、第1のノードで前記第1のトランジスタのゲートに接続しているソースを有する第2のトランジスタと、

第2の基準電圧源Vabcに接続し、第2の基準電圧の供給を受けるドレーンと、アースに接続しているソースと、前記第1のノードで前記第2のトランジスタのソースと前記第1のトランジスタのゲートに接続しているゲートとを有する第4のトランジスタと、

を備える能動バイアス回路。 - 前記第2の電流ミラー回路が、

前記第4のトランジスタと、

前記第1のノードに接続しているドレーンと、アースに接続しているソースと、第2のノードで前記電力増幅器のゲートに接続しているゲートとを有する第3のトランジスタと、

第3の基準電圧源Vddに接続し、第3の基準電圧の供給を受けるドレーンと、アースに接続しているソースとを有する前記電力増幅器と、

を備える請求項1に記載の能動バイアス回路。 - 電力増幅器が動作していない時に該電力増幅器へ流れる、電力増幅器の零入力直流電流を広い温度範囲にわたって一定の値に維持するための能動バイアス回路であって、

第1のトランジスタと、

同第1のトランジスタのドレーンに接続しているゲートと、第1の基準電圧Vrefの供給を受けるために、第1の基準電圧源に接続しているドレーンとを有する第2のトランジスタと、

第2の基準電圧Vabcの供給を受けるために、第2の基準電圧源に接続しているドレーンと、前記第2のトランジスタのソースと前記第1のトランジスタのゲートに接続しているゲートとを有する第4のトランジスタと、

を含む第1の電流ミラー回路と、

前記第4のトランジスタと、第1のノードで前記第2のトランジスタのソースに接続しているドレーンと、アースに接続しているソースとを有する第3のトランジスタと、

第3の基準電圧の供給を受けるために第3の基準電圧源Vddに接続しているドレーンと、アースに接続しているソースと、第2のノードで前記第3のトランジスタのゲート、および、第3のノードで降伏電圧抵抗RBを介して第4のトランジスタのソースに接続しているゲートと、を有する電力増幅器と、

を含む第2の電流ミラー回路と、

前記第1の基準電圧源に接続している第1の端子と前記第2のトランジスタのドレーンに接続している第2の端子とを有する第1の抵抗R1と、

前記第1の抵抗R1の第2の端子に接続し、前記第1のトランジスタのドレーンに接続している第2の端子を有する第2の抵抗R2と、を含む温度補償回路と、

前記第1のトランジスタのソースと前記アースとの間に接続している設定抵抗Rsetを含む電圧源調整回路と、

を備える能動バイアス回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/918,015 US6492874B1 (en) | 2001-07-30 | 2001-07-30 | Active bias circuit |

| PCT/US2002/020309 WO2003012980A1 (en) | 2001-07-30 | 2002-06-26 | Active bias circuit |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005526412A JP2005526412A (ja) | 2005-09-02 |

| JP2005526412A5 JP2005526412A5 (ja) | 2006-01-05 |

| JP4087336B2 true JP4087336B2 (ja) | 2008-05-21 |

Family

ID=25439654

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003518034A Expired - Fee Related JP4087336B2 (ja) | 2001-07-30 | 2002-06-26 | 能動バイアス回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6492874B1 (ja) |

| JP (1) | JP4087336B2 (ja) |

| KR (1) | KR100830361B1 (ja) |

| CN (1) | CN100502230C (ja) |

| WO (1) | WO2003012980A1 (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6831517B1 (en) * | 2002-12-23 | 2004-12-14 | Intersil Americas, Inc. | Bias-management system and method for programmable RF power amplifier |

| US6864748B2 (en) * | 2003-01-31 | 2005-03-08 | Lsi Logic Corporation | Differential current amplifier with common mode rejection and high frequency boost |

| JP2004274433A (ja) * | 2003-03-10 | 2004-09-30 | Mitsubishi Electric Corp | 高周波集積回路装置 |

| US6946912B2 (en) * | 2003-10-21 | 2005-09-20 | Northrop Grumman Corporation | MMIC distributed amplifier gate control using active bias |

| US6956437B2 (en) * | 2003-12-23 | 2005-10-18 | Agere Systems Inc. | Metal-oxide-semiconductor device having integrated bias circuit |

| JP4569165B2 (ja) * | 2004-05-13 | 2010-10-27 | ソニー株式会社 | バイアス回路およびこれを有する増幅回路ならびに通信装置 |

| US7057462B2 (en) * | 2004-05-28 | 2006-06-06 | Freescale Semiconductor, Inc. | Temperature compensated on-chip bias circuit for linear RF HBT power amplifiers |

| KR100605258B1 (ko) * | 2005-02-28 | 2006-07-31 | 삼성전자주식회사 | 초 저전력 소모 특성을 갖는 기준전압 발생회로 |

| TW200637139A (en) * | 2005-04-06 | 2006-10-16 | Richwave Technology Corp | Adaptive linear biasing circuit |

| US20070030064A1 (en) * | 2005-08-03 | 2007-02-08 | Yinglei Yu | Integrated laterally diffused metal oxide semiconductor power detector |

| US7274258B2 (en) * | 2005-09-08 | 2007-09-25 | Industrial Technology Research Institute | Dynamic bias circuit for a radio-frequency amplifier |

| WO2007051753A1 (fr) | 2005-11-04 | 2007-05-10 | Thomson Licensing | Élement electro-optique integrant une diode organique electroluminescente et un transistor organique de modulation de cette diode. |

| US7365604B2 (en) * | 2005-12-16 | 2008-04-29 | Mediatek Inc. | RF amplifier with a bias boosting scheme |

| WO2008074149A1 (en) * | 2006-12-21 | 2008-06-26 | Icera Canada ULC | Current controlled biasing for current-steering based rf variable gain amplifiers |

| JP2007329831A (ja) * | 2006-06-09 | 2007-12-20 | Matsushita Electric Ind Co Ltd | 増幅回路 |

| US7446612B2 (en) * | 2006-09-08 | 2008-11-04 | Skyworks Solutions, Inc. | Amplifier feedback and bias configuration |

| US7869775B2 (en) | 2006-10-30 | 2011-01-11 | Skyworks Solutions, Inc. | Circuit and method for biasing a gallium arsenide (GaAs) power amplifier |

| US8093952B2 (en) * | 2006-12-29 | 2012-01-10 | Broadcom Corporation | Method and system for precise current matching in deep sub-micron technology |

| JP4271708B2 (ja) * | 2007-02-01 | 2009-06-03 | シャープ株式会社 | 電力増幅器、およびそれを備えた多段増幅回路 |

| WO2009004534A1 (en) * | 2007-07-03 | 2009-01-08 | Nxp B.V. | Electronic device and a method of biasing a mos transistor in an integrated circuit |

| JP2009165100A (ja) * | 2007-12-11 | 2009-07-23 | Hitachi Metals Ltd | 高周波増幅器及び高周波モジュール並びにそれらを用いた移動体無線機 |

| JP5107272B2 (ja) * | 2009-01-15 | 2012-12-26 | 株式会社東芝 | 温度補償回路 |

| US8710812B1 (en) * | 2009-01-27 | 2014-04-29 | Xilinx, Inc. | Regulating a supply voltage provided to a load circuit |

| US9166533B2 (en) * | 2009-07-30 | 2015-10-20 | Qualcomm Incorporated | Bias current monitor and control mechanism for amplifiers |

| CN102006017B (zh) * | 2010-12-02 | 2013-11-06 | 无锡中普微电子有限公司 | 偏置电路及其功率放大电路 |

| CN102638230B (zh) * | 2011-02-10 | 2015-08-05 | 启碁科技股份有限公司 | 温度补偿装置及卫星信号接收系统 |

| US8665015B1 (en) * | 2012-08-17 | 2014-03-04 | Cambridge Silicon Radio Limited | Power amplifier circuit |

| JP6043599B2 (ja) * | 2012-11-15 | 2016-12-14 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | バイアス回路、および増幅装置 |

| JP5821876B2 (ja) * | 2013-03-05 | 2015-11-24 | 株式会社村田製作所 | 電力増幅モジュール |

| EP2779452B1 (en) * | 2013-03-13 | 2018-08-15 | Nxp B.V. | Switchable current source circuit and method |

| EP2922199B1 (en) * | 2014-03-17 | 2020-05-13 | Nxp B.V. | A bias circuit for a transistor amplifier |

| US9780736B1 (en) * | 2016-03-30 | 2017-10-03 | Synaptics Incorporated | Temperature compensated offset cancellation for high-speed amplifiers |

| US10224918B2 (en) * | 2016-12-07 | 2019-03-05 | Infineon Technologies Americas Corp. | Active gate bias driver |

| EP3611841B1 (en) * | 2018-08-13 | 2023-11-29 | Avago Technologies International Sales Pte. Limited | System and method for controlling the impact of process and temperature in passive signal detector for automotive ethernet |

| US10615893B1 (en) * | 2018-09-27 | 2020-04-07 | Intel Corporation | Transmitter with feedback control |

| KR102262903B1 (ko) | 2019-04-18 | 2021-06-09 | 삼성전기주식회사 | 듀얼 보상 기능을 갖는 바이어스 회로 및 증폭 장치 |

| CN115699568A (zh) | 2020-06-11 | 2023-02-03 | 株式会社索思未来 | 放大电路、差动放大电路、接收电路以及半导体集成电路 |

| EP4020798A1 (en) | 2020-12-23 | 2022-06-29 | Carrier Corporation | Oscillator circuit comprising surface integrated waveguide resonator |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3995228A (en) | 1975-09-26 | 1976-11-30 | Threshold Corporation | Active bias circuit for operating push-pull amplifiers in class A mode |

| US4220930A (en) | 1978-12-26 | 1980-09-02 | Rca Corporation | Quasi-linear amplifier with feedback-controlled idling currents |

| US4789842A (en) | 1987-11-23 | 1988-12-06 | Jiri Naxera | Composite transistor device with over-current protection |

| FR2623951B1 (fr) * | 1987-11-27 | 1990-03-09 | Thomson Hybrides Microondes | Amplificateur lineaire hyperfrequence a tres large bande passante |

| US4975632A (en) | 1989-03-29 | 1990-12-04 | Texas Instruments Incorporated | Stable bias current source |

| US5469111A (en) | 1994-08-24 | 1995-11-21 | National Semiconductor Corporation | Circuit for generating a process variation insensitive reference bias current |

| US5570065A (en) | 1994-08-26 | 1996-10-29 | Motorola, Inc. | Active bias for radio frequency power amplifier |

| US5608353A (en) | 1995-03-29 | 1997-03-04 | Rf Micro Devices, Inc. | HBT power amplifier |

| JP3039611B2 (ja) | 1995-05-26 | 2000-05-08 | 日本電気株式会社 | カレントミラー回路 |

| US5689211A (en) | 1996-02-14 | 1997-11-18 | Lucent Technologies Inc. | Quiescent current control for the output stage of an amplifier |

| US5724004A (en) * | 1996-06-13 | 1998-03-03 | Motorola, Inc. | Voltage bias and temperature compensation circuit for radio frequency power amplifier |

| US5986508A (en) | 1996-08-26 | 1999-11-16 | Nevin; Larry J. | Bias concept for intrinsic gain stabilization over temperature |

| US5854578A (en) | 1997-09-15 | 1998-12-29 | Motorola, Inc. | Active circuit having a temperature stable bias |

| US5949274A (en) | 1997-09-22 | 1999-09-07 | Atmel Corporation | High impedance bias circuit for AC signal amplifiers |

| JP4158214B2 (ja) | 1997-10-31 | 2008-10-01 | 沖電気工業株式会社 | 半導体集積回路 |

| KR100272508B1 (ko) | 1997-12-12 | 2000-11-15 | 김영환 | 내부전압(vdd) 발생회로 |

| FI105611B (fi) | 1998-03-13 | 2000-09-15 | Nokia Mobile Phones Ltd | Radiotajuusvahvistimet |

| US6091279A (en) | 1998-04-13 | 2000-07-18 | Lucent Technologies, Inc. | Temperature compensation of LDMOS devices |

| US6046642A (en) | 1998-09-08 | 2000-04-04 | Motorola, Inc. | Amplifier with active bias compensation and method for adjusting quiescent current |

| US6087820A (en) | 1999-03-09 | 2000-07-11 | Siemens Aktiengesellschaft | Current source |

| IT1313384B1 (it) * | 1999-04-28 | 2002-07-23 | St Microelectronics Srl | Schema di polarizzazione in modo corrente ad alta precisione e minimorumore per un transistore bipolare a giunzione con degenerazione ut |

| US6313705B1 (en) * | 1999-12-20 | 2001-11-06 | Rf Micro Devices, Inc. | Bias network for high efficiency RF linear power amplifier |

| US6300837B1 (en) * | 2000-03-28 | 2001-10-09 | Philips Electronics North America Corporation | Dynamic bias boosting circuit for a power amplifier |

| US6259324B1 (en) | 2000-06-23 | 2001-07-10 | International Business Machines Corporation | Active bias network circuit for radio frequency amplifier |

-

2001

- 2001-07-30 US US09/918,015 patent/US6492874B1/en not_active Expired - Lifetime

-

2002

- 2002-06-26 WO PCT/US2002/020309 patent/WO2003012980A1/en active Application Filing

- 2002-06-26 KR KR1020047001462A patent/KR100830361B1/ko active IP Right Grant

- 2002-06-26 JP JP2003518034A patent/JP4087336B2/ja not_active Expired - Fee Related

- 2002-06-26 CN CNB028150481A patent/CN100502230C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1537358A (zh) | 2004-10-13 |

| KR100830361B1 (ko) | 2008-05-20 |

| US6492874B1 (en) | 2002-12-10 |

| CN100502230C (zh) | 2009-06-17 |

| KR20040028963A (ko) | 2004-04-03 |

| JP2005526412A (ja) | 2005-09-02 |

| WO2003012980A1 (en) | 2003-02-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4087336B2 (ja) | 能動バイアス回路 | |

| US9584085B2 (en) | Amplifying system | |

| US6313705B1 (en) | Bias network for high efficiency RF linear power amplifier | |

| JP6229369B2 (ja) | 電力増幅器 | |

| US6549076B2 (en) | High-output amplifier | |

| KR101232407B1 (ko) | 이득 확장 스테이지를 가진 증폭기 | |

| KR20060114339A (ko) | 단일 칩 전력 증폭기 및 인벨롭 변조기 | |

| JP2004343244A (ja) | 高周波増幅回路 | |

| JP2004328107A (ja) | 高周波電力増幅用半導体集積回路および高周波電力増幅用電子部品並びに無線通信システム | |

| KR100843065B1 (ko) | 전력 증폭기 회로 | |

| US6414547B1 (en) | Variable gain RF amplifier | |

| JP2012199746A (ja) | ドハティ増幅器及びドハティ増幅器のバイアス設定方法 | |

| TW201901334A (zh) | 電流鏡裝置及相關放大電路 | |

| US6774724B2 (en) | Radio frequency power amplifier active self-bias compensation circuit | |

| US20140167854A1 (en) | Electronic system - radio frequency power amplifier and method for self-adjusting bias point | |

| US20040095192A1 (en) | Radio frequency power amplifier adaptive bias control circuit | |

| KR100712430B1 (ko) | 전계 효과 트랜지스터의 바이어스 회로 | |

| JP2010283556A (ja) | 高周波増幅器及びそれを用いた高周波モジュール | |

| JP4401776B2 (ja) | 自動バイアス供給源調節機構を有する可変利得増幅器 | |

| JP7171950B2 (ja) | 電力増幅装置 | |

| JP2002009559A (ja) | ベースバイアス回路及びこのベースバイアス回路を用いた電力増幅器 | |

| US6967533B2 (en) | Arrangement for saving energy in transmitter | |

| US8248166B2 (en) | Triplet transconductor | |

| US10454430B2 (en) | Circuit with voltage drop element | |

| JPH08511404A (ja) | 非線形増幅器用dcバイアス電流補償回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050608 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050608 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070927 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071002 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071225 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080220 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4087336 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110228 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120229 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130228 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130228 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140228 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |