JP4080129B2 - 電力用半導体スイッチのゲート駆動回路 - Google Patents

電力用半導体スイッチのゲート駆動回路 Download PDFInfo

- Publication number

- JP4080129B2 JP4080129B2 JP2000058216A JP2000058216A JP4080129B2 JP 4080129 B2 JP4080129 B2 JP 4080129B2 JP 2000058216 A JP2000058216 A JP 2000058216A JP 2000058216 A JP2000058216 A JP 2000058216A JP 4080129 B2 JP4080129 B2 JP 4080129B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor switch

- switching element

- power semiconductor

- state

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 132

- 239000003990 capacitor Substances 0.000 description 18

- 238000010586 diagram Methods 0.000 description 13

- 230000003071 parasitic effect Effects 0.000 description 11

- 230000015556 catabolic process Effects 0.000 description 5

- 239000011888 foil Substances 0.000 description 3

- 238000010992 reflux Methods 0.000 description 3

- 230000006378 damage Effects 0.000 description 2

- 230000001965 increasing effect Effects 0.000 description 2

- 230000008929 regeneration Effects 0.000 description 2

- 238000011069 regeneration method Methods 0.000 description 2

- 238000010276 construction Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000004146 energy storage Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- BULVZWIRKLYCBC-UHFFFAOYSA-N phorate Chemical compound CCOP(=S)(OCC)SCSCC BULVZWIRKLYCBC-UHFFFAOYSA-N 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/04—Modifications for accelerating switching

- H03K17/0403—Modifications for accelerating switching in thyristor switches

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Power Conversion In General (AREA)

Description

【産業上の利用分野】

本発明は、電力用半導体スイッチのゲート駆動回路、特に電力用半導体スイッチを鋭い立ち上がりで高速でオンするパルス駆動回路に関するものである。

【0002】

【従来の技術】

電力エネルギー分野の1つにパルス大電力技術がある。これは、ゆっくりと蓄積したエネルギーを1千万分の1秒というきわめて短い時間に1億ワット以上の瞬時パワーとして放出させるものであるが、できるだけ急速にエネルギーを放出させるために、高電圧でかつ超高速で動作するスイッチング素子が不可欠であり、この目的のためにギャップスイッチやサイラトロンが用いられている。しかし、これらのスイッチは高い繰り返し周波数で動作することに問題があると共に、寿命が短いという問題があった。

【0003】

最近、半導体デバイスの進歩により、比較的高電圧、大電流で高速スイッチング特性を持ったサイリスタ、静電誘導サイリスタ、ゲートターンオフサイリスタ(GTO)、絶縁ゲートバイポーラトランジスタ(IGBT)などの半導体スイッチング素子が提案され、実用化されるようになっている。これらの半導体スイッチング素子を複数個直列に接続したものは、パルスパワー用超高電圧電力用半導体スイッチとして使用できる可能性がある。

【0004】

このような電力用半導体スイッチをパルス駆動させるためには可能な限り高速でターンオンさせる必要がある。そのためのトリガ信号としては、ターンオンの初期の数十nsecの短時間、非常に高速で立ち上がる大きな電流をゲートに流し、その後、50μsec程度の間、1A程度の連続オン電流を流す必要がある。このように電力用半導体スイッチをパルス駆動するためのゲート駆動回路は従来幾つか提案されている。

【0005】

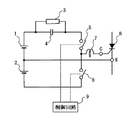

図1は、電力用半導体スイッチをパルス駆動するための従来のゲート駆動回路の一例を示すものである。直流電源として、オン用の直流電源1と、オフ用の直流電源2とが設けられている。オン用の直流電源1の両端には、抵抗3とコンデンサ4とが接続され、これら抵抗とコンデンサとの間の接続点は、オン用スイッチング素子5を経て制御すべき電力用半導体スイッチ6のゲートGに接続されている。直流電源からゲートに至る回路部分の合計寄生インダクタンスを、オン用スイッチング素子5と電力用半導体スイッチ6のゲートGとの間に接続したインダクタ7として表す。

【0006】

上述した抵抗3は、コンデンサ4に対する充電抵抗として動作すると共に、電力用半導体スイッチ6をオン状態に保持するための電流をゲートに供給するものである。さらに、電力用半導体スイッチ6のカソードKは、オン用直流電源1の負極に接続されており、オン用スイッチング素子5とインダクタ7との接続点は、オフ用スイッチング素子8を経てオフ用直流電源2の負極に接続されている。

【0007】

【発明が解決すべき課題】

図1に示した従来のゲート駆動回路の動作を、図2に示す信号波形を参照して説明する。電力用半導体スイッチ6がオフ状態に維持されているときは、制御回路9の制御の下でオン用スイッチング素子5(SW5)はオフ、オフ用スイッチング素子8(SW8)はオンとなっている。したがって、コンデンサ4は、オン用直流電源1から抵抗3を介してこの電源の電圧E1に充電されている。時刻t0において、オン用スイッチング素子5をオフからオンへ切り換えると、コンデンサ4に蓄えられていたエネルギーはこのスイッチング素子を経て電力用半導体スイッチ6のゲートGからカソードKへ流れることになる。このように電力用半導体スイッチ6のゲートGを流れる電流の最大値をI2で示す。このように大きな電流がゲートに流れるので、電力用半導体スイッチ6はターンオンする。その後ゲート電流が流れ続ける間、電力用半導体スイッチ6はオン状態を持続し、時刻t1においてオン用スイッチング素子5をオフ、オフ用スイッチング素子8をオンすることによりターンオフされる。

【0008】

ここで、オン用スイッチング素子5をオンとしたときにゲートに流れる電流iGの上昇率(diG/dt)は、オン用直流電源1の電圧E1と、図1においてインダクタ7で表されている寄生インダクタンスLSとによって決まる。すなわち、diG/dt=E1/LS で与えられる。この寄生インダクタンスLSは、通常100nH程度であり、またゲート電流iGの上昇率(diG/dt)は3000A/μsec以上が要求される。したがって、オン用直流電源1の電圧E1としては300V以上必要となる。

【0009】

一方、電力用半導体スイッチ6を高速でターンオンさせるために必要なゲートに供給する電荷量Qは決まっている。この電荷量Qはコンデンサ4に蓄えられている電荷量と等しく、これによるエネルギーは1/2×QE1で表される。このエネルギーを蓄えるために抵抗3で発生する損失も1/2×QE1となり、オン用直流電源1から供給されるエネルギーはこれらの合計に等しく、QE1となる。

【0010】

上述した電荷量Qを確保するコンデンサ4の容量を0.5μFとし、パルス駆動の繰り返し周波数を2KHzとすると、オン用直流電源1から供給される電力は90Wとなる。この電力に、電力用半導体スイッチ6を50μsecの間、連続的にオン状態に保持するための電力30Wを加えると、オン用直流電源1から供給される電力は120Wと非常に大きなものとなる。

【0011】

このように、電力用半導体スイッチ6を高速でターンオンさせてパルス駆動するためには、きわめて大きな電力を供給することができるオン用直流電源1が必要となり、ゲート駆動回路が複雑で、大型となり、コストも高いものとなる。

【0012】

図3は、従来の電力用半導体スイッチのゲート駆動回路の他の例を示すものであるが、第1図に示したものと比較すると、オン用直流電源1の正極と、オン用スイッチング素子5との間に、抵抗3とコンデンサ4との並列回路を接続した点が相違しているだけである。このようなゲート駆動回路の動作は、図1に示したものと殆ど同一であり、上述したところと同じ動作条件では、オン用直流電源1はきわめて大きな電力を供給できるものであるとする必要がある。

【0013】

上述したように、大電力用の半導体スイッチをパルス駆動するために、ターンオン時にゲートに急激に大電流を流そうとすると、ゲート電源容量が過大となり、多数の電力用半導体スイッチを直列接続するような用途では重大な問題となる。また、ゲート駆動回路での損失が大きいため、ゲート駆動回路が大型化し、システムの構築に支障を来すという問題もある。

【0014】

したがって、本発明の目的は、上述した従来の欠点を解消し、簡単な回路で、大きなゲート電流を急激に流して電力用半導体スイッチをパルス駆動できるゲート駆動回路を提供しようとするものである。

【0015】

【課題を解決するための手段】

本発明は、制御すべき電力用半導体スイッチをパルス駆動するゲート駆動回路において、一方の極が、電力用半導体スイッチの主電極に接続される直流電源と、前記電力用半導体スイッチの主電極とゲートとの間に接続されたリアクトルおよび第1のスイッチング素子の直列回路と、前記電力用半導体スイッチのゲートと直流電源の他方の極との間に接続された第2のスイッチング素子とを具え、前記電力用半導体スイッチをオフ状態に保つために、前記第1のスイッチング素子をオフ状態に、第2のスイッチング素子をオン状態に維持し、電力用半導体スイッチをターンオンする際には、前記第1のスイッチング素子をオフ状態からオン状態へ切換えて前記リアクトルにエネルギーを蓄えた後に、前記第2のスイッチング素子をオン状態からオフ状態に切換えて、前記リアクトルに蓄えたエネルギーを電力用半導体スイッチのゲートに急激に流すことによって電力用半導体スイッチをターンオンするように構成したことを特徴とするものである。

【0016】

このような本発明による電力用半導体スイッチのゲート駆動回路においては、前記リアクトルをエネルギー蓄積手段として用い、このリアクトルに出力電圧の低い直流電源から所要の電流となるまで流し、蓄積した誘導エネルギーを開放する際に生じる高い誘起電圧を利用して急激に立ち上がるゲート電流を電力用半導体スイッチのゲートに流すことにより、低電力損失で高性能の電力用半導体スイッチ用ゲート駆動回路を実現することができる。

【0017】

本発明によるゲート駆動回路の好適な実施例においては、前記第1および第2のスイッチング素子を半導体スイッチング素子で構成し、前記電力用半導体スイッチがオンとなった後にも、前記第1の半導体スイッチング素子をオン状態に継続して維持することによって電力用半導体スイッチをオン状態に保持するゲート電流を、前記リアクトルに蓄えられているエネルギーによって生成するように構成する。あるいはまた、前記第1のスイッチング素子と前記リアクトルとの接続点と、前記第2のスイッチング素子の前記直流電源の他方の極に接続された端子との間にフリーフォイルダイオードを接続し、前記電力用半導体スイッチがターンオンした後に、前記第1のスイッチング素子をオフ状態として、電力用半導体スイッチにゲート電流を流しつつ前記リアクトルに蓄えられているエネルギーを前記フリーフォイルダイオードを経て前記直流電源へ回生し、その後第1のスイッチング素子を再びオン状態として電力用半導体スイッチをオン状態に保持するためのゲート電流を、前記リアクトルに蓄えられているエネルギーによって生成するように構成することもできる。さらに、連続したパルス駆動を行うためには、前記第2の半導体スイッチング素子をオンとして電力用半導体スイッチをターンオフすると同時に、前記第1の半導体スイッチング素子をオフとして次のターンオン動作に備えるように構成することができる。

【0018】

また、本発明においては、前記第1のスイッチング素子を半導体スイッチング素子で構成すると共に、前記第2のスイッチング素子を、このスイッチング素子自身がオン状態からオフ状態に切り換わるときに、前記リアクトルの両端に発生される逆誘起電圧でブレークダウンする特性を有する半導体スイッチング素子で構成するのが好適である。また、前記第1の半導体スイッチング素子とリアクトルとの接続点と、前記直流電源の他方の端子との間にフリーホイールダイオードを接続し、前記第1の半導体スイッチング素子がオフしたときに、前記リアクトルの電流を流し続ける経路を確保し、リアクトルに過電圧が発生しないようにするのが好適である。

【0019】

本発明者は、特公平7-67271号公報において、電力用半導体スイッチを連続的にオン状態に保つための電流を、リアクトルと直列に接続されたスイッチング素子をチョッピング動作させて得るようにした駆動回路を提案している。このようにスイッチング素子をチョッピング動作させるためには、正側電源と負側電源との2つの電源が必要であり、電源回路が複雑となる。また、この駆動回路を、電力用半導体スイッチをパルス駆動するための駆動回路として用いることについても何ら示唆していない。すなわち、リアクトルへの電流を転流する際に、大きな逆誘起電圧が発生し、これが寄生インダクタンスに印加されることによって急激に立ち上がる電流をゲートに流すという本発明の基本的な動作原理については何も教示していない。

【0020】

【発明の実施の形態】

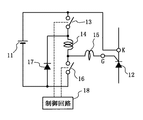

図4は、本発明による電力用半導体スイッチのゲート駆動回路の一実施例の基本的な構成を示す回路図である。直流電源11の正極を電力用半導体スイッチ12のカソードKに接続すると共に、この正極と電力用半導体スイッチ12のゲートGとの間に、オン用のスイッチング素子13とリアクトル14との直列回路を接続する。電力用半導体スイッチ12のゲートGとリアクトル14との間には寄生インダクタンスを表すインダクタ15が接続されている。さらに、リアクトル14とゲートGとの接続点と、直流電源11の負極との間にはオフ用のスイッチング素子16を接続する。また、オン用のスイッチング素子13とリアクトル14との接続点と、直流電源11の負極との間には、アノードを負極に接続したダイオード17を設ける。このダイオード17は、フリーホイールダイオードとして作用するものである。さらに、オン用スイッチング素子13およびオフ用スイッチング素子16のオンオフを制御する制御回路18を設ける。

【0021】

次に、図4に示すゲート駆動回路の動作を、図5に示す信号波形図をも参照して説明する。電力用半導体スイッチ12がオフ状態にあるときは、オン用スイッチング素子13(SW13)はオフ状態にあり、オフ用スイッチング素子16(SW16)はオン状態にある。この状態で、時刻t0において、制御回路18によりオン用スイッチング素子13をオフ状態からオン状態に切り換えると、直流電源11の正極から、スイッチング素子13、リアクトル14およびオフ用スイッチング素子16を経て直流電源の負極に至る回路が形成され、リアクトル14に流れる電流が直線的に増大していく。ここで、直流電源11の電圧をEとし、リアクトル14のインダクタンスをLとすると、リアクトルに流れる電流の勾配は、E/Lとなる。

【0022】

時刻t1において、リアクトル14を流れる電流が所望の値I1となるが、このとき制御回路18によってオフ用スイッチング素子16をオン状態からオフ状態に切り換えると、リアクトル14に流れていた電流が電力用半導体スイッチ12のゲートGへ転流しようとするが、上述したように、電力用半導体スイッチのカソードKとゲートGとの間に少なからず存在する寄生インダクタンス(図4ではインダクタ15で示す)のために、リアクトル14に流れていた電流が直ちに転流することはできず、したがってリアクトル14に大きな逆誘起電圧が発生する。

【0023】

このようにリアクトル14の両端間に発生する大きな逆誘起電圧は、オフ用スイッチング素子16に加わるが、このスイッチング素子は半導体スイッチング素子で構成されるので、最大定格電圧があり、これを越えると破損してしまうことになる。そこで、本発明の好適な実施例では、このオフ用のスイッチング素子16を半導体スイッチング素子で構成し、これを最大定格電圧でブレークダウンして、リアクトル14の誘導エネルギーの一部分を吸収する機能を持った半導体デバイスを用いる。このような半導体デバイスとしては、例えばインターナショナル社製のHEXFETがある。このような半導体スイッチング素子16のブレークダウン電圧をVBとすると、リアクトル14による逆誘起電圧は、(VB−E)に抑圧される。

【0024】

この電圧(VB−E)は、寄生インダクタンスLSを表すインダクタ15にも印加されるので、(VB−E)/LSの勾配で電流は立ち上がり、急激に増大していく。インダクタ14の電流がゲート電流と等しくなる時刻t2で、オフ用スイッチング素子16のブレークダウンは止まり、このスイッチング素子には電流が流れなくなるので、電力用半導体スイッチ12のゲート電流だけを流すようになる。このように、オフ用のスイッチング素子16がブレークダウンしている期間が、ゲート電流の上昇期間となる。

【0025】

上述した従来技術の説明と同様に、インダクタ15で表される寄生インダクタンスLSを100nHとし、ゲート電流iGの上昇率diG/dtを3000A/μsecとし、直流電源11の電圧Eを30Vとすると、ブレークダウン電圧VBは330Vとなるようにすれば良い。この期間におけるリアクトル14の電流の減少量を40A程度とすると、リアクトル14のインダクタンスLは、

(VB−E)×50nsec/40A=375nHとなる。

【0026】

したがって、時刻t1におけるリアクトル14の電流I1は190A必要となる。このとき、リアクトル14に蓄えられた電磁エネルギーは1/2×L×I1 2となり、これが直流電源11から供給される。この電力は、パルス動作の繰り返し周波数を上述した従来技術で説明したのと同じ2KHzとすると、1/2×375nH×1902×2KHz=13.5Wとなり、従来例の120Wの約1/9と非常に小さなものとなる。

【0027】

時刻t2以降は、リアクトル14から、電力用半導体スイッチ12のゲートG−カソードK−オン用スイッチング素子13の経路を経てリアクトル14の残留電磁エネルギー(=1/2×L×I2 2)による電流がゲート電流として環流し、回路による損失に応じて減衰していくが、連続オン電流として、従来例よりも大きな電荷量をゲートGに供給することができる。このように、本発明においては、電力用半導体スイッチ12をターンオンとした後、この状態を維持するためのエネルギーをリアクトル14の残留エネルギーから得るようにしており、直流電源11から供給しているものではない点も従来のものとの顕著な相違点である。

【0028】

時刻t5において、電力用半導体スイッチ12をターンオフするには、制御回路18によってオン用スイッチング素子13をオン状態からオフ状態とし、オフ用スイッチング素子16をオフ状態からオン状態とすることにより、電力用半導体スイッチのカソードKが直流電源11の正極に接続され、ゲートGが負極に接続されるので、電力用半導体スイッチのゲート・カソード間は逆バイアスされ、確実にターンオフすることができる。

【0029】

上述した実施例においては、図5に示すように、制御回路18によって、オン用スイッチング素子13は時刻t0においてオフからオンに切り換えられ、時刻t5においてオンからオフに切り換えられ、オフ用スイッチング素子16は時刻t1においてオンからオフに切り換えられ、時刻t5においてオフからオンへ切り換えるようにしている。したがって、電力用半導体スイッチ12がオンした後は、リアクトル14の磁気エネルギーは電力用半導体スイッチのゲート−カソード、オン用半導体装置13を通るルートで循環されているが、電力用半導体スイッチのゲートには不必要に大きな電流が流れることになる。このように大きなゲート電流は回路損失を招き、半導体装置のゲート駆動回路全体としての運転効率を低下させる要因となっている。

【0030】

図6は、本発明による電力用半導体スイッチのゲート駆動回路の他の実施例における動作を示すものである。本例の回路構成そのものは、図4に示したものと同じであるが、制御回路18によるオン用スイッチング素子13の駆動の仕方が相違している。したがって、その部分における動作を説明すれば足りるが、全動作について上述した実施例よりも詳細に説明する。

【0031】

モードIは電力用半導体スイッチ12が定常オフ状態にあるモードであり、オン用スイッチング素子13がオフ、オフ用スイッチング素子16がオンとなっており、電力用半導体スイッチ12のゲートGとカソードKとの間に直流電源11の電圧Eが、逆極性に印加されており、電力用半導体スイッチは確実にオフ状態を保っている。勿論、このモードIではリアクトル14の電流は零である。

【0032】

モードIIはターンオンの準備期間であり、電力用半導体スイッチ12を急峻なゲート電流でターンオンさせるために、予めリアクトル14にゲートに必要な電流を流しておくための期間である。このために、時刻t0において、制御回路18によってオン用スイッチング素子13をオンとして、リアクトル14に直流電源11の電圧Eを加えてリアクトルに電流をI1まで立ち上げる。

【0033】

次のモードIIIでは、時刻t1において制御回路18によってオフ用スイッチング素子16をオフとする。したがってリアクトル14を流れていた電流は電力用半導体スイッチ12のゲートへ転流しようとするが、このゲート周りに存在する寄生インダクタンスのために直ちには流れないので、リアクトル14の両端間には過大な逆誘起電圧が発生しようとする。上述したように、この逆電圧が高いほど、電力用半導体スイッチに流れるゲート電流のdi/dtは大きくなり好都合となるが、この電圧はオフ用スイッチング素子16にも印加されるので、このオフ用スイッチング素子の定格電圧を越えると、このスイッチング素子は破壊してしまう恐れがある。オフ用スイッチング素子16として、決まった電圧でブレークダウンし、サージ電力を吸収する能力があり、しかもオン抵抗も低いインターナショナル整流器社のパワーMOSFETを使用することにより、スイッチング素子の破壊の問題は解決できる。

【0034】

上述したオフ用スイッチング素子16のブレークダウン電圧をEbとすると、リアクトル14は(Eb−E)の電圧でクランプされる。また、この電圧は電力用半導体スイッチ12のゲート周辺の寄生インダクタンス15にも印加されるので、ゲート電流は急激に立ち上がり、リアクトル14を流れる電流に等しくなるとクランプ状態が解除されてこのモードIIIは終了する。この時間がゲート電流の立ち上がり時間となるので、従来と同等の立ち上がりdi/dt特性を有するゲート電流を流すためには、電圧(Eb−E)を300Vとする必要がある。したがって、このモードIIIの時間は、例えば50nsときわめて短いので、ブレークダウンで消費される瞬時パワーは大きいがエネルギーは大きくはない。また.モードIIIの終了時にリアクトル14を流れる電流はI2まで減少する。

【0035】

モードIVは第1の環流期間である。上述したクランプ期間が完了した後、ピークに達したゲート電流を直ちに減少させないように、時刻t1でオフ用スイッチング素子16をオフした後もオン用スイッチング素子13のオン状態を短時間持続させる。このとき、リアクタ14から電力用半導体スイッチ12のゲートG−カソードK、オン用スイッチング素子13を経て電流が還流することになるが、このような環流期間は必ずしも設ける必要はない。この環流期間の終了時にはリアクトル14を流れる電流はI3まで低下する。

【0036】

次のモードVが本実施例に特有のものである。すなわち、上述したモードIVで第1の環流期間を継続していくと、電力用半導体スイッチ12のゲートに必要以上の電荷を注入し、エネルギーを無駄に消費してしまうことになる。そこで、本実施例では、電力用半導体スイッチ12のゲートターンオンに必要な量の電荷の注入が行なわれたらリアクトル14のゲート電流を電力用半導体スイッチ12を連続的にオンするのに要するレベルまで急速に減少させるようにしている。すなわち、時刻t3において、オン用スイッチング素子13をオフとして、このスイッチング素子を流れていた電流をフリーホイールダイオード17へ転流して直流電源11へ回生するようしている。オン用スイッチング素子13をオフとすると、リアクトル14から電力用半導体スイッチ12のゲートG−カソードK−直流電源11−フリーホイールダイオード17−リアクトル14へと流れ、直流電源11に回生することになる。この回生期間の終了時にはリアクトル14の電流はI4まで減少する。

【0037】

次のモードVIは第2の環流期間であり、時刻t4においてオン用スイッチング素子13をオンとして、電力用半導体スイッチ12を連続的にオン状態に維持するためのゲート電流、すなわち連続オン電流I4 〜5(例えば1A程度)を必要な期間(例えば50μs程度)流し続けるものであり、減衰率はできるだけ小さくするのが望ましい。

【0038】

最後のモードVIIはオフ期間であって、制御回路18によって時刻t5において、オン用スイッチング素子13をオフとするとともにオフ用スイッチング素子16をオンとして電力用半導体スイッチ12をターンオフした後、このターンオフ状態を持続する。ここで、オフ用スイッチング素子16をオンすると、電力用半導体スイッチ12のゲート・カソード間に電源電圧Eが逆電圧として印加され、カソードからゲートへ向けてゲート引き抜き電流が流れ、電力用半導体スイッチを確実にターンオフさせることができる。パルスパワー回路に適用する場合には、このときには電力用半導体スイッチ12のアノード電流は零であるので、ゲート引き抜き電流は余り流れない。本例では、オフ用スイッチング素子16をオンすると同時にオン用スイッチング素子13をオフとしているが、このタイミングに多少の遅れや進みがあっても差し支えない。すなわち、これらのスイッチング素子13および16が同時にオンとなる状態が短時間存在しても、直列にリアクトル14が接続されているので、大きな短絡電流の発生を抑止することができる。上述したようにオフ用スイッチング素子16がオンすると、リアクトル14−スイッチング素子16−フリーホイールダイオード17−リアクトル14の経路が形成され、初期電流I5が環流し、リアクトル14の残留磁気エネルギーが回路の損失として無駄に消費されることになる。したがって、初期電流I5の大きさが決められているとすれば、リアクトル14のインダクタンス値を小さくするのが得策であることがわかる。

【0039】

図7は制御回路18の一例の構成を示す回路図、図8はその動作を示す波形図である。本例では、図8の最上段に示すような制御信号Sを入力してオン用スイッチング素子13およびオフ用スイッチング素子16に対する駆動信号を生成させている。図7に示すように、制御信号Sをインバータ21へ入力してその反転信号を生成する。制御信号Sは抵抗22およびダイオード23の並列回路を経てNAND回路24の一方の入力端子へ供給し、このNAND回路の他方の入力端子へはインバータ21から出力される反転信号を供給する。また、NAND回路24の一方の入力端子は抵抗22と相俟って放電時定数を決めるコンデンサ25に接続する。

【0040】

NAND回路24の出力端子を抵抗26およびダイオード27の並列回路を経てNAND回路28の一方の入力端子に接続し、このNAND回路の他方の入力端子にはインバータ21から出力される制御信号Sの反転信号を供給する。さらに、このNAND回路28の一方の入力端子は抵抗26と共に放電時定数を決めるコンデンサ29に接続する。NAND回路24からはオン用スイッチング素子14のオン信号が供給され、NAND回路28からはオフ用スイッチング素子16のオン信号が供給される。

【0041】

このような制御回路の基本的な構成は既知であると共に図8の波形図からその動作は理解できるので、以下簡単に説明する。時刻t0において制御信号Sが立ち上がり、その反転信号が立ち下がるためNAND回路24およびNAND回路28の一方の入力信号が「0」となり、コンデンサ25および29の電圧に関わらずNAND回路24の出力は引き続き「1」となり、NAND回路28の出力は「0」から「1」へ変化する。したがって時刻t0から再び反転信号ーSが「1」となる時刻t1の期間ではオン用スイッチング素子13とオフ用スイッチング素子16は同時にオンとなる。

【0042】

次に、時刻t 1 において制御信号Sが立ち下がると、その反転信号

が立ち上がり、一方時刻t0で急速充電されたコンデンサ25は抵抗22により放電され、時刻t5で閾値に達するまでは「1」とみなされるため、NAND回路24の出力信号は「0」へ変化し、オフ用スイッチング素子16をオフとする。これにより時刻t1まで充電されていたコンデンサ29は抵抗26により放電され、時刻t4で閾値に達するまでは「1」とみなされるためNAND回路28の出力信号が「0」へ変化し、オン用スイッチング素子13をオフとする。

【0043】

コンデンサ29の電圧が時刻t4において閾値に達すると、NAND回路28の出力信号は「1」に反転し、オン用スイッチング素子13のオン信号が「1」となる。その後、コンデンサ25の電圧が閾値に達した時刻t5においてNAND回路24の出力信号は「1」に反転し、オフ用スイッチング素子16のオン信号は「1」となると共にコンデンサ29がダイオード27により急速に充電されるためNAND回路28の出力信号も「0」に反転し、オン用スイッチング素子13のオン信号が「0」となる。

【0044】

上述したように、本例の制御回路においては、モードIIの開始時刻t0とモードIIIの開始時刻t1を規定する立ち上がりおよび立ち下がりを有する制御信号Sを用いることによって、それ以後のモードの開始タイミングを制御回路の抵抗およびコンデンサの時定数を適切に設定することによって決めることができる。

【0045】

本発明は上述した実施例にのみ限定されるものではなく、幾多の変更や変形が可能である。例えば、上述した実施例では電力用半導体スイッチとしてゲートターンオフサイリスタ(GTO)としたが、IGBT、サイリスタ、SIサイリスタ、バイポーラトランジスタなどの電力用半導体デバイスを用いることもできる。

【0046】

さらに、上述した実施例においては、オン用およびオフ用のスイッチング素子を用いているが、これは半導体素子が適しており、バイポーラトランジスタ、MOSFETなどの半導体スイッチング素子を用いることができる。また、フリーフォイルダイオードの代わりに半導体スイッチング素子を使用することもできる。

【0047】

【発明の効果】

上述したように、本発明による電力用半導体スイッチのゲート駆動回路によれば、簡単な回路でかつ小さい電力で、急激に増大するゲート電流を電力用半導体スイッチのゲートに流すことができる。

【0048】

また、第2の実施例においては、リアクトルの電流がピークに達した後に、オン用スイッチング素子をオフとすることによってリアクトルを流れる電流をフリーホイールダイオードを経て直流電源に流す電流回生期間を設けたため、リアクトルの磁気エネルギーを直流電源に回生することができ、電力消費を尚一層小さくすることができる。

【図面の簡単な説明】

【図1】従来の電力用半導体スイッチのゲート駆動回路の一例を示す回路図である。

【図2】同じくその動作を説明するための信号波形図である。

【図3】従来のゲート駆動回路の他の例を示す回路図である。

【図4】本発明による電力用半導体スイッチのゲート駆動回路の一実施例を示す回路図である。

【図5】同じくその動作を説明するための信号波形図である。

【図6】本発明による電力用半導体スイッチのゲート駆動回路の他の実施例における動作を示す信号波形図である。

【図7】本発明による電力用半導体スイッチのゲート駆動回路の制御回路の一例の構成を示す回路図である。

【図8】同じくその動作を説明するための信号波形図である。

【符号の説明】

11 直流電源、 12 電力用半導体スイッチ、 13 オン用スイッチング素子、 14 リアクトル、 15 寄生インダクタ、 16 オフ用スイッチング素子、 17 フリーホイールダイオード、18 制御回路、 21 インバータ、 22、26 抵抗、 23、27 ダイオード、 24、28 NAND回路、 25、29 コンデンサ

Claims (4)

- 制御すべき電力用半導体スイッチをパルス駆動するゲート駆動回路において、一方の極が、電力用半導体スイッチの主電極に接続される直流電源と、前記電力用半導体スイッチの主電極とゲートとの間に接続されたリアクトルおよび第1のスイッチング素子の直列回路と、前記電力用半導体スイッチのゲートと直流電源の他方の極との間に接続された第2のスイッチング素子とを具え、前記第1のスイッチング素子を半導体スイッチング素子で構成すると共に、前記第2のスイッチング素子を、このスイッチング素子自身がオン状態からオフ状態に切り換わるときに、前記リアクトルの両端に発生される逆誘起電圧でブレークダウンする特性を有する半導体スイッチング素子で構成し、前記電力用半導体スイッチをオフ状態に保つために、前記第1のスイッチング素子をオフ状態に、第2のスイッチング素子をオン状態に維持し、電力用半導体スイッチをターンオンする際には、前記第1のスイッチング素子をオフ状態からオン状態へ切換えて前記リアクトルにエネルギーを蓄えた後に、前記第2のスイッチング素子をオン状態からオフ状態に切換えて、前記リアクトルに蓄えたエネルギーを電力用半導体スイッチのゲートに急激に流すことによって電力用半導体スイッチをターンオンするように構成したことを特徴とする電力用半導体スイッチのゲート駆動回路。

- 前記電力用半導体スイッチがターンオンした後にも、前記第1のスイッチング素子を継続してオン状態に維持することによって電力用半導体スイッチをオン状態に保持するためのゲート電流を、前記リアクトルに蓄えられているエネルギーによって生成するように構成したことを特徴とする請求項1に記載の電力用半導体スイッチのゲート駆動回路。

- 前記第2のスイッチング素子をオフ状態からオン状態に切換えて電力用半導体スイッチをターンオフするのと同時に、前記第1のスイッチング素子をオン状態からオフ状態に切換えて次のターンオン動作に備えるように構成したことを特徴とする請求項2に記載の電力用半導体スイッチのゲート駆動回路。

- パルス駆動すべき電力用半導体スイッチのカソードに接続された直流電源の正極と、電力用半導体スイッチのゲートとの間にオン用半導体スイッチング素子とリアクトルとの直列回路を接続すると共に、前記オン用半導体スイッチング素子とリアクトルとの接続点と、前記直流電源の負極との間に、負極側がアノードとなるようにフリーホイールダイオードを接続し、前記電力用半導体スイッチのゲートと前記直流電源の負極との間にオフ用の半導体スイッチング素子を接続して構成し、前記電力用半導体スイッチがターンオンした後に、前記オン用半導体スイッチング素子をオフ状態として、電力用半導体スイッチにゲート電流を流しつつ前記リアクトルに蓄えられているエネルギーを前記フリーホイールダイオードを経て前記直流電源へ回生し、その後オン用半導体スイッチング素子を再びオン状態として電力用半導体スイッチをオン状態に保持するためのゲート電流を、前記リアクトルに蓄えられているエネルギーによって生成するように構成したことを特徴とする電力用半導体スイッチのゲート駆動回路。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000058216A JP4080129B2 (ja) | 1999-07-15 | 2000-03-03 | 電力用半導体スイッチのゲート駆動回路 |

| KR10-2000-0039920A KR100385789B1 (ko) | 1999-07-15 | 2000-07-12 | 전력용 반도체 스위치의 게이트 구동 회로 |

| US09/615,301 US6268754B1 (en) | 1999-07-15 | 2000-07-13 | Gate driving circuit for power semiconductor switch |

| EP00306006A EP1069683B1 (en) | 1999-07-15 | 2000-07-14 | Gate driving circuit for power semiconductor switch |

| DE60005758T DE60005758T2 (de) | 1999-07-15 | 2000-07-14 | Ansteuerschaltung für einen Leistungshalbleiterschalter |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP11-201163 | 1999-07-15 | ||

| JP20116399 | 1999-07-15 | ||

| JP2000058216A JP4080129B2 (ja) | 1999-07-15 | 2000-03-03 | 電力用半導体スイッチのゲート駆動回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001086733A JP2001086733A (ja) | 2001-03-30 |

| JP2001086733A5 JP2001086733A5 (ja) | 2005-10-27 |

| JP4080129B2 true JP4080129B2 (ja) | 2008-04-23 |

Family

ID=26512612

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000058216A Expired - Fee Related JP4080129B2 (ja) | 1999-07-15 | 2000-03-03 | 電力用半導体スイッチのゲート駆動回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6268754B1 (ja) |

| EP (1) | EP1069683B1 (ja) |

| JP (1) | JP4080129B2 (ja) |

| KR (1) | KR100385789B1 (ja) |

| DE (1) | DE60005758T2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4565773B2 (ja) * | 2001-05-31 | 2010-10-20 | 日本碍子株式会社 | 高電圧パルス発生回路 |

| US7183740B2 (en) * | 2003-06-05 | 2007-02-27 | Toyota Jidosha Kabushiki Kaisha | Motor drive apparatus, vehicle having the same mounted therein, and computer readable storage medium having a program stored therein to cause computer to control voltage conversion |

| US7458504B2 (en) * | 2006-10-12 | 2008-12-02 | Huhtamaki Consumer Packaging, Inc. | Multi walled container and method |

| JP5258706B2 (ja) * | 2009-08-25 | 2013-08-07 | 東芝三菱電機産業システム株式会社 | 半導体電力変換装置のゲート駆動回路 |

| US8830647B2 (en) | 2012-05-24 | 2014-09-09 | Mersen Usa Newburyport-Ma, Llc | Fault current limiter |

| EP2793397B1 (en) * | 2013-04-19 | 2016-01-13 | ABB Technology AG | Current switching device with IGCT |

| RU2605454C1 (ru) * | 2015-08-19 | 2016-12-20 | Акционерное общество "ТВЭЛ" (АО "ТВЭЛ") | Адаптивное устройство для управления силовым тиристором |

| KR102327683B1 (ko) * | 2019-12-26 | 2021-11-17 | 엘지전자 주식회사 | 전력 변환 장치 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4136382A (en) * | 1978-01-18 | 1979-01-23 | Exxon Research & Engineering Co. | Converter system |

| JPS5545276A (en) | 1978-09-27 | 1980-03-29 | Hitachi Ltd | Gate circuit of gate turn-off thyristor |

| JPS59172969A (ja) * | 1983-03-22 | 1984-09-29 | Toyo Electric Mfg Co Ltd | 自己消弧形サイリスタのゲート駆動回路 |

| JPS6022464A (ja) * | 1983-07-15 | 1985-02-04 | Hitachi Ltd | 自己消弧形半導体素子のゲ−ト回路 |

| JPS627774U (ja) * | 1985-06-28 | 1987-01-17 | ||

| DE8718008U1 (de) | 1987-03-20 | 1993-02-18 | Leonhard, Reimund, Dipl.-Ing., 8043 Unterföhring | Steuerschaltung für einen stromgesteuerten Leistungshalbleiter |

| JPH0767271B2 (ja) | 1989-01-31 | 1995-07-19 | 東洋電機製造株式会社 | トランジスタのベース駆動回路 |

| JPH08107667A (ja) * | 1994-10-07 | 1996-04-23 | Hitachi Ltd | 自己消弧形素子の駆動回路 |

| JPH0937543A (ja) | 1995-07-19 | 1997-02-07 | Toshiba Corp | ゲート回路 |

| US5734258A (en) * | 1996-06-03 | 1998-03-31 | General Electric Company | Bidirectional buck boost converter |

| US5742146A (en) * | 1996-12-03 | 1998-04-21 | Magnetek, Inc. | Drive circuit for a switched reluctance motor with improved energy recovery using a common dump capacitor and recovering phase circuit |

| SG66453A1 (en) * | 1997-04-23 | 1999-07-20 | Int Rectifier Corp | Resistor in series with bootstrap diode for monolithic gate device |

| KR100292485B1 (ko) * | 1997-12-27 | 2001-07-12 | 구자홍 | 에스알모터의구동회로 |

-

2000

- 2000-03-03 JP JP2000058216A patent/JP4080129B2/ja not_active Expired - Fee Related

- 2000-07-12 KR KR10-2000-0039920A patent/KR100385789B1/ko not_active Expired - Fee Related

- 2000-07-13 US US09/615,301 patent/US6268754B1/en not_active Expired - Fee Related

- 2000-07-14 EP EP00306006A patent/EP1069683B1/en not_active Expired - Lifetime

- 2000-07-14 DE DE60005758T patent/DE60005758T2/de not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| KR20010049768A (ko) | 2001-06-15 |

| EP1069683B1 (en) | 2003-10-08 |

| DE60005758D1 (de) | 2003-11-13 |

| EP1069683A2 (en) | 2001-01-17 |

| EP1069683A3 (en) | 2001-05-02 |

| JP2001086733A (ja) | 2001-03-30 |

| US6268754B1 (en) | 2001-07-31 |

| KR100385789B1 (ko) | 2003-06-02 |

| DE60005758T2 (de) | 2005-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3811681B2 (ja) | 高電圧パルス発生回路 | |

| JP3812353B2 (ja) | 半導体電力変換装置 | |

| US7919887B2 (en) | High repetitous pulse generation and energy recovery system | |

| CN101154880B (zh) | 抑制浪涌电压的半导体器件 | |

| JP4837336B2 (ja) | ゲート指令装置、電動機指令機器及びターンオフ指令方法 | |

| US6426666B1 (en) | Diode-assisted gate turn-off thyristor | |

| JP2003052178A (ja) | 3レベルインバータ装置 | |

| EP2801153B1 (en) | Apparatus and method for control of semiconductor switching devices | |

| JP3978312B2 (ja) | サイリスタ用ゲートドライバ | |

| JP4080129B2 (ja) | 電力用半導体スイッチのゲート駆動回路 | |

| JP3261911B2 (ja) | 半導体装置のスナバ回路 | |

| JP4506276B2 (ja) | 自己消弧形半導体素子の駆動回路 | |

| Klaka et al. | A family of reverse conducting gate commutated thyristors for medium voltage drive applications | |

| US6069472A (en) | Converter/inverter using a high efficiency switching circuit | |

| JP3569192B2 (ja) | 半導体電力変換装置 | |

| JP2003033044A (ja) | スナバ回路 | |

| JPH10209832A (ja) | 半導体スイッチ回路 | |

| US7733067B2 (en) | Burst frequency resonant inverter | |

| EP1421662A1 (en) | An electrical apparatus and a limiting method | |

| Giannakis et al. | A Three-Level Voltage-Source Gate Driver for SiC MOSFETs in Synchronous Rectification Mode | |

| JP4113405B2 (ja) | 半導体素子のゲート駆動回路及び半導体装置 | |

| SU1629937A1 (ru) | Устройство дл выключени тиристора | |

| GB2050738A (en) | Switching inductive loads | |

| Burgum | The GTO—a new power switch | |

| Li et al. | A novel approach for realizing hard-driven gate-turn-off thyristor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050901 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050901 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070824 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070918 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120215 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130215 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130215 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |