JP4079658B2 - 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 - Google Patents

2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 Download PDFInfo

- Publication number

- JP4079658B2 JP4079658B2 JP2002058517A JP2002058517A JP4079658B2 JP 4079658 B2 JP4079658 B2 JP 4079658B2 JP 2002058517 A JP2002058517 A JP 2002058517A JP 2002058517 A JP2002058517 A JP 2002058517A JP 4079658 B2 JP4079658 B2 JP 4079658B2

- Authority

- JP

- Japan

- Prior art keywords

- gain

- circuit

- wobble signal

- write clock

- recording

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B27/00—Editing; Indexing; Addressing; Timing or synchronising; Monitoring; Measuring tape travel

- G11B27/10—Indexing; Addressing; Timing or synchronising; Measuring tape travel

- G11B27/19—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier

- G11B27/24—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by sensing features on the record carrier other than the transducing track ; sensing signals or marks recorded by another method than the main recording

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B7/00—Recording or reproducing by optical means, e.g. recording using a thermal beam of optical radiation by modifying optical properties or the physical structure, reproducing using an optical beam at lower power by sensing optical properties; Record carriers therefor

- G11B7/004—Recording, reproducing or erasing methods; Read, write or erase circuits therefor

- G11B7/005—Reproducing

- G11B7/0053—Reproducing non-user data, e.g. wobbled address, prepits, BCA

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B2220/00—Record carriers by type

- G11B2220/20—Disc-shaped record carriers

- G11B2220/21—Disc-shaped record carriers characterised in that the disc is of read-only, rewritable, or recordable type

- G11B2220/215—Recordable discs

- G11B2220/216—Rewritable discs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B2220/00—Record carriers by type

- G11B2220/20—Disc-shaped record carriers

- G11B2220/25—Disc-shaped record carriers characterised in that the disc is based on a specific recording technology

- G11B2220/2537—Optical discs

- G11B2220/2562—DVDs [digital versatile discs]; Digital video discs; MMCDs; HDCDs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B7/00—Recording or reproducing by optical means, e.g. recording using a thermal beam of optical radiation by modifying optical properties or the physical structure, reproducing using an optical beam at lower power by sensing optical properties; Record carriers therefor

- G11B7/24—Record carriers characterised by shape, structure or physical properties, or by the selection of the material

- G11B7/2407—Tracks or pits; Shape, structure or physical properties thereof

- G11B7/24073—Tracks

- G11B7/24082—Meandering

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Optical Recording Or Reproduction (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

Description

【発明の属する技術分野】

本発明は、2値化ウォブル信号を生成する回路、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成回路、2値化ウォブル信号を生成する方法、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成方法及びライトクロック生成回路を備える光ディスク装置に関する。

【0002】

【従来の技術】

光ピックアップから出力されるレーザ光を用いて、光ディスクに情報を記録したり、光ディスクに記録されている情報を再生したりする情報記録再生装置(光ディスク装置)が実用化されている。

【0003】

ここに、近年、パーソナルコンピュータ(PC)は、その機能が向上するに伴い、音楽や映像といったAV(Audio-Visual)情報を取り扱うことが可能となってきている。これらのAV情報の情報量は非常に大きいために、情報の記録媒体として光ディスクが注目されるようになり、その低価格化とともに、光ディスク装置がPCの周辺機器の一つとして普及するようになってきている。

【0004】

一般に、CD−R/RW(Compact Disc−Recordable/Rewritable)、DVD(Digital Versatile Disc)−R/RW、DVD+R/RW等の記録可能な記録系メディアでは、各半径位置における線速度を正確に検出するために、線速度一定(Constant Linear Velocity)方式で回転制御を行った時にメディア上に刻まれたトラックの蛇行(ウォブル)から検出されるウォブル信号の周波数が一定になるようなフォーマットを採用している。

【0005】

このようなウォブル信号は、再生/記録の動作に関わらず常に検出する必要があるが、メディアに記録されたデータや記録のためのレーザ変調成分がノイズとなり、ウォブル品質を低下させる不具合がある。即ち、ウォブル信号はトラックからの反射光に含まれているが、光ディスクに記録されている記録データやレーザ光の出力変動などにより、反射光には、ウォブル信号に対してノイズとなる成分が複雑に含まれている。

【0006】

そこで、このようなウォブル信号は、一般に、例えばトラックからの反射光をトラック接線方向に関して2分割された分割受光素子で受光し、各分割受光素子の出力信号(光電変換信号)の差を求めることによりノイズ成分を除去し、ウォブル信号を抽出するようにしている。

【0007】

ところが、現実には、分割受光素子が出荷前にはトラックからの反射光が分割受光素子の受光面の中央に位置するように位置調整されていても、稼動中の温度変化や振動などによる経時変化等によって、反射光の受光位置が受光面の中央からずれるようなケースもある。このようなケースでは、各受光素子の出力信号に含まれるノイズ成分が異なるため、受光素子間の出力信号の差を求めてもノイズ成分が残ってしまう等の不具合がある。

【0008】

このような不具合を改善するため、例えば、特開平8−194969号公報によれば、トラック接線方向に分割された分割受光素子の出力信号の各々に対して、信号の振幅を正規化する、いわゆる振幅一定AGC(自動ゲイン制御)を行ない、その差分によってウォブル信号を生成することで、データ信号成分がきれいに除去されたウォブル信号の検出方法が公開されている。また、同公報によれば、未記録時にはデータ信号成分を除去する必要がないため、振幅一定AGC回路を使用しない系も備えており、データの既記録/未記録に応じて使い分けるようにしている。

【0009】

【発明が解決しようとする課題】

このような特開平8−194969号公報に示されるウォブル検出方法の場合、再生時には高品質なウォブル信号を得ることはできるが、記録中は対象外でありウォブル信号品質は低下してしまう。

【0010】

特に、再生から記録への動作切換えに伴う記録開始時に関しては、何ら考慮されておらず、このような記録開始時にも良好なウォブル信号を得ることはできず、このウォブル信号に基づくライトクロックの生成も適正に行えない。即ち、再生時と記録時とでは、元々、レーザパワーが異なり、検出されるウォブル成分のレベルも異なるので、動作切換え時の制御を適正に行わないと、後述するように、2値化ウォブル信号のスライス電圧のずれ(例えば、ヒステリシス)などにより、ジッタ(時間軸方向の振れ)を生じ、PLL回路におけるライトクロックのロック外れや不安定動作などを生じてしまう。

【0011】

本発明は、再生動作から記録動作への切換え時においてもウォブル信号を高精度に検出することができ、ジッタの少ない適正なライトクロックを生成することができるライトクロック生成回路及び光ディスク装置を提供することを目的とする。

【0012】

本発明は、上記目的を実現する上で、回路規模をより小さくすることができるライトクロック生成回路を提供する。

【0013】

本発明は、上記目的を実現する上で、メディアの記録状態(未記録/既記録)に左右されないライトクロック生成回路を提供する。

【0014】

本発明は、上記目的を実現する上で、PLL回路のロック外れを確実に防止し、かつ、ジッタが小さくて良好なライトクロックを生成することができるライトクロック生成回路を提供する。

【0015】

【課題を解決するための手段】

請求項1記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号を生成する回路において、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する2つの可変ゲインアンプと、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る減算器と、を備える。

請求項10記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号を生成する方法において、2つの可変ゲインアンプによって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する工程と、ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、減算器によって、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る工程と、を備える。

請求項2記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成回路において、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する2つの可変ゲインアンプと、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る減算器と、この減算器から出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、この2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成するPLL回路と、を備える。

請求項11記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成方法において、2つの可変ゲインアンプによって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する工程と、ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、減算器によって、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る工程と、ウォブル振幅一定AGC回路によって、この減算器から出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、PLL回路によって、前記2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成する工程と、を備える。

【0016】

従って、請求項2,11記載の発明によれば、記録開始直後の一定期間に、分割受光素子後段の可変ゲインアンプのゲインをゲインコントロール回路により再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように変化させて得られたウォブル信号よりライトクロックを生成しているので、記録開始直前から記録開始直後へのウォブル信号の変化を抑えて、ウォブル信号振幅一定AGCのゲイン変動を緩やかすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成でき、また、可変ゲインアンプのゲインの段階的な変化の最終変更後は記録中に適正な信号レベルを維持できるので、安定したライトクロック生成が行なえる。

【0017】

請求項3記載の発明は、メディア上に形成されたトラックの蛇行に基づく2値化ウォブル信号を生成する回路において、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る減算器と、この減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する可変ゲインアンプと、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、を備える。

請求項12記載の発明は、メディア上に形成されたトラックの蛇行に基づく2値化ウォブル信号を生成する方法において、減算器によって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る工程と、可変ゲインアンプによって、前記減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する工程と、ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、ウォブル振幅一定AGC回路によって、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、を備える。

請求項4記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成回路において、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る減算器と、この減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する可変ゲインアンプと、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、この2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成するPLL回路と、を備える。

請求項13記載の発明は、メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成方法において、減算器によって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る工程と、可変ゲインアンプによって、前記減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する工程と、ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、ウォブル振幅一定AGC回路によって、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、PLL回路によって、前記2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成する工程と、を備える。

【0018】

従って、請求項4,13記載の発明によれば、記録開始直後の一定期間中に、減算器後段の可変ゲインアンプのゲインをゲインコントロール回路により再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように変化させて得られたウォブル信号よりライトクロックを生成しているので、請求項2、11記載の発明より回路規模が小さいながら同様の作用・効果が得られる。

【0020】

従って、記録開始直後は可変ゲインアンプに入力されるウォブル信号が大きいため、一旦ゲインを再生時のゲインレベルよりも小さく設定しておくことにより、再生動作中と変わらないウォブル信号を得ることができる一方、定常状態後の記録動作中にはノイズ成分も大きいことから可変ゲインアンプのゲインは大きいことが好ましいことから、再生時のゲインレベルまで段階的にゲインを大きくすることにより、確実にウォブル信号を得ることができ、適正なライトクロックの生成が可能となる。

【0021】

請求項5記載の発明は、請求項2又は4記載のライトクロック生成回路において、前記ゲインコントロール回路は、記録開始直後の一定期間中には前記ウォブル振幅一定AGC回路が追従可能な範囲で前記可変ゲインアンプのゲインステップとその時間間隔とを段階的に可変させる。

【0022】

従って、可変ゲインアンプのゲインの段階的な可変に対してウォブル振幅一定AGC回路の追従が確実となり、ライトクロック生成動作を適正に行わせることができる。

【0023】

請求項6記載の発明は、請求項2,4又は5記載のライトクロック生成回路において、前記ゲインコントロール回路は、記録開始直前のウォブル信号の振幅と記録開始直後のウォブル信号の振幅とが同等となるように、記録開始位置直前が未記録領域か既記録領域かに応じて記録開始前の前記可変ゲインアンプのゲインを切換える。

【0024】

従って、記録開始位置直前の領域が未記録領域か既記録領域かによって記録開始前の可変ゲインアンプのゲインを切換え、記録開始直前のウォブル信号の振幅と記録開始直後のウォブル信号の振幅とが同等となるようにしているので、メディアの記録状態(未記録/既記録)に関わらず、記録直前から記録開始直後へのウォブル信号の変化を抑えて、ウォブル信号振幅一定AGCのゲイン変動を緩やかすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成できる。

【0025】

請求項7記載の発明は、請求項2,4,5又は6記載のライトクロック生成回路において、記録開始直後の一定期間中には前記PLL回路のループゲインを上げるようにして前記PLL回路のループゲインを決定するPLLゲインコントロール回路を備える。

【0026】

従って、記録開始直後の一定期間中にはPLL回路のループゲインを上げるようにしているので、ウォブル信号の変化が大きいと予想される期間のみPLL回路の引込み能力を高めてロック外れを防ぐと共に、ウォブル信号が安定した段階ではジッタが小さくて良好なライトクロックを生成することができる。

【0027】

請求項8記載の発明は、請求項7記載のライトクロック生成回路において、前記PLLゲインコントロール回路は、記録開始直後の一定期間中には前記PLL回路のループゲインを一旦高いゲインに設定し、その後、低いゲインに切換えるように可変させる。

【0028】

従って、記録開始直後はPLL回路のループゲインを一旦高いゲインに設定することにより、再生から記録への切換え時にウォブル信号の品質や振幅の変化に起因して2値化ウォブル信号に高域周波数変動が発生してもウォブル信号のロック外れを確実に防止でき、ウォブル信号が安定した段階では低いゲインに切換えることによりジッタが小さくて良好なライトクロックを生成することができる。

【0029】

請求項9記載の発明は、請求項8記載のライトクロック生成回路において、前記PLLゲインコントロール回路は、前記PLL回路のループゲインを高いゲインから低いゲインに段階的に可変させる。

【0030】

従って、記録開始直後はPLL回路のループゲインを高いゲインに設定することにより、再生から記録への切換え時にウォブル信号の品質や振幅の変化に起因して2値化ウォブル信号に高域周波数変動が発生してもウォブル信号のロック外れを確実に防止でき、ウォブル信号が安定する段階に向けて段階的に低いゲインに切換えることによりジッタが小さくて良好なライトクロックを生成することができる。

【0031】

請求項14記載の発明の光ディスク装置は、記録面に蛇行させたトラックが形成されたメディアを回転させる回転駆動機構と、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子、及び、前記メディアに対してレーザ光を照射するレーザ光源を有する光ピックアップと、前記光源の発光動作を制御する光源駆動回路と、前記分割受光素子から出力される信号が入力されて前記光源駆動回路側に対してライトクロックを出力する請求項2,4,5,6,7,8又は9記載のライトクロック生成回路と、を備える。

【0032】

従って、請求項2,4,5,6,7,8又は9記載のライトクロック生成回路を用いているので、PLL回路のロック外れによる記録失敗を生ずることがなく、かつ、記録開始時の記録品質が低下することのない光ディスク装置を提供できる。

【0033】

【発明の実施の形態】

本発明の第一の実施の形態を図1ないし図6に基づいて説明する。まず、図1に基づいて本発明が適用される光ディスク装置の構成・作用の概略を説明する。

【0034】

まず、CD−R/RW,DVD±R/RW等の記録可能なメディア1を回転させる回転駆動機構の主要部を構成するスピンドルモータ2が設けられている。また、回転駆動されるメディア1に対してレーザ光源(図示せず)からののレーザ光のスポットを照射し、メディア1からの反射光を後述する分割受光素子で検出する光ピックアップ3が設けられている。

【0035】

この光ピックアップ3には、検出された再生信号のフィルタリングやデジタル化を行う再生回路4と、この再生回路4で生成されたユーザデータ成分のデータフォーマットを変換するデコーダ5とが順に接続されており、CPU6を介して外部ホスト(図示せず)に転送可能とされている。一方、記録すべき情報は外部ホストからCPU6を介してエンコーダ7に転送され、このエンコーダ7でデータフォーマットを変換し、光源駆動回路であるレーザ制御回路8で情報ビットに応じて光ピックアップ3中のレーザ光源の発光制御を行うことでメディア1上に書込みを行うように構成されている。

【0036】

一方、光ピックアップ3中の分割受光素子から得られる出力信号に基づきサーボ信号を生成する演算回路9が設けられ、このサーボ信号をサーボ回路10に出力することにより光ピックアップ3の対物レンズ(図示せず)の位置制御を行うように構成されている。また、このサーボ回路10では、PLL回路11から得られるライトクロック信号に基づきスピンドルモータ2の回転制御も行う。

【0037】

さらに、演算回路9で演算された分割受光素子出力が入力されてウォブル信号を抽出するウォブル検出回路12が設けられている。このウォブル検出回路12から出力されるウォブル信号はPLL回路11に入力されており、ウォブル信号に基づきライトクロック信号が生成される。これにより、基本的に、メディア1の回転に追従した正確なライトクロックの生成が可能とされている。ここに、PLL回路11とウォブル検出回路12とにより本発明のライトクロック生成回路が構成されている。

【0038】

また、物理アドレス情報を含んだウォブル信号はアドレス検出回路13に送られ、アドレスデコーダ14でアドレス情報に変換され、アクセス位置のアドレス情報を再生するように構成されている。

【0039】

ここで、本実施の形態で用いられるメディア1及び分割受光素子の構成例について図2を参照して説明する。まず、メディア1上には図2(a)に示すように蛇行したトラックが螺旋状又は同心円状に刻まれている。分割受光素子15は図2(b)に示すようにメディア1上に照射されたスポットSからの反射信号に対し、トラック接線方向に対応した分割線16で2つに分けられた受光領域A,Bが形成されたものである。最も簡易なウォブル信号演算としては、図2(c)に示すように分割受光素子15の各受光領域A,Bの受光量の差分(A−B)から検出する例が挙げらけれる。もちろん光ピックアップ3上の分割受光素子は2分割構造に限らず、4分割構造等の多分割構造であっても構わないが、分割線16で分けられた受光領域毎にまとめて演算処理するようにすればよい。

【0040】

このような前提的な構成の下、本実施の形態のライトクロック生成回路21の構成例を図3に示す。このライトクロック生成回路21は前述したようにウォブル検出回路12とPLL回路11とにより構成されている。ウォブル検出回路12では、まず、光ピックアップ3中の分割受光素子15の各受光領域A,Bから演算回路9を経た出力信号が入力される2つの可変ゲインアンプVGA22a,22bが設けられている。これらの可変ゲインアンプVGA22a,22bは所望ゲインで各受光領域A,Bからの出力信号の増幅又は減衰が可能なもので、そのゲインを可変設定するVGAゲインコントロール回路23が設けられている。VGAゲインコントロール回路23としては、装置の動作状態(記録/再生など)によって自動的に処理できる機能を持たせたものでも良いが、本実施の形態では、CPU6からの指示に基づきゲインを変更できる構成とされている。

【0041】

また、これらの可変ゲインアンプVGA22a,22bの出力側には両者の出力信号の差を演算することによりウォブル信号を出力する減算器24が接続されている。この減算器24の後段にはフィルタ回路25が接続されている。このフィルタ回路25は、メディア1上のデータ信号の洩れ込みや光ピックアップ3の位置ずれによるDCオフセットなど、本来のウォブル信号成分以外のノイズ成分が含まれており、必要な周波数成分のみ抽出するためのものである。具体的にはローパスフィルタLPFとハイパスフィルタHPFとの組合せ、又は、バンドパスフィルタBPFが良い。フィルタ回路25で周波数分離されたウォブル信号は、2値化に十分な振幅にするためウォブル信号振幅を一定電圧に調整制御するウォブル(WBL)振幅一定AGC(自動ゲイン制御)回路26に入力される。このWBL振幅一定AGC回路26の後段にはウォブル信号を2値化ウォブル信号にデジタル化する2値化回路27が接続されている。PLL回路11はこの2値化回路27から得られる2値化ウォブル信号に基づきライトクロックを生成する。なお、フィルタ回路25はWBL振幅一定AGC回路26の後に配置しても良い。

【0042】

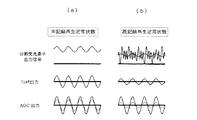

このような構成において、まず、定常状態(再生/記録の切換え時ではなく、切換え後、安定した状態)の信号波形について図4を参照して説明する。未記録再生定常状態の分割受光素子15の出力信号はレーザパワーが小さいため、図4(a)中に示すように、そのDCレベルは小さい。減算器24による減算後のフィルタ回路25の出力ではDC成分は除去され、ウォブル成分が抽出される。その後、2値化に必要な、若しくは、アドレス検出(フォーマットによってはウォブル信号にアドレスが重畳されている)に必要な目標ウォブル信号振幅にするようにWBL振幅一定AGC回路26により増幅される(点線状態から実線状態まで増幅される)。この時のAGCゲインは大きくなっている。

【0043】

一方、記録中定常状態では、図4(b)に示すように、レーザ光源の発光成分が分割受光素子15の出力信号に重畳されており、レーザパワーも大きいのでウォブル成分も大きい。減算器24及びフィルタ回路25によりレーザ発光成分とDC成分とを除去することで、未記録再生定常状態の場合より大きなウォブル信号が得られる。従って、この場合に点線状態から実線状態(目標振幅)まで増幅するよう制御している時のWBL振幅一定AGC回路26のゲインは小さくなっている。

【0044】

このような事情を踏まえ、可変ゲインアンプVGA22a,22bのゲインを固定したまま、再生から記録への動作切換え時の信号の様子を図5を参照して説明する。この場合、図4(a)に示した未記録再生定常状態と図4(b)に示した記録中定常状態とを繋ぎ合わせた形になるが、未記録再生時の大きいAGCゲインのまま記録動作に移ると振幅が大きいウォブル信号が入力されるため、記録開始直後のWBL振幅一定AGC回路26の出力は振幅が非常に大きくなる。この結果、後段の2値化ウォブル信号のスライス電圧のずれ(例えばヒステリシス)などにより、ジッタ(時間軸方向の振れ)を生じライトクロックのロック外れや、不安定動作を生じさせてしまう。

【0045】

このような点を考慮し、本実施の形態では、再生から記録への動作切換え時における記録開始直後の一定期間は、VGAゲインコントロール回路23によって可変ゲインアンプVGA22a,22bのゲインを段階的に変化させるようにしたものである。図6にゲインアンプVGA22a,22bのゲインを記録開始直後に段階的に変化させた場合の動作例を示す。

【0046】

即ち、記録開始直後はWBL振幅一定AGC回路26に入力されるウォブル信号が大きいため、ゲインアンプVGA22a,22bのゲインを一旦小さく設定しておくことで再生中と変わらないウォブル信号が得られる。しかし、記録中はレーザ発光の変調などノイズ成分も大きいことから、記録定常状態に移行した段階ではゲインアンプVGA22a,22bのゲインは大きい方がよいことから、ゲインアンプVGA22a,22bのゲインを段階的に大きくしていく。この場合のゲインステップと時間間隔は後段のWBL振幅一定AGC回路26の追従が十分可能で、かつ、大きな出力変化にならないように設定される。

【0047】

従って、本実施の形態によれば、記録開始直後の一定期間は、可変ゲインアンプVGA22a,22bのゲインをVGAゲインコントロール回路23により段階的に変化させて得られたウォブル信号を用いてライトクロックを生成するようにしているので、記録開始直前から記録開始直後へのウォブル信号の変化を抑えて、WBL振幅一定AGC回路26のゲイン変動を緩やかにすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成できる。また、可変ゲインアンプVGA22a,22bのゲインの段階的な変化の最終変更後は記録中に適正な信号レベルを維持できるので、安定したライトクロック生成を行わせることができる。また、可変ゲインアンプVGA22a,22bのゲインの段階的な可変に対してWBL振幅一定AGC回路26の追従が確実となり、ライトクロック生成動作を適正に行わせることができる。さらには、繊細な特性が必要とされるWBL振幅一定AGC回路26に対しては特殊な切換え機能等の付加を必要とせず、かつ、外付け部品等による制約もなく、当該ライトクロック生成回路をLSIに内蔵させて作製することもできる。

【0048】

本発明の第二の実施の形態を図7に基づいて説明する。第一の実施の形態で示した部分と同一部分は同一符号を用いて示し、説明も省略する。本実施の形態では、可変ゲインアンプと減算器との順序を入替えたもので、分割受光素子15からの出力信号の差を減算器24により演算してウォブル信号とした後、このウォブル信号を可変ゲインアンプVGA22に入力させてゲインに応じて増幅又は減衰させるようにしたものである。

【0049】

動作的には、第一の実施の形態の場合と同様である。本実施の形態によれば、可変ゲインアンプVGAが1個でよいので、第一の実施の形態の場合よりも回路規模が小さいながら同様の作用・効果が得られる。

【0050】

本発明の第三の実施の形態を図8に基づいて説明する。本実施の形態では、記録開始位置直前が未記録領域か既記録領域かに応じて記録開始前の可変ゲインアンプVGA22a,22b(又は、22)のゲインを切換えることで、記録開始直前のウォブル信号の振幅と記録開始直後のウォブル信号の振幅とが同等となるようにしたものである。

【0051】

この点について、図8に示す信号状態を参照して説明する。図8(a)は未記録再生定常状態、図8(b)は既記録再生定常状態の信号波形を示す。既記録領域の再生では分割受光素子15の出力信号にデータ信号成分が重畳されるため、未記録領域と比べると平均信号レベルとしては小さくなる。このため、ウォブル信号も小さく検出される。そこで、記録開始直後のウォブル信号の振幅と記録直前のウォブル信号の振幅とをほぼ同じにするためには、記録開始直前の領域が未記録か、既記録かに応じて可変ゲインアンプVGA22a,22b(又は、22)のゲインを変更しておく必要がある。通常、メディア1の既記録位置は分かっているので、その情報に対応してCPU6などでVGAゲインコントロール回路23の設定を切換えるようにすればよい。

【0052】

従って、本実施の形態によれば、メディア1の記録状態(未記録/既記録)に関わらず、記録直前から記録開始直後へのウォブル信号の変化を抑えて、WBL振幅一定AGC回路26のゲイン変動を緩やかにすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成することができる。

【0053】

本発明の第四の実施の形態を図9に基づいて説明する。本実施の形態は、ライトクロック生成回路21で特にPLL回路11の構成に関するものである。PLL回路11は、基本的には、周知のように、PD(位相比較器)31とフィルタ32とVCO(電圧制御発振器)33と1/n分周器34とによるループ回路として構成されるが、本実施の形態では、ループゲインを切換え可能とするために特性の異なる複数、例えば2個のフィルタ32a,32bが用意され、PLLゲインコントロール回路35によりゲイン切換え可能に構成されている。

【0054】

一般に、定常時のPLL特性はメディア1の回転で発生する低域の周波数変動に追従すればよく、ライトクロックのジッタを小さくすることを重視してループゲインは比較的小さめに設計される。しかし、再生と記録との切換え時には前述したようにウォブル信号の品質や振幅が変化するため、2値化回路27により得られる2値化ウォブル信号に高域の周波数変動が発生し、そのままのループゲインではPLL回路11のロックが外れやすくなる。そこで、本実施の形態では、上述の如く、PLLゲインコントロール回路35を備えることでループゲイン切換え機能を付加しているものである。

【0055】

まず、VCO(電圧制御発振器)33の出力信号がライトクロックとなるが、ライトクロックの1/n分周器34によるn分周(n:ウォブル信号と同じ周波数になる分周比)信号と2値化回路27からの2値化ウォブル信号との位相をPD(位相比較器)31で比較する。その比較結果を特性の異なる複数種類のフィルタ32a,32bに供給し、その出力をVCO33の発振周波数を決定する入力信号とする。複数のフィルタ32a,32bはPLLゲインコントロール回路35で切換え、若しくは、ON/OFF制御することでPLL回路11のループゲインを変更する。具体的には、記録開始直後に一旦高いループゲインにし、ウォブル信号の変動が収まった時点で低いループゲインに切換える。この他、PLLゲインも複数種類用意しておき、可変ゲインアンプVGA22a,22bの場合と同様に記録開始直後から段階的にループゲインを小さくしていってもよい。

【0056】

このように、本実施の形態によれば、記録開始直後の一定期間中にはPLL回路11のループゲインを上げるようにしているので、ウォブル信号の変化が大きいと予想される期間のみPLL回路11の引込み能力を高めてロック外れを防ぐと共に、ウォブル信号が安定した段階ではジッタが小さくて良好なライトクロックを生成することができる。

【0057】

【発明の効果】

請求項2、11記載の発明のライトクロック生成回路によれば、記録開始直後の一定期間に、分割受光素子後段の可変ゲインアンプのゲインをゲインコントロール回路により再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように変化させて得られたウォブル信号よりライトクロックを生成するようにしたので、記録開始直前から記録開始直後へのウォブル信号の変化を抑えて、ウォブル信号振幅一定AGCのゲイン変動を緩やかにすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成でき、また、可変ゲインアンプのゲインの段階的な変化の最終変更後は記録中に適正な信号レベルを維持できるので、安定したライトクロック生成を行わせることができる。

又、記録開始直後は可変ゲインアンプに入力されるウォブル信号が大きいため、一旦ゲインを再生時のゲインレベルよりも小さく設定しておくことにより、再生動作中と変わらないウォブル信号を得ることができる一方、定常状態後の記録動作中にはノイズ成分も大きいことから可変ゲインアンプのゲインは大きいことが好ましいことから、再生時のゲインレベルまで段階的にゲインを大きくすることにより、確実にウォブル信号を得ることができ、適正なライトクロックの生成が可能となる。

【0058】

請求項4,13記載の発明のライトクロック生成回路によれば、記録開始直後の一定期間中に、減算器後段の可変ゲインアンプのゲインをゲインコントロール回路により再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように変化させて得られたウォブル信号よりライトクロックを生成しているので、請求項1記載の発明より回路規模が小さいながら同様の効果を得ることができる。

【0059】

又、請求項2,11記載の発明と同様に、記録開始直後は可変ゲインアンプに入力されるウォブル信号が大きいため、一旦ゲインを再生時のゲインレベルよりも小さく設定しておくことにより、再生動作中と変わらないウォブル信号を得ることができる一方、定常状態後の記録動作中にはノイズ成分も大きいことから可変ゲインアンプのゲインは大きいことが好ましいことから、再生時のゲインレベルまで段階的にゲインを大きくすることにより、確実にウォブル信号を得ることができ、適正なライトクロックの生成が可能となる。

【0060】

請求項5記載の発明によれば、請求項2又は4記載のライトクロック生成回路において、可変ゲインアンプのゲインの段階的な可変に対してウォブル振幅一定AGC回路の追従が確実となり、ライトクロック生成動作を適正に行わせることができる。

【0061】

請求項6記載の発明によれば、請求項2,4又は5記載のライトクロック生成回路において、記録開始位置直前の領域が未記録領域か既記録領域かによって記録開始前の可変ゲインアンプのゲインを切換え、記録開始直前のウォブル信号の振幅と記録開始直後のウォブル信号の振幅とが同等となるようにしたので、メディアの記録状態(未記録/既記録)に関わらず、記録直前から記録開始直後へのウォブル信号の変化を抑えて、ウォブル信号振幅一定AGCのゲイン変動を緩やかにすることができ、よって、再生/記録の切換え時でもウォブル周波数の高域的振れを抑制してジッタの少ないライトクロックを生成することができる。

【0062】

請求項7記載の発明によれば、請求項2,4,5又は6記載のライトクロック生成回路において、記録開始直後の一定期間中にはPLL回路のループゲインを上げるようにしたので、ウォブル信号の変化が大きいと予想される期間のみPLL回路の引込み能力を高めてロック外れを防ぐと共に、ウォブル信号が安定した段階ではジッタが小さくて良好なライトクロックを生成することができる。

【0063】

請求項8記載の発明によれば、請求項7記載のライトクロック生成回路において、記録開始直後はPLL回路のループゲインを一旦高いゲインに設定することにより、再生から記録への切換え時にウォブル信号の品質や振幅の変化に起因して2値化ウォブル信号に高域周波数変動が発生してもウォブル信号のロック外れを確実に防止でき、ウォブル信号が安定した段階では低いゲインに切換えることによりジッタが小さくて良好なライトクロックを生成することができる。

【0064】

請求項9記載の発明によれば、請求項8記載のライトクロック生成回路において、記録開始直後はPLL回路のループゲインを高いゲインに設定することにより、再生から記録への切換え時にウォブル信号の品質や振幅の変化に起因して2値化ウォブル信号に高域周波数変動が発生してもウォブル信号のロック外れを確実に防止でき、ウォブル信号が安定する段階に向けて段階的に低いゲインに切換えることによりジッタが小さくて良好なライトクロックを生成することができる。

【0065】

請求項14記載の発明の光ディスク装置によれば、請求項2,4,5,6,7,8又は9記載のライトクロック生成回路を用いているので、PLL回路のロック外れによる記録失敗を生ずることがなく、かつ、記録開始時の記録品質が低下することのない光ディスク装置を提供することができる。

【図面の簡単な説明】

【図1】本発明の第一の実施の形態の光ディスク装置の構成を示す概略ブロック図である。

【図2】メディア、分割受光素子等に関する説明図である。

【図3】ライトクロック生成回路を示すブロック図である。

【図4】定常状態の信号波形を示す波形図である。

【図5】VGAゲイン固定時の信号波形を示す波形図である。

【図6】VGAゲインを段階的に変化させた場合の信号波形を示す波形図である。

【図7】本発明の第二の実施の形態を示すライトクロック生成回路のブロック図である。

【図8】本発明の第三の実施の形態を示す記録状態毎の信号波形を示す波形図である。

【図9】本発明の第四の実施の形態を示すPLL回路のブロック図である。

【符号の説明】

1 メディア

2 回転駆動機構

3 光ピックアップ

11 PLL回路

15 分割受光素子

16 分割線

21 ライトクロック生成回路

22,22a,22b 可変ゲインアンプ

23 ゲインコントロール回路

24 減算器

26 ウォブル信号振幅一定AGC

27 2値化回路

35 PLLゲインコントロール回路

Claims (14)

- メディア上に形成されたトラックの蛇行に基づくウォブル信号を生成する回路において、

少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する2つの可変ゲインアンプと、

記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、

2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る減算器と、

を備えることを特徴とするウォブル信号を生成する回路。 - メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成回路において、

少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する2つの可変ゲインアンプと、

記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、

2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る減算器と、

この減算器から出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、

このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、

この2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成するPLL回路と、

を備えることを特徴とするライトクロック生成回路。 - メディア上に形成されたトラックの蛇行に基づく2値化ウォブル信号を生成する回路において、

少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る減算器と、

この減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する可変ゲインアンプと、

記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、

前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、

このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、

を備えることを特徴とする2値化ウォブル信号を生成する回路。 - メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成回路において、

少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る減算器と、

この減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する可変ゲインアンプと、

記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定するゲインコントロール回路と、

前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインが自動調整されるウォブル振幅一定AGC回路と、

このウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る2値化回路と、

この2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成するPLL回路と、

を備えることを特徴とするライトクロック生成回路。 - 前記ゲインコントロール回路は、記録開始直後の一定期間中には前記ウォブル振幅一定AGC回路が追従可能な範囲で前記可変ゲインアンプのゲインステップとその時間間隔とを段階的に可変させることを特徴とする請求項2又は4記載のライトクロック生成回路。

- 前記ゲインコントロール回路は、記録開始直前のウォブル信号の振幅と記録開始直後のウォブル信号の振幅とが同等となるように、記録開始位置直前が未記録領域か既記録領域かに応じて記録開始前の前記可変ゲインアンプのゲインを切換えることを特徴とする請求項2,4又は5記載のライトクロック生成回路。

- 記録開始直後の一定期間中には前記PLL回路のループゲインを上げるようにして前記PLL回路のループゲインを決定するPLLゲインコントロール回路を備えることを特徴とする請求項2,4,5又は6記載のライトクロック生成回路。

- 前記PLLゲインコントロール回路は、記録開始直後の一定期間中には前記PLL回路のループゲインを一旦高いゲインに設定し、その後、低いゲインに切換えるように可変させることを特徴とする請求項7記載のライトクロック生成回路。

- 前記PLLゲインコントロール回路は、前記PLL回路のループゲインを高いゲインから低いゲインに段階的に可変させることを特徴とする請求項8記載のライトクロック生成回路。

- メディア上に形成されたトラックの蛇行に基づくウォブル信号を生成する方法において、

2つの可変ゲインアンプによって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する工程と、

ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、

減算器によって、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る工程と、

を備えることを特徴とするウォブル信号を生成する方法。 - メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成方法において、

2つの可変ゲインアンプによって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号を決定されたゲインに応じて増幅する工程と、

ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、

減算器によって、2つの前記可変ゲインアンプ間の出力差を演算してウォブル信号を得る工程と、

ウォブル振幅一定AGC回路によって、この減算器から出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、

2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、

PLL回路によって、前記2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成する工程と、

を備えることを特徴とするライトクロック生成方法。 - メディア上に形成されたトラックの蛇行に基づく2値化ウォブル信号を生成する方法において、

減算器によって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る工程と、

可変ゲインアンプによって、前記減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する工程と、

ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、

ウォブル振幅一定AGC回路によって、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、

2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、

を備えることを特徴とする2値化ウォブル信号を生成する方法。 - メディア上に形成されたトラックの蛇行に基づくウォブル信号よりライトクロックを生成するライトクロック生成方法において、

減算器によって、少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子の各々の出力信号の間の差を演算してウォブル信号を得る工程と、

可変ゲインアンプによって、前記減算器から出力されるウォブル信号を決定されたゲインに応じて増幅する工程と、

ゲインコントロール回路によって、記録開始直後の一定期間中には前記可変ゲインアンプのゲインを再生時のゲインレベルよりも一旦小さくした後、再生時のゲインレベルまで段階的に大きくなるように可変させるようにして前記可変ゲインアンプのゲインを決定する工程と、

ウォブル振幅一定AGC回路によって、前記可変ゲインアンプから出力されるウォブル信号の振幅を一定に保持させるようにゲインを自動調整する工程と、

2値化回路によって、前記ウォブル振幅一定AGC回路から出力される信号をデジタル化して2値化ウォブル信号を得る工程と、

PLL回路によって、前記2値化回路から出力される2値化ウォブル信号を基準にライトクロックを生成する工程と、

を備えることを特徴とするライトクロック生成方法。 - 記録面に蛇行させたトラックが形成されたメディアを回転させる回転駆動機構と、

少なくともトラック接線方向に対応する方向の分割線で2つに分けられた分割受光素子、及び、前記メディアに対してレーザ光を照射するレーザ光源を有する光ピックアップと、

前記光源の発光動作を制御する光源駆動回路と、

前記分割受光素子から出力される信号が入力されて前記光源駆動回路側に対してライトクロックを出力する請求項2,4,5,6,7,8又は9記載のライトクロック生成回路と、

を備える光ディスク装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002058517A JP4079658B2 (ja) | 2002-03-05 | 2002-03-05 | 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 |

| EP20030743615 EP1482487A1 (en) | 2002-03-05 | 2003-03-05 | Light clock generating circuit and optical disk unit |

| US10/506,215 US7061845B2 (en) | 2002-03-05 | 2003-03-05 | Write clock generating circuit and optical disk apparatus |

| PCT/JP2003/002585 WO2003075264A1 (fr) | 2002-03-05 | 2003-03-05 | Circuit de generation d'horloge lumineuse et unite de disque optique |

| US11/410,099 US20060187784A1 (en) | 2002-03-05 | 2006-04-25 | Write clock generation circuit and optical disk apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002058517A JP4079658B2 (ja) | 2002-03-05 | 2002-03-05 | 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003257122A JP2003257122A (ja) | 2003-09-12 |

| JP2003257122A5 JP2003257122A5 (ja) | 2005-07-14 |

| JP4079658B2 true JP4079658B2 (ja) | 2008-04-23 |

Family

ID=27784705

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002058517A Expired - Fee Related JP4079658B2 (ja) | 2002-03-05 | 2002-03-05 | 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7061845B2 (ja) |

| EP (1) | EP1482487A1 (ja) |

| JP (1) | JP4079658B2 (ja) |

| WO (1) | WO2003075264A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4079658B2 (ja) * | 2002-03-05 | 2008-04-23 | 株式会社リコー | 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 |

| TWI332208B (en) * | 2003-01-28 | 2010-10-21 | Tian Holdings Llc | Method and apparatus for generating wobble signal |

| JP3853806B2 (ja) * | 2004-06-24 | 2006-12-06 | シャープ株式会社 | 光ディスク装置 |

| CN100435220C (zh) * | 2004-12-06 | 2008-11-19 | 建兴电子科技股份有限公司 | 可补偿摇摆定址信号的光盘机及其方法 |

| US7729214B1 (en) * | 2005-08-09 | 2010-06-01 | Mediatek Inc. | Method and apparatus applied in optical disc drive for obtaining push-pull signal via adjusting amplifying gain according to fluctuating signals generated from photo detector of pick-up head |

| WO2007102495A1 (ja) * | 2006-03-09 | 2007-09-13 | Nec Corporation | 光ディスク装置及び光ディスク媒体の欠陥検出方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2628265B1 (fr) * | 1987-03-06 | 1990-12-21 | Thomson Csf | Antenne directive a transducteurs multiples notamment pour sonar |

| FR2682833B1 (fr) * | 1991-10-18 | 1993-12-03 | Thomson Csf | Filtre a ondes de surface et a trajet acoustique replie. |

| JP3051526B2 (ja) * | 1991-11-08 | 2000-06-12 | パイオニア株式会社 | 光学式記録再生装置における光ヘッドのサーボ装置 |

| US5703427A (en) * | 1993-03-19 | 1997-12-30 | Thomson-Csf | Surface-wave distributed acoustic reflection transducer and filter including such a transducer |

| JP3761904B2 (ja) * | 1993-08-30 | 2006-03-29 | キヤノン株式会社 | サーボル−プの自動利得制御回路 |

| JP3458502B2 (ja) * | 1995-01-11 | 2003-10-20 | ソニー株式会社 | 光ディスク装置 |

| FR2739232B1 (fr) * | 1995-09-26 | 1997-10-24 | Thomson Csf | Filtre a ondes acoustiques de surface utilisant le couplage de trois voies acoustiques |

| FR2740933B1 (fr) * | 1995-11-03 | 1997-11-28 | Thomson Csf | Sonde acoustique et procede de realisation |

| FR2740908B1 (fr) * | 1995-11-07 | 1997-11-28 | Thomson Csf | Transducteur a ondes acoustiques de surface attaque en differentiel |

| JPH10293926A (ja) * | 1997-02-21 | 1998-11-04 | Pioneer Electron Corp | 記録用クロック信号発生装置 |

| FR2762458B1 (fr) * | 1997-04-18 | 1999-07-09 | Thomson Csf | Dispositif a ondes acoustiques de surface a couplage par proximite a entrees/sorties differentielles |

| FR2774826B1 (fr) * | 1998-02-06 | 2000-05-05 | Thomson Csf | Filtre a resonateurs a ondes acoustiques de surface |

| JP3720197B2 (ja) | 1998-08-20 | 2005-11-24 | パイオニア株式会社 | 位相比較装置 |

| FR2785473B1 (fr) * | 1998-10-30 | 2001-01-26 | Thomson Csf | Filtre faibles pertes a ondes acoustiques de surface sur substrat de quartz de coupe optimisee |

| JP2001134943A (ja) * | 1999-11-05 | 2001-05-18 | Yamaha Corp | 光ディスク記録装置のプッシュプル信号処理回路およびウォブル抽出回路ならびにプリピット検出回路 |

| JP4422855B2 (ja) | 2000-03-16 | 2010-02-24 | 株式会社日立製作所 | ウォブル信号再生回路 |

| JP2001297454A (ja) * | 2000-04-14 | 2001-10-26 | Matsushita Electric Ind Co Ltd | 光ディスク装置 |

| JP4079658B2 (ja) * | 2002-03-05 | 2008-04-23 | 株式会社リコー | 2値化ウォブル信号を生成する回路、ライトクロック生成回路、2値化ウォブル信号を生成する方法、ライトクロック生成方法及び光ディスク装置 |

-

2002

- 2002-03-05 JP JP2002058517A patent/JP4079658B2/ja not_active Expired - Fee Related

-

2003

- 2003-03-05 WO PCT/JP2003/002585 patent/WO2003075264A1/ja not_active Application Discontinuation

- 2003-03-05 US US10/506,215 patent/US7061845B2/en not_active Expired - Fee Related

- 2003-03-05 EP EP20030743615 patent/EP1482487A1/en not_active Withdrawn

-

2006

- 2006-04-25 US US11/410,099 patent/US20060187784A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20060187784A1 (en) | 2006-08-24 |

| JP2003257122A (ja) | 2003-09-12 |

| EP1482487A1 (en) | 2004-12-01 |

| US7061845B2 (en) | 2006-06-13 |

| WO2003075264A1 (fr) | 2003-09-12 |

| US20050105424A1 (en) | 2005-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3968193B2 (ja) | プリピット検出装置 | |

| JP2001338421A (ja) | ディスクドライブ装置、ウォブル情報生成方法 | |

| US6859425B2 (en) | Wobble signal detection circuit and optical disk device | |

| KR19990017725A (ko) | 편심억압 서보방법 및 이를 이용한 서보장치 | |

| JP3914018B2 (ja) | ウォブル信号検出装置及び光学的情報記録再生装置 | |

| US20060187784A1 (en) | Write clock generation circuit and optical disk apparatus | |

| JP3812363B2 (ja) | 光ディスク装置 | |

| JP3881835B2 (ja) | 記録再生装置 | |

| US6992956B2 (en) | Disk reproducing apparatus for precisely determining a value of an address signal reproduced from the disk | |

| JP3768142B2 (ja) | ドロップアウト検出回路及び光ディスク装置 | |

| JP2002117536A (ja) | 光ディスク装置 | |

| JP3853806B2 (ja) | 光ディスク装置 | |

| JP4370658B2 (ja) | 記録方法及び装置 | |

| US7385886B2 (en) | Optical disk drive and method of controlling spindle motor thereof | |

| JP2005158168A (ja) | 情報読取装置およびプリピット検出回路 | |

| JP2007026641A (ja) | 位相調整で光ディスクドライブからウォッブル信号を検出する装置及び方法 | |

| JP2001067674A (ja) | ディスク駆動装置および方法、並びに記録媒体 | |

| JP2003217127A (ja) | 光ピックアップ装置及び光ディスク装置 | |

| JP2000298835A (ja) | 光ディスク装置 | |

| JP3910787B2 (ja) | ウォブル信号検出装置、光ディスク装置及び情報処理装置 | |

| JP2006048880A (ja) | ウォブル信号検出方法及びウォブル信号検出装置 | |

| JP4265224B2 (ja) | 光ディスク装置とウォブル信号検出回路及びウォブル信号検出方法 | |

| KR20030053046A (ko) | 광디스크 장치 및 서보 제어 방법 | |

| WO2005101389A1 (ja) | 光ディスク記録再生装置 | |

| JP2009170005A (ja) | クロック生成装置及びクロック生成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20041005 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041115 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041115 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20050620 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070828 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071026 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080108 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080205 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |