JP4040712B2 - スタートパルス垂直信号生成器およびtft液晶表示装置のゲート駆動方法 - Google Patents

スタートパルス垂直信号生成器およびtft液晶表示装置のゲート駆動方法 Download PDFInfo

- Publication number

- JP4040712B2 JP4040712B2 JP31462596A JP31462596A JP4040712B2 JP 4040712 B2 JP4040712 B2 JP 4040712B2 JP 31462596 A JP31462596 A JP 31462596A JP 31462596 A JP31462596 A JP 31462596A JP 4040712 B2 JP4040712 B2 JP 4040712B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- pulse

- vertical signal

- cpv

- pulse vertical

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Synchronizing For Television (AREA)

- Transforming Electric Information Into Light Information (AREA)

Description

【発明の属する技術分野】

本発明はデータイネーブル信号(Data Enable Signal;DE) を用いてBIOS(Basic Input Output System) と無関係にプレチャージするスタートパルス垂直(Start Pulse Vertical;STV) 信号生成器に係り、より詳しくは、液晶表示装置の駆動回路において、ゲートを駆動するためのSTV信号を入力するとき、BIOSと無関係に二つ前のクロックにおいてプレチャージ用STV信号を生成せしめることにより、実際データが入るメインSTV信号以前に一次的にパネルのゲートをオンさせてデータを入力し、メインSTV信号が入力されるときゲートの駆動速度を速くするデータイネーブル信号DEを用いてBIOSと無関係にプレチャージするSTV信号生成器に関する。

【0002】

【従来の技術】

一般的なPCセットにおいては、ディスプレーのための制御信号として垂直同期信号Vsync 、水平同期信号Hsync 、データイネーブル信号DE、メインクロック信号MCLKおよびデータ(色信号)を生成している。このようなPCセットにおいて、同期モード(Sync Mode) とはデータ制御のため垂直同期信号Vsync 、水平同期信号Hsync に各種信号を生成することをいい、DEモードとはデータ制御のためデータイネーブル信号DEにデータ制御信号を生成することをいう。

【0003】

PCセットメーカーによっては、垂直同期信号Vsync 、水平同期信号Hsync およびデータイネーブル信号DEを全て提供する場合と、垂直同期信号Vsync 、水平同期信号Hsync のみを提供する場合並びに、データイネーブル信号DEのみを提供する場合がある。メインクロック信号MCLKとデータは同期モードやDEモードに関係なしで常に提供される。

【0004】

垂直同期信号Vsync はディスプレー装置の垂直ラインを制御するための信号であり、水平同期信号Hsync は水平ラインを動作するための信号である。

同期信号は一般的なモニターを用いるとき制御のために生成する信号であり、データイネーブル信号は液晶表示装置用フラットパネルを制御するために適当であるように生成する信号である。

【0005】

モニターは電子銃により1次元に画面構成を動作させ、液晶表示装置パネルはロー、カラムにより2次元に画面を構成する。

BIOSは同期モード、DEモードいずれの場合にも適応でき、制御信号の各種情報などの変化を可能にする。

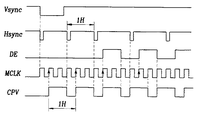

これを図3および図4に示す。

【0006】

BIOSはシステムの効用性を高めるため出力を行うタイミングを可変可能にし、例えば図4の同期モードにおいてデータ‘1’は水平同期信号後にメインクロック信号MCLKを三つ経てから出力される。

この場合、設計時にメインクロック信号三つの後、データ‘1’を処理するように設定しているが、他のPCセットメーカーにおいて水平同期信号後に四つのメインクロック信号を経た後データが出力されるように設定されている場合、BIOSを変更しなければならない。

【0007】

クロックパルス垂直信号(Clock Pulse Vertical Signal; CPV) はVGA方式で用いられ、このVGA方式では、画素として640カラム*480ロー*RGB個の有効データ個数が存在する。

しかしながら、実際タイミングを見るとき、制御信号はブランク期間を有しており、有効データ個数より多い800*525のメインクロック個数からなる。

【0008】

ブランク期間では、電子銃が画面にデータを走査するとき水平方向に帰線する時間と垂直方向に帰線する時間が必要であり、この時間の間はデータを入力しても画面には表れない。

1水平同期信号は800個のメインクロックが集まって構成され、1垂直同期信号は水平同期信号525個が集まって構成される。

【0009】

1水平同期信号に係る信号はメインクロック信号からつくって用いるが、1垂直同期信号に係る信号をメインクロック信号からつくる場合、800*525個のメインクロック信号をカウントしなければならないので非効率的であり、通常、垂直同期信号に係る垂直ライン制御信号などは1水平同期信号と周期が同一であるCPV信号を生成して用いる。

【0010】

このCPV信号はゲートドライバー集積回路を動作するための基準信号になり、ゲート信号と関連するすべての信号を生成することになる。

一般的に、液晶表示装置の内部ではデータイネーブル信号DEとメインクロック信号を生成しており、この信号を用いて実際必要な信号を生成して用いている。

【0011】

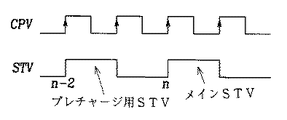

この場合、液晶表示装置のゲートドライブを駆動するためのクロックパルスとしてCPV信号を用い、ゲートドライブの動作時点を知らせるためSTV信号を用いるが、これを図1に示す。

図1に示すように、STV信号をみるとメインSTV信号よりCPV信号2つ前のクロックn−2において任意のSTVを生成してプレチャージさせる。

【0012】

そうすると、実際データが入力されるメインSTV信号以前に1次的にパネルのゲートをスイッチオンさせ、データを入力してメインSTV信号が動作する速度を高めることになり、結果的にゲートが正確な時点で動作を始めることになる。

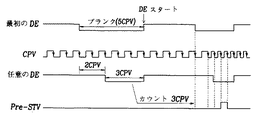

従来では前記のようなSTV信号を生成するために垂直同期信号Vsync を用いており、これを図2に示す。このように、従来では垂直同期信号を基準にして一定時間T後にPre−STV信号を発生させていた。

【0013】

【発明が解決しようとする課題】

しかしながら、前記過程において垂直同期信号を基準にしてPre−STV信号を発生する際の遅延時間Tは企業ごとに一定していない。すなわち、垂直同期信号を基準にして任意の一定時間Tだけ遅延するPre−STV信号をつくる場合、各企業の製品のBIOSによりPre−STV信号が生成されるタイミングが異なるため、毎回BIOSをセットアップさせなければならないという問題がある。

【0014】

つまり、従来のSTV信号生成器では各企業ごとにBIOSが異なるため、毎回BIOSをセットアップさせなければならないという短所がある。

従来のPre−STV信号生成法とBIOSに従う補正方法について説明する。

図5または図9に示すように、プレチャージ用STV信号はポイントAにおいて有効データが出力されるため、基準信号になる‘n+2’期間より以前であるn番目の位置において発生し得るように垂直同期信号Vsync のローパルス信号からカウントしてつくらせる。

【0015】

このため、設計したシステムのプレチャージSTV信号のnが100であって、B社の場合nが150個必要であるとすると、BIOSでブランク期間の基準信号を変更し、システムに適合するように150個を100個に変更しなければならない。

本発明はこのようなBIOSの修正をすることなく、プレチャージSTV信号の位置が図5のポイントAに示す有効データが出力する位置において常に一定となるようにし、例えば、nの個数が100個または150個と無関係に常に一定の位置に発生するようにして、画面においてデータ損失をなくし、BIOS調整の煩わしさを少なくしようとするものである。

【0016】

さらに、図5に示すように、n+2後であるポイントAにおいて有効データが出力されるように回路設計した時のnの個数を100に固定すると、垂直同期信号Vsync の後CPV信号102(n+2)個後にSTV信号が発生することになるが、回路設計されたシステムはハードウェア的に構成されるため、最初の設計時に102個後にSTV信号を生成するようにすると、この値は再び回路設計するまでは変化することなく固定してしまう。図6にCPV信号が生成される過程の波形を示す。

【0017】

この方法はBIOSの値を変動することで、nの個数をPCセットにおいて常に対応させて設計システムと同一にする方法を用いているが、煩わしいという短所がある。

従って、本発明は前記のような短所を解決するためのものであって、その目的は、BIOSと無関係に動作するデータイネーブル信号DEを用いてPre−STV信号を生成することにより、BIOSセットアップが必要でない、BIOSと無関係にプレチャージするスタートパルス垂直信号生成器を提供することにある。

【0018】

【課題を解決するための手段】

本発明に係るスタートパルス垂直信号生成器は、データイネーブル信号DEとメインクロック信号が入力され、これをカウントしてクロックパルス垂直信号CPVを生成するクロックパルス垂直信号生成部と、前記クロックパルス垂直信号CPVとデータイネーブル信号DEとが入力され、各種パルス信号を生成するパルス信号生成部と、前記クロックパルス垂直信号生成部のクロックパルス垂直信号CPVとパルス信号生成部から出力される各種パルス信号が入力され、スタートパルス垂直信号STVを生成するスタートパルス垂直信号生成部とを含んで構成される。

【0019】

さらに、本発明のTFT液晶表示装置のゲート駆動方法では、最初に入力されるブランク期間をクロックパルス垂直信号CPVの周期でカウントした値と、前記ブランク期間を最小限1周期以上遅延させてCPVでカウントした値を所定の周期で貯蔵し、次のDEのブランク信号のブランク期間の始まりから前記1周期以上遅延させたCPVの周期後にプレチャージSTV信号を出力するようにすることを特徴とする。

【0020】

【発明の実施の形態】

以下、本発明の好ましい実施形態を添付図面に基づいて詳細に説明する。

図7は本発明の1実施形態に従うスタートパルス垂直信号生成器(以下、STV信号生成器と称す)のブロック構成図であり、図8は本発明の実施形態に従うSTV信号生成器内のスタートパルス垂直信号生成部(以下、STV信号生成部と称す)の詳細図である。

【0021】

図7に示すように、本発明の実施形態に従うSTV信号生成器の構成は、データイネーブル信号DEとメインクロック信号MCLKが入力され、これをカウントしてクロックパルス垂直信号CPVを生成するためのクロックパルス垂直信号生成部1と、前記クロックパルス垂直信号生成部1に連結され、前記クロックパルス垂直信号CPVとデータイネーブル信号DEが入力され、各種パルス信号(DE_n+1,DE_n+3,RST_rise,RST_fall)を生成するためのパルス信号生成部2と、前記クロックパルス垂直信号生成部1のクロックパルス垂直信号CPVとパルス信号生成部2から出力される各種パルス信号(DE_n+1,DE_n+3,RST_rise,RST_fall)が入力され、プレチャージスタートパルス垂直信号Pre−STVを生成するためのプレチャージSTV信号生成部3とからなる。

【0022】

図8に示すように、前記プレチャージSTV信号生成部3の構成は、データイネーブル信号DEをクロックパルス垂直信号CPVの1クロック信号分遅延した信号(DE_n+1)とリセット信号(RST_rise)が入力され、ブランク期間の間カウントするためのDE_n+1カウンタ31と、データイネーブル信号DEをクロックパルス垂直信号CPVの3クロック信号分遅延した信号(DE_n+3)とリセット信号(RST_fall)が入力され、ブランク期間よりクロックパルス垂直信号CPVの2クロック信号分遅れてブランク期間の間カウントするためのDE_n+3カウンタ34と、前記DE_n+3カウンタ34のカウント値を貯蔵するためのカウンタ値貯蔵器33と、前記カウンタ値貯蔵器33のカウント値と前記DE_n+1カウンタ31の値を比較して同一である場合、パルス信号を発生するためのカウンタ比較器32と、前記カウンタ比較器32から出力されるパルス信号が入力されてプレチャージスタートパルス垂直信号を出力するためのSTV信号生成器35とからなる。

【0023】

まず、この発明の基本概念について簡単に説明する。

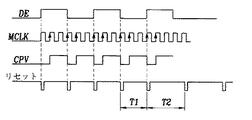

図10に示すように、データイネーブル信号DEよりクロックパルス垂直信号CPV2つ分前にBIOSと無関係にプレチャージ用クロックパルス垂直信号STVを生成することである。

DEをもってCPVを生成する場合、DEの立上り部分においてカウントし始めて所望する時間後にCPVの立上りエッジまたは立下りエッジを形成し、次のDE立上りエッジが入る前にCPVのまた他のエッジ部分を形成する。これを図11に示す。

【0024】

DEが存在する区間のCPV信号周期T1はDE信号周期または垂直同期信号Hsync 周期と同様であり、ブランク期間のCPV信号周期はT1と同様にすることができるが、BIOS可変にもっと効果的にT1と同様に合わせることよりCPVを生成するカウンタ1周期(10ビットカウンタは1024個のメインクロック信号)T2につくることがずっと合理的であり、本発明の回路においてもこのように適用した。

【0025】

すなわち、最初のデータイネーブル信号DEとクロックパルス垂直信号CPVが入力されるとき、ブランク期間のクロックパルス垂直信号CPV値が可変しても常にデータイネーブル信号DEのスタートより二つのクロックパルス垂直信号CPV前でプレチャージさせる信号を生成することである。

まず、最初のデータイネーブル信号DEのブランク期間の長さよりクロックパルス垂直信号CPV2つ分短いブランク期間の任意のデータイネーブル信号DEを生成する。

【0026】

任意のデータイネーブル信号DEのブランク期間内のクロックパルス垂直信号CPVの個数を数えて(3CPV)この値を貯蔵し、この後、最初のデータイネーブル信号DEの次のブランク期間が始まる部分からカウントを開始して、任意のデータイネーブル信号DEのブランク期間のカウンタ値と同一のカウント値で、パルスを発生させると、最初のデータイネーブル信号DEのブランク期間において所望のタイミングで任意のパルスを発生するようにすることができる。ここでは、クロックパルス垂直信号CPVの2クロック信号分前のタイミングでパルスを発生させることができる。

【0027】

さらに、クロックパルス垂直信号CPVの個数が変わっても常に最初のデータイネーブル信号DEのデータイネーブルスタートポイントにおいてクロックパルス垂直信号CPV2つ分だけ先行して信号を生成できる。

前記構成によるこの発明の実施形態に従うSTV信号生成器の作用について説明する。

【0028】

まず、使用者により電源が印加されると、この発明の実施形態に従うBIOSと無関係にプレチャージするSTV信号生成器の動作が始まる。

動作が始まると、図9に示すような波形を有するデータイネーブル信号DEおよびメインクロック信号MCLKがクロックパルス垂直信号生成部(CPV信号生成部)1に入力される。

【0029】

そうすると、クロックパルス垂直信号生成部1においてはクロックパルス垂直信号CPVを生成して出力する。

各種のパルス信号生成部2においては前記クロックパルス垂直信号生成部1から出力されるクロックパルス垂直信号CPVとメインクロック信号MCLKが入力されて各種信号(DE_n+1,DE_n+3,RST_rise,RST_fall)を生成する。この信号を図9に示す。

【0030】

次に、DE_n+1カウンタ31はデータイネーブル信号DEをクロックパルス垂直信号CPVの1クロック信号分遅延した信号DE_n+1とリセット信号RST_riseが入力され、クロックパルス垂直信号CPVのブランク期間の間カウントする。

同時に、DE_n+3カウンタ34はデータイネーブル信号DEをクロックパルス垂直信号CPVの3クロック信号分遅延した信号DE_n+3とリセット信号RST_fallが入力され、クロックパルス垂直信号CPV2つ分遅延して、ブランク期間の間カウントする。

【0031】

カウンタ値貯蔵器33は前記DE_n+3カウンタ34のカウント値を貯蔵する。

次に、図9に示すように、カウンタ比較器32は次のブランク期間が始まると、前記カウンタ値貯蔵器33のカウント値と前記DE_n+1カウンタ31値を比較し、同一になったとき、パルス信号を発生させる。

【0032】

その後、Pre−STV信号生成器35は前記カウンタ比較器32から出力されるパルス信号が入力されプレチャージスタートパルス垂直信号を出力する。

【0033】

【発明の効果】

以上のように、本発明の実施例において、ゲートを駆動するためのSTV信号を入力するとき、BIOSと無関係に2つ前のクロックにおいてプレチャージ用STV信号を生成せしめることにより、実際にデータが入るメインSTV信号以前に1次的にパネルのゲートをオンさせ、データを入力してメインSTV信号が入力されるとき、ゲートの駆動速度を速くするデータイネーブル信号DEを用いてBIOSと無関係にプレチャージするSTV信号生成器を提供することができる。

【図面の簡単な説明】

【図1】一般的なSTVを示す波形図である。

【図2】従来の一般的な垂直同期信号を用いたSTV信号生成過程を示す波形図である。

【図3】BIOSに係わる各信号の波形図である。

【図4】BIOSに係わる各信号の波形図である。

【図5】従来のプレチャージSTV信号生成法とBIOSに従う補正方法を示す波形図である。

【図6】CPV信号生成法に従う各信号の波形図である。

【図7】本発明の実施例に従うBIOSと無関係にプレチャージするSTV信号生成器のブロック構成図である。

【図8】本発明の実施例に従うBIOSと無関係にプレチャージするSTV信号生成器内のSTV信号生成部の詳細図である。

【図9】本発明の実施例に従うBIOSと無関係にプレチャージするSTV信号生成器に用いられるそれぞれの信号波形図である。

【図10】本発明の実施例に従うBIOSと無関係にプレチャージするSTV信号生成器の動作を示す簡単な概念図である。

【図11】データイネーブル信号DEをもってCPVを生成する過程の各信号の波形図である。

【符号の説明】

1 クロックパルス垂直信号生成部

2 パルス信号生成部

3 プレチャージSTV信号生成部

31 DE_n+1カウンタ

32 カウンタ比較器

33 カウンタ値貯蔵器

34 DE_n+3カウンタ

35 Pre−STV信号生成器

Claims (5)

- 外部からデータイネーブル信号DEとメインクロック信号とを入力し、前記データイネーブル信号DEが変化するごとに前記メインクロック信号のパルスをカウントし、そのカウントに基づいてクロックパルス垂直信号CPVを生成するクロックパルス垂直信号生成部と、

前記クロックパルス垂直信号CPVのパルスをカウントし、そのカウントに基づいて前記データイネーブル信号DEを遅延させて遅延パルス信号を生成し、かつ、前記データイネーブル信号DEの状態に応じてブランク期間の開始時点と終了時点とでリセットパルス信号を生成するパルス信号生成部と、

前記リセットパルス信号に応じてリセットされ、前記遅延パルス信号に応じてブランク期間で前記クロックパルス垂直信号CPVのパルスをカウントし、そのカウントに基づき、ブランク期間の終了時点より前記クロックパルス垂直信号CPVの周期の所定数倍分先行してプレチャージスタートパルス垂直信号を生成するプレチャージスタートパルス垂直信号生成部と、

を有するスタートパルス垂直信号生成器。 - 前記遅延パルス信号は、

前記データイネーブル信号DEを前記クロックパルス垂直信号CPVの1周期分遅延させた第1遅延パルス信号DE_n+1と、

前記データイネーブル信号DEを前記クロックパルス垂直信号CPVの3周期分遅延させた第2遅延パルス信号DE_n+3と、

を含み、

前記リセットパルス信号は、

前記第1遅延パルス信号DE_n+1に応じて前記プレチャージスタートパルス垂直信号生成部によって行われる前記クロックパルス垂直信号CPVのパルスのカウントをリセットするための第1リセット信号RST_riseと、

前記第2遅延パルス信号DE_n+3に応じて前記プレチャージスタートパルス垂直信号生成部によって行われる前記クロックパルス垂直信号CPVのパルスのカウントをリセットするための第2リセット信号RST_fallと、

を含む、請求項1に記載のスタートパルス垂直信号生成器。 - 前記プレチャージスタートパルス垂直信号生成部は、ブランク期間の終了時点より前記クロックパルス垂直信号CPVの2周期分先行して前記プレチャージスタートパルス垂直信号を生成することを特徴とする、請求項1に記載のスタートパルス垂直信号生成器。

- 前記プレチャージスタートパルス垂直信号生成部は、

前記第1リセット信号RST_riseに応じてリセットされ、前記第1遅延パルス信号DE_n+1に応じてブランク期間に前記クロックパルス垂直信号CPVのパルスをカウントするDE_n+1カウンタと、

前記第2リセット信号RST_fallに応じてリセットされ、前記第2遅延パルス信号DE_n+3に応じて前記DE_n+1カウンタによる前記クロックパルス垂直信号CPVのパルスのカウント開始から前記クロックパルス垂直信号CPVの2周期分遅延して前記クロックパルス垂直信号CPVのパルスをカウントし始め、ブランク期間に前記クロックパルス垂直信号CPVのパルスをカウントするDE_n+3カウンタと、

ブランク期間が終了するごとに前記DE_n+3カウンタのカウント値を貯蔵するためのカウンタ値貯蔵器と、

ブランク期間の一つで前記DE n+3カウンタによってカウントされて前記カウンタ値貯蔵器に貯蔵されたカウント値を次のブランク期間で前記DE_n+1カウンタのカウント値と比較し、それらのカウント値が一致した時点でパルス信号を発生させるカウンタ比較器と、

前記カウンタ比較器から出力されるパルス信号に応じて前記プレチャージスタートパルス垂直信号を出力するプレチャージスタートパルス垂直信号生成器と、

を含む、請求項2に記載のスタートパルス垂直信号生成器。 - 外部から入力される第1データイネーブル信号をクロックパルス垂直信号の少なくとも1周期分遅延させて第2データイネーブル信号を生成し、

前記第1データイネーブル信号の示すブランク期間の一つでは前記第2データイネーブル信号の示すブランク期間の開始時点から前記第1データイネーブル信号の示すブランク期間の終了時点まで前記クロックパルス垂直信号のパルスをカウントしてそのカウント値を貯蔵し、

前記第1データイネーブル信号の示す次のブランク期間ではその開始時点から前記クロックパルス垂直信号のパルスをカウントし、そのカウント値が貯蔵されたカウント値に達した時点でプレチャージスタートパルス垂直信号を出力する、

TFT液晶表示装置のゲート駆動方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1995P44308 | 1995-11-28 | ||

| KR1019950044308A KR0156804B1 (ko) | 1995-11-28 | 1995-11-28 | 데이타 인에이블 신호를 이용하여 바이오스에 관계없이 프리챠지를 하는 스타트 펄스 버티컬 신호 생성기 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09198014A JPH09198014A (ja) | 1997-07-31 |

| JP4040712B2 true JP4040712B2 (ja) | 2008-01-30 |

Family

ID=19436100

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31462596A Expired - Lifetime JP4040712B2 (ja) | 1995-11-28 | 1996-11-26 | スタートパルス垂直信号生成器およびtft液晶表示装置のゲート駆動方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5828368A (ja) |

| JP (1) | JP4040712B2 (ja) |

| KR (1) | KR0156804B1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10165155B2 (en) | 2013-08-29 | 2018-12-25 | Sharp Kabushiki Kaisha | Image processing device |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2809180B2 (ja) * | 1996-03-22 | 1998-10-08 | 日本電気株式会社 | 液晶表示装置 |

| KR100315011B1 (ko) * | 1998-03-27 | 2002-02-28 | 주식회사 현대 디스플레이 테크놀로지 | 액정표시장치의모드검출회로 |

| JP2001159877A (ja) * | 1999-09-20 | 2001-06-12 | Sharp Corp | マトリクス型画像表示装置 |

| US6778170B1 (en) * | 2000-04-07 | 2004-08-17 | Genesis Microchip Inc. | Generating high quality images in a display unit without being affected by error conditions in synchronization signals contained in display signals |

| KR100365500B1 (ko) * | 2000-12-20 | 2002-12-18 | 엘지.필립스 엘시디 주식회사 | 도트 인버젼 방식의 액정 패널 구동 방법 및 그 장치 |

| KR100759972B1 (ko) * | 2001-02-15 | 2007-09-18 | 삼성전자주식회사 | 액정 표시 장치와 이의 구동 장치 및 방법 |

| KR20040009815A (ko) * | 2002-07-26 | 2004-01-31 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| TW559756B (en) * | 2002-08-26 | 2003-11-01 | Chi Mei Optoelectronics Corp | Defective pixel remedy device and method of LCD panel |

| JP2004085891A (ja) | 2002-08-27 | 2004-03-18 | Sharp Corp | 表示装置および表示駆動回路の制御装置ならびに表示装置の駆動方法 |

| JP2006171125A (ja) * | 2004-12-13 | 2006-06-29 | Nec Lcd Technologies Ltd | 表示装置及び自動同期判定回路 |

| TWI327720B (en) * | 2005-03-11 | 2010-07-21 | Sanyo Electric Co | Active matrix type display device and driving method thereof |

| JP4986468B2 (ja) * | 2005-03-11 | 2012-07-25 | 三洋電機株式会社 | アクティブマトリクス型表示装置 |

| US8072394B2 (en) * | 2007-06-01 | 2011-12-06 | National Semiconductor Corporation | Video display driver with data enable learning |

| KR100911848B1 (ko) | 2008-04-01 | 2009-08-11 | 주식회사 실리콘웍스 | 액정표시장치의 소스 드라이버 칩의 내부에서 프레임스타트펄스 신호를 생성하는 방법 |

| KR101492563B1 (ko) * | 2008-08-20 | 2015-03-12 | 삼성디스플레이 주식회사 | 타이밍 컨트롤러 및 이를 갖는 표시장치 |

| JP5578411B2 (ja) * | 2010-01-13 | 2014-08-27 | Nltテクノロジー株式会社 | 表示装置の駆動回路及び駆動方法 |

| US20150194083A1 (en) * | 2014-01-03 | 2015-07-09 | Pixtronix, Inc. | Adaptive power-efficient high-speed data link between display controller and component on glass driver ics |

| US11676521B2 (en) * | 2020-06-16 | 2023-06-13 | Xiamen Tianma Micro-Electronics Co., Ltd. | Display device |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4626837A (en) * | 1983-11-17 | 1986-12-02 | Wyse Technology | Display interface apparatus |

| US5179692A (en) * | 1985-08-07 | 1993-01-12 | Seiko Epson Corporation | Emulation device for driving a LCD with signals formatted for a CRT display |

| JP2892009B2 (ja) * | 1988-05-28 | 1999-05-17 | 株式会社東芝 | 表示制御方式 |

| JP2892010B2 (ja) * | 1988-05-28 | 1999-05-17 | 株式会社東芝 | 表示制御方式 |

| EP0494610A3 (en) * | 1991-01-08 | 1993-02-03 | Kabushiki Kaisha Toshiba | Tft lcd control method for setting display controller in sleep state when no access to vram is made |

| JPH0651727A (ja) * | 1992-06-04 | 1994-02-25 | Toshiba Corp | 表示制御方法及び表示制御装置 |

-

1995

- 1995-11-28 KR KR1019950044308A patent/KR0156804B1/ko not_active Expired - Lifetime

-

1996

- 1996-11-26 JP JP31462596A patent/JP4040712B2/ja not_active Expired - Lifetime

- 1996-11-27 US US08/757,819 patent/US5828368A/en not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10165155B2 (en) | 2013-08-29 | 2018-12-25 | Sharp Kabushiki Kaisha | Image processing device |

Also Published As

| Publication number | Publication date |

|---|---|

| US5828368A (en) | 1998-10-27 |

| JPH09198014A (ja) | 1997-07-31 |

| KR0156804B1 (ko) | 1998-12-15 |

| KR970029312A (ko) | 1997-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4040712B2 (ja) | スタートパルス垂直信号生成器およびtft液晶表示装置のゲート駆動方法 | |

| JP6114703B2 (ja) | タイミングコントローラ、及びこれを有する表示装置 | |

| JP4567931B2 (ja) | 液晶表示装置のパネル駆動装置及びパネル駆動システム | |

| US11635845B2 (en) | Display driver, display device and method of driving display panel | |

| JP2016110145A (ja) | 表示パネルの駆動方法及びこれを遂行するための表示装置 | |

| KR970005937B1 (ko) | 데이타 인에이블 신호 입력시 엘.씨.디 제어신호 출력회로 | |

| JP2003228338A (ja) | 液晶表示装置 | |

| US20020003523A1 (en) | Method of processing signal of LCM timing controller | |

| KR100186556B1 (ko) | 액정표시장치 | |

| US20060092100A1 (en) | Display controlling device and controlling method | |

| US10950156B1 (en) | System of multiple timing controllers of a display panel | |

| JP2000284761A (ja) | 表示装置および表示装置用インターフェイス回路 | |

| KR20080010946A (ko) | 디스플레이장치 및 그 제어방법 | |

| JP3684264B2 (ja) | ディジタル映像信号処理用の映像制御信号発生装置 | |

| KR0182177B1 (ko) | 최적 게이트 펄스 발생 회로 | |

| JPH1011035A (ja) | コンピュータ、ディスプレイ装置およびコンピュータシステム | |

| JP7324902B2 (ja) | 表示ドライバ、表示装置及び表示パネルの駆動方法 | |

| US6154072A (en) | Signal production circuit | |

| JP3427298B2 (ja) | ビデオ信号変換装置およびlcd装置 | |

| US20040090447A1 (en) | Wide-range and balanced display position adjustment method for LCD controller | |

| KR920009008B1 (ko) | 온 스크린 표시 시스템 | |

| US6195071B1 (en) | Timing control circuit of AC type plasma display panel system | |

| US6937290B1 (en) | Method and apparatus using the Bresenham algorithm to synthesize a composite SYNC signal | |

| KR100194692B1 (ko) | 0번 게이트 라인의 구동 신호 발생 회로 | |

| US20100188379A1 (en) | Display and Method for Driving the Same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070514 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070522 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070529 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070612 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20070822 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20070827 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070921 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071016 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101116 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121116 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131116 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131116 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131116 Year of fee payment: 6 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |