JP3977053B2 - 容量素子及びその製造方法 - Google Patents

容量素子及びその製造方法 Download PDFInfo

- Publication number

- JP3977053B2 JP3977053B2 JP2001332371A JP2001332371A JP3977053B2 JP 3977053 B2 JP3977053 B2 JP 3977053B2 JP 2001332371 A JP2001332371 A JP 2001332371A JP 2001332371 A JP2001332371 A JP 2001332371A JP 3977053 B2 JP3977053 B2 JP 3977053B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- electrode

- wiring layer

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/201—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits

- H10D84/204—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors

- H10D84/212—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors of only capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/495—Capacitive arrangements or effects of, or between wiring layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/495—Capacitive arrangements or effects of, or between wiring layers

- H10W20/496—Capacitor integral with wiring layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、半導体集積回路においてアナログ回路等に使用される容量素子及びその製造方法に関する。

【0002】

【従来の技術】

これまで、半導体集積回路(IC)において、高周波数領域で直流成分をカットするために容量素子が一般に用いられている。そして、外部部品削減や端子数削減等によるコストダウンという理由から容量素子をICに内蔵することが求められていた。また、そのほか、ノイズ対策の容易さ等の理由からも容量素子をICに内蔵することが求められていた。

【0003】

従来、ICに内蔵した容量素子には必ず寄生容量が存在する。この寄生容量は、容量素子が本来有する容量の誤差となり精度の低下を招来する原因となる。また、容量自体は電力を消費することはないが、寄生容量部で無駄な電力が消費されてしまう。このため、ICにおける駆動増幅器にとっても、寄生容量が大きいとその分だけ駆動能力を上げる必要があり、この結果、消費電力が大きくなるという悪循環に陥ることにもなる。このように、ICに内蔵した容量素子の寄生容量は、ICの高速性能化の足かせともなっていた。

【0004】

かかる寄生容量を低減すべく、MOS(Metal-Oxide-Semiconductor)容量から、以下に述べる2層Poly容量やMIM(Metal-Insulator-Metal)容量等のプロセス開発がなされてきた。また、寄生容量の回路への影響を低減するための工夫が回路面やレイアウト面からなされてきた。

【0005】

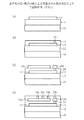

図13は、従来の容量素子の構造を示す概略図であり、図13(a)は、2層Poly容量の構造を示す断面図、図13(b)は、MIM容量の構造を示す断面図である。

【0006】

2層Poly容量は、図13(a)に示すように、シリコン基板100上の層間絶縁膜102中に、多結晶シリコン膜からなる下層電極104及び上層電極106を形成したものである。一方、MIM容量は、図13(b)に示すように、シリコン基板100上の層間絶縁膜102中にアルミニウムや、銅、窒化チタン等の金属からなる下層電極108及び上層電極110を形成したものである。最近は、寄生容量及び寄生抵抗の点で有利なMIM容量が主流となりつつある。

【0007】

ICに内蔵された容量素子は、その構造上、下層電極に寄生容量が付き易くなっている。このため、このような容量素子をICに組み込むときには、回路的に寄生容量の影響を受け難い側に下層電極を使用する。すなわち、例えば、電位が固定される側に下層電極を使用する。そして、回路的に寄生容量の影響を受けやすい側に上層電極を使用するのが一般的となっている。

【0008】

従来のMIM容量をICに適用した例として、サンプル・アンド・ホールド回路に適用した場合を図14を用いて説明する。図14(a)は、サンプル・アンド・ホールド回路に用いられたMIM容量の構造を示す断面図であり、図14(b)は、MIM容量の構造を示す上面図である。なお、図14(a)の断面図は、図14(b)のA−A′線断面を示している。また、図14に示す容量素子には、配線層間等に形成された複数の層間絶縁膜が存在するが、以下の図14の説明では、これら層間絶縁膜を一括して層間絶縁膜124と呼ぶこととする。

【0009】

図14(a)に示すように、サンプル・アンド・ホールド回路では、入力電圧が入力される入力部112と、出力電圧を出力する出力部114が、スイッチ116を介して接続されている。スイッチ116と出力部114との間には、ノード118が設けられ容量120が接続されている。容量120のノード118に対向する側が接地され電位が固定されている。この容量120として、MIM容量が用いられる。

【0010】

MIM容量では、図14(a)に示すように、基板122上に層間絶縁膜124を介して容量の下層電極としても機能する下層電極兼下部配線層126が形成されている。下層電極兼下部配線層126の上には、層間絶縁膜124を介して上層電極128が形成されている。そして、上層電極128上側には、層間絶縁膜124中に形成されたビア層130を介して上層電極128に接続する上部配線層132が形成されている。

【0011】

サンプル・アンド・ホールド回路では、その動作中にノード118が高いインピーダンスとなる期間がある。このため、容量120に寄生容量が存在すると、その寄生容量を介してノイズが乗り易くなり誤差の原因となる。そこで、このようなサンプル・アンド・ホールド回路にMIM容量を適用する場合には、一般に、図14(a)に示すように上層配線128がノード118に接続される。一方、下層電極兼下部配線層126が、接地され電位が固定される側となっている。このように、寄生容量の付き易い傾向にあるMIM容量の下層電極を固定電位とすることにより、寄生容量の影響を可能な限り低減しようとする工夫がなされていた。

【0012】

【発明が解決しようとする課題】

上述のように、ICに内蔵した容量素子の寄生容量を低減し或いは除去するために、プロセス開発や回路設計等の種々の観点からのアプローチがこれまでなされてきた。

【0013】

しかしながら、上述した従来の容量素子では、十分に寄生容量を低減することができなかった。また、従来のMIM容量の構造では、外来ノイズの影響を受けやすいという難点も存在していた。

【0014】

本発明の目的は、容量の精度低下や無駄な消費電力等の原因となる寄生容量を従来のものに比べて大幅に低減し、また、外部ノイズを遮蔽しうる容量素子及びその製造方法を提供することにある。

【0015】

【課題を解決するための手段】

上記目的は、基板上に第1の絶縁膜を介して形成された下層電極と、前記下層電極上に第2の絶縁膜を介して形成された上層電極と、前記上層電極上に第3の絶縁膜を介して形成され、前記上層電極と電気的に接続された上部配線層と、前記基板と前記下層電極との間に形成され、前記上部配線層と電気的に接続された下部配線層と、前記第1乃至第3の絶縁膜に形成されたビアホール内に埋め込まれて形成され、前記上部配線層、前記下部配線層、及び中継用配線層を電気的に接続する複数の側部配線層とを有し、前記上部配線層、及び前記下部配線層が前記上層電極、及び前記下層電極を上下方向から被い、且つ前記複数の側部配線層が前記上層電極、及び前記下層電極を側方から囲むように形成された容量素子により達成される。

【0017】

また、上記目的は、基板上に、第1の絶縁膜を介して下部配線層を形成する工程と、前記第1の絶縁膜上及び前記下部配線層上に、第2の絶縁膜を形成する工程と、前記第2の絶縁膜に埋め込まれ、前記第下部配線層に電気的に接続された第1のビア層を形成する工程と、前記第1のビア層が埋め込まれた前記第2の絶縁膜上に、前記第1のビア層を介して前記下部配線層に電気的に接続された中間配線層を形成する工程と、前記第2の絶縁膜上及び前記中間配線層上に、第3の絶縁膜を形成する工程と、前記第3の絶縁膜に埋め込まれ、前記中間配線層に電気的に接続された第2のビア層を形成する工程と、前記第2のビア層が埋め込まれた前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、前記第4の絶縁膜に埋め込まれ、前記第2のビア層に電気的に接続された中継用配線層を形成する工程と、前記中継用配線層が埋め込まれた前記第4の絶縁膜上に、下層電極を形成する工程と、前記下層電極上に、第5の絶縁膜を介して上層電極を形成する工程と、前記第4の絶縁膜上及び前記上層電極上に、第6の絶縁膜を形成する工程と、前記第6の絶縁膜に埋め込まれ、前記上層電極に電気的に接続された第3のビア層と、前記第6の絶縁膜に埋め込まれ、前記中継用配線層に電気的に接続された複数の側部配線層とを形成する工程と、前記第3のビア層及び前記複数の側部配線層が埋め込まれた前記第6の絶縁膜上に、前記第3のビア層と前記複数の側部配線層とに電気的に接続された上部配線層を形成する工程とを有し、前記下部配線層を形成する工程では、前記上層電極及び前記下層電極を下方から被うように前記下部配線層を形成し、前記複数の側部配線層を形成する工程では、前記上層電極及び前記下層電極を側方から囲むように前記複数の側部配線層を形成し、前記上部配線層を形成する工程では、前記上層電極及び前記下層電極を上方から被うように前記上部配線層を形成することを特徴とする容量素子の製造方法により達成される。

【0019】

【発明の実施の形態】

[第1実施形態]

本発明の第1実施形態による容量素子及びその製造方法について図1乃至図4を用いて説明する。図1は、本実施形態による容量素子の構造を示す概略図、図2乃至図4は、本実施形態による容量素子の製造方法を示す工程断面図である。

【0020】

まず、本実施形態による容量素子について図1を用いて説明する。図1(a)は、本実施形態による容量素子の構造を示す断面図、図1(b)は、本実施形態による容量素子の構造を示す上面図である。図1(a)では、本実施形態による容量素子を、サンプル・アンド・ホールド回路に適用した場合を示している。サンプル・アンド・ホールド回路は、一般に、IC等においてA/D変換器等の入力電圧を標本化し、保持するために使用される回路である。なお、図1(a)は、図1(b)のA−A′線断面を示している。また、本実施形態による容量素子には、配線層間等に形成された複数の層間絶縁膜が存在するが、便宜上以下の説明では、これら層間絶縁膜を一括して層間絶縁膜12と呼ぶこととする。

【0021】

本実施形態による容量素子では、基板10上に、層間絶縁膜12を介して下部配線層14が形成されている。下部配線層14の上には、層間絶縁膜12を介し中間配線層16aが形成されている。中間配線層16a上には、層間絶縁膜12を介してMIM容量の下層電極22が形成されている。中間配線層と16aと下層電極22とは、ビア層18a、中継用配線層20aを介して電気的に接続されている。

【0022】

下層電極22上には、層間絶縁膜12を介してMIM容量の上層電極24が形成されている。上層電極24上には、層間絶縁膜12を介して上部配線層28が形成されている。上層電極24と上部配線層28とは、ビア層26aを介して電気的に接続されている。

【0023】

また、上部配線層28は、ビア層29、中間配線層16b、ビア層18b、中継用配線層20b、ビア層26bを介して下部配線層14に電気的に接続されている。中間配線層16bは、中間配線層16aと同層に形成されている。中継用配線層20bは、中継用配線層20aと同層に形成されている。

【0024】

また、中継用配線層20a、20bと同層に中継用配線層20cが形成されており、上部配線層28と中継用配線層20cとがビア層26cを介して接続されている。ビア層26c及び中継用配線層20cは、図1(b)に示すように、下層電極22及び上層電極24の周囲を囲むように複数形成されている。

【0025】

図1(a)に示すように、サンプル・アンド・ホールド回路では、入力電圧が入力される入力部30と、出力電圧を出力する出力部32が、スイッチ34を介して接続されている。スイッチ34と出力部32との間には、ノード36が設けられ容量38が接続されている。容量38のノード36に対向する側が接地され電位が固定されている。この容量38として、上記構造を有する本実施形態による容量素子が用いられる。

【0026】

すなわち、サンプル・アンド・ホールド回路において、本実施形態による容量素子の中間配線層16aがノード36に接続され、下部配線層14に電気的に接続している上部配線層28が、接地され電位が常時固定される側となっている。

【0027】

本実施形態による容量素子は、下層電極22と基板10との間に形成された下部配線層14と、下部配線層14と上部配線層28とを接続するビア層29等からなる配線類と、下層電極22及び上層電極24の側方に形成されたビア層26cとを有することに特徴がある。このように、MIM容量の下層電極22及び上層電極24を配線類で被うことにより寄生容量が生じるのを防止することができる。さらに、MIM容量の下層電極22及び上層電極24を被う配線類がシールドとして機能し、外来ノイズを遮蔽することができる。

【0028】

ここで、上記構造を有する本実施形態による容量素子をサンプル・アンド・ホールド回路の容量38として適用した場合の効果について説明する。

【0029】

サンプル・アンド・ホールド回路では、スイッチ34を短時間オンにすることにより、容量38に入力電位を充電する。この期間をサンプリング期間という。次いで、スイッチ34をオフにすると、容量38に充電された電圧は保持され次にスイッチ34をオンにするまで保持された電位は変化しない。この期間をホールド期間という。このホールド期間中は、ノード36が高いインピーダンスとなるため、容量38に寄生容量が存在すると、その寄生容量を介してノイズが乗りやすく誤差の原因となる。

【0030】

本実施形態による容量素子のように、配線類により被われた下層電極22を寄生容量の影響を受けやすいノード36側の電極として使用し、上層電極24を固定電位側とすることにより、寄生容量に影響されず、より精度の高い回路を実現することができる。

【0031】

次に、本実施形態による容量素子の製造方法について図2乃至図4を用いて説明する。

【0032】

まず、基板10上に層間絶縁膜12を形成する。次いで、層間絶縁膜12上に、例えばアルミニウム膜を形成し、下部配線層14にパターニングする(図2(a))。

【0033】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に、下部配線層14に達するビアホールを形成する。次いで、全面に金属膜を形成しビアホールに金属膜を埋め込む。次いで、CMP(Chemical Mechanical Polishing)により、ビアホールに埋め込まれたもの以外の余分な金属膜を除去する。こうして、下部配線層14に電気的に接続するビア層29を形成する(図2(b))。

【0034】

次いで、全面に、例えばアルミニウム膜を形成し、通常のリソグラフィー技術により、中間配線層16a、16bにパターニングする(図2(c))。

【0035】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に、中間配線層16aに達するビアホールと、中間配線層16bに達するビアホールとを形成する。次いで、全面に金属膜を形成し、これらビアホールに金属膜を埋め込む。次いで、CMPにより、ビアホールに埋め込まれたもの以外の余分な金属膜を除去する。こうして、中間配線層16aに電気的に接続するビア層18aと、中間配線層16bに電気的に接続するビア層18bとを形成する(図2(d))。

【0036】

次いで、銅配線プロセスに適用されるダマシン法を用いて中継用配線層20a、20b、20cを形成する。すなわち、全面に、層間絶縁膜12を形成し、層間絶縁膜12中にビア層18a、18bに達する溝と、いずれにも達しない溝とを形成する。次いで、全面に例えば銅膜を形成し、これら溝中に銅膜を埋め込む。 次いで、CMPにより、溝に埋め込まれたもの以外の余分な銅膜を除去する。こうして、ビア層18aに電気的に接続する中継用配線層20aと、ビア層18bに電気的に接続する中継用配線層20bと、いずれにも接続しない中継用配線層20cとを形成する(図3(a))。

【0037】

次いで、全面に、窒化チタン膜40a、層間絶縁膜12、窒化チタン膜40bを順次形成する。(図3(b))。

【0038】

次いで、通常のリソグラフィー技術により、積層された窒化チタン膜40a、層間絶縁膜12、窒化チタン膜40bをパターニングし、溝に埋め込まれた中継用配線層20aと接触する下層電極22と、層間絶縁膜12を介して下層電極22に対向する上層電極24とを形成する(図3(c))。

【0039】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に上層電極24に達するビアホールと、中継用配線層20b、20cに達するビアホールとを形成する。次いで、全面に金属膜を形成し、これらビアホールに金属膜を埋め込む。次いで、CMPにより、ビアホールに埋め込まれたもの以外の余分な金属膜を除去する。こうして、上層電極24に電気的に接続するビア層26aと、中継用配線層20bに電気的に接続するビア層26bと、中継用配線層20cに電気的に接続するビア層26cとを形成する(図4(a))。

【0040】

次いで、ビア層26a、26b、26cに接続する上部配線層28を形成する。次いで、全面に、層間絶縁膜12を形成し、本実施形態による容量素子の製造を終了する(図4(b))。

【0041】

このように、本実施形態によれば、MIM容量の下層電極22及び上層電極24を配線類により上下側方から被うので、寄生容量が生じるのを防止することができ、また、外来ノイズを遮断することができる。

【0042】

[第2実施形態]

本発明の第2実施形態による容量素子及びその製造方法について図5を用いて説明する。図5は、本実施形態による容量素子の構造を示す断面図である。なお、第1実施形態による容量素子及びその製造方法と同一の構成要素については同一の符号を付し説明を省略或いは簡略にする。

【0043】

本実施形態による容量素子は、第1実施形態による容量素子の中継用配線層20a、20b、20cと中間配線層16a、16bとの間に、配線層を一層追加し、下層電極22に対してアレイ状の配線パターンからなる配線容量を形成したものである。

【0044】

すなわち、中継用配線層20a、20b、20cには、ビア層18a、18b、18cを介して、配線層41a、41b、41cが接続されている。

【0045】

配線層41aのいずれかに、ビア層42aを介して中間配線層16aが接続している。配線層41bは、ビア層42bを介して中間配線層16bに接続している。また、下部配線層14には、中間配線層16aに接続していない配線層41aに対向するように、中間配線層16cがビア層29aを介して接続されている。中継用配線層20aと配線層41aと中間配線層16cとはほぼ同一の面積を有している。また、配線層41aと中間配線層16cとは層間絶縁膜12を介して対向している。

【0046】

このように、本実施形態による容量素子は、中継用配線層20a及び配線層41aと、中間配線層16cとからなるアレイ状の配線パターンが配線間容量をなしていることに主たる特徴がある。このように、MIM容量の下層電極22と下部配線層14との間にアレイ状の配線パターンからなる配線間容量を形成することにより、これらがMIM容量に対して一定比率の容量となるため、MIM容量の精度の低下を防止することができる。

【0047】

本実施形態による容量素子は、第1実施形態による容量素子の製造方法において、中継用配線層20a、20b、20cを形成する工程の前段に、配線層41a、41b、41cを形成する工程を追加することにより製造することができる。なお、中間配線層16a、16bを製造する際に、ビア層29aを介して下部配線層14に接続され、配線層41aに対向する中間配線層16cを同時に形成する必要がある。

【0048】

このように、本実施形態によれば、MIM容量の下層電極22及び上層電極24を配線類により上下側方から被うので、寄生容量が生じるのを防止することができ、また、外来ノイズを遮断することができる。さらに、下層電極22に対してアレイ状の配線間容量を形成するので、より精度の高い容量を実現することができる。

【0049】

なお、上記実施形態では、中継用配線層20a及び配線層41aとの2層とからなるアレイ状の配線パターンを形成していたが、配線層41aのみならず複数の配線層を追加してアレイ状の配線パターンを構成してもよい。

【0050】

この際、追加する複数の配線層及び配線層間のビア層を、同じ配線マスク及び同じビアマスクを用いたリソグラフィー技術により、配線層及びビア層を積み重ねて形成してもよい。こうすることで、簡単にアレイ状の配線パターンを形成することができる。

【0051】

また、配線間容量を形成する中継用配線層20a及び配線層41aと対向する中間配線層16cの組み合わせの数は、下層電極の面積に比例するように設定することが望ましい。これにより、より正確に容量を算出することができ、より精度の高いMIM容量を得ることができる。

【0052】

[第3実施形態]

本発明の第3実施形態による容量素子及びその製造方法について図6乃至図9を用いて説明する。図6は、本実施形態による容量素子の構造を示す概略図、図7乃至図9は、本実施形態による容量素子の製造方法を示す工程断面図である。なお、第1実施形態による容量素子及びその製造方法と同一の構成要素については同一の符号を付し説明を省略或いは簡略にする。

【0053】

まず、本実施形態による容量素子について図6を用いて説明する。図6(a)は、本実施形態による容量素子の構造を示す断面図、図6(b)は、本実施形態による容量素子の構造を示す上面図である。図6(a)では、第1実施形態と同様に、本実施形態による容量素子をサンプル・アンド・ホールド回路に適用した場合を示している。なお、図6(a)は、図6(b)のA−A′線断面を示している。

【0054】

本実施形態による容量素子では、基板10上に、層間絶縁膜12を介してMIM容量の下層電極として機能する下層電極兼下部配線層44が形成されている。下層電極兼下部配線層44の上には、層間絶縁膜12を介してMIM容量の上層電極46が形成されている。上層電極46上には、層間絶縁膜12を介して中間配線層50が形成されている。上層電極46と中間配線層50とは、ビア層48を介して電気的に接続されている。

【0055】

中間配線層50上には、層間絶縁膜12を介して上部配線層52が形成されている。上部配線層52は、ビア層54、中間配線層56、ビア層58を介して下層電極兼下部配線層44に電気的に接続されている。中間配線層56は、中間配線層50と同層に形成されている。

【0056】

図6(a)に示すように、第1実施形態と同様に、サンプル・アンド・ホールド回路の容量38として、上記構造を有する本実施形態による容量素子が用いられる。すなわち、サンプル・アンド・ホールド回路において、本実施形態による容量素子の中間配線層50がノード36に接続され、下層電極兼下部配線層44に電気的に接続している上部配線層52が、接地され電位が常時固定される側となっている。

【0057】

本実施形態による容量素子は、上層電極46の上側に、下層電極兼下部配線層44に接続され、下層電極兼下部配線層44とともにMIM容量の上層電極46を挟む上部配線層52を有することに主たる特徴がある。このように、下層電極兼下部配線層44と上部配線層52とにより上層電極46を挟む構造とすることにより、寄生容量が生ずるのを抑えることができる。また、上部配線層52がシールドとして機能し、外来のノイズから上層電極46を遮断することができる。

【0058】

次に、本実施形態による容量素子の製造方法について図7乃至9を用いて説明する。

【0059】

まず、基板10上に層間絶縁膜12を形成する。次いで、層間絶縁膜12上に、例えばアルミニウム膜を形成する。次いで、形成したアルミニウム膜を通常のリソグラフィー技術により、MIM容量の下層電極及び配線として機能する下層電極兼下部配線層44にパターニングする(図7(a))。

【0060】

次いで、全面に、層間絶縁膜12と窒化チタン膜60とを順次形成する(図7(b))。

【0061】

次いで、通常のリソグラフィー技術により、層間絶縁膜12及び窒化チタン膜60をパターニングし、層間絶縁膜12を介して下層電極兼下部配線層44に対向する上層電極46を形成する(図7(c))。

【0062】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に、上層電極46に達するビアホール62と、下層電極兼下部配線層44に達するビアホール64とを形成する(図7(d))。

【0063】

次いで、全面に金属膜を形成しビアホール62、44に金属膜を埋め込む。次いで、CMPにより、ビアホール62、44に埋め込まれたもの以外の余分な金属膜を除去する。こうして、上層電極46に電気的に接続するビア層48と、下層電極兼下部配線層44に電気的に接続するビア層54とを形成する(図8(a))。

【0064】

次いで、全面に、例えばアルミニウム膜を形成する。次いで、通常のリソグラフィー技術により、形成したアルミニウム膜を各ビア層48、54に接続する中間配線層50、56にパターニングする(図8(b))。

【0065】

次いで、全面に、層間絶縁膜12を形成し、下層電極兼下部配線層44に接続する中間配線層56に達するビアホール66を形成する(図8(c))。

【0066】

次いで、全面に、金属膜を形成しビアホール66に金属膜を埋め込む。次いで、CMPにより、ビアホール66に埋め込まれたもの以外の余分な金属膜を除去する。こうして、中間配線層56に電気的に接続するビア層58を形成する(図9(a))。

【0067】

次いで、全面に、例えばアルミニウム膜を形成し、通常のリソグラフィー技術により、アルミニウム膜をビア層58に接続する上部配線層52にパターニングする(図9(b))。

【0068】

次いで、全面に、層間絶縁膜12を形成し、本実施形態による容量素子の製造を終了する(図9(c))。

【0069】

このように、本実施形態によれば、MIM容量の上層電極46を下層電極兼下部配線層44と、下層電極兼下部配線層44に電気的に接続された上部配線層52とにより被うので、寄生容量が生じるのを防止することができ、また、外来ノイズを遮断することができる。

【0070】

なお、第1実施形態において、ビア層26c及び中継用配線層20cを、下層電極22及び上層電極24の周囲と囲むように複数形成していたように、本実施形態においても、下層電極兼下部配線層44に接続されたビア層等を上層電極46の周囲を囲むように複数形成してもよい。こうすることで、より効果的に外来ノイズを遮断することができる。

【0071】

[第4実施形態]

本発明の第4実施形態による容量素子及びその製造方法について図10乃至図12を用いて説明する。図10は、本実施形態による容量素子の構造を示す概略図、図11及び図12は、本実施形態による容量素子の製造方法を示す工程断面図である。なお、第1乃至第3実施形態による容量素子及びその製造方法と同一の構成要素については同一の符号を付し説明を省略或いは簡略にする。

【0072】

まず、本実施形態による容量素子について図10を用いて説明する。図10(a)は、本実施形態による容量素子の構造を示す断面図、図10(b)は、本実施形態による容量素子の構造を示す上面図である。図10(a)では、第1実施形態と同様に、本実施形態による容量素子をサンプル・アンド・ホールド回路に適用した場合を示している。なお、図10(a)は、図10(b)のA−A′線断面を示している。

【0073】

本実施形態による容量素子では、図10(a)に示すように、基板10上に層間絶縁膜12を介して下部配線層68が形成されている。下部配線層68上には、層間絶縁膜12を介してMIM容量の下層電極70が形成されている。下部配線層68と下層電極70とは、ビア層72、中継用配線層74を介して電気的に接続されている。

【0074】

下層電極70上には、層間絶縁膜12を介してMIM容量の上層電極46が形成されている。上層電極46上には、層間絶縁膜12を介して中間配線層50が形成されている。上層電極46と中間配線層50とは、ビア層48を介して電気的に接続されている。

【0075】

中間配線層50の上には、層間絶縁膜12を介して上部配線層52が形成されている。上部配線層52は、ビア層76、中継用配線層78、ビア層80、中間配線層56、ビア層58を介して下部配線層68に電気的に接続されている。中継用配線層78は、中継用配線層74と同層に形成されている。中間配線層56は、中間配線層50と同層に形成されている。

【0076】

サンプル・アンド・ホールド回路においては、第3実施形態と同様に、中間配線層50がノード36に接続され、下層電極70に接続する上部配線層52が、接地され電位が固定される側となっている。

【0077】

本実施形態による容量素子は、上層電極46の上側に、下部配線層68に電気的に接続され、下部配線層68とともにMIM容量の上層電極46を挟む上部配線層52を有することに主たる特徴がある。このように、下部配線層68と上部配線層52とにより上層電極46を挟む構造とすることにより、寄生容量が生ずるのを抑えることができる。また、上部配線層52がシールドとして機能し、外来のノイズから上層電極46を遮断することができる。

【0078】

次に、本実施形態による容量素子の製造方法について図11及び図12を用いて説明する。

【0079】

まず、基板10上に層間絶縁膜12を形成する。次いで、層間絶縁膜12上に、例えばアルミニウム膜を形成する。次いで、形成したアルミニウム膜を通常のリソグラフィー技術により、下部配線層68にパターニングする(図11(a))。

【0080】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に下部配線層68に達するビアホールを形成する。次いで、全面に、金属膜を形成しビアホール中に金属膜を埋め込む。次いで、CMPにより、ビアホールに埋め込まれたもの以外の余分な金属膜を除去する。こうして、下部配線層68に電気的に接続するビア層72、76を形成する(図11(b))。

【0081】

次いで、銅配線プロセスに適用されるダマシン法を用いて中継用配線層74、78を形成する。すなわち、全面に、層間絶縁膜12を形成し、層間絶縁膜12中にビア層72、76に達する溝を形成する。次いで、全面に例えば銅膜を形成し溝中に銅膜を埋め込む。次いで、CMPにより、溝に埋め込まれたもの以外の余分な銅膜を除去する。こうして、ビア層72、76に電気的に接続する中継用配線層74、78を形成する(図11(c))。

【0082】

次いで、全面に、窒化チタン膜82a、層間絶縁膜12、窒化チタン膜82bを順次形成する。(図11(d))。

【0083】

次いで、通常のリソグラフィー技術により、積層された窒化チタン膜82a、層間絶縁膜12、窒化チタン膜82bをパターニングし、溝に埋め込まれた中継用配線層74と接触する下層電極70と、層間絶縁膜12を介して下層電極70に対向する上層電極46とを形成する(図12(a))。

【0084】

次いで、全面に、層間絶縁膜12を形成し、層間絶縁膜12中に上層電極46に達するビアホールと、中継用配線層78に達するビアホールとを形成する。次いで、全面に金属膜を形成しビアホールに金属膜を埋め込む。次いで、CMPにより、ビアホールに埋め込まれたもの以外の余分な金属膜を除去する。こうして、上層電極46に電気的に接続するビア層48と、中継用配線層78に電気的に接続するビア層80とを形成する(図12(b))。

【0085】

次いで、第1実施形態と同様に、ビア層48に接続する中間配線層50と、ビア層80に接続する中間配線層56とを形成する。次いで、全面に層間絶縁膜12を形成した後、中間配線層56にビア層58を介して接続する上部配線層52を形成する。次いで、全面に層間絶縁膜12を形成し、本実施形態による容量素子の製造を終了する(図12(c))。

【0086】

このように、本実施形態によれば、MIM容量の上層電極46を下部配線層68と、下部配線層68に電気的に接続する上部配線層52とにより被うので、寄生容量が生じるのを防止することができ、また、外来ノイズを遮断することができる。

【0087】

[変形実施形態]

本発明の上記実施形態に限らず種々の変形が可能である。

【0088】

例えば、上記実施形態では、下部配線層14や、中間配線層16a、16b、上部配線層28、下層電極兼下部配線層44、中間配線層50、上部配線層52、中間配線層56、下部配線層68等の配線層を、通常のリソグラフィー技術によりアルミニウム配線として形成していたが、これら配線層を、ダマシン法により銅配線として形成してもよい。

【0089】

また、上記実施形態では、本発明による容量素子をサンプル・アンド・ホールド回路に適用した場合を示していたが、適用可能な回路はサンプル・アンド・ホールド回路に限定されるものではない。他の回路に適用する場合においても、サンプル・アンド・ホールド回路に適用した場合と同様に電位等を考慮して、上層電極及び下層電極の接続を決定することが望ましい。

【0090】

以上詳述したように、本発明による容量素子及びその製造方法の特徴をまとめると以下の通りになる。

【0091】

(付記1) 基板上に第1の絶縁膜を介して形成された下層電極と、前記下層電極に対して第2の絶縁膜を介して対向する上層電極と、前記基板と前記下層電極の間に形成され、前記上層電極に電気的に接続された下部配線層とを有することを特徴とする容量素子。

【0092】

(付記2) 付記1記載の容量素子において、前記上層電極に電気的に接続され、前記下層電極を側方から被うように形成された側部配線層を更に有することを特徴とする容量素子。

【0093】

(付記3) 付記1又は2記載の容量素子において、前記下層電極と前記下部配線層との間に、前記下層電極に接続された第1の配線パターンと、前記第1の配線パターンに対向し、前記下部配線層に接続された第2の配線パターンとを更に有することを特徴とする容量素子。

【0094】

(付記4) 付記3記載の容量素子において、前記第1の配線パターンは、複数の配線容量用配線層がアレイ状に配列されたものであり、前記第2の配線パターンは、前記第1の配線パターンの配線容量用配線層の各々に対向するように配列された複数の配線容量用配線層がアレイ状に配列されたものであることを特徴とする容量素子。

【0095】

(付記5) 基板上に第1の絶縁膜を介して形成された下層電極と、前記下層電極に対して第2の絶縁膜を介して対向する上層電極と、前記基板と前記下層電極の間に形成され、前記下層電極に電気的に接続された下部配線層と、前記上層電極上に第3の絶縁膜を介して形成され、前記下部配線層に電気的に接続された上部配線層とを有することを特徴とする容量素子。

【0096】

(付記6) 付記5記載の容量素子において、前記下層電極に電気的に接続され、前記下層電極を側方から被うように形成された側部配線層を更に有することを特徴とする容量素子。

【0097】

(付記7) 基板上に第1の絶縁膜を介して下層電極を形成する工程と、前記下層電極に対して第2の絶縁膜を介して対向する上層電極を形成する工程とを有する容量素子の製造方法であって、前記基板と前記下層電極の間に、前記上層電極に電気的に接続された下部配線層を形成する工程を更に有することを特徴とする容量素子の製造方法。

【0098】

(付記8) 付記7記載の容量素子の製造方法において、前記上層電極に電気的に接続され、前記下層電極を側方から被う側部配線層を形成する工程を更に有することを特徴とする容量素子の製造方法。

【0099】

(付記9) 付記7又は8記載の容量素子の製造方法において、前記下層電極と前記下部配線層との間に、前記下層電極に接続された第1の配線パターンを形成する工程と、前記第1の配線パターンに対向し、前記下部配線層に接続された第2の配線パターンとを形成する工程とを更に有することを特徴とする容量素子の製造方法。

【0100】

(付記10) 付記9記載の容量素子の製造方法において、複数の配線容量用配線層をアレイ状に配列するように形成して前記第1の配線パターンを形成し、前記第1の配線パターンの配線容量用配線層の各々に対向するように、複数の配線容量用配線層をアレイ状に配列するように形成して前記第2の配線パターンを形成することを特徴とする容量素子の製造方法。

【0101】

(付記11) 付記9又は10記載の容量素子の製造方法において、前記第1の配線パターン及び前記第2の配線パターンの形成には、同一の配線形成用マスク及びビア形成用マスクを用いることを特徴とする容量素子の製造方法。

【0102】

(付記12) 基板上に第1の絶縁膜を介して下層電極を形成する工程と、前記下層電極に対して第2の絶縁膜を介して対向する上層電極を形成する工程と、前記基板と前記下層電極の間に、前記下層電極に電気的に接続された下部配線層を形成する工程と、前記上層電極上に第3の絶縁膜を介して、前記下部配線層に電気的に接続された上部配線層を形成する工程とを有することを特徴とする容量素子の製造方法。

【0103】

(付記13) 付記12記載の容量素子の製造方法において、前記下層電極に電気的に接続され、前記下層電極を側方から被う側部配線層を形成する工程を更に有することを特徴とする容量素子の製造方法。

【0104】

【発明の効果】

以上の通り、本発明によれば、基板上に第1の絶縁膜を介して形成された下層電極と、下層電極に対して第2の絶縁膜を介して対向する上層電極と、基板と下層電極の間に形成され、上層電極に電気的に接続された下部配線層とを有するので、容量の精度低下や無駄な消費電力等の原因となる寄生容量を従来のものに比べて大幅に低減することができ、また、外部ノイズを遮蔽することができる。

【0105】

また、基板上に第1の絶縁膜を介して形成された下層電極と、下層電極に対して第2の絶縁膜を介して対向する上層電極と、基板と前記下層電極の間に形成され、下層電極に電気的に接続された下部配線層と、上層電極上に第3の絶縁膜を介して形成され、下部配線層に電気的に接続された上部配線層とを有するので、同様に寄生容量を大幅に低減することができ、また、外来ノイズを遮蔽することができる。

【図面の簡単な説明】

【図1】本発明の第1実施形態による容量素子の構造を示す概略図である。

【図2】本発明の第1実施形態による容量素子の製造方法を示す工程断面図(その1)である。

【図3】本発明の第1実施形態による容量素子の製造方法を示す工程断面図(その2)である。

【図4】本発明の第1実施形態による容量素子の製造方法を示す工程断面図(その3)である。

【図5】本発明の第2実施形態による容量素子の構造を示す断面図である。

【図6】本発明の第3実施形態による容量素子の構造を示す概略図である。

【図7】本発明の第3実施形態による容量素子の製造方法を示す工程断面図(その1)である。

【図8】本発明の第3実施形態による容量素子の製造方法を示す工程断面図(その2)である。

【図9】本発明の第3実施形態による容量素子の製造方法を示す工程断面図(その3)である。

【図10】本発明の第4実施形態による容量素子の構造を示す概略図である。

【図11】本発明の第4実施形態による容量素子の製造方法を示す工程断面図(その1)である。

【図12】本発明の第4実施形態による容量素子の製造方法を示す工程断面図(その2)である。

【図13】従来の容量素子の構造を示す概略図である。

【図14】従来の容量素子をサンプリング・アンド・ホールド回路に適用した場合を示す概略図である。

【符号の説明】

10…基板

12…層間絶縁膜

14…下部配線層

16a、16b、16c…中間配線層

18a、18b、18c…ビア層

20a、20b、20c…中継用配線層

22…下層電極

24…上層電極

26a、26b、26c…ビア層

28…上部配線層

29、29a…ビア層

30…入力部

32…出力部

34…スイッチ

36…ノード

38…容量

40a、40b…窒化チタン膜

41a、41b、41c…配線層

42a、42b…ビア層

44…下層電極兼下部配線層

46…上層電極

48…ビア層

50…中間配線層

52…上部配線層

54…ビア層

56…中間配線層

58…ビア層

60…窒化チタン膜

62…ビアホール

64…ビアホール

66…ビアホール

68…下部配線層

70…下層電極

72…ビア層

74…中継用配線層

76…ビア層

78…中継用配線層

80…ビア層

82a、82b…窒化チタン膜

100…シリコン基板

102…層間絶縁膜

104…下層電極

106…上層電極

108…下層電極

110…上層電極

112…入力部

114…出力部

116…スイッチ

118…ノード

120…容量

122…基板

124…層間絶縁膜

126…下層電極兼下部配線層

128…上層電極

130…ビア層

132…上部配線層

Claims (4)

- 基板上に第1の絶縁膜を介して形成された下層電極と、

前記下層電極上に第2の絶縁膜を介して形成された上層電極と、

前記上層電極上に第3の絶縁膜を介して形成され、前記上層電極と電気的に接続された上部配線層と、

前記基板と前記下層電極との間に形成され、前記上部配線層と電気的に接続された下部配線層と、

前記第1乃至第3の絶縁膜に形成されたビアホール内に埋め込まれて形成され、前記上部配線層、前記下部配線層、及び中継用配線層を電気的に接続する複数の側部配線層とを有し、

前記上部配線層、及び前記下部配線層が前記上層電極、及び前記下層電極を上下方向から被い、且つ前記複数の側部配線層が前記上層電極、及び前記下層電極を側方から囲むように形成された容量素子。 - 請求項1記載の容量素子において、

前記下層電極と前記下部配線層との間に、前記下層電極に接続された第1の配線パターンと、

前記第1の配線パターンと前記下部配線層との間に、前記下部配線層に接続された第2の配線パターンとを更に有する

ことを特徴とする容量素子。 - 請求項2記載の容量素子において、

前記第1の配線パターンは、複数の配線容量用配線層が平面的にアレイ状に配列されたものであり、

前記第2の配線パターンは、前記第1の配線パターンの配線容量用配線層の各々に平行な複数の配線容量用配線層が平面的にアレイ状に配列されたものである

ことを特徴とする容量素子。 - 基板上に、第1の絶縁膜を介して下部配線層を形成する工程と、

前記第1の絶縁膜上及び前記下部配線層上に、第2の絶縁膜を形成する工程と、

前記第2の絶縁膜に埋め込まれ、前記第下部配線層に電気的に接続された第1のビア層を形成する工程と、

前記第1のビア層が埋め込まれた前記第2の絶縁膜上に、前記第1のビア層を介して前記下部配線層に電気的に接続された中間配線層を形成する工程と、

前記第2の絶縁膜上及び前記中間配線層上に、第3の絶縁膜を形成する工程と、

前記第3の絶縁膜に埋め込まれ、前記中間配線層に電気的に接続された第2のビア層を形成する工程と、

前記第2のビア層が埋め込まれた前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

前記第4の絶縁膜に埋め込まれ、前記第2のビア層に電気的に接続された中継用配線層を形成する工程と、

前記中継用配線層が埋め込まれた前記第4の絶縁膜上に、下層電極を形成する工程と、

前記下層電極上に、第5の絶縁膜を介して上層電極を形成する工程と、

前記第4の絶縁膜上及び前記上層電極上に、第6の絶縁膜を形成する工程と、

前記第6の絶縁膜に埋め込まれ、前記上層電極に電気的に接続された第3のビア層と、前記第6の絶縁膜に埋め込まれ、前記中継用配線層に電気的に接続された複数の側部配線層とを形成する工程と、

前記第3のビア層及び前記複数の側部配線層が埋め込まれた前記第6の絶縁膜上に、前記第3のビア層と前記複数の側部配線層とに電気的に接続された上部配線層を形成する工程とを有し、

前記下部配線層を形成する工程では、前記上層電極及び前記下層電極を下方から被うように前記下部配線層を形成し、

前記複数の側部配線層を形成する工程では、前記上層電極及び前記下層電極を側方から 囲むように前記複数の側部配線層を形成し、

前記上部配線層を形成する工程では、前記上層電極及び前記下層電極を上方から被うように前記上部配線層を形成する

ことを特徴とする容量素子の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001332371A JP3977053B2 (ja) | 2001-10-30 | 2001-10-30 | 容量素子及びその製造方法 |

| KR1020020014653A KR100777902B1 (ko) | 2001-10-30 | 2002-03-19 | 용량 소자 및 그 제조 방법 |

| US10/102,798 US6646860B2 (en) | 2001-10-30 | 2002-03-22 | Capacitor and method for fabricating the same |

| TW091105610A TW543053B (en) | 2001-10-30 | 2002-03-22 | Capacitor and method for fabricating the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001332371A JP3977053B2 (ja) | 2001-10-30 | 2001-10-30 | 容量素子及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003133424A JP2003133424A (ja) | 2003-05-09 |

| JP2003133424A5 JP2003133424A5 (ja) | 2005-04-07 |

| JP3977053B2 true JP3977053B2 (ja) | 2007-09-19 |

Family

ID=19147793

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001332371A Expired - Lifetime JP3977053B2 (ja) | 2001-10-30 | 2001-10-30 | 容量素子及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6646860B2 (ja) |

| JP (1) | JP3977053B2 (ja) |

| KR (1) | KR100777902B1 (ja) |

| TW (1) | TW543053B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6873185B2 (en) | 2002-06-19 | 2005-03-29 | Viasic, Inc. | Logic array devices having complex macro-cell architecture and methods facilitating use of same |

| JP2004327619A (ja) * | 2003-04-23 | 2004-11-18 | Toshiba Corp | 半導体集積回路装置及びその製造方法 |

| US6940707B2 (en) * | 2003-07-03 | 2005-09-06 | Matsushita Electric Industrial Co., Ltd. | Differential capacitor, differential antenna element, and differential resonator |

| US7390518B2 (en) * | 2003-07-11 | 2008-06-24 | Cadbury Adams Usa, Llc | Stain removing chewing gum composition |

| US7187536B2 (en) * | 2003-08-28 | 2007-03-06 | Tessera, Inc. | Structure and method of making a capacitor having low equivalent series resistance |

| JP3954561B2 (ja) * | 2003-11-27 | 2007-08-08 | 沖電気工業株式会社 | 半導体集積回路の多層化電源ラインおよびそのレイアウト方法 |

| US7335966B2 (en) * | 2004-02-26 | 2008-02-26 | Triad Semiconductor, Inc. | Configurable integrated circuit capacitor array using via mask layers |

| WO2005098954A1 (en) * | 2004-04-02 | 2005-10-20 | Triad Semiconductor, Inc. | Via configurable architecture for customization of analog circuitry in a semiconductor device |

| US7334208B1 (en) | 2004-11-09 | 2008-02-19 | Viasic, Inc. | Customization of structured ASIC devices using pre-process extraction of routing information |

| KR100794521B1 (ko) | 2005-12-17 | 2008-01-16 | 삼성전자주식회사 | 커패시터 어레이 |

| JP2007294848A (ja) * | 2006-03-30 | 2007-11-08 | Eudyna Devices Inc | キャパシタおよび電子回路 |

| US7411270B2 (en) * | 2006-04-03 | 2008-08-12 | Freescale Semiconductor, Inc. | Composite capacitor and method for forming the same |

| US7692309B2 (en) * | 2007-09-06 | 2010-04-06 | Viasic, Inc. | Configuring structured ASIC fabric using two non-adjacent via layers |

| US7626802B2 (en) * | 2007-10-19 | 2009-12-01 | Oh Young Joo | Metal capacitor and manufacturing method thereof |

| JP5104403B2 (ja) * | 2008-02-29 | 2012-12-19 | 富士通株式会社 | キャパシタ |

| US8362589B2 (en) * | 2008-11-21 | 2013-01-29 | Xilinx, Inc. | Integrated capacitor with cabled plates |

| US9287350B2 (en) * | 2014-07-22 | 2016-03-15 | Taiwan Semiconductor Manufacturing Co., Ltd. | Metal-insulator-metal capacitor |

| JP6384553B2 (ja) * | 2017-02-07 | 2018-09-05 | 株式会社ソシオネクスト | 容量素子、容量アレイおよびa/d変換器 |

| CN110323334B (zh) * | 2019-07-09 | 2023-03-24 | 四川中微芯成科技有限公司 | 一种用寄生电容做adc电容的结构及方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2508301B2 (ja) | 1989-10-23 | 1996-06-19 | 日本電気株式会社 | 半導体集積回路 |

| US5330931A (en) * | 1993-09-22 | 1994-07-19 | Northern Telecom Limited | Method of making a capacitor for an integrated circuit |

| US5814850A (en) * | 1995-08-22 | 1998-09-29 | Nippon Steel Corporation | Semiconductor device including a capacitor responsible for a power supply voltage to semiconductor device and capable of blocking an increased voltage |

| US5633781A (en) * | 1995-12-22 | 1997-05-27 | International Business Machines Corporation | Isolated sidewall capacitor having a compound plate electrode |

| US5926359A (en) * | 1996-04-01 | 1999-07-20 | International Business Machines Corporation | Metal-insulator-metal capacitor |

| US6078072A (en) * | 1997-10-01 | 2000-06-20 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device having a capacitor |

| JP3842111B2 (ja) * | 2001-11-13 | 2006-11-08 | 富士通株式会社 | 半導体装置及びその製造方法 |

-

2001

- 2001-10-30 JP JP2001332371A patent/JP3977053B2/ja not_active Expired - Lifetime

-

2002

- 2002-03-19 KR KR1020020014653A patent/KR100777902B1/ko not_active Expired - Lifetime

- 2002-03-22 US US10/102,798 patent/US6646860B2/en not_active Expired - Lifetime

- 2002-03-22 TW TW091105610A patent/TW543053B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| TW543053B (en) | 2003-07-21 |

| JP2003133424A (ja) | 2003-05-09 |

| KR20030035765A (ko) | 2003-05-09 |

| US6646860B2 (en) | 2003-11-11 |

| US20030081371A1 (en) | 2003-05-01 |

| KR100777902B1 (ko) | 2007-11-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3977053B2 (ja) | 容量素子及びその製造方法 | |

| JP4947849B2 (ja) | 半導体装置およびその製造方法 | |

| JP4937489B2 (ja) | 受動素子を有する半導体デバイスおよびそれを作製する方法 | |

| US5949098A (en) | Semiconductor integrated circuit having an improved arrangement of power supply lines to reduce noise occurring therein | |

| JP4707330B2 (ja) | 半導体装置およびその製造方法 | |

| JP3746979B2 (ja) | 半導体装置及びその製造方法 | |

| US6417556B1 (en) | High K dielectric de-coupling capacitor embedded in backend interconnect | |

| CN1953170A (zh) | 半导体器件 | |

| JP2010140972A (ja) | 半導体装置 | |

| US20040043556A1 (en) | Capacitor formed in a multilayer wiring structure of a semiconductor device | |

| JP2004327619A (ja) | 半導体集積回路装置及びその製造方法 | |

| US6323099B1 (en) | High k interconnect de-coupling capacitor with damascene process | |

| JP2010225880A (ja) | 半導体装置及びその製造方法 | |

| WO2003061010A2 (en) | Integrated ground shield | |

| JP2001177056A (ja) | 半導体集積回路装置 | |

| JP2004119461A (ja) | 半導体装置及びその製造方法 | |

| JP2005072233A (ja) | 半導体装置 | |

| JPH07312415A (ja) | 半導体集積回路 | |

| US20050115740A1 (en) | Multilayered power supply line for semiconductor integrated circuit and layout method thereof | |

| JPS63108763A (ja) | 半導体集積回路 | |

| KR20030093115A (ko) | 반도체 집적 회로 장치 | |

| US6977805B2 (en) | Capacitor element, semiconductor integrated circuit and method of manufacturing those | |

| JPH04286150A (ja) | 半導体集積回路装置 | |

| KR101159112B1 (ko) | 가변 용량 캐패시터 및 그 제조방법 | |

| JP2544749B2 (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040601 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040601 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050131 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050509 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050927 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070320 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070619 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070620 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100629 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 3977053 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100629 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110629 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110629 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110629 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110629 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120629 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120629 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130629 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140629 Year of fee payment: 7 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |