JP3810246B2 - 半導体装置および半導体装置の製造方法 - Google Patents

半導体装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP3810246B2 JP3810246B2 JP2000071795A JP2000071795A JP3810246B2 JP 3810246 B2 JP3810246 B2 JP 3810246B2 JP 2000071795 A JP2000071795 A JP 2000071795A JP 2000071795 A JP2000071795 A JP 2000071795A JP 3810246 B2 JP3810246 B2 JP 3810246B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor region

- semiconductor

- terminal

- region

- electrically connected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 394

- 238000004519 manufacturing process Methods 0.000 title claims description 23

- 239000000758 substrate Substances 0.000 claims description 116

- 238000000034 method Methods 0.000 claims description 48

- 230000001681 protective effect Effects 0.000 claims description 37

- 238000002955 isolation Methods 0.000 claims description 29

- 239000012535 impurity Substances 0.000 claims description 13

- 230000008569 process Effects 0.000 claims description 13

- 239000004020 conductor Substances 0.000 claims description 11

- 230000005669 field effect Effects 0.000 claims description 11

- 239000010410 layer Substances 0.000 description 153

- 230000003071 parasitic effect Effects 0.000 description 85

- 230000015556 catabolic process Effects 0.000 description 34

- 239000011229 interlayer Substances 0.000 description 20

- 238000000926 separation method Methods 0.000 description 20

- 238000009792 diffusion process Methods 0.000 description 18

- 230000035945 sensitivity Effects 0.000 description 16

- 229910021332 silicide Inorganic materials 0.000 description 16

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 16

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 229910052698 phosphorus Inorganic materials 0.000 description 12

- 239000011574 phosphorus Substances 0.000 description 12

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 229920005591 polysilicon Polymers 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 229910052785 arsenic Inorganic materials 0.000 description 11

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 11

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 9

- 229910052796 boron Inorganic materials 0.000 description 9

- 238000010586 diagram Methods 0.000 description 9

- 230000003068 static effect Effects 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 230000005611 electricity Effects 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000013461 design Methods 0.000 description 7

- 229920002120 photoresistant polymer Polymers 0.000 description 6

- 239000002344 surface layer Substances 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 230000002542 deteriorative effect Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 230000001965 increasing effect Effects 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 230000006378 damage Effects 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- -1 tungsten nitride Chemical class 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000005865 ionizing radiation Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/74—Thyristor-type devices, e.g. having four-zone regenerative action

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0259—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using bipolar transistors as protective elements

- H01L27/0262—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using bipolar transistors as protective elements including a PNP transistor and a NPN transistor, wherein each of said transistors has its base coupled to the collector of the other transistor, e.g. silicon controlled rectifier [SCR] devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0255—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using diodes as protective elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

- H01L27/0251—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices

- H01L27/0266—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection for MOS devices using field effect transistors as protective elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置およびその製造技術に関し、特に、サイリスタ構造の保護回路を有する半導体装置およびその製造方法に適用して有効な技術に関するものである。

【0002】

【従来の技術】

半導体製造工程における微細加工技術の進歩により、半導体装置を構成する素子や配線等の微細化が進められており、これに伴って半導体装置の性能が益々向上している。しかし、一方で微細化された素子や配線等は、静電気等のような過電圧に極めて弱く、破壊しやすいという問題があり、半導体装置の信頼性を確保するためには、静電気等による劣化および破壊現象におけるメカニズムの解明とともに、保護構造の確立が強く要望されている。

【0003】

ところで、本発明者はサイリスタ構造の保護回路について調査した結果、例えば特開平8−306872号公報には、入力端子に接続された保護用MOS電界効果トランジスタのゲート端子とソース端子とが、寄生PNPNサイリスタのトリガ端子およびその寄生PNPNサイリスタにおけるNPNトランジスタのコレクタ・エミッタ間に接続された等価基板抵抗を介して接地電位に電気的に接続される構造が開示されている。この技術においては、上記コレクタ・エミッタ間の等価基板抵抗の電圧降下により上記NPNトランジスタのベース電位を上昇させて寄生PNPNサイリスタを駆動させる回路構造が開示されている。また、この公報には、絶縁基板上の半導体層に寄生PNPNサイリスタおよび保護用MOS電界効果トランジスタを設ける技術が開示されている。

【0004】

【発明が解決しようとする課題】

ところが、上記サイリスタ構造の保護回路技術においては、以下の課題があることを本発明者は見出した。

【0005】

すなわち、第1に、保護回路を構成するサイリスタのターンオン時間が遅延する課題がある。例えば上記公報の技術においては、入力端子にサージ電圧が印加された際、保護用MOS電界効果トランジスタのドレイン・ソース降伏により流れ始めた電流により上記等価基板抵抗の電圧降下が上記NPNトランジスタのベース・エミッタ電圧を上回って初めて寄生PNPNサイリスタが駆動するため、そのサイリスタのターンオン時間が遅延する。

【0006】

第2に、サイリスタ構造の保護回路のデバイス設計が難しいという課題がある。例えば上記公報の技術においては、上記等価基板抵抗が寄生PNPNサイリスタの感度特性に影響することから適切な値にする必要があるが、その等価基板抵抗は、その縦構造(寸法や不純物分布等)がプロセス毎に変動するので、上記感度特性が適切な値になるように形成することが難しい。

【0007】

第3に、内部回路の素子の微細化に対応することが難しいという課題がある。保護回路の降伏電圧は、内部回路の素子を保護することから内部回路のゲート絶縁耐圧よりも低いことが必要である。しかし、例えば上記公報の技術においては、入力端子電圧が保護用MOS電界効果トランジスタのドレイン・ソース降伏電圧と寄生バイポーラトランジスタのベース・エミッタ電圧との和を上回って初めて保護用MOS電界効果トランジスタのドレイン・ソース降伏電流が流れ始めるので、内部回路の素子の微細化につれて、保護回路の降伏電圧を、内部回路の素子のゲート絶縁膜の耐圧より低くすることが難しくなる。

【0008】

第4に、絶縁層上に素子形成用の半導体層を設ける、いわゆるSOI(Silicon On Insulator)基板を用いた場合、静電気等で生じた電流を逃がし難い構造となっていることから保護回路に高い放電能力が要求されるという課題がある。SOI基板を用いた場合、完全な素子分離が可能なので、配線−基板間の寄生容量や拡散容量等を低減でき、半導体装置の動作速度を向上させることが可能である。したがって、高周波信号回路を有する半導体装置には適している。しかし、完全な素子分離が可能な反面、静電気等によって生じた過電流も逃がし難く、素子破壊も生じ易い。このため、SOI基板を用いた半導体装置においては、保護回路に高い放電能力(感度)が要求されている。

【0009】

本発明の目的は、保護回路を構成するサイリスタのターンオン時間を短縮することのできる技術を提供することにある。

【0010】

また、本発明の目的は、サイリスタ構造の保護回路のデバイス設計を容易にすることのできる技術を提供することにある。

【0011】

また、本発明の目的は、内部回路の素子の微細化に対応した保護回路構成を実現することのできる技術を提供することにある。

【0012】

さらに、本発明の目的は、サイリスタ構造の保護回路の放電能力を向上させることのできる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0014】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

すなわち、本発明は、絶縁層上に設けられた半導体層において、前記半導体層の主面側から絶縁層に延びる分離部によって分離された同一の半導体層内に、保護用のサイリスタと、その駆動を誘発するトリガ素子とを設け、その保護用のサイリスタのゲートと、前記トリガ素子の基板電極部とを同一の半導体領域内に設けて、そのゲートと基板電極部とを電気的に接続し、前記トリガ素子の降伏により発生した基板電流により、前記保護用のサイリスタを駆動させるようにしたものである。

【0016】

また、本発明は、信号用の端子に過電圧が印加された際に接続方向が順方向となるように前記信号用の端子と基準電位用の端子との間に電気的に接続された保護用のダイオードを前記同一の半導体層内に設けたものである。

【0017】

また、本発明は、前記保護用のサイリスタおよびトリガ素子を形成する半導体領域の表層に高融点金属シリサイド層を設けたものである。

【0018】

また、本発明は、前記トリガ端子の基板電極部と、基準電位用の端子との間に抵抗を電気的に接続したものである。

【0019】

また、本発明は、前記保護用のサイリスタの第1のバイポーラトランジスタのベースと信号用の端子との間に抵抗を電気的に接続したものである。

【0020】

また、本発明は、前記トリガ素子と内部回路の素子とを同一工程時に形成するものである。

【0021】

また、本発明は、前記トリガ素子を、前記内部回路の素子に合わせて形成するものである。

【0022】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。

【0023】

また、本実施の形態においては、電界効果トランジスタ(MOS・FET(Metal Oxide Semiconductor Field Effect Transistor)をMOSと略し、pチャネル型のMOS・FETをpMOSと略し、nチャネル型のMOS・FETをnMOSと略す。

【0024】

(実施の形態1)

まず、本実施の形態を説明する前に、本発明者らが本発明をするのに検討した技術(以下、発明者検討技術という)について説明する。

【0025】

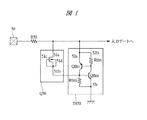

図1は、その回路図を示している。入力端子50は、入力保護抵抗R50を介して内部回路の入力ゲートと電気的に接続されている。この入力保護抵抗R50と入力ゲートとを結ぶ配線と接地端子との間には、保護用MOSQ50および寄生PNPNサイリスタQth50が電気的に接続されている。

【0026】

保護用MOSQ50は、ドレイン端子51a、ソース端子51b、ゲート端子51cおよび基板端子51dを有している。また、寄生PNPNサイリスタTH50は、寄生PNPバイポーラトランジスタQth51と、寄生NPNバイポーラトランジスタQth52と、等価nウエル抵抗Rth51と、等価p基板抵抗Rth52とで構成されている。符号52aは、寄生PNPバイポーラトランジスタQth51のエミッタ端子を示し、符号52bは、後述のn型ウエルに電位を供給するための電位供給端子を示し、符号52cは、寄生NPNバイポーラトランジスタQth52のエミッタ端子を示している。

【0027】

上記保護用MOSQ50のソース端子51b、ゲート端子51cおよび基板端子部51dは、互いに電気的に接続され、上記寄生PNPNサイリスタTH50のトリガ電極部に電気的に接続されている。すなわち、保護用MOSQ50のソース端子51b、ゲート端子51cおよび基板端子51dは、寄生NPNバイポーラトランジスタQth52および等価p基板抵抗Rth52と電気的に接続されている。

【0028】

図2は、図1の回路のデバイス構造断面図を示している。高濃度p型基板53の表面には、低濃度p型エピタキシャル層54が形成されている。この低濃度p型エピタキシャル層54には、p型ウエル55およびn型ウエル56が形成されている。

【0029】

一方のp型ウエル55には、上記保護用MOSQ50のドレイン端子51aおよびソース端子51bを構成するn+型拡散層、保護用MOSQ50の基板端子51dを構成するp+型拡散層および寄生NPNバイポーラトランジスタQth2のエミッタ端子52cを構成するn+型拡散層が形成されている。上記基板端子51dは、寄生NPNバイポーラトランジスタQth2のベース端子、すなわち、寄生PNPNサイリスタのトリガ電極部でもある。また、エミッタ端子52cは接地端子と電気的に接続されている。上記等価p基板抵抗Rth52は、実質的には基板端子51dとエミッタ端子52c間のp型ウエル55に寄生的に形成される拡散抵抗である。

【0030】

他方のn型ウエル56には、上記寄生PNPバイポーラトランジスタQth51のエミッタ端子52aを構成するp+型拡散層およびn型ウエル56に所定の電位を供給するための電位供給部52bを構成するn+型拡散層が形成されている。上記等価nウエル抵抗Rth51は、実質的にはn型ウエル56に寄生的に形成される拡散抵抗である。

【0031】

この発明者検討技術においては、基本的に、入力端子50に正のサージ電圧が印加されると、保護用MOSQ50のドレイン・ソース降伏によりそのドレイン端子51aおよびソース端子51b間にパンチスルー電流が流れ、この電流が寄生PNPNサイリスタTH50のトリガ電流となる。しかし、実質的には、そのトリガ電流の他に、上記パンチスルー電流が等価p基板抵抗Rth52(p型ウエル55の拡散抵抗)を通じて接地端子に流れることにより、等価p基板抵抗Rth52の電圧降下によって寄生NPNバイポーラトランジスタQth52のベース電位が上昇し、寄生NPNバイポーラトランジスタQth52が駆動する要素を有している。すなわち、この技術では、寄生PNPNサイリスタTH50が駆動する電圧(保護素子のフォワードブロッキング(forward blocking)電圧(以下、単にブロック電圧という))が、保護用MOSQ50の降伏電圧と、等価p基板抵抗Rth52の電圧降下による寄生NPNバイポーラトランジスタQth52のベース電圧との和になる。

【0032】

しかし、上記本発明者検討技術においては、例えば以下の課題がある。第1に、寄生PNPNサイリスタTH50のターンオン時間が遅延する、という課題がある。これは、入力端子50にサージ電圧が印加された際、保護用MOSQ50のドレイン・ソース降伏により流れ始めた電流により上記等価p基板抵抗Rth52の電圧降下が上記寄生NPNバイポーラトランジスタQth52のベース・エミッタ電圧を上回って初めて寄生PNPNサイリスタTH50が駆動するためである。

【0033】

第2に、保護回路のデバイス設計が難しいという課題がある。上記等価p基板抵抗Rth52は、寄生PNPNサイリスタTH50の感度特性に影響することから、その感度特性が適切な値になるように形成する必要がある。しかし、その等価p基板抵抗Rth52が形成されるp型ウエル55は、その縦構造(寸法や不純物分布等)がプロセス毎に変動してしまうので、寄生PNPNサイリスタTH50の感度特性が適切な値になるように等価p基板抵抗Rth52を形成することは難しい。

【0034】

第3に、内部回路の素子の微細化に対応することが難しいという課題がある。保護回路の降伏電圧は、内部回路の素子を保護することから内部回路のゲート絶縁耐圧よりも低いことが必要である。しかし、上記発明者検討技術においては、入力端子50に印加されるサージ電圧が保護用MOS電界効果トランジスタのドレイン・ソース降伏電圧と寄生NPNバイポーラトランジスタQth52のベース電圧との和以上となって初めて保護MOSQ50のドレイン・ソース降伏電流が流れ始めるので、内部回路の素子の微細化につれて、保護回路の降伏電圧を、内部回路の素子のゲート絶縁膜の耐圧より低くすることが難しくなる。

【0035】

第4に、絶縁層上に素子形成用の半導体層を設ける、いわゆるSOI(Silicon On Insulator)基板を用いた場合、静電気等で生じた電流を逃がし難い構造となっていることから保護回路に高い放電能力が要求されるという課題がある。SOI基板を用いた場合、完全な素子分離が可能なので、配線−基板間の寄生容量や拡散容量等を低減でき、半導体装置の動作速度を向上させることが可能であり、高周波信号回路を有する半導体装置に適している。しかし、完全な素子分離が可能な反面、静電気等によって生じた電流も逃がし難く、素子破壊も生じ易いという問題があるため、SOI基板を用いた半導体装置においては、保護回路に高い放電能力が要求されている。

【0036】

次に、本実施の形態1の半導体装置について説明する。本実施の形態1の半導体装置は、半導体基板として上記SOI基板が用いられている。半導体装置の内部回路を静電気等による過電圧または過電流から保護するための保護回路の主要部は、サイリスタと、それを駆動するトリガ素子とを有するサイリスタ保護素子によって構成されている。そして、そのサイリスタとトリガ素子とが、完全な分離部に囲まれた同一の半導体層部分に形成されている。

【0037】

まず、本実施の形態1の半導体装置における保護回路の一例を図3〜図5によって説明する。なお、図3中における破線は、上記完全な分離部を模式的に示しており、上記保護回路に関しては、その破線に囲まれた素子が同一の半導体層部分に設けられていることを模式的に示している。また、図4(a)の矢印は負の過電流の放電経路を示し、(b)の矢印は正の過電流の放電経路を示している。

【0038】

図3に示すように、外部端子1は、内部回路2の電極を引き出すための端子であり、一般的には、ボンディングパッドとも呼ばれ、平面的には半導体チップの主面の外周近傍や主面中央等に配置され、断面的には最上の配線層に形成されている。この外部端子1は、信号用の端子を示しており、内部回路2内の周辺回路部を介して主回路部と電気的に接続されている。この周辺回路部は、例えば入力回路、出力回路または入出力双方向回路等のように、半導体装置の内部と外部との電気的レベルの整合やタイミングの調整を行うインターフェイス回路部である。主回路部は、半導体装置の機能を決める主要な回路部である。本実施の形態1においては、その主回路部に、例えばLNA(Low Noise Amplifier)やMIXER等のような高周波信号回路が形成されている。なお、本実施の形態1において、高周波信号とは、例えば1GHz以上の信号を言う。

【0039】

このような内部回路2は、相対的に高電位側の電源端子VCCと、相対的に低電位側の電源端子VSSとの間に電気的に接続されている。高電位側の電源端子VCCは、半導体装置を駆動させるべく相対的に高い電圧を供給するための端子であり、具体的には、例えば1.8V〜3.3V程度に設定される。低電位側の電源端子VSSは、半導体装置の基準電位を供給する端子であり、一般的には、接地端子、GND端子とも呼ばれ、具体的には、例えば0Vまたは他の電位に設定される。なお、これら低電位側の電源端子VSSや高電位側の電源端子VCCへの電位供給は、外部端子1から直接的に供給される場合もあるが、それ以外に内部回路2内の内部電源から供給される場合もある。

【0040】

この外部端子1と内部回路2とを結ぶ配線と、低電位側の電源端子VSSとの間に、本実施の形態1の保護回路3が電気的に接続されている。保護回路3は、半導体装置の内部回路2を静電気等による過電圧や過電流から保護する回路であり、例えばダイオードD1、寄生PNPNサイリスタTH、トリガ素子TRおよびクランプ素子CLを有している。このうち、ダイオードD1、寄生PNPNサイリスタTH1およびトリガ素子TRは、完全な分離部に囲まれた同一の半導体層部分に形成されている。

【0041】

ダイオードD1は、外部端子1に負の電圧が印加された際に動作して電荷を逃がすための保護素子であり、外部端子1に負の過電圧が印加された場合に接続方向が順方向となるように外部端子1と低電位側の電源端子VSSとの間に電気的に接続されている。このようなダイオードD1を設けたことにより、図4(a)に示すように、低電位側の電源端子VSSの電位よりも負の過電圧が外部端子1に印加された場合、過電流を低電位側の電源端子VSSからダイオードD1を通じて外部端子1に逃がすことができるので、負の過電圧に対する静電気破壊耐性を向上させることが可能となっている。ここでは、ダイオードD1が、例えばpn接合ダイオードで形成されているが、これに限定されるものではなく、例えばダイオード接続されたMOSで形成しても良い。このpn接合ダイオードやダイオード接続されたMOSにおいては、小さな面積で形成できるので、レイアウト面積の大幅な増大を招くことなく、保護回路3を形成することが可能となる。

【0042】

一方、サイリスタ保護素子は、外部端子1に正の電圧が印加された際に動作して電荷を逃がすための保護素子であり、寄生PNPNサイリスタTHおよびトリガ素子TRを有している。この寄生PNPNサイリスタTHは、第1,第2のバイポーラトランジスタQth1,Qth2と、抵抗Rth1とを有している。第1のバイポーラトランジスタQth1はPNP型のバイポーラトランジスタからなり、第2のバイポーラトランジスタQth2はNPN型のバイポーラトランジスタからなる。

【0043】

第1のバイポーラトランジスタQth1のエミッタは外部端子1と電気的に接続されている。また、第1のバイポーラトランジスタQth1のベースは、抵抗Rth1を介してそのエミッタおよび外部端子1と電気的に接続されている他、第2のバイポーラトランジスタQth2のコレクタとも電気的に接続されている。さらに、第1のバイポーラトランジスタQth1のコレクタは、第2のバイポーラトランジスタQth2のベースと電気的に接続されている。この第2のバイポーラトランジスタQth2のベースは、寄生PNPNサイリスタTHのゲート、すなわち、トリガ電極部となっている。この第2のバイポーラトランジスタQth2のエミッタは低電位側の電源端子VSSと電気的に接続されている。

【0044】

本実施の形態1においては、寄生PNPNサイリスタTHのトリガ電極部となる第2のバイポーラトランジスタQth2のベースに、上記トリガ素子TRの基板電極(バックゲート)が電気的に接続されている。このトリガ素子TRは、寄生PNPNサイリスタTHを駆動させるきっかけを与える素子であり、例えばダイオード接続されたnMOSによって形成されている。トリガ素子TRのドレインは、外部端子1と電気的に接続され、そのソースは、ゲート電極および低電位側の電源端子VSSと電気的に接続されている。ただし、トリガ素子TRは、nMOSに限定されるものではなく種々変更可能であり、例えばバイポーラトランジスタで形成することもできる。その場合、トリガ素子用のバイポーラトランジスタのベースを第2のバイポーラトランジスタQth2のベースに電気的に接続する。そして、トリガ素子用のバイポーラトランジスタのコレクタを外部端子1と電気的に接続し、エミッタを低電位の電源端子VSSと電気的に接続する。

【0045】

このようなサイリスタ保護素子を設けたことにより、図4(b)に示すように、外部端子1に正の過電圧が印加され、トリガ素子TRのソース・ドレイン間が降伏すると、それにより発生した基板電流によって寄生PNPNサイリスタTHがターンオンする。これにより、過電流を外部端子1から寄生PNPNサイリスタTHおよびトリガ素子TRを通じて低電位側の電源端子VSSに逃がすことができるので、正の過電圧に対する静電気破壊耐性を向上させることが可能となっている。

【0046】

特に、本実施の形態1においては、寄生PNPNサイリスタTHのトリガ素子(第2のバイポーラトランジスタQth2のベース)に、トリガ素子TRの基板電極を電気的に接続した(後述するように第2のバイポーラトランジスタQth2のベースとトリガ素子TRの基板電極とが、同一半導体領域に一体的に形成されている)ことにより、寄生PNPNサイリスタTHを高速にターンオンさせることができる。これは、外部端子1に正の過電圧が印加されると、トリガ素子TRのソース・ドレイン間の降伏により発生した基板電流が寄生PNPNサイリスタTHのトリガ電流として働くが、その際、その基板電流は、寄生PNPNサイリスタTHのトリガ電極(第2のバイポーラトランジスタQth2のベース)に注入される以外に流路がないために、寄生PNPNサイリスタTHのトリガ電極部に効率良く注入されるようになるからである。したがって、本実施の形態1においては、正の過電圧に対しても高感度で良好な静電破壊耐性を示す保護回路3を設けることが可能となる。また、トリガ電流の利用効率を高くできるので、トリガ素子TR自体のサイズ(占有面積)を小さくすることが可能となる。このため、半導体チップのサイズを縮小することができる。したがって、半導体装置の歩留まりを向上させることができ、製造コストを低減することも可能となる。また、保護回路3(特に寄生PNPNサイリスタTHとトリガ素子TR)のサイズを小さくできるので、寄生容量を小さくすることが可能となる。したがって、高周波信号回路を有する半導体装置において、電気特性を低下させずに、静電破壊耐性を向上させることが可能となる。

【0047】

ここで、図5は、寄生PNPNサイリスタTHの保持電圧を示す典型的な電流IA−電圧VA特性を示している。Vhは寄生PNPNサイリスタTHの保持(hold)電圧、Vbfは保護素子(寄生PNPNサイリスタTH)の上記ブロック電圧(寄生PNPNサイリスタTHの動作開始電圧)を示している。

【0048】

本実施の形態1においては、外部端子1に過電圧が印加され、その外部端子1の電圧が、トリガ素子TR(nMOSで例示)のソース・ドレイン降伏電圧BVDSに達した際に発生した基板電流が寄生PNPNサイリスタTHのゲート(トリガ電極部)に注入される。このため、サイリスタ保護素子のブロック電圧Vbfは、上記ソース・ドレイン降伏電圧BVDSと等しくなる。したがって、本実施の形態1の場合は、そのブロック電圧Vbfを、上記発明者検討技術(Vbf=BVDS+VBE)よりもベース・エミッタ電圧VBE(例えば約0.8V)分だけ小さくできる。このため、ブロック電圧Vbfを、内部回路2を構成するMOSのゲート絶縁耐圧に対して、より小さく設定できるので、より優れた静電破壊耐性を得ることが可能となる。内部回路2を構成するMOSのゲート絶縁膜は性能向上要求等に伴い薄膜化が進められている。したがって、ゲート絶縁耐圧も低くくなることから上記ブロック電圧もそれに伴い低くせざるを得ない。本実施の形態1においては、そのブロック電圧Vbfを小さくできるので、そのような内部回路2のMOSの微細化(ゲート絶縁膜の薄膜化)にも対応できる。逆に、保護回路側から内部回路の素子に対しての制約を緩和できるので、内部回路2の素子の微細化を推進することが可能となる。したがって、半導体装置の動作速度を向上させることが可能となる。

【0049】

上記図3に示したクランプ素子CLは、例えば上記内部回路3の高電位側の電源端子VCCと低電位側の電源端子VSSとの間にダイオード接続されたnMOSによって形成されている。このようなクランプ素子CLを設けたことにより、内部回路3の電源端子VCC,VSS間に過電圧が印加された場合の放電経路を形成することができるので、静電破壊耐性を向上させることが可能となる。

【0050】

このような保護回路3は、例えば半導体装置の全ての入力回路または出力回路に対して設けても良いし、特定の入力回路または出力回路に対して設けても良い。また、入力回路および出力回路の両方の周辺回路に対して保護回路3を設けても良い。保護回路3を入力回路に対して設けた場合の一例を図6および図7に示す。なお、図6および図7の破線は図3と同じことを意味している。また、ここでは一般的な半導体回路の入力回路を示している。

【0051】

図6(a),(b)は、いずれも入力回路がCMOS(Complementary MOS)インバータ回路INVで構成されている場合を例示している。CMOSインバータ回路INVは、pMOSQ1aとnMOSQ1bとが電源端子VCC,VSS間に直列に接続されて構成されている。CMOSインバータ回路INVの出力は、半導体装置の上記主回路部と電気的に接続され、入力は、入力保護抵抗R1を介して上記外部端子1と電気的に接続されている。図6(a)では、その入力保護抵抗R1とCMOSインバータ回路INVの入力との間に保護用のダイオードD2,D3が電気的に接続されている。また、図6(b)では、その入力保護抵抗R1とCMOSインバータ回路INVの入力との間に、ダイオードD2,D3に代えて、ダイオード接続された保護用のpMOSQ2aおよびnMOSQ2bが電気的に接続されている。

【0052】

入力保護抵抗R1は、CMOSインバータ回路INVに過電流が流れるのを抑制または防止し、かつ、外部端子1側からみたインピーダンスを大きくすることで、CMOSインバータ回路INVの入力側配線等に帯電した電荷をダイオードD2,D3および電源配線を通じて外部端子側に逃がし易くするための機能を有している。

【0053】

また、図6(a)に示す保護用のダイオードD2,D3は、CMOSインバータ回路INVの入力のゲート電極と電源端子VCCとの間およびその入力のゲート電極と電源端子VSSとの間に、それぞれ逆方向接続になるように電気的に接続されている。この保護用のダイオードD2,D3は、例えばCD(Charged Device)法による静電破壊試験等において、外部端子1を接地させて半導体装置内部に帯電させた電荷を放電させる際に、CMOSインバータ回路INVの入力配線(入力側の金属配線、ゲート電極を含む)の電位と、CMOSインバータ回路INVのMOSQ1a,Q1bが配置された半導体基板側のウエルまたはそのMOSQ1a,Q1bのソース・ドレイン用の半導体領域(拡散層)の電位との間に差が生じるのを防ぐ機能を有している。

【0054】

すなわち、本実施の形態1においては、CMOSインバータ回路INVの入力段に入力保護抵抗R1およびダイオードD2,D3を接続することにより、外部端子1を接地した場合、CMOSインバータ回路INVの出力配線側に帯電した電荷を、ダイオードD2,D3を通じて外部入力配線側に素早く放電させることが可能となっている。これにより、CMOSインバータ回路INVの入力配線側の電荷と出力側の電荷との放電時間の差を縮めることができるので、その放電時間差に起因して、CMOSインバータ回路INVのMOSQ1a,Q1bのゲート絶縁膜に瞬間的に高電圧が印加されるのを防止することができる。このため、ゲート絶縁破壊を防止でき、半導体装置の歩留りおよび信頼性を向上させることが可能となっている。なお、このダイオードD2,D3は、後述するように半導体基板におい上記した保護回路3のダイオードD1とは異なるウエル内に配置されている。

【0055】

図6(b)の保護用のpMOSQ2aおよびnMOSQ2bもダイオードD2,D3と同じように機能する。保護用のpMOSQ2aおよびnMOSQ2bは、CMOSインバータ回路INVの入力のゲート電極と電源端子VCCとの間およびその入力のゲート電極と電源端子VSSとの間に、それぞれ逆方向接続になるようにダイオード接続されている。この場合、MOSの方が、ダイオードよりもブレイクダウン電圧を約1V程度低くできるので、上記した電荷の放電動作が行われ易い構造となる。したがって、上記した電荷の放電を素早く行うことが可能となる。また、ダイオードD2,D3に代えて、バイポーラトランジスタをダイオード接続しても良い。この場合、バイポーラトランジスタの方が、ダイオードよりも駆動能力が高いことから上記した電荷の放電を素早く行うことが可能となる。

【0056】

ここでは、上記保護回路3の低電位側の電源端子VSSと、図6(a),(b)で示した入力保護抵抗R1、ダイオードD2,D3、pMOSQ2a、nMOSQ2bおよびCMOSインバータ回路INVの低電位側の電源端子VSSとを共通にしているが、別々にしても良い。その場合、電源端子VSSの電位は等しくても良いし、異なっていても良い。このように電源端子VSSを別々に分離することにより、一方の回路側で生じた電位変動に起因して他方の回路の電源の電位が変動するのを防止することが可能となる。

【0057】

一方、図7(a),(b)は入力回路にバイポーラトランジスタを用いている場合が例示されている。図7(a)では、外部端子1は、入力保護抵抗R1を介してバイポーラトランジスタQ3のベースと電気的に接続されている。このバイポーラトランジスタQ3の出力(コレクタ)は、内部回路2の主回路部と電気的に接続されている。

【0058】

また、図7(b)では、入力回路にBiCMOS(Bipolar CMOS)回路が形成されている場合が例示されている。BiCMOS回路は、バイポーラトランジスタの持つ負荷駆動能力と、CMOSの低電力性との両方の長所を組み合わせた回路であり、例えばCMOSインバータ回路INVを構成するpMOSQ1aおよびnMOSQ1bと、nMOSQ4と、電源端子VCC,VSS間に直列に接続された2個のバイポーラトランジスタQ5a,Q5bを有している。ここでは、外部端子1は、入力保護抵抗R1を介してCMOSインバータ回路INVおよびnMOSQ4の入力と電気的に接続されている。このCMOSインバータ回路INVの出力はバイポーラトランジスタQ5aのベースと電気的に接続されている。また、nMOSQ4のドレインは、バイポーラトランジスタQ5aのエミッタとバイポーラトランジスタQ5bのコレクタとの接続部に電気的に接続され、ソースは、バイポーラトランジスタQ5bのベースと電気的に接続されている。このようなBiCMOS回路の出力は内部回路2の主回路と電気的に接続されている。

【0059】

ところで、この図6および図7においては、一般的な半導体回路の入力回路を示し、入力回路の入力端子の前段に入力保護抵抗R1等を設けた場合を例示したが、内部回路2が高周波信号回路の場合には、入力保護抵抗R1を取り付けない方が良好な高周波特性を得る上で好ましい。本実施の形態1においては、保護回路3によって正負の過電圧による過電流を速やかに除去できるので、高周波信号回路等のように入力保護抵抗R1等を取り付けられないようなデバイスであっても、充分に内部回路2内の素子を保護することが可能である。

【0060】

次に、本実施の形態1の半導体装置における保護回路3のデバイス構造を図8および図9により説明する。なお、図8は、上記保護回路3のダイオードD1、寄生PNPNサイリスタTHおよびトリガ素子TR1部分の模式的な平面図を示し、図9は図8のA−A線の模式的な断面図を示している。

【0061】

半導体基板としては、上記したようにSOI基板4が用いられている。SOI基板4を用いることにより、半導体装置の動作速度の向上、消費電力の低下および高周波特性の向上を実現することが可能となる。SOI基板4は、支持基板4A上に、埋込絶縁層4Bを介して半導体層4Cが形成されてなる。支持基板4Aは、例えばp型のシリコン単結晶からなり、主としてSOI基板4の機械的強度を確保する機能を有している。埋込絶縁層4Bは、例えば酸化シリコン(SiO2)膜からなり、その厚さは、例えば0.5μm程度である。半導体層4Cは、素子が形成される層であり、例えばp型のシリコン単結晶を主体として形成され、その厚さは、例えば1〜3μm程度である。ここでは、半導体層4Cが、半導体基板層4Cs上にエピタキシャル層4Cepが形成されてなる場合が例示されている。エピタキシャル層4Cepを設けることにより、例えばMOSのゲート絶縁膜の膜質を向上させることができ、薄膜化させることができる上、バイポーラトランジスタのエミッタ−コレクタ(埋込コレクタ層)間の距離の設定を良好にすることが可能となる。

【0062】

この半導体層4Cには、nウエル(第1の半導体領域)5N1およびpウエル(第2の半導体領域)5P1が形成されている。nウエル5N1は、例えばリンまたはヒ素が導入されてなり、特に限定されないが、その不純物濃度は、例えば1016/cm3程度である。また、これに隣接するpウエル5P1は、例えばホウ素が導入されてなり、特に限定されないが、その不純物濃度は、例えば5×1015/cm3程度である。なお、図9においては、図面を見易くするため、nウエル5N1およびpウエル5P1にはハッチングを付していない。

【0063】

また、半導体層4Cの主面には、例えば酸化シリコンからなる分離部6Aが形成されている。この分離部6Aは、例えばLOCOS(Local Oxidization of Silicon)法等によって形成されており、その底部は、埋込絶縁層4Bまで達していない。この分離部6Aによって素子形成用の活性領域L1〜L3が規定されている。なお、この分離部6Aは、LOCOS法によって形成されるものに限定されるものではなく、例えば半導体層4Cに溝を掘り、その内部に絶縁膜等を埋め込むことで形成した、いわゆる溝型の分離部(トレンチアイソレーション)としても良い。

【0064】

さらに、本実施の形態1においては、その分離部6Aの上面から半導体層4Cを介して埋込絶縁層4Bに達する溝が掘られ、その溝内に、例えば酸化シリコン等からなる絶縁膜が埋め込まれることにより完全な分離部6Bが形成されている。すなわち、その分離部6Bと埋込絶縁層4Bとによって囲まれた半導体層4Cは、他の半導体層4Cと完全に絶縁分離されている。ここでは、その分離部6Bが図8に示すように平面枠状に形成されており、その枠内の半導体層4C部分に上記保護回路3のダイオードD1、寄生PNPNサイリスタTHおよびトリガ素子TRが形成されている。すなわち、ダイオードD1、寄生PNPNサイリスタTH、トリガ素子TR、nウエル5N1およびpウエル5P1は、完全な分離部6Bおよび埋込絶縁層4Bに取り囲まれた同一の半導体層4C内に形成されている。なお、ダイオードD1、寄生PNPNサイリスタTH、トリガ素子TRで構成される保護素子のサイズは、特に限定されないが、例えば50×50μm程度である。

【0065】

また、内部回路2の領域においても各部において完全な分離が行われている。これにより、半導体層4Cにα線等のような電離性放射線が照射されても収集される電荷量が少ないため、ソフトエラー耐性を向上させることが可能となる。また、CMOS構造においてラッチアップ現象を防止することができるので、pMOSおよびnMOSの隣接間隔を最小分離幅にできる。したがって、CMOS回路を有する半導体装置の高集積化を実現することが可能となる。なお、完全な分離部6Bとは、隣接する素子間の電気的分離が設計上許容される範囲で分離されているものも含む。

【0066】

上記ダイオードD1は、例えばpn接合ダイオードからなり、nウエル5N1と、その上部に形成されたp+型半導体領域(第8の半導体領域)7P1およびn+型半導体領域(第3の半導体領域)8N1とを主要部として有している。このp+型半導体領域7P1は、例えばp型不純物のホウ素が含有されてなり、n+型半導体領域8N1は、例えばn型不純物のリンまたはAsが含有されてなる。これらp+型半導体領域7P1と、n+型半導体領域8N1とは、同一のnウエル5N1内に設けられている。これにより、それらの間の抵抗値を低くすることが可能となっている。また、p+型半導体領域7P1と、n+型半導体領域8N1とは、平面的にその互いの長辺同士が平行になるように配置されている。これにより、p+型半導体領域7P1と、n+型半導体領域8N1との間に流れる電流の経路幅を広く確保することができるので、それらの間の抵抗値を低くすることが可能となっている。これらの構成により、上記負の過電圧による過電流の放電経路の抵抗を下げることができるので、その過電流を速やかに逃がすことが可能となっている。

【0067】

なお、このp+型半導体領域7P1は、SOI基板4上の層間絶縁膜9aに穿孔されたコンタクトホール10aを通じて第1層配線11a1と電気的に接続され、さらに低電位側の電源端子VSSと電気的に接続されている。また、n+型半導体領域8N1は、層間絶縁膜9aに穿孔されたコンタクトホール10bを通じて第1層配線11b1に接続され、さらに外部端子1と電気的に接続されている。

【0068】

また、上記寄生PNPNサイリスタTHを構成するバイポーラトランジスタQth1は、p+型半導体領域(第4の半導体領域)7P2と、nウエル5N1と、n+型半導体領域(第5の半導体領域)8N2と、pウエル5P1とを主要部として有している。p+型半導体領域7P2は、例えばホウ素が含有されてなり、nウエル5N1の領域内において上記したn+型半導体領域8N1に隣接して平行に延びて形成されている。また、n+型半導体領域8N2は、例えばリンまたはヒ素が含有されてなり、nウエル5N1とpウエル5P1との両方にまたがるように、上記したp+型半導体領域7P2に隣接して平行に延びて形成されている。なお、p+型半導体領域7P2は、層間絶縁膜9aに穿孔されたコンタクトホール10cを通じて第1層配線11b2に接続され、さらに外部端子1と電気的に接続されている。また、寄生PNPNサイリスタTHを構成する抵抗Rth1は、nウエル5N1の抵抗と等価である。

【0069】

また、寄生PNPNサイリスタTHを構成するバイポーラトランジスタQth2は、n+型半導体領域8N2と、nウエル(第1半導体領域)5N1と、pウエル(第2半導体領域)5P1と、n+型半導体領域(第5半導体領域)8N4とを主要部として有している。

n+型半導体領域(第4半導体領域)8N3は、例えばリンまたはヒ素が含有されてなり、上記分離部6Aを隔ててn+型半導体領域8N2の隣に配置されている。このn+型半導体領域8N3も、n+型半導体領域8N2に平行に延びて形成されている。ここでは、pウエル5P1部分がバイポーラトランジスタQth2のベース(すなわち、寄生PNPNサイリスタTHのトリガ電極部)となる。なお、n+型半導体領域8N3は、層間絶縁膜9aに穿孔されたコンタクトホール10dを通じて第1層配線11b3に接続され、さらに外部端子1と電気的に接続されている。

【0070】

また、上記トリガ素子TRは、活性領域L3内のpウエル5P1に形成された一対のn+型半導体領域8N3およびn+型半導体領域(第7の半導体領域)8N4と、ゲート絶縁膜12aと、ゲート電極13aとを有している。一対のn+型半導体領域8N3,8N4は、トリガ素子TRのソース・ドレインを形成する領域であり、例えばリンまたはヒ素が含有されてなる。このソース・ドレイン用の一対のn+型半導体領域8N3,8N4の間にチャネル領域が形成される。このチャネル領域が、トリガ素子TRの基板電極として機能する。

【0071】

本実施の形態1においては、そのトリガ素子TRの基板電極と、寄生PNPNサイリスタTHのバイポーラトランジスタQth2のベース(寄生PNPNサイリスタTHのトリガ電極部)とが同一のpウエル5P1に形成されている。これにより、それらの間の抵抗値を低くすることができ、トリガ素子TRで生じた基板電流を効率良くバイポーラトランジスタQth2のベースに注入することが可能となっている。また、トリガ素子TRのチャネル幅方向(ゲート電極13aの平面的な延在方向)を、バイポーラトランジスタQth2のベースに相当する部分に対して平行になるように配置したことにより、上記基板電流の経路幅を広く確保することができるので、それらの間の抵抗値を低くすることが可能となっている。これらにより、寄生PNPNサイリスタTHのターンオン時間を短縮でき、その感度を向上させることができる。したがって、上記正の過電圧による過電流を速やかに逃がすことが可能となっている。

【0072】

また、サイリスタ保護素子の感度劣化が保護素子を形成する半導体領域の寸法変動の影響を受け難い構造とすることができる。したがって、保護回路のデバイス設計を容易にすることが可能となる。

【0073】

さらに、トリガ素子TRのチャネル長が、内部回路2のMOSのチャネル長とほぼ同一にされている。これにより、サイリスタ保護素子の感度が、内部回路2の素子(MOS)に応じて最適な値に設定されている。すなわち、内部回路2の素子の微細化に応じて、サイリスタ保護素子の感度の設定が可能となっている。

【0074】

上記トリガ素子TRのゲート絶縁膜12aは、例えば酸化シリコンからなる。また、ゲート電極13aは、例えば低抵抗ポリシリコンからなるが、これに限定されるものではなく種々変更可能であり、例えば低抵抗ポリシリコン上に、例えばコバルトシリサイドやタングステンシリサイド等のような高融点金属シリサイド層を設けた、いわゆるポリサイドゲート電極構造としても良い。また、低抵抗ポリシリコン上に、例えば窒化タングステン等のようなバリアを介してタングステン等のような金属膜を設けた、いわゆるポリメタルゲート電極構造としても良い。このゲート電極13aは、層間絶縁膜9aに形成されたコンタクトホール10fを通じて第1層配線と電気的に接続され、さらに低電位側の電源端子VSSと電気的に接続されている。また、n+型半導体領域8N4は、層間絶縁膜9aに穿孔されたコンタクトホール10eを通じて第1層配線11a2に接続され、さらに低電位側の電源端子VSSと電気的に接続されている。

【0075】

なお、上記層間絶縁膜9aは、例えば酸化シリコンからなる。また、上記コンタクトホール10a〜10eは、それぞれが配置された各半導体領域の延在方向に沿って延びて形成されている。これにより配線と各半導体領域との接触抵抗を低減させることが可能となっている。また、上記第1層配線11a1,11a2,11b1〜11b3は、例えばアルミニウムまたはアルミニウム−シリコン−銅合金等のような金属膜からなる。

【0076】

このように、本実施の形態1の半導体装置によれば、上記のような保護回路3を設けたことにより、SOI基板4を用いた場合においても、正、負両方の過電圧に対する過電流を速やかに逃がすことができる。このため、SOI基板4に形成された半導体装置の歩留まりを向上させることが可能となる。したがって、その半導体装置のコストを低減することが可能となる。

【0077】

また、サイリスタ保護素子内の各素子の電極を同一半導体領域に設けることにより、サイリスタ保護素子のサイズの微細化を図ることができ、また、各電極間の抵抗を下げることができるので、内部回路2に高周波信号回路が設けられるような半導体装置であっても、その電気的特性(周波数特性)の劣化を生じさることなく半導体装置内の回路、特に入力に組み込むことができ、静電破壊耐性を向上させることが可能となる。

【0078】

次に、上記のようなサイリスタ構造の保護回路3を有する半導体装置の具体例を図10〜図12に示す。図10はその半導体装置の要部平面図、図11は図10のA−A線の断面図、図12は図10の半導体装置の他の部分の断面図である。

【0079】

半導体層4Cには、上記ダイオードD1、寄生PNPNサイリスタTH、トリガ素子TRの他に、クランプ素子CL、バイポーラトランジスタQ3、pMOSQ1aおよびnMOSQ1bが形成されている。クランプ素子CL、バイポーラトランジスタQ3、pMOSQ1aおよびnMOSQ1bは、それぞれ分離部6Bによって囲まれた半導体層4C部分に互いに電気的に分離された状態で形成されている。

【0080】

図10および図11に示すように、クランプ素子CLは、分離部6Bおよび埋込絶縁層4Bに取り囲まれた半導体層4Cに形成されている。この半導体層4Cには、pウエル5P2が形成されている。このpウエル5P2の上部には、クランプ素子CLのソース・ドレインを形成する一対のn+型半導体領域8N5,8N6およびウエル電位供給部を形成するp+型半導体領域7P3が形成されている。この一対のn+型半導体領域8N5,8N6には、例えばリンまたはヒ素が含有され、ウエル電位供給部を形成するp+型半導体領域7P3には、例えばホウ素が含有されている。

【0081】

n+型半導体領域8N5およびp+型半導体領域7P3は、層間絶縁膜9aに穿孔されたコンタクトホール10f,10gを通じて第1層配線11a3と電気的に接続されている。他方のn+型半導体領域8N6は、層間絶縁膜9aに穿孔されたコンタクトホール10hを通じて第1層配線11c1と電気的に接続されている。なお、n+型半導体領域8N5およびp+型半導体領域7P3の間は、分離部6Aによって分離されている。

【0082】

クランプ素子CLのゲート絶縁膜12bおよびゲート電極13bは、上記トリガ素子TRのゲート絶縁膜12aおよびがゲート電極13aと同じ構造となっている。異なるのは、ゲート電極13bは、層間絶縁膜9bに穿孔されたコンタクトホール10iを通じて第1層配線11a3と電気的に接続されていることである。

【0083】

バイポーラトランジスタQ3は、分離部6Bおよび埋込絶縁層4Bに取り囲まれた半導体層4Cに形成されている。この半導体層4Cには、埋込n+型ウエル14、n+型半導体領域15、n型半導体領域16、p型半導体領域17およびn+型半導体領域18が形成されている。このバイポーラトランジスタQ3は、例えば縦型のNPNバイポーラトランジスタからなり、そのコレクタは、埋込n+型ウエル14、n+型半導体領域15およびn型半導体領域16を有している。

【0084】

埋込n+型ウエル14は、上記埋込コレクタ層に相当する層であり、コレクタ抵抗を下げる機能を有している。埋込n+型ウエル14には、例えばアンチモン(Sb)が含有されており、n+型半導体領域15およびn型半導体領域16が電気的に接続されている。n+型半導体領域15は、例えばリンまたはヒ素が含有されてなり、コレクタ引出領域を形成し、層間絶縁膜9aに穿孔されたコンタクトホール10jを通じて第1層配線11dと電気的に接続されている。このn型半導体領域16は、例えばリンまたはヒ素が含有されてなり、その上部には、バイポーラトランジスタQ3のベース用のp型半導体領域17が形成されている。

【0085】

このベース用のp型半導体領域17は、例えばホウ素が含有されてなり、層間絶縁膜9aに穿孔されたコンタクトホール10kを通じて第1層配線11b4と電気的に接続されている。このp型半導体領域17の上部には、バイポーラトランジスタQ3のエミッタ用のn+型半導体領域18が形成されている。このエミッタ用のn+型半導体領域18は、例えばリンまたはヒ素が含有されてなり、層間絶縁膜9aに穿孔されたコンタクトホール10mを通じて第1層配線11eと電気的に接続されている。なお、コレクタ引出用のn+型半導体領域15およびベース用のp型半導体領域17は、その間に介在された分離部6Aによって電気的に分離されている。

【0086】

一方、図12に示すように、pMOSQ1aは、分離部6Bおよび埋込絶縁層4Bに取り囲まれた半導体層4Cに形成されている。この半導体層4Cには、nウエル5N2が形成されている。このnウエル5N2の上部には、pMOSQ1aのソース・ドレインを形成する一対のp+型半導体領域7P4,7P5およびウエル電位供給部を形成するn+型半導体領域8N7が形成されている。この一対のp+型半導体領域7P4,7P5には、例えばホウ素が含有され、ウエル電位供給部を形成するn+型半導体領域8N7には、例えばリンまたはヒ素が含有されている。

【0087】

p+型半導体領域7P4,7P5は、それぞれ層間絶縁膜9aに穿孔されたコンタクトホール10n,10pを通じて第1層配線11f,11gと電気的に接続されている。n+型半導体領域8N7は、層間絶縁膜9aに穿孔されたコンタクトホール10qを通じて第1層配線11hと電気的に接続されている。なお、p+型半導体領域7P5およびn+型半導体領域8N7の間は、分離部6Aによって分離されている。

【0088】

pMOSQ1aのゲート絶縁膜12cおよびゲート電極13cは、上記トリガ素子TRのゲート絶縁膜12aおよびがゲート電極13aと同じ構造となっている。異なるのは、ゲート電極13cは、pMOSQ1bのゲート電極13dと電気的に接続されていることである。

【0089】

nMOSQ1bは、分離部6Bおよび埋込絶縁層4Bに取り囲まれた半導体層4Cに形成されている。この半導体層4Cには、pウエル5P3が形成されている。このpウエル5P3の上部には、nMOSQ1bのソース・ドレインを形成する一対のn+型半導体領域8N8,8N9およびウエル電位供給部を形成するp+型半導体領域7P6が形成されている。この一対のn+型半導体領域8N8,8N9には、例えばリンまたはヒ素が含有され、ウエル電位供給部を形成するp+型半導体領域7P6には、例えばホウ素が含有されいる。

【0090】

n+型半導体領域8N8,8N9は、それぞれ層間絶縁膜9aに穿孔されたコンタクトホール10r,10sを通じて第1層配線11i,11fと電気的に接続されている。p+型半導体領域7P6は、層間絶縁膜9aに穿孔されたコンタクトホール10tを通じて第1層配線11jと電気的に接続されている。なお、n+型半導体領域8N8およびp+型半導体領域7P6の間は、分離部6Aによって分離されている。また、nMOSQ1aのゲート絶縁膜12dおよびゲート電極13dは、上記トリガ素子TRのゲート絶縁膜12aおよびがゲート電極13aと同じ構造となっている。

【0091】

また、図10に示すように、外部端子1VSSは、半導体チップの外部から内部に対して低電位の電源を供給する端子であり、上記低電位側の電源端子VSSの一つでもある。この外部端子1VSSは、これと一体的にパターン形成された第1層配線11a,11a1〜11a3を通じて、上記保護回路3の各部と電気的に接続されているとともに、内部回路2内の電源端子VSSと電気的に接続されている。

【0092】

また、外部端子1S(1)は、半導体チップの外部から内部に対して信号を伝送する端子であり、これと一体的にパターン形成された第1層配線11b,11b1,11b3を通じて、上記保護回路3の各部と電気的に接続されているとともに、第1層配線11b4を通じて内部回路2内の回路の入力端子(ここではバイポーラトランジスタQ3のベースが例示)と電気的に接続されている。

【0093】

さらに、外部端子1VCCは、半導体チップの外部から内部に対して高電位の電源を供給する端子であり、上記高電位側の電源端子VCCの一つでもある。この外部端子1VCCは、これと一体的にパターン形成された第1層配線11c,11c1を通じて、上記保護回路3の一部と電気的に接続されているとともに、内部回路2内の電源端子VCCと電気的に接続されている。

【0094】

なお、第1層配線11a,11a1〜11a3,11b,11b1,11b3,11b4,11c,11c1は、表面保護膜9bによって被覆されている。表面保護膜9bは、例えば酸化シリコンの単層膜、酸化シリコン膜上に窒化シリコン膜を堆積してなる積層膜または酸化シリコン膜上に窒化シリコン膜を介してポリイミド膜を堆積してなる積層膜からなる。表面保護膜9bの一部には、上記外部端子1,1S,1VSS,1VCCが露出するような開口部19が形成されている。

【0095】

次に、本実施の形態1の半導体装置におけるSOI基板4の製造方法の一例を図13および図14によって説明する。

【0096】

まず、図13(a)に示すように、例えばp型のシリコン単結晶からなる半導体層形成基板4Csa(この段階では、例えば平面略円形状の半導体ウエハと称する半導体薄板)の表面に、例えば熱酸化法等によって酸化シリコンからなる埋込絶縁層4Bを形成する。続いて、図13(b)に示すように、その半導体層形成基板4Csaとは別に、例えばp型のシリコン単結晶からなる支持基板4A(この段階では、例えば平面略円形状の半導体ウエハと称する半導体薄板)を用意し、それら半導体層形成基板4Csaおよび支持基板4Aを埋込絶縁層4Bを介して張り合わせ加熱処理(例えば1100℃以下)を施す。その後、半導体層形成基板4Csaの裏面を研磨することにより、図13(c)に示すように、半導体基板層4Csを形成する。その後、半導体基板層4Cs上に、例えばp型のシリコン単結晶からなるエピタキシャル層を形成し、前記SOI基板4を製造する。この技術の場合、半導体基板層4Csの結晶性が優れている。また、埋込絶縁層4Bを熱酸化法によって形成しているので、ピンホール等が欠陥を少なくすることができる。

【0097】

また、例えば次のようにしても良い。まず、図14(a)に示すように、上記と同様に半導体層形成基板4Csaの表面に埋込絶縁層4Bを形成した後、埋込絶縁層4Bを形成した半導体層形成基板4Csaの所定の深さ位置に水素等をイオン注入法等によって注入することにより注入層20を形成する。続いて、図14(b)に示すように、その半導体層形成基板4Csaと、支持基板4Aとを埋込絶縁層4Bを介して張り合わせ加熱処理(例えば1100℃以下)を施す。この際、上記注入層20にマイクロクラックを生じさせることにより、図14(c)に示すように、埋込絶縁層4B上に一部の半導体層形成基板4Csaを残して半導体基板層4Csを形成し、残りの半導体層形成基板4Csa部分を剥離する。その後、半導体基板層4Csの表面を軽く研磨し、表面処理を施した後、上記と同様に、エピタキシャル層を形成し、前記SOI基板4を製造する。この技術の場合、上記図13の製造技術による効果の他に、半導体基板層4Csの厚さを制御性の高いイオン注入法によって設定できるので、半導体基板層4Csの厚さの均一性を向上させることができる。

【0098】

次に、本実施の形態1の半導体装置の製造方法の一例を図15〜図18によって説明する。なお、図15〜図18において、(a)は保護回路3部分のSOI基板4の断面図を示し、(b)はCMOS回路部分のSOI基板4の断面図を示している。

【0099】

図15は、本実施の形態1の半導体装置における製造工程中のSOI基板4(この段階では、半導体ウエハと称する平面円形状の薄板)の要部断面図を示している。半導体層4Cは、半導体基板層4Cs上にエピタキシャル層4Cepが形成されてなり、その主面には、分離部6Aが、例えばLOCOS法等によって形成されている。また、分離部6Bは、分離部6Aの上面から埋込絶縁層4Bに達する溝が掘られ、その内部に酸化シリコン膜等からなる絶縁膜が埋め込まれることで形成されている。半導体層4Cには、nウエル5N1,5N2およびpウエル5P1〜5P3が形成されている。

【0100】

また、半導体層4Cの主面上には、ゲート絶縁膜12a〜12dが形成されている。ゲート絶縁膜12a〜12dは、例えば酸化シリコン膜からなり、例えば同一の熱酸化工程によって形成されている。このように、本実施の形態1においては、トリガ素子用のnMOSのゲート絶縁膜12aと、内部回路のMOSのゲート絶縁膜12c,12dとを同一の熱酸化処理によって形成する。

【0101】

また、そのゲート絶縁膜12a〜12d上には、ゲート電極13a〜13dが形成されている。ゲート電極13aは、例えばSOI基板4の主面上に、例えば低抵抗ポリシリコン膜等をCVD(Chemical Vapor Deposition)法等によって堆積した後、これをフォトリソグラフィ技術およびドライエッチング技術によってパターニングすることによって形成されている。このように、本実施の形態1においては、トリガ素子用のnMOSのゲート電極13aと、内部回路のMOSのゲート電極13c,13dとを、同一の導体膜で、同一工程時にパターン形成する。

【0102】

まず、このようなSOI基板4上に、図16に示すように、n型半導体領域の形成領域が露出され、それ以外が被覆されるようなフォトレジストパターン21aを形成する。続いて、そのフォトレジストパターン21aをマスクとして、半導体層4Cに、例えばリンまたはヒ素をイオン注入法等によって導入した後、フォトレジストパターン21aを除去する。このような不純物の導入処理によって、図17に示すように、n+型半導体領域8N1〜8N9を形成する。このように、本実施の形態1においては、トリガ素子用のnMOSのソース・ドレイン用のn+型半導体領域8N3,8N4と、内部回路のnMOSのソース・ドレイン用のn+型半導体領域8N8,8N9とを同工程時に形成する。

【0103】

次いで、SOI基板4上に、p型半導体領域の形成領域が露出され、それ以外が被覆されるようなフォトレジストパターン21bを形成した後、そのフォトレジストパターン21bをマスクとして、半導体層4Cに、例えばホウ素をイオン注入法等によって導入する。このような不純物の導入処理によって、図18に示すように、p+型半導体領域7P1〜7P6を形成する。

【0104】

このように本実施の形態1の半導体装置の製造方法においては、寄生PNPNサイリスタTHを駆動するトリガ素子TRの各部と、保護対象の内部回路2における素子の各部とを別々に形成するのではなく、同一工程時に形成する。すなわち、内部回路2の素子に合わせてトリガ素子TRを形成する。このため、例えば内部回路2の素子(MOS)の寸法(各部平面寸法やゲート絶縁膜厚)が小さくなれば、それに応じてトリガ素子TRの寸法(各部平面寸法やゲート絶縁膜厚)も小さくなり、寄生PNPNサイリスタTHのターンオン時間も短くすることができる。すなわち、上記サイリスタ保護素子の感度を、内部回路2の素子(MOS)に応じて最適な値にすることが可能となっている。したがって、内部回路2の素子(MOS)を保護するのに最適なサイリスタ保護素子を形成することが可能となる。このことについてはクランプ素子CLについても同様の効果が得られる。

【0105】

また、上記サイリスタ保護素子を形成するために、新たなプロセスや複雑なプロセスを追加する必要がない。このため、製造時間や製造コストを増大させることなく、サイリスタ保護素子を有する半導体装置の製造することが可能となる。したがって、サイリスタ保護素子を有する半導体装置のコストを低減することが可能となる。

【0106】

(実施の形態2)

本実施の形態2においては、図19に示すように、p+型半導体領域7P1,7P2、n+型半導体領域8N1〜8N4およびゲート電極13aの表層に、シリサイド層22が形成されている。このシリサイド層22は、例えばコバルトシリサイド、チタンシリサイドまたはタングステンシリサイド等のような高融点金属シリサイドからなり、通常のサリサイドプロセスによって形成されている。

【0107】

なお、ゲート電極13aの側面には、サイドウォール23が形成されている。このサイドウォール23は、例えば酸化シリコン膜からなり、ゲート電極13aの表層のシリサイド層22と、ソース・ドレイン用のn+型半導体領域8N3,8N4の表層のシリサイド層22とが電気的に接続されないように形成されている。

【0108】

このように、本実施の形態2においては、内部回路2に高周波信号回路が設けられるような半導体装置であっても、その電気的特性(周波数特性)を劣化させることなく、サイリスタ保護素子を半導体装置の回路、特に入力に組み込むことが可能となっている。

【0109】

また、そのシリサイド層22を内部回路2を構成するMOSにおけるソース・ドレイン用の半導体領域およびゲート電極の表層に形成することにより、内部回路2の電気的特性(特に周波特性)を向上させることができるので、半導体装置の動作速度を向上させることが可能となる。また、このシリサイド層22は、通常のサリサイドプロセスにより、保護回路3と内部回路2とで同時に形成できるので、この構造を採用したからといって特に製造プロセスが増加することもない。なお、この場合も内部回路2のMOSのゲート電極の側面に上記サイドウォール23が形成される。

【0110】

ところで、本実施の形態2においては、上記サイリスタ保護素子を有する半導体装置にサリサイドプロセスを採用するのにあたって、例えば以下のような構造上の工夫がなされている。

【0111】

寄生PNPNサイリスタTHのバイポーラトランジスタQTH1の形成領域において、p+型半導体領域7P28(エミッタ)と、n+型半導体領域8N2(ベース)との間に、分離部6Aが形成されている。これは、その箇所に分離部6Aを形成せずに安易にシリサイド層22を形成してしまうと、p+型半導体領域7P2と、n+型半導体領域8N2とがシリサイド層22を通じて電気的に接続され、寄生PNPNサイリスタTHのバイポーラトランジスタQTH1のベース・エミッタ間がシリサイド層22を通じて低抵抗で接続されてしまい、バイポーラトランジスタQTH1が動作しなくなってしまうので、それを防止するためである。また、p+型半導体領域7P2と、n+型半導体領域8N2との間に分離部6Aを設けることにより、バイポーラトランジスタQTH1のベース・エミッタ間に並列に接続される抵抗Rth1(nウエル5N1の拡散抵抗)をある程度大きくすることができるので、バイポーラトランジスタQTH1をオンさせ易くすることができる。すなわち、寄生PNPNサイリスタTHの感度を向上させることが可能となる。

【0112】

以上のような構造および製造方法以外は、前記実施の形態1と同じなので説明を省略する。

【0113】

(実施の形態3)

本実施の形態3においては、図20に示すように、寄生PNPNサイリスタTHのバイポーラトランジスタQth1のベースと外部端子1との間に抵抗(第1の抵抗)R2を接続し、寄生PNPNサイリスタTHのバイポーラトランジスタQth2のベース(トリガ電極部)と電源端子VSSとの間に抵抗(第2の抵抗)R3を接続している。なお、抵抗R2を無くしても良い。

【0114】

前記実施の形態1,2においては、上記サイリスタ保護素子の感度の向上を図っていたが、その感度の向上のために寄生PNPNサイリスタTHのターンオン電流をあまり小さな値にしてしまうと、過電圧以外の要因によって寄生PNPNサイリスタTHが動作してしまう。

【0115】

そこで、本実施の形態3においては、上記抵抗R2,R3を回路内に積極的に組み込み、それらの抵抗値を調整するようにした。これにより、寄生PNPNサイリスタTHのターンオン電流を適切な値に設定することができるので、上記のような寄生PNPNサイリスタTHの誤動作を防止することが可能となる。

【0116】

このような抵抗R2,R3は、拡散層を用いた抵抗(以下、拡散抵抗という)またはポリシリコン膜を用いた抵抗(以下、ポリシリ抵抗という)によって形成することができる。拡散抵抗は、前記SOI基板4の半導体層4Cに不純物を導入することにより形成する。また、ポリシリ抵抗は、前記SOI基板4の半導体層4C上にポリシリ抵抗をパターン形成する。いずれの場合も、抵抗値の設定精度および再現性が高いので、サイリスタ保護素子の回路上およびデバイス上の設計を容易にすることが可能となる。特に、ポリシリ抵抗の場合は、SOI基板4上に形成することができるので、サイリスタ保護素子の平面的なサイズを拡散抵抗に比べて小さくすることが可能となる。

【0117】

なお、抵抗R2の値は、nウエル5N1の抵抗と拡散抵抗(またはポリシリ抵抗)との和になる。また、抵抗R3の値は、pウエル5P1の抵抗と拡散抵抗(またはポリシリ抵抗)との和になる。しかし、いずれの場合も拡散抵抗(またはポリシリ抵抗)をウエルの抵抗よりも高くすることにより、それらが実効的なものとなるので、nウエル5N1やpウエル5P1の抵抗を無視することができる。

【0118】

このような場合のデバイス構造の一例を図21に示す。ダイオードD1と寄生PNPNサリサイドTHとが、分離部6Aおよび溝型の分離部6Bによって電気的に分離されている。すなわち、ダイオードD1とサイリスタ保護素子(寄生PNPNサイリスタTHおよびトリガ素子TR)とが互いに絶縁された別々の半導体層4Cに形成されている。n+型半導体領域8N1は、分離部6A,6Bによって2つのn+型半導体領域8N1aおよびn+型半導体領域(第3の半導体領域)8N1bに分離されている。ダイオードD1と接続されるn+型半導体領域8N1aは、コンタクトホール10b1を通じて第1層配線11b11に接続され、これを通じて外部端子1と電気的に接続されている。一方、寄生PNPNサイリスタTHのバイポーラトランジスタQ1aのベースと接続されるn+型半導体領域8N1bは、コンタクトホール10b2を通じて第1層配線11b12に接続され、これを通じて外付けの抵抗R2aに電気的に接続され、さらに、これを介して外部端子1(1S)と電気的に接続されている。

【0119】

また、寄生PNPNサイリスタTHのバイポーラトランジスタQ1aのベースと接続されるn+型半導体領域8N1bとp+型半導体領域7P2との間に分離部6Aを設けることにより、n+型半導体領域8N1bとp+型半導体領域7P2との間の分離を行い、それらの間のnウエル5N1に形成される抵抗Rth1を高くしている。図20に示した抵抗R2は、この抵抗R2aと抵抗Rth1との和で形成されている。ここでは、抵抗R2aの値が、抵抗Rth1の値よりも高く設定されており、抵抗R2の実効的な値を決めている。

【0120】

また、p+型半導体領域7P2と、n+型半導体領域8N2との間にも分離部6が形成されている。また、pウエル5P1の上部において分離部6Aに囲まれた領域には、p+型半導体領域(第9の半導体領域)7P7が形成されている。このp+型半導体領域7P7は、例えばホウ素がpウエル5P1に含有されてなり、トリガ素子TRを構成するnMOSの基板電極と、pウエル5P1に形成される抵抗Rth2を介して電気的に接続されている。また、このp+型半導体領域7P7は、層間絶縁膜9aに穿孔されたコンタクトホール10uを通じて第1層配線11a4と電気的に接続され、これを通じて外付けの抵抗R3aに電気的に接続され、さらに、これを介して低電位側の電源端子VSSと電気的に接続されている。図20に示した抵抗R3は、この抵抗R3aと抵抗Rth2との和で形成されている。ここでは、抵抗R3aの値が、抵抗Rth2の値よりも高く設定されており、抵抗R3の実効的な値を決めている。

【0121】

(実施の形態4)

本実施の形態4は、前記実施の形態3に、前記実施の形態2の技術を適用したものである。すなわち、本実施の形態4においては、図22に示すように、p+型半導体領域7P1,7P2,7P7、n+型半導体領域8N1〜8N4およびゲート電極13aの表層に、シリサイド層22が形成されている。

【0122】

本実施の形態4においては、前記実施の形態2,3と同様の効果を得ることが可能となる。特に、本実施の形態4によれば、サイリスタ保護素子の各電極間の抵抗値を抵抗R2a,R3aの値の調整により適宜高い精度で調節できるので、サイリスタ保護素子の動作特性を最適化することが可能となる。

【0123】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0124】

例えば前記実施の形態1〜4においては、配線をアルミニウム等で形成した場合について説明したが、これに限定されるものではなく、例えば銅によって形成しても良い。その場合、層間絶縁膜に配線溝を形成し、その溝内に配線材料を埋め込むことで配線層を形成する、いわゆるダマシンまたはデュアルダマシン法によって多層配線構造を構成しても良い。これにより、信号の伝送速度を向上させることが可能となる。また、配線の微細化が可能となる。なお、この配線材料に銅を用いた場合には、配線溝の内壁面に、例えば窒化チタン等のような銅の拡散を防止するためのバリア膜を設けることが好ましい。

【0125】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野である高周波信号回路を有する半導体装置に適用した場合について説明したが、それに限定されるものではなく、例えばDRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)またはフラッシュメモリ(EEPROM;Electric Erasable Programmable Read Only Memory)等のようなメモリ回路を有する半導体装置、マイクロプロセッサ等のような論理回路を有する半導体装置あるいは上記メモリ回路と論理回路とを同一半導体基板に設けている混載型の半導体装置にも適用できる。

【0126】

【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

(1).本発明によれば、保護用のサイリスタのゲートと、前記トリガ素子の基板電極部とを同一の半導体領域内に設けて、そのゲートと基板電極部とを電気的に接続し、前記トリガ素子の降伏により発生した基板電流により、前記保護用のサイリスタを駆動させることにより、保護回路を構成する保護用のサイリスタのターンオン時間を短縮することが可能となる。

(2).上記(1)により、保護用のサイリスタを有する保護回路の放電能力を向上させることが可能となる。

(3).上記(1),(2)により、内部回路の素子の微細化に対応した保護回路構成を実現することが可能となる。

(4).上記(1),(2)により、絶縁層上に半導体層を設けてなる基板を用いた半導体装置であっても、過電流を速やかに逃がすことが可能となる。

(5).本発明によれば、保護用のサイリスタのゲートと、前記トリガ素子の基板電極部とを同一の半導体領域内に設けて、そのゲートと基板電極部とを電気的に接続することにより、保護回路を微細化することが可能となる上、各保護回路を構成する素子の電極間の抵抗や寄生容量を下げることができる。したがって、内部回路の電気的特性を劣化させることなく、保護回路の放電能力を向上させることが可能となる。

(6).本発明によれば、保護用のサイリスタのゲートと、前記トリガ素子の基板電極部とを同一の半導体領域内に設けて、そのゲートと基板電極部とを電気的に接続し、前記トリガ素子の降伏により発生した基板電流により、前記保護用のサイリスタを駆動させることにより、保護用のサイリスタの感度劣化が保護素子を形成する半導体領域の寸法変動の影響を受け難い構造とすることができる。したがって、保護回路のデバイス設計を容易にすることが可能となる。

【図面の簡単な説明】

【図1】本発明者らが本発明をするのに検討した技術の回路図である。

【図2】図1の回路のデバイス構造を示す半導体基板の断面図である。

【図3】本発明の一実施の形態である半導体装置の要部回路図である。

【図4】(a)は図3の半導体装置の保護回路における負の過電流の放電経路を模式的に示す回路図であり、(b)は正の過電流の放電経路を模式的に示す回路図である。

【図5】図3の保護回路の保持電圧を示す典型的な電流−電圧特性を示すグラフ図である。

【図6】(a)および(b)は図3の半導体装置の入力回路の一例を示す回路図である。

【図7】(a)および(b)は図3の半導体装置の入力回路の他の一例を示す回路図である。

【図8】図3の半導体装置の保護回路のデバイス構造を示す半導体基板の要部平面図である。

【図9】図8のA−A線の断面図である。

【図10】図3の半導体装置のデバイス構造をさらに詳細に示した半導体基板の要部平面図である。

【図11】図10のA−A線の断面図である。

【図12】図10の所定の部分の断面図である。

【図13】(a)〜(c)は図8および図9の半導体基板の製造工程中における要部断面図である。

【図14】(a)〜(d)は図8および図9の半導体基板の製造工程中における要部断面図である。

【図15】(a)および(b)は図8および図9の半導体装置の製造工程中における要部断面図である。

【図16】(a)および(b)は図15に続く半導体装置の製造工程中における要部断面図である。

【図17】(a)および(b)は図16に続く半導体装置の製造工程中における要部断面図である。

【図18】(a)および(b)は図17に続く半導体装置の製造工程中における要部断面図である。

【図19】本発明の他の実施の形態である半導体装置の要部断面図である。

【図20】本発明のさらに他の実施の形態である半導体装置の要部回路図である。

【図21】図20のデバイス構造を示す半導体装置の要部断面図である。

【図22】本発明のさらに異なる実施の形態である半導体装置の要部断面図である。

【符号の説明】

1 外部端子

1VSS 外部端子

1S 外部端子

1VCC 外部端子

2 内部回路

3 保護回路

4 SOI基板

4A 支持基板

4B 埋込絶縁層

4C 半導体層

4Cs 半導体基板層

4Csa 半導体層形成基板

4Cep エピタキシャル層

5N1 nウエル

5N2 nウエル

5P1 pウエル

5P2 pウエル

5P3 pウエル

6A 分離部

6B 分離部

7P1〜7P7 p+型半導体領域

8N1〜8N9 n+型半導体領域

8N1a,8N1b n+型半導体領域

9a 層間絶縁膜

9b 表面保護膜

10a〜10k,10m,10n、10p〜10u コンタクトホール

10b1,10b2 コンタクトホール

11a,11a1〜11a4,11b11,11b12 第1層配線

11b,11b1〜11b4 第1層配線

11c、11c1 第1層配線

11d〜11j 第1層配線

12a〜12d ゲート絶縁膜

13a〜13d ゲート電極

14 埋込n+型ウエル

15 n+型半導体領域

16 n型半導体領域

17 p型半導体領域

18 n+型半導体領域

19 開口部

20 注入層

21a フォトレジストパターン

22 シリサイド層

23 サイドウォール

VCC 高電位側の電源端子

VSS 低電位側の電源端子

50 入力端子

51a ドレイン端子

51b ソース端子

51c ゲート端子

51d 基板端子

52a エミッタ端子

52b 電位供給端子

52c エミッタ端子

53 高濃度p型基板

54 低濃度p型エピタキシャル層

55 p型ウエル

56 n型ウエル

D1 ダイオード

TH 寄生PNPNサイリスタ

TR トリガ素子

CL クランプ素子

Qth1,Qth2 バイポーラトランジスタ

Rth1 抵抗

R1 入力保護抵抗

INV CMOSインバータ回路

Q1a pMOS・FET

Q1b nMOS・FET

Q2a pMOS・FET

Q2b nMOS・FET

Q3 バイポーラトランジスタ

Q4 nMOS

Q5a,Q5b バイポーラトランジスタ

L1〜L3 活性領域

R50 入力保護抵抗

Q50 保護用MOS・FET

TH50 寄生PNPNサイリスタ

Qth51 寄生PNPバイポーラトランジスタ

Qth52 寄生NPNバイポーラトランジスタ

Rth51 等価nウエル抵抗

Rth52 等価p基板抵抗

Claims (8)

- 第1端子と第2端子との間に接続されたサイリスタを含む保護回路を有する半導体装置であって、

n型の導電型からなる第1半導体領域と、

前記第1半導体領域と隣接するp型の導電型からなる第2半導体領域と、

前記第1半導体領域内に形成されたp型の導電型からなる第3半導体領域と、

絶縁膜を介して前記第2半導体領域上に形成された導電体片と、

前記第2半導体領域内に形成されたn型の導電型からなる第4および第5半導体領域であって、前記導電体片の一方側に形成された前記第4半導体領域と、前記導電体片の他方側に形成された前記第5半導体領域とを有し、

前記第3および第4半導体領域は前記第1端子と電気的に接続されており、前記導電体片と前記第5半導体領域は前記第2端子と電気的に接続されており、前記第1、第2、第3および第5半導体領域はサイリスタとして機能し、

前記第1半導体領域内に形成されたn型の導電型からなる第6半導体領域と、

前記第1半導体領域内に形成されたp型の導電型からなる第7半導体領域とを有し、

前記第6半導体領域は前記第1端子と電気的に接続されており、前記第7半導体領域は前記第2端子と電気的に接続されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記第1および第2半導体領域を横切って延在するn型の導電型からなる第8半導体領域をさらに有することを特徴とする半導体装置。 - 第1端子と第2端子との間に接続されたサイリスタを含む保護回路を有する半導体装置であって、

n型の導電型からなる第1半導体領域と、

前記第1半導体領域と隣接するp型の導電型からなる第2半導体領域と、

前記第1半導体領域内に形成されたp型の導電型からなる第3半導体領域と、

絶縁膜を介して前記第2半導体領域上に形成された導電体片と、

前記第2半導体領域内に形成されたn型の導電型からなる第4および第5半導体領域であって、前記導電体片の一方側に形成された前記第4半導体領域と、前記導電体片の他方側に形成された前記第5半導体領域とを有し、

前記第3および第4半導体領域は前記第1端子と電気的に接続されており、前記導電体片と前記第5半導体領域は前記第2端子と電気的に接続されており、前記第1、第2、第3および第5半導体領域はサイリスタとして機能し、

前記第1および第2半導体領域を横切って延在するn型の導電型からなる第6半導体領域を有することを特徴とする半導体装置。 - 請求項1または3記載の半導体装置において、

前記第3半導体領域は前記第2半導体領域よりも高い不純物濃度を有し、前記第4および第5半導体領域は前記第1半導体領域よりも高い不純物濃度を有することを特徴とする半導体装置。 - 請求項1または3記載の半導体装置において、

ゲート電極、ソースおよびドレイン領域をそれぞれ有するpチャネル型MISFETおよびnチャネル型MISFETを含む内部回路を有し、

前記第1端子は前記pチャネル型MISFETおよびnチャネル型MISFETと電気的に接続されていることを特徴とする半導体装置。 - 請求項1または3記載の半導体装置において、

絶縁膜上に半導体層が形成され、

前記半導体層に前記絶縁膜に達する分離部が形成され、

前記絶縁膜および分離部に囲まれた前記半導体層に、前記第1半導体領域および前記第2半導体領域が形成されることを特徴とする半導体装置。 - 請求項1または3記載の半導体装置において、

トリガ素子は、前記導電体片、前記第4および第5半導体領域を有し、

前記導電体片はトリガ素子のゲート電極を構成することを特徴とする半導体装置。 - 絶縁層上に形成された半導体層と、

前記半導体層の主面側から前記絶縁層に延びる分離部と、

前記半導体層上に形成された信号用の端子と、

前記半導体層に形成された内部回路と、

前記信号用の端子を前記内部回路に電気的に接続する信号用の配線と、

前記信号用の配線と基準電位用の端子との間に電気的に接続された保護回路とを有し、

前記保護回路は、保護用のサイリスタと、その駆動を誘発するトリガ素子とを有しており、

前記保護用のサイリスタと、前記トリガ素子とを、前記分離部に囲まれた同一の半導体層内に形成し、前記保護用のサイリスタのゲートと、前記トリガ素子の基板電極部とを、前記同一の半導体層内の同一の半導体領域に形成し、

前記保護用のサイリスタは、

前記同一の半導体層内に形成された第1の半導体領域と、

前記第1の半導体領域に対して反対の導電型の半導体領域であって、前記第1の半導体領域に隣接するように前記同一の半導体層に形成され、前記保護用のサイリスタのゲートが形成される第2の半導体領域と、

前記第1の半導体領域に対して同一の導電型の半導体領域であって、前記第1の半導体領域内に形成され、かつ、前記信号用の端子と電気的に接続された第3の半導体領域と、

前記第1の半導体領域に対して反対の導電型の半導体領域であって、前記第1の半導体領域内に形成され、かつ、前記信号用の端子と電気的に接続された第4の半導体領域と、

前記第1の半導体領域に対して同一の導電型の半導体領域であって、前記第1の半導体領域および第2の半導体領域に跨るように形成された第5の半導体領域とを有し、

前記トリガ素子は、電界効果トランジスタからなり、

前記第2の半導体領域に対して反対の導電型の半導体領域であって、前記第2の半導体領域内に形成され、かつ、前記信号用の端子と電気的に接続されたソース・ドレイン用の第6の半導体領域と、

前記第2の半導体領域に対して反対の導電型の半導体領域であって、前記第2の半導体領域内に形成され、かつ、前記基準電位用の端子と電気的に接続されたソース・ドレイン用の第7の半導体領域と、

前記第6、第7の半導体領域間の第2の半導体領域に形成され、前記トリガ素子の基板電極部を形成するチャネル領域と、

前記チャネル領域上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極とを有し、

前記ゲート絶縁膜と前記内部回路の電界効果トランジスタのゲート絶縁膜とを同一工程時に形成する工程と、

前記ゲート電極と前記内部回路の電界効果トランジスタのゲート電極とを同一工程時に形成する工程と、

前記第3、第5、第6、第7の半導体領域と前記内部回路を構成する素子の半導体領域とを同一の不純物導入工程によって形成する工程と、

前記第4の半導体領域と前記内部回路を構成する素子の半導体領域とを同一の不純物導入工程によって形成する工程とを有することを特徴とする半導体装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000071795A JP3810246B2 (ja) | 2000-03-15 | 2000-03-15 | 半導体装置および半導体装置の製造方法 |

| TW090104497A TW517353B (en) | 2000-03-15 | 2001-02-27 | Semiconductor device and manufacturing method of the semiconductor device |

| US09/804,193 US6621108B2 (en) | 2000-03-15 | 2001-03-13 | Semiconductor device and the process of manufacturing the semiconductor device |

| KR1020010013105A KR100698990B1 (ko) | 2000-03-15 | 2001-03-14 | 반도체 장치 및 반도체 장치의 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000071795A JP3810246B2 (ja) | 2000-03-15 | 2000-03-15 | 半導体装置および半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001267433A JP2001267433A (ja) | 2001-09-28 |

| JP2001267433A5 JP2001267433A5 (ja) | 2005-02-03 |

| JP3810246B2 true JP3810246B2 (ja) | 2006-08-16 |

Family

ID=18590310

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000071795A Expired - Fee Related JP3810246B2 (ja) | 2000-03-15 | 2000-03-15 | 半導体装置および半導体装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6621108B2 (ja) |

| JP (1) | JP3810246B2 (ja) |

| KR (1) | KR100698990B1 (ja) |

| TW (1) | TW517353B (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004531047A (ja) * | 2000-11-06 | 2004-10-07 | サーノフ コーポレイション | 高速トリガリングのためのコンパクト内部寸法及び外部オンチップ・トリガリングを有するシリコン制御整流器静電放電保護デバイス |

| US7020857B2 (en) * | 2002-05-20 | 2006-03-28 | International Business Machines Corporation | Method and apparatus for providing noise suppression in a integrated circuit |

| JP4146672B2 (ja) | 2002-06-14 | 2008-09-10 | シャープ株式会社 | 静電気保護素子 |

| US6873015B2 (en) * | 2002-10-02 | 2005-03-29 | Micron Technology, Inc. | Semiconductor constructions comprising three-dimensional thin film transistor devices and resistors |

| US7808047B1 (en) * | 2002-11-14 | 2010-10-05 | Altera Corporation | I/O ESD protection device for high performance circuits |

| JP4318511B2 (ja) * | 2003-08-26 | 2009-08-26 | 三洋電機株式会社 | 昇圧回路 |

| JP4065855B2 (ja) * | 2004-01-21 | 2008-03-26 | 株式会社日立製作所 | 生体および化学試料検査装置 |

| US6936514B1 (en) | 2004-04-05 | 2005-08-30 | Advanced Micro Devices, Inc. | Semiconductor component and method |

| KR100679943B1 (ko) | 2004-11-10 | 2007-02-08 | 주식회사 하이닉스반도체 | 낮은 촉발전압에서 동작이 가능한 실리콘제어정류기구조의 정전기방전 보호 회로 |

| US7223640B2 (en) * | 2005-03-03 | 2007-05-29 | Advanced Micro Devices, Inc. | Semiconductor component and method of manufacture |

| US20070102789A1 (en) * | 2005-11-09 | 2007-05-10 | International Business Machines Corporation | Bipolar transistor and back-gated transistor structure and method |

| JP5243773B2 (ja) * | 2006-12-12 | 2013-07-24 | 株式会社豊田中央研究所 | 静電気保護用半導体装置 |

| JP2008205271A (ja) * | 2007-02-21 | 2008-09-04 | Matsushita Electric Ind Co Ltd | 半導体保護回路およびその製造方法、半導体保護回路の動作方法 |

| US7876602B2 (en) * | 2007-06-18 | 2011-01-25 | Bae Systems Information And Electronic Systems Integration Inc. | Single-event upset immune static random access memory cell circuit, system, and method |

| WO2010038101A1 (en) * | 2008-10-03 | 2010-04-08 | Freescale Semiconductor, Inc. | Semiconductor device and electronic device |

| US9916381B2 (en) | 2008-12-30 | 2018-03-13 | Telecom Italia S.P.A. | Method and system for content classification |

| FR3001085A1 (fr) * | 2013-01-15 | 2014-07-18 | St Microelectronics Sa | Dispositif semiconducteur bidirectionnel de protection contre les decharges electrostatiques, utilisable sans circuit de declenchement |

| JP2014165245A (ja) * | 2013-02-22 | 2014-09-08 | Toyota Central R&D Labs Inc | 静電気保護用半導体装置 |

| US9438034B2 (en) * | 2014-01-15 | 2016-09-06 | Nanya Technology Corporation | Transient voltage suppressor |

| US9287254B2 (en) * | 2014-01-30 | 2016-03-15 | Stmicroelectronics S.A. | Electronic device and protection circuit |

| US9871126B2 (en) * | 2014-06-16 | 2018-01-16 | Infineon Technologies Ag | Discrete semiconductor transistor |

| US10411006B2 (en) * | 2016-05-09 | 2019-09-10 | Infineon Technologies Ag | Poly silicon based interface protection |

| US10600776B2 (en) * | 2017-02-24 | 2020-03-24 | Nxp B.V. | Device and method for electrostatic discharge (ESD) protection |

| US10361186B1 (en) * | 2018-02-07 | 2019-07-23 | Infineon Technologies Ag | Suppression of parasitic discharge path in an electrical circuit |

| JP7079638B2 (ja) * | 2018-03-29 | 2022-06-02 | ローム株式会社 | 半導体素子 |

| WO2021075353A1 (ja) * | 2019-10-18 | 2021-04-22 | 株式会社ソシオネクスト | 半導体集積回路装置 |

| CN111627902B (zh) * | 2020-06-04 | 2022-06-24 | 电子科技大学 | 一种具有sgt和晶闸管的可编程过电压保护器件 |

| CN111627903B (zh) * | 2020-06-04 | 2022-06-24 | 电子科技大学 | 一种具有u-mosfet和晶闸管的可编程过电压保护器件 |

| JP6818931B1 (ja) * | 2020-09-10 | 2021-01-27 | 善文 安藤 | 真空チャネル電界効果トランジスタ、その製造方法及び半導体装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5181091A (en) * | 1988-04-29 | 1993-01-19 | Dallas Semiconductor Corp. | Integrated circuit with improved protection against negative transients |

| DE59108436D1 (de) * | 1991-10-22 | 1997-02-06 | Itt Ind Gmbh Deutsche | Schutzschaltung für Anschlusskontakte von monolithisch integrierten Schaltungen |

| FR2685817B1 (fr) * | 1991-12-31 | 1994-03-11 | Sgs Thomson Microelectronics Sa | Protection generale d'un circuit integre contre les surcharges permanentes et decharges electrostatiques. |

| JPH0837238A (ja) * | 1994-07-21 | 1996-02-06 | Hitachi Ltd | 半導体集積回路装置 |

| JPH08306872A (ja) | 1995-05-01 | 1996-11-22 | Nippon Telegr & Teleph Corp <Ntt> | Mos入力保護回路 |

| US6064093A (en) * | 1996-03-29 | 2000-05-16 | Citizen Watch Co., Ltd. | Protection circuit with clamping feature for semiconductor device |

| US6121661A (en) * | 1996-12-11 | 2000-09-19 | International Business Machines Corporation | Silicon-on-insulator structure for electrostatic discharge protection and improved heat dissipation |

| JP4256544B2 (ja) * | 1998-08-25 | 2009-04-22 | シャープ株式会社 | 半導体集積回路の静電気保護装置、その製造方法および静電気保護装置を用いた静電気保護回路 |

-

2000

- 2000-03-15 JP JP2000071795A patent/JP3810246B2/ja not_active Expired - Fee Related

-

2001

- 2001-02-27 TW TW090104497A patent/TW517353B/zh not_active IP Right Cessation

- 2001-03-13 US US09/804,193 patent/US6621108B2/en not_active Expired - Lifetime

- 2001-03-14 KR KR1020010013105A patent/KR100698990B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| TW517353B (en) | 2003-01-11 |

| KR20010092313A (ko) | 2001-10-24 |

| US20010025963A1 (en) | 2001-10-04 |

| US6621108B2 (en) | 2003-09-16 |

| KR100698990B1 (ko) | 2007-03-26 |

| JP2001267433A (ja) | 2001-09-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3810246B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP4917172B2 (ja) | 垂直型電流制御型シリコン・オン・インシュレータ(soi)デバイス及びそれを形成する方法 | |

| KR100325553B1 (ko) | 반도체 집적회로의 정전기 보호장치, 그의 제조방법 및 그를사용한 정전기 보호회로 | |

| US6909149B2 (en) | Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies | |

| US8354722B2 (en) | SCR/MOS clamp for ESD protection of integrated circuits | |

| JP3675303B2 (ja) | 静電気保護回路が内蔵された半導体装置及びその製造方法 | |

| US20070040222A1 (en) | Method and apparatus for improved ESD performance | |

| US20050212051A1 (en) | Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies | |

| KR101195720B1 (ko) | 반도체 집적 회로 디바이스 및 그 제조 방법 | |

| JP3144330B2 (ja) | 半導体装置 | |

| EP0827202A2 (en) | Semiconductor device including protection means and method of fabricating the same | |

| CN109920849B (zh) | 后镇流式纵向npn晶体管 | |

| US8956925B2 (en) | Silicon controlled rectifier structure with improved junction breakdown and leakage control | |

| KR100673421B1 (ko) | 반도체 집적회로장치 및 그 제조방법 | |

| US8513738B2 (en) | ESD field-effect transistor and integrated diffusion resistor | |

| JP3942192B2 (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2009081458A (ja) | 半導体集積回路の静電気保護装置、その製造方法および静電気保護装置を用いた静電気保護回路 | |

| JP5337463B2 (ja) | 静電気保護素子、半導体装置及びそれらの製造方法 | |

| JPH1012746A (ja) | 半導体装置 | |

| JP3254549B2 (ja) | 半導体装置及びその製造方法 | |

| KR100289838B1 (ko) | 정전방전회로를 포함하는 반도체장치 및 그의 제조방법 | |

| KR20020082400A (ko) | Esd보호장치 및 그것의 제조방법 | |

| JPH09283638A (ja) | 半導体装置およびその製造方法 | |

| JPH10189876A (ja) | 半導体集積回路装置およびその製造方法 | |

| JPH06232354A (ja) | 静電気保護デバイス |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040301 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20050315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20051216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060502 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060523 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100602 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110602 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110602 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110602 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120602 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120602 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130602 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140602 Year of fee payment: 8 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |