JP3652257B2 - 半導体素子収納用パッケージ - Google Patents

半導体素子収納用パッケージ Download PDFInfo

- Publication number

- JP3652257B2 JP3652257B2 JP2001022707A JP2001022707A JP3652257B2 JP 3652257 B2 JP3652257 B2 JP 3652257B2 JP 2001022707 A JP2001022707 A JP 2001022707A JP 2001022707 A JP2001022707 A JP 2001022707A JP 3652257 B2 JP3652257 B2 JP 3652257B2

- Authority

- JP

- Japan

- Prior art keywords

- mounting portion

- semiconductor element

- screw mounting

- base

- screw

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Description

【発明の属する技術分野】

本発明は、半導体素子を収容し外部電気回路基板にネジ止め用の貫通孔や切欠を介してネジ止めされる半導体素子収納用パッケージに関する。

【0002】

【従来の技術】

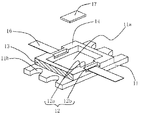

従来の、外部電気回路基板(図示せず)にネジ止め用の貫通孔や切欠を介してネジ止めされる半導体素子収納用パッケージ(以下、半導体パッケージという)の例を図3に示す。

【0003】

同図に示すように、半導体パッケージは一般に、略四角形の金属板から成り、上面に半導体素子17が載置される載置部11aと、対向する辺部に形成されたネジ取付部11bとを有する、鉄(Fe)−ニッケル(Ni)−コバルト(Co)合金や銅(Cu)−タングステン(W)合金等の金属材料から成る基体11を有する。また、1対の対向する側壁の内外の一部を切り欠いて形成された取付部12a、およびこの内外を導出するように形成されたメタライズ層12bから成り、内外を電気的に導通する入出力部12を有するとともに、他の1対の対向する側壁の外面に形成されたメタライズ層13を有し、載置部11aを囲繞するようにして基体11の上面に銀ロウ等のロウ材を介して取着される、アルミナ(Al2O3)セラミックスや窒化アルミニウム(AlN)セラミックス等の絶縁体から成る枠体14を具備している。

【0004】

この枠体14のメタライズ層13は、基体11の上面に枠体14を銀ロウ等のロウ材で接合した際に、その接合部位にメニスカスを形成することにより接合を強固なものとするため、及び外部からの電磁波をシールドする所謂電磁シールド層として機能させるために設けられている。

【0005】

また、メタライズ層12bは、半導体パッケージ内外を導出するように設けられており、この表層に外部電気回路基板と電気的に接続される、Fe−Ni−Co合金やFe−Ni合金等の金属材料から成るリード端子16が銀ロウ等のロウ材で接合される。

【0006】

このような半導体パッケージに半導体素子17を樹脂接着剤,ロウ材等の接着剤を介して接着固定するとともに、半導体素子17の電極をボンディングワイヤ(図示せず)を介して、半導体パッケージ内部のメタライズ層12bに接続し、しかる後、枠体14上面に蓋体(図示せず)を金(Au)−錫(Sn)等の低融点ロウ材で接合することにより、製品としての半導体装置となる。

【0007】

このような半導体装置は、外部電気回路基板にネジ取付部11bを介してネジ止め固定され、外部電気回路基板から供給される駆動信号により半導体素子17を作動させ、大容量の情報を高速に伝送できる装置として機能する。

【0008】

【発明が解決しようとする課題】

しかしながら、上記従来の半導体パッケージにおいて、その小型化のために枠体14のメタライズ層13とネジ取付部11bとは数mm以下と近接しており、基体11とメタライズ層13との間に形成されるフィレット(メニスカス)が非常に大きくなる場合、即ちフィレットがネジ取付部11b周辺部にまで形成された不要なロウ材溜まりと成る場合、ネジがロウ材溜まりを介してネジ取付部11bに挿通固定されることと成る。その結果、基体11上面のネジ取付部11b周辺部をネジで強固に固定できない。従って、半導体パッケージを外部電気回路基板にネジで強固に固定できないため、基体11下面が外部電気回路基板に完全に密着せず、半導体素子17の作動時に発する熱を効率良く外部電気回路基板に伝えることができない。そのため、半導体素子17は作動性が損なわれたり、熱により破損したりする等の問題点を有していた。

【0009】

上記問題点を解決する手段として、ネジ取付部11bと枠体14との間隔を大きくすることも考えられるが、この場合、半導体パッケージが大型化することとなり、近時の小型化,軽量化の動向から外れることとなる。

【0010】

従って、本発明は上記問題点に鑑み完成されたものであり、その目的は、ネジ取付部の周辺部にロウ材溜まりの発生を有効に防止することにより、半導体パッケージを外部電気回路基板に強固にネジで固定できるようにし、半導体素子の発する熱を効率良く外部電気回路基板に伝え、半導体素子を長期にわたり正常かつ安定に作動させることにある。

【0011】

【課題を解決するための手段】

本発明の半導体素子収納用パッケージは、略四角形の金属板から成り、上面に半導体素子が載置される載置部を有するとともに対向する辺部に貫通孔または上下面を貫通する切欠から成るネジ取付部が設けられた基体と、該基体の上面に前記載置部を囲繞するようにロウ付けされた、前記対向する辺部側に位置する側壁の外面にメタライズ層が形成されているとともに他の側壁に内外を導通する入出力部が設けられている絶縁体から成る枠体とを具備した半導体素子収納用パッケージにおいて、前記ネジ取付部は前記側壁の外面よりも外側に突出しており、前記メタライズ層の前記ネジ取付部に最も近接した部位に、前記基体と前記枠体との接合部から前記ネジ取付部に向かうロウ材の広がりを防ぐための非形成部が設けられていることを特徴とする。

【0012】

本発明は、このような構成により、ネジ取付部の周辺部にロウ材溜まりの発生を有効に防止でき、半導体パッケージの下面を外部電気回路基板の上面に完全に密着できる。そのため、半導体素子の発する熱を効率良く外部電気回路基板に伝えることができ、半導体素子を長期間にわたり正常かつ安定に作動させ得る。

【0013】

【発明の実施の形態】

本発明の半導体パッケージについて以下に詳細に説明する。図1は、本発明の半導体パッケージについて実施の形態の一例を示す斜視図、図2は枠体とネジ取付部の周辺部の拡大斜視図である。

【0014】

これらの図において、1は基体、4は枠体、7は半導体素子である。これら基体1,枠体4とで半導体素子7を収容するための容器が構成される。

【0015】

基体1は、略四角形の金属板から成り、Fe−Ni−Co合金やCu−W合金等の金属材料から成る。また、その上面の略中央部に半導体素子7を載置固定するための載置部1aを有するとともに、対向する辺部に外部電気回路基板にネジ止めされるネジ取付部1bを有する。ネジ取付部1bは、枠体4の側壁の外面よりも外側に突出している。

【0016】

この基体1は半導体素子7の作動時に発する熱を効率良く外部電気回路基板に伝熱する、所謂放熱板として機能するとともに、半導体素子7を支持する支持部材として、さらには外部電気回路基板に固定される固定基板として機能する。

【0017】

この基体1は、その金属材料のインゴットに圧延加工や打ち抜き加工等の従来周知の金属加工法を施すことによって所定の形状に製作される。また、基体1の表面には、耐蝕性に優れかつロウ材との濡れ性に優れる金属、具体的には厚さ0.5〜9μmのNi層と、厚さ0.5〜5μmのAu層とを順次メッキ法により被着させておくのがよい。その場合、基体1が酸化腐食するのを有効に防止できるとともに、基体1上面に半導体素子7を強固に接着固定できる。

【0018】

また、基体1はその上面に半導体素子7が載置される載置部1aを囲繞するように、1対の対向する側壁の内外の一部を切り欠いて形成された取付部2aに、この内外を導出するように形成されたメタライズ層2bを有する。また、ネジ取付部1bが設けられた基体1の対向する辺部側に位置する、一対の側壁の外面に、メタライズ層3およびその非形成部5を有する枠体4が、銀ロウ等のロウ材で接合されており、枠体4の内側に半導体素子7を収容するための空所が形成される。

【0019】

枠体4は、Al2O3セラミックスやAlNセラミックス等の絶縁材料から成り、その原料粉末に適当な有機バインダや溶剤等を添加混合しスラリーと成すとともに、このスラリーをドクターブレード法やカレンダーロール法によってセラミックグリーンシートと成し、しかる後セラミックグリーンシートに適当な打ち抜き加工を施し、これを複数枚積層し約1600℃の高温で焼成することによって作製される。

【0020】

メタライズ層2bは、半導体素子7と外部電気回路基板との電気的接続を行う手段として機能しており、その表面に、ボンディングワイヤやリード端子6との接合を容易かつ強固なものとするための、厚さ0.5〜9μmのNi層と厚さ0.5〜5μmのAu層が順次メッキ法により被着されている。そのため、半導体素子7はボンディングワイヤを介して、さらに外部電気回路基板はリード端子6を介して強固に接合され、駆動信号の伝達が良好なものとなる。

【0021】

また、メタライズ層3は、基体1上面に枠体4を銀ロウ等のロウ材で接合した際に、その接合部位にメニスカスを形成することにより接合を強固なものとするため、及び外部からの電磁波をシールドする所謂電磁シールド層として機能させるために設けられている。

【0022】

これらメタライズ層2b,3は、タングステン(W)やモリブデン(Mo)、マンガン(Mn)等で形成されており、例えば、W等の粉末に有機溶剤、溶媒を添加混合して得た金属ペーストを、枠体4用のセラミックグリーンシートに、予め従来周知のスクリーン印刷法により所定パターンに印刷塗布しておくことによって枠体4に形成される。

【0023】

また、本発明の非形成部5は、メタライズ層3のネジ取付部1bに最も近接した部位に形成され、基体1と枠体4との接合部からネジ取付部1bに向かってロウ材が広がるのを防ぐ。即ち、メタライズ層3と基体1上面により形成されるフィレットが、ロウ材過多等により非常に大きくなり不要なロウ材溜まりと成るのを有効に防止できる。その結果、半導体パッケージの下面を外部電気回路基板の上面に完全に密着させ得る。従って、半導体素子7の発する熱を効率良く外部電気回路基板に伝えることができ、半導体素子7を長期にわたり正常かつ安定に作動させ得る。

【0024】

この非形成部5は、枠体4の、ネジ取付部1bを枠体4に向かって延長させた側壁外面の部位に形成されている。また、非形成部5は、その中心部が、貫通孔または基体1の上下面を貫通する切欠から成るネジ取付部1bの先端(基体1の中心部側の端)の位置に対向するように形成されているのが好ましい。また、その1つの幅は、ネジ取付部1bの最大幅の1/5〜ネジ頭(略円板状の膨大部)の直径の2.5倍であることが好ましい。

【0025】

非形成部5の1つの幅が、ネジ取付部1bの最大幅の1/5未満の場合、ロウ材過多の際にネジ取付部1b周辺にロウ材溜まりが発生し易くなる。一方、ネジ頭の直径の2.5倍を超える場合、基体1と枠体4との接合を強固なものとするフィレットが少なくなり、それらの接合が損なわれ易くなるとともに、電磁シールド性が大きく損なわれることとなる。

【0026】

また、非形成部5の基体1上面からの高さは、0.15mm以上あることが好ましく、0.15mm未満の場合、非形成部5上面のメタライズ層3と基体1上面とでロウ材によるブリッジが発生し易くなり、このブリッジがロウ材溜まりとなり、ネジ止めした際の問題点を誘発させることとなる。

【0027】

また、非形成部5の形状は、多角形,円形,楕円形等、種々の形状とし得、多角形の場合は角部にR(円弧状部)があっても良い。また、基体1と枠体4との接合部にフィレットが形成されるのを防ぐためには、少なくとも非形成部5の下部が上記の幅(ネジ取付部1bの最大幅の1/5〜ネジ頭(略円板状の膨大部)の直径の2.5倍)を有しており、非形成部5の上部は下部よりも幅が小さくなっていてもよい。その場合、非形成部5の下部は、基体1上面からの高さが0.15mm以上あればよい。例えば、非形成部5の形状は、下部が一定の幅で上部が下部の幅よりもは狭い一定の幅を有する段状のもの、下部が一定の幅で上部が上方に向かって先細りとなったもの、下部から上部に向かって全体的に先細りとなったもの等とし得る。

【0028】

このように、非形成部5を設けることにより、ロウ材溜まりの発生を防止し、半導体パッケージと外部電気回路基板との密着を完全なものとしたり、半導体パッケージが大型化するのを回避できる。

【0029】

また、枠体4の側壁外面のメタライズ層3に非形成部5を設けることにより、従来の場合に比し、メタライズ層3の厚さをほぼ均一にすることができ、基体1と枠体4との接合を安定なものとできる。即ち、従来のように枠体4の一つの側壁の外面の全域に金属ペーストを印刷した場合、枠体4の側壁の長さに起因して金属ペーストの厚さにばらつきが生じる。具体的にはその高低差は5〜20μm程度もあるため、枠体4の側壁外面に完全に金属ペーストを印刷できない場合もある。そのため、印刷されない部位があるまま焼結しメタライズ層3と成し、基体1とロウ材で接合した場合、メタライズ層3が形成されていない面積によっては、それらの接合が不完全なものとなり、基体1と枠体4との接合を安定なものとすることができない。

【0030】

一方、非形成部5を設けることにより、金属ペーストを印刷する枠体4の側壁外面の長さが短くなるため、金属ペーストの厚さのばらつき、即ちその高低差を非常に小さくでき、ほぼ一定の厚さのメタライズ層3を形成することができる。そのため、基体1と枠体4との接合を常に安定なものとし得る。

【0031】

このような枠体4上面には、蓋体がAu−Sn等の低融点ロウ材で接合され、半導体素子7の酸化等による作動性の劣化を有効に防止し、半導体素子7を気密に封止する。

【0032】

本発明の半導体パッケージは、金属材料から成りネジ取付部1bを有する基体1上面に、半導体素子7の載置部1aを囲繞するように、対向する側壁の外面に形成されたメタライズ層3を有するとともにセラミックス等から成り他の対向する側壁の内外を導出するように形成されたメタライズ層2bを有する枠体4をロウ付けした半導体パッケージに関し、ネジ取付部1bは側壁の外面よりも外側に突出しており、メタライズ層3のネジ取付部1bに最も近接した部位に、基体1と枠体4の接合部からネジ取付部1bに向かうロウ材の広がりを防ぐための非形成部5が設けられていることを特徴としている。

【0033】

このような半導体パッケージに半導体素子7を樹脂接着剤,ロウ材等の接着剤を介して接着固定するとともに、半導体素子7の電極をボンディングワイヤを介して、半導体パッケージ内部のメタライズ層2bに接続し、しかる後、枠体4上面に蓋体をAu−Sn等の低融点ロウ材で接合することにより、製品としての半導体装置となる。

【0034】

かくして、本発明は、ネジ取付部1b周辺部にロウ材溜まりの発生を有効に防止できるため、外部電気回路基板と半導体パッケージとの密着固定を良好なものとし、半導体素子7を長期にわたり正常かつ安定に作動させ得る。

【0035】

なお、本発明は、上記実施の形態に限定されず、本発明の要旨を逸脱しない範囲内において種々の変更を行うことは何等支障無い。例えば、半導体素子7は、LD(半導体レーザ),PD(フォトダイオード)等の光信号により作動する光半導体素子であっても良く、この場合、光半導体素子を収納する容器は、光ファイバや光アイソレータ等の光学部品を実装するための光半導体パッケージとなる。

【0036】

【発明の効果】

本発明は、略四角形の金属板から成り、上面に半導体素子が載置される載置部を有するとともに対向する辺部に貫通孔または上下面を貫通する切欠から成るネジ取付部が設けられた基体と、基体の上面に載置部を囲繞するようにロウ付けされた、対向する辺部側に位置する側壁の外面にメタライズ層が形成されているとともに他の側壁に内外を導通する入出力部が設けられている絶縁体から成る枠体とを具備し、ネジ取付部は側壁の外面よりも外側に突出しており、メタライズ層のネジ取付部に最も近接した部位に、基体と枠体との接合部からネジ取付部に向かうロウ材の広がりを防ぐための非形成部が設けられていることにより、ロウ材溜まりの発生を防止し、半導体パッケージと外部電気回路基板との密着を完全なものとしたり、半導体パッケージが大型化するのを回避できる。

【図面の簡単な説明】

【図1】本発明の半導体パッケージについて実施の形態の一例を示す斜視図である。

【図2】図1の枠体とネジ取付部の周辺部の拡大斜視図である。

【図3】従来の半導体パッケージの斜視図である。

【符号の説明】

1:基体

1a:載置部

1b:ネジ取付部

2b:メタライズ層

3:メタライズ層

4:枠体

5:非形成部

7:半導体素子

Claims (1)

- 略四角形の金属板から成り、上面に半導体素子が載置される載置部を有するとともに対向する辺部に貫通孔または上下面を貫通する切欠から成るネジ取付部が設けられた基体と、該基体の上面に前記載置部を囲繞するようにロウ付けされた、前記対向する辺部側に位置する側壁の外面にメタライズ層が形成されているとともに他の側壁に内外を導通する入出力部が設けられている絶縁体から成る枠体とを具備した半導体素子収納用パッケージにおいて、前記ネジ取付部は前記側壁の外面よりも外側に突出しており、前記メタライズ層の前記ネジ取付部に最も近接した部位に、前記基体と前記枠体との接合部から前記ネジ取付部に向かうロウ材の広がりを防ぐための非形成部が設けられていることを特徴とする半導体素子収納用パッケージ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001022707A JP3652257B2 (ja) | 2001-01-31 | 2001-01-31 | 半導体素子収納用パッケージ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001022707A JP3652257B2 (ja) | 2001-01-31 | 2001-01-31 | 半導体素子収納用パッケージ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002231842A JP2002231842A (ja) | 2002-08-16 |

| JP3652257B2 true JP3652257B2 (ja) | 2005-05-25 |

Family

ID=18888081

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001022707A Expired - Fee Related JP3652257B2 (ja) | 2001-01-31 | 2001-01-31 | 半導体素子収納用パッケージ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3652257B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4783272B2 (ja) * | 2006-12-01 | 2011-09-28 | 株式会社東芝 | 半導体パッケージ |

-

2001

- 2001-01-31 JP JP2001022707A patent/JP3652257B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002231842A (ja) | 2002-08-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4903738B2 (ja) | 電子部品収納用パッケージおよび電子装置 | |

| JP2012064785A (ja) | 素子収納用パッケージ、およびこれを備えた電子装置 | |

| JP3652257B2 (ja) | 半導体素子収納用パッケージ | |

| JP6082114B2 (ja) | 素子収納用パッケージおよび実装構造体 | |

| JP4969490B2 (ja) | 基板保持部材及びパッケージ、並びに電子装置 | |

| JP3652255B2 (ja) | 半導体素子収納用パッケージ | |

| JP4009169B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JP4373831B2 (ja) | 電子部品収納用パッケージおよび電子装置 | |

| JP4594073B2 (ja) | 接続端子ならびにこれを用いた電子部品収納用パッケージおよび電子装置 | |

| JP3619452B2 (ja) | 半導体素子収納用パッケージ | |

| JP3615697B2 (ja) | 半導体素子収納用パッケージ | |

| JP3642739B2 (ja) | 半導体素子収納用パッケージ | |

| JP2004228532A (ja) | 入出力端子および半導体素子収納用パッケージならびに半導体装置 | |

| JP3762261B2 (ja) | 光半導体素子収納用パッケージおよび光半導体装置 | |

| JP4206321B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JP3164802B1 (ja) | 電子部品収納用パッケージ | |

| JP3527902B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JPH06334077A (ja) | 半導体素子収納用パッケージ | |

| JP5725900B2 (ja) | 半導体素子収納用パッケージ、およびこれを備えた半導体装置 | |

| JP2006128267A (ja) | 入出力端子ならびにこれを用いた電子部品収納用パッケージおよび電子装置 | |

| JP4041327B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JP3420476B2 (ja) | 半導体素子収納用パッケージ | |

| JP4057883B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JP2003338572A (ja) | 入出力端子および半導体素子収納用パッケージならびに半導体装置 | |

| JP4164011B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040825 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050222 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090304 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090304 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100304 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110304 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110304 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120304 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120304 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130304 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130304 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140304 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |