JP3634918B2 - 埋設ストラップを有する半導体デバイス及びその製造方法 - Google Patents

埋設ストラップを有する半導体デバイス及びその製造方法 Download PDFInfo

- Publication number

- JP3634918B2 JP3634918B2 JP08629796A JP8629796A JP3634918B2 JP 3634918 B2 JP3634918 B2 JP 3634918B2 JP 08629796 A JP08629796 A JP 08629796A JP 8629796 A JP8629796 A JP 8629796A JP 3634918 B2 JP3634918 B2 JP 3634918B2

- Authority

- JP

- Japan

- Prior art keywords

- trench

- semiconductor

- semiconductor device

- layer

- buried strap

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/038—Making the capacitor or connections thereto the capacitor being in a trench in the substrate

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

- Element Separation (AREA)

Description

【発明の属する技術分野】

本発明は、埋設ストラップを有するトレンチ・キャパシタ構造を備える半導体デバイスに関する。より詳細には、第1段位置合せ埋設ストラップを有するトレンチ・キャパシタ構造を備える半導体デバイスを製作する方法に関する。

【0002】

【従来の技術】

集積回路が広く使用され、その応用範囲が広いため、様々な半導体メモリが開発されてきた。こうした半導体メモリ・デバイスは、絶えず新しくより広い用途に使用されつつあり、そのため能力がより高くコストのより安い集積回路が必要とされている。したがって、メモリ容量が増大しチップ・サイズが縮小した安価な半導体デバイスが絶えず求められている。このような改良は、デバイスの小型化と半導体メモリ・デバイスのレイアウト及び設計の改善として実現されてきた。

【0003】

従来技術によるデバイスの多くは、トレンチ・キャパシタと、トレンチ・キャパシタと突合せとなる能動半導体領域の縁部との間での、電気妨害(すなわち隣接するメモリ・セルのチャネル領域からの漏れによる妨害)及び寄生デバイス形成を防止する手段として、陥凹酸化物(ROX)分離トレンチを使って隣接するトレンチ・キャパシタ・セルを分離している。したがって、ROX分離トレンチを組み込んだ設計または構造を利用する場合、2つの構成部品間での電気妨害及び寄生デバイス形成を避けるために隣接するメモリ・セルのメモリ・セル・キャパシタとゲート電極の間で維持しなければならない最小間隔(ROXトレンチの長さ)がある。しかし、ROX分離トレンチが占める半導体基板上の面積はかなりの大きさである。したがって、ROX分離トレンチの使用を避けるまたは最小限に抑えるように半導体デバイスを設計すると、メモリ・アレイをより高密度に充填することが可能になり、好ましい。

【0004】

さらに、DRAMセルなど多くのメモリ・デバイスは、キャパシタ構造中に蓄積された電荷でビットを表す動的メモリ・セルを利用している。DRAMセルでは、コンデンサ構造はFETの記憶ノードと結合していなければならない。しかし、既に既存の半導体デバイスが高密度で存在するため、表面ストラップに利用できる余地は余りない。その上、デバイス密度が高くフィーチャ・サイズが最小になっているため、加工シーケンスが、絶えず範囲が増大する構造及び材料に適合する必要がある。たとえば、接点は一般に、接点を設けるべき領域の上の不動態層中に接点孔をエッチングし、続いてその中に導電材料を付着させて形成する。しかし、半導体デバイスのトポロジのために、接点孔を形成するとしばしばゲート導体(ワード線)などの他の表面構造や不動態層自体に損傷を与えることになる。したがって、半導体デバイスの様々な領域を接触させるために埋設ストラップを設けることがしばしば好ましい。第一に、ストラップが埋設されているため、半導体デバイスの表面に残るスペースが多くなり、したがってさらに高いデバイス密度の実現も容易になる。第二に、ストラップ接点は集積プロセスの最初に(すなわち多数の構造の形成前に)形成されるため、他の表面構造に対する潜在的損傷がなくなる。

【0005】

より少数の加工シーケンスを使用すると同時により大きな記憶容量を与え、より高密度に充填したメモリ・アレイが可能な、半導体メモリ・デバイスの設計及び方法が絶えず求められている。さらに、共にトレンチ・キャパシタ構造と位置合せされた、埋設ストラップ及び分離構造を有するトレンチ・キャパシタ構造が求められている。

【0006】

【発明が解決しようとする課題】

本願の目的は、第1レベルの位置合せされた分離構造とトレンチ内からドープされた半導体基板中に延びる埋設ストラップとを有するトレンチ・キャパシタ構造を備える半導体デバイス及びその製造方法を提供することである。

【0007】

【課題を解決するための手段】

一態様において、本発明は、

半導体基板と、

前記基板中に延びる第1のトレンチと、

前記トレンチに隣接するドープされた領域と、

前記ドープ領域中に延び、前記第1トレンチと部分的に交差する第2のトレンチとを備え、

前記第1トレンチが、その中に導電材料が位置する第1の絶縁部分を有し、前記第2トレンチが、前記第1トレンチ内の前記導電材料と前記ドープ領域とに隣接する第1の導電部分を有し、前記第2トレンチがまた、前記第2トレンチを少なくとも部分的に充填し、かつ前記第2トレンチの前記第1導電部分の上にそれに隣接して位置する第2の絶縁部分をも有する、

埋設ストラップを有する半導体デバイスを製造する方法に関する。

【0008】

別の態様において、本発明は、

半導体基板中に、導電材料がその中に位置する絶縁層を有する第1のトレンチを形成するステップと、

前記第1トレンチ内に、前記半導体基板中に延びる第2のトレンチを形成するステップと、

前記第2トレンチ内に、半導体基板の表面より下に導電材料の層を形成するステップと、

前記第2トレンチ内の導電材料の、前記第1トレンチ及び前記半導体基板の上に延びて埋設ストラップを画定する連続部分を覆って保護層を付着するステップと、

前記第2トレンチの露出部分を前記埋設ストラップより下まで陥没させるステップと、

前記保護層を除去するステップと、

前記第2トレンチ内に絶縁領域を形成するステップと、

前記第1トレンチ内の導電材料を覆って絶縁層を形成するステップと

を含む、埋設ステップを有する半導体デバイスを製造する方法に関する。

【0009】

別の態様では、この方法はさらに、前記第1トレンチを形成する前にシリコン基板を覆う導電材料を形成するステップを含むことができる。本発明の別の態様では、この方法はさらに、第1トレンチが上部と下部を有する内壁によって画定され、かつ前記トレンチ内部に絶縁層を形成するステップが、

前記内壁の底部に薄い絶縁層を形成するステップと、

前記内壁の頂部に厚い絶縁層を形成するステップとを含むことを特徴とすることができる。

【0010】

【発明の実施の形態】

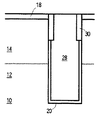

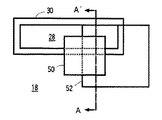

本発明の半導体メモリ・デバイスは、その一実施形態を図1及び図2に示すが、p+基板領域12の上方に形成したNウェル14を有する複合半導体基板10中に形成することができる。この半導体メモリ・デバイスのトレンチ・キャパシタは、導電材料の充填物28と薄い絶縁層26と側壁で画定された厚い絶縁層30とを有する深いトレンチ20を備える。埋設トラップを形成する導電材料の連続層42は、深いトレンチ20内から半導体基板10の能動領域中へと延びて、トレンチ・キャパシタの導電性充填物28をFETの記憶ノードと結合する。第2の絶縁層54が、深いトレンチ内の導電材料充填物28の上と埋設トラップ42の頂面及び少なくとも一側面の上に延びる。

【0011】

本明細書の全体を通して、本発明の説明及び図がはっきりするように、本発明の様々な態様を簡略化して概略的に示してあることに留意されたい。たとえば、本願におけるトレンチ構成の平面図及び垂直断面図は、幾何学的な形状、特に正方形として図示してある。しかし、当業者なら理解するであろうが、実際の半導体方法では、トレンチの実際の形成にはより丸まったフィーチャを組み込むのが普通である。また、本発明の範囲は特定の形状の構成に限定されるものではない。

【0012】

図3ないし図9を見るとわかるように、本発明の半導体メモリ・デバイスの製作中に作成される中間構造を示す図が示してある。p+基板12上にNウェル14が形成されている複合半導体基板などの半導体基板10が図3に示してある。当業者なら理解するであろうが、ドープ領域の位置と形状は半導体デバイスの具体的設計によって変わり、代替設計も本発明に含合されるものである。次に、半導体基板の表面を共形に覆って表面誘電層18を形成することができる。この誘電層は既知の複数の方法の任意の一つ、たとえば酸化成長または化学的気相付着によって形成することができる。半導体基板を覆う薄い表面誘電層は、単一の薄い絶縁層として概略的に示してある。しかし、好ましい実施形態では、この絶縁層は酸化シリコン層と窒化シリコン層など、誘電材料の複合体を含む。より好ましくは、第1の酸化シリコン層が約100Åで、酸化物の上の窒化シリコンの第2の層が約1000Åである。

【0013】

表面誘電層18の頂面にマスキング酸化物層(図示せず)を形成し、パターン化して、半導体基板内まで深いトレンチ20が形成されるようにすることができる。この深いトレンチは、当技術分野で周知の方法、たとえば反応性イオン・エッチング(RIE)によって形成することができる。やはり図3を参照するとわかるが、トレンチ20は、底壁と、側壁上部及び側壁下部を有する側壁とによって画定することができる。側壁上部は厚い絶縁層30を有し、側壁下部は薄い絶縁層26を有することが好ましい。好ましい実施例では、側壁上部は側壁の約10〜20%を占め、側壁下部は側壁の下側80〜90%を占める。ただし、これらのパーセントは例示にすぎず、他の側壁構成でも本発明は有用であることに留意されたい。

【0014】

深いトレンチ20を形成した後、当技術で周知の方法、たとえば熱酸化物成長または化学的気相付着によって、トレンチ側壁に沿って薄い絶縁層26を形成することができる。この薄い絶縁層は厚さ5〜10nmとすることが好ましい。この絶縁層は、一般の絶縁材料、たとえば酸化シリコン、窒化シリコン、好ましくはこの組合せから構成することができる。次に深いトレンチ20を導電材料28、たとえばホウ素でドープしたポリシリコンなどp+ドープ・ポリシリコンで充填することができる。これにより、トレンチ・キャパシタ構造中での電荷の蓄積が容易になる。

【0015】

その後、深いトレンチ20から導電材料28の一部分を除去して、トレンチ側壁の上部を露出させることができる。除去の終了する点がトレンチ側壁の上部と下部を画定する。好ましい実施例では、ポリシリコン充填物はトレンチの下部80%に残ることになる。導電性充填物28の一部分を除去し、トレンチ側壁の上部を露出させた後、トレンチ側壁上部に沿って厚い分離層30を形成することができる。これらの厚い分離層は、化学的気相付着、熱酸化物成長、あるいは絶縁材料の共形層を側壁に付着できるその他の手段によって形成することができる。異方性エッチング(たとえばRIE)を施して、トレンチの側壁上に形成された部分は除去せずに酸化物の一部分を除去することができる。この厚い分離層は、前記で論じた薄い絶縁層で利用するものと同様の通常の誘電体を含むことができる。好ましい実施形態では、トレンチ側壁上部に沿って形成された薄い分離層は厚さ約50〜100nmである。しかし、陥凹領域52の深さ(図9参照)が後述の寄生デバイスの形成を妨げるのに十分な深いものである場合は、厚い分離層及びそれを形成するプロセスを省略することができる。

【0016】

その後、ホウ素でドープしたポリシリコンなどの導電性充填材料28の第2の付着物を、新しく形成した厚い分離層30に隣接するトレンチ上部に付着することができる。その後、新しく付着した導電性充填物28を平面化して、表面誘電体と平行な平面を形成することができ、これは化学機械式研磨やRIEなど当技術分野で周知の手段によって実施することができる。得られた構造の断面は図3に示す通りである。

【0017】

フォトリソグラフィ・マスク(図示せず)を塗布し、露光し、現像して、深いトレンチ20とそれに隣接する半導体領域10との一部分の上に連続する領域を露出させることができる。この露出領域をRIE(反応性イオン・エッチング)などでエッチ・バックして、図4及び図5に示すような浅いトレンチ40を形成することができる。この分離トレンチの作成に使用する好ましいエッチング剤は、酸化シリコンとシリコンを非選択的にエッチングする、CF4/O2を使用するものである。浅いトレンチ40は、側壁の頂部約5〜10%の深さまで延び、Nウェル領域14や厚い分離層30の下には延びないことが好ましい。浅いトレンチ40内に未ドーブのポリシリコン42を付着して平面化した後、フォトリソグラフィ・マスク(図示せず)を除去する。このマスクはポリシリコンの付着温度には耐えられないので、ボリシリコンの付着前に除去することが好ましい。

【0018】

次いで導電材料42、たとえば未ドープのポリシリコンを浅いトレンチ40内に付着し平面化して、過剰の未ドープのポリシリコンを除去し、誘電層と平行な表面を形成することができる。得られる構造を図6に示す。図7を参照すると、次いで深いトレンチ20のドープしたポリシリコン28と浅いトレンチ40の未ドープのポリシリコン42を半導体基板10の表面より下まで陥没させて、浅いトレンチ40の下部に未ドープのポリシリコンの連続層42を残すことができる。深いトレンチ中のドープしたポリシリコンと浅いトレンチ中の未ドープのポリシリコンは、未ドープのポリシリコンの層が約100nmの厚さで残る深さまでエッチ・バックすることが好ましい。さらに、ドープした半導体領域14からドーパントを加熱すると、基板または深いトレンチの導電性充填物28あるいはその両方がストラップ42中に拡散して、それを導電性にすることに留意されたい。

【0019】

露出したシリコン材料を陥没させるのに利用するプロセスは、シリコンを表面誘電層18に対して選択的に陥没させるプロセスで実施することが好ましい。このような選択的プロセスには、シリコン(ドープ済みのものも未ドープのものも)を表面誘電層に対して選択的にエッチングする、エッチング剤を使用するのが含まれる。なお表面誘電層18はエッチ・ストップとして働くことになる。たとえば、薄い表面誘電層が薄い酸化シリコン層を覆う厚い窒化シリコン層を含むときは、窒化物に対するポリシリコンの選択的エッチングを使用することができる。このようなエッチングは当技術分野で周知であり、その一例は、グエン(Nguyen)等の論文”Substrate Trenching Mechanism During Plasma and Magnetically Enhanced Polysilicon Etching”,Journal of Eletrochenical Society,Vol. 138, No.4, pp.1112−1117(1991年4月)に記載されており、その内容を参照により本明細書に組み込む。ポリシリコンを表面誘電層に対して選択的にエッチングするエッチング剤を使用する場合でも、この手順中に、表面誘電層の一部分が消費されることを理解されたい。したがって、特定のエッチングまたはその他の選択的プロセスの選択性に応じて、消費される表面誘電層の量が変化する。表面誘電層所望の厚さもそれに応じて変化する。表面誘電層の厚さは、加工によってその厚さが、下の半導体基板及びその中の電子素子がエッチングまたは損傷する程度まで減少しないような厚さとすべきである。厚さ約100〜150nmの表面誘電層を利用すると、一般に表面誘電層がその下の領域への望ましくないエッチングや損傷を防止するという受け入れ可能な保証を与える。

【0020】

図8及び図9に示すように、半導体デバイスを覆ってレジスト50を塗布し、露出し、現像して、浅いトレンチ40に対するレジスト50の部分を残し、導電材料42上のレジスト50が半導体基板10と薄い分離層30と深いトレンチ20の導電性充填物28とを覆って延びるようにすることができる。レジスト50はまた浅いトレンチ40で画定される領域の外側の深いトレンチ20と表面誘電層18の限られた部分を覆って延びることができる。次いで深いトレンチ20と浅いトレンチ40のマスクされず露出しているポリシリコン領域を陥没させる。この場合も、ポリシリコンを表面誘電層18に対して選択的にエッチングすることが好ましい。露出したポリシリコン領域を、浅いトレンチ40の元の深さより下の深さまで陥没させて、開いた陥凹領域52を形成する。ただし陥凹領域52をトレンチ40の元の深さより約200nm以上下の、寄生デバイスの形成を防止するのに十分な深さにする場合は、前記で論じたように元の深さ中に厚い酸化物カラーを設ける必要はない。

【0021】

その後、図1及び図2に示すように、開いた陥凹領域52を絶縁材料で充填して、第2の絶縁層54を形成することができる。適切な絶縁材料の例としては、それだけに限られるものではないが、酸化シリコン、及び酸化シリコンと窒化シリコンの組合せがある。好ましい絶縁体は、化学的気相付着によってTEOS(テトラエトキシシラン)を付着することにより形成することができる。その後、N2雰囲気中での熱高密度化などによって酸化物を高密度化することができる。シリコン構造が耐えられる応力に応じて酸化性雰囲気が好ましいこともある。その後、当技術分野で周知の手段によって絶縁材料を平面化して、この追加の絶縁体が表面誘電層と平行な平面を形成するようにすることができる。浅いトレンチ40内に残った未ドープのポリシリコン42が、トレンチ・キャパシタの導電性充填物及びFETの記憶ノードと接触する埋設ストラップを形成する。

【0022】

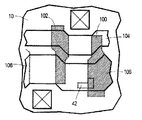

図10に示すように、本発明のトレンチ・キャパシタ・セルを利用すると、アレイ・レイアウトで多くのROX領域を省略することが可能になる。キャパシタ100、102は図10に示すように、ワード線104、106の方向と直角になる2つの端部(例えば、「第1の端部」、「第2の端部」と呼ぶとする。)に確定される長手形状に構成することができる。このとき、トレンチの間隔は、ROX分離トレンチは不要なためソース拡散領域のスペースの関数となる。その結果、トレンチ・キャパシタ100と102のそれぞれを、隣接するメモリ・セルの能動半導体領域と突合せて配置することができる。埋設ストラップは、トレンチ・キャパシタ100からトランジスタの能動半導体領域(例えば、記憶ノード)に延びることができる。また、キャパシタ・セル100のトランジスタの能動半導体領域を、能動ワード線104の下に配置することができ、この能動半導体領域の配置は、埋設トラップ42を収容するトレンチ100の端部(第2の端部)の側とは反対の端部(第1の端部)の側である。他方、ワード線106は、トレンチ100の能動ワード線104の側とは反対の端部(第2の端部)の側にある埋設ストラップの上を延びることができる。

【0023】

本発明の上記の諸実施形態の結果、深いトレンチ側壁内で構造が形成され第1レベルが位置合せされた、半導体トレンチ・コンデンサ・セルが提供される。これらの製造プロセスの許容差は、本マスク1個分すなわち浅いトレンチを画定するのに使用されるマスクまでに限定されている。残りの構造は浅いトレンチの壁と自己位置合せされる。深いトレンチによって利用される領域内をFETの記憶ノード中まで延びる埋設ストラップが形成される。このストラップが必要とする絶縁も回線に配置されて画定され、したがってより高密度に充填できるメモリ・アレイの構築が可能になる。トレンチ側壁と位置合せされた第1レベルである本発明の分離構造を構成することにより、従来、トレンチ・キャパシタ専用に使用されていた隣接するメモリ・セルの能動半導体領域からの余分のチップ・スペースがもはや不要となる。

【0024】

以上、本発明をその好ましい実施形態に関して詳細に開示し説明してきたが、本発明の趣旨及び範囲から逸脱することなく、その形状及び細部に他の変更を加えることができることを当業者なら理解されよう。

【0025】

まとめとして、本発明の構成に関して以下の事項を開示する。

【0026】

(1)半導体基板中に第1のトレンチを有し、該第1のトレンチが導電材料をその中に位置する絶縁領域を有するように形成するステップと、

前記第1トレンチ内に、前記半導体基板中に延びる第2のトレンチを形成するステップと、

前記第2トレンチ内に、半導体基板の表面より下に導電材料の層を形成するステップと、

前記第2トレンチ内の導電材料の、前記第1トレンチ及び前記半導体基板の上に延びて埋設ストラップを画定する連続部分を覆って保護層を付着するステップと、

前記第2トレンチの露出部分を前記埋設ストラップより下まで陥没させるステップと、

前記保護層を除去するステップと、

前記第2トレンチ内に絶縁領域を形成するステップと、

前記第1トレンチ内の導電材料を覆って絶縁層を形成するステップと

を含む、埋設ストラップを有する半導体デバイスを製造する方法。

(2)前記第1トレンチを形成する前に、前記半導体基板を覆って誘電層を形成するステップをさらに含む、上記(1)に記載の方法。

(3)まず前記半導体基板を覆って酸化シリコンの層を形成し、次いで前記酸化シリコンを覆って窒化シリコンの層を形成することによって前記誘電層を形成することを特徴とする、上記(2)に記載の方法。

(4)前記絶縁材料が酸化シリコンを含み、前記方法がさらに前記絶縁層の形成後に前記絶縁材料を高密度化するステップを含むことを特徴とする、上記(1)に記載の方法。

(5)前記第1トレンチが上部と下部を有する内壁によって画定され、絶縁層と整列した第1トレンチを形成するステップが、

前記内壁の下部に薄い絶縁層を形成するステップと、

前記内壁の上部に厚い絶縁層を形成するステップと

を含むことを特徴とする、上記(1)に記載の方法。

(6)前記第1トレンチ中に付着される前記導電材料がp+ドープしたポリシリコンを含むことを特徴とする、上記(1)に記載の方法。

(7)前記第2トレンチ中に付着される前記導電材料が未ドープのポリシリコンを含むことを特徴とする、上記(6)に記載の方法。

(8)前記保護層を除去する前に前記第1トレンチ内の導電材料を陥没させることを特徴とする、上記(5)に記載の方法。

(9)前記第2トレンチ内の前記半導体基板表面より下に導電材料の層を形成するステップが、

前記第2トレンチ内に導電材料を付着するステップと、

前記第2トレンチ内の前記半導体基板表面より下の導電材料を陥没させるステップとを含むことを特徴とする、上記(2)に記載の方法。

(10)前記第1トレンチ内の導電材料を前記半導体基板の表面より下まで陥没させるステップをさらに含む、上記(9)に記載の方法。

(11)前記第2トレンチ内の導電材料を陥没させる前記ステップと、前記第1トレンチ内の導電材料を陥没させる前記ステップが、前記導電材料を前記導電層に対して選択的にエッチングするエッチング剤を使用することによって同時に実施されることを特徴とする、上記(10)に記載の方法。

(12)前記第2トレンチ内に前記絶縁領域を形成するステップと、前記第1トレンチを覆って絶縁層を形成するステップが、前記第1トレンチ及び前記第2トレンチの前記陥凹部分内に絶縁材料を同時に付着するステップを含むことを特徴とする、上記(10)に記載の方法。

(13)半導体基板と、

前記基板中に延びる第1のトレンチと、

前記トレンチに隣接するドープされた領域と、

前記ドープ領域中に延び、前記第1トレンチと部分的に交差する第2のトレンチとを備え、

前記第1トレンチが、その中に導電材料が位置する第1の絶縁部分を有し、前記第2トレンチが、前記第1トレンチ内の前記導電材料と前記ドープ領域とに隣接する第1の導電部分を有し、前記第2トレンチがまた、前記第2トレンチを少なくとも部分的に充填し、かつ前記第2トレンチの前記第1導電部分の上にそれに隣接して位置する第2の絶縁部分をも有する

半導体デバイス。

(14)前記第2トレンチが底部を有し、前記ストラップが前記第2トレンチの底部と接触していることを特徴とする、上記(13)に記載の半導体構造。

(15)前記埋設ストラップの周囲に隣接する第2トレンチの一部分がストラップより下に延びることを特徴とする、上記(14)に記載の半導体構造。

(16)前記埋設ストラップを覆う前記絶縁層が、前記第1トレンチ導電材料の上を延びることを特徴とする、上記(13)に記載の半導体構造。

(17)前記半導体基板の表面を覆う導電層をさらに備える、上記(13)に記載の半導体構造。

(18)前記導電層が酸化シリコンの層を覆う窒化シリコンの層を含むことを特徴とする、上記(17)に記載の半導体構造。

(19)トランジスタが、第1トレンチに隣接し、前記埋設ストラップと対向する位置にあることを特徴とする、上記(13)に記載の半導体構造。

(20)電子デバイスの能動半導体チャネルが前記第1トレンチに隣接していることを特徴とする、上記(18)に記載の半導体構造。

【図面の簡単な説明】

【図1】陰影付きで示した埋設ストラップを備えた本発明のトレンチ・キャパシタ・セルの平面図である。

【図2】図1のトレンチ・キャパシタ・セルのA−A’で切断した断面図である。

【図3】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造のA−A’で切断した断面図である。

【図4】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造の図5に対応する平面図である。

【図5】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造のA−A’で切断した断面図である。

【図6】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造のA−A’で切断した断面図である。

【図7】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造のA−A’で切断した断面図である。

【図8】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造の図9に対応する平面図である。

【図9】図1及び図2に示したトレンチ・キャパシタ・セルを製造する際に作成される構造のA−A’で切断した断面図である。

【図10】本発明のトレンチ・キャパシタ・セルを組み込んだメモリ・アレイ設計を示す、半導体デバイスの部分平面図である。

【符号の説明】

10 複合半導体基板

12 p+基板領域

14 Nウェル

18 表面誘電層

20 深いトレンチ

26 浅い絶縁層

28 導電性充填物

30 厚い分離層

40 浅いトレンチ

42 埋設トラップ

50 レジスト

52 陥凹領域

54 第2分離層

Claims (7)

- 半導体基板と、

上部トレンチ・レベルから前記基板中に延びる第1のトレンチと、

前記上部トレンチ・レベルの下に、前記第1のトレンチに隣接して配置されたドープ領域と、

前記半導体基板の前記ドープ領域中から延びて、前記第1トレンチの一部分と重なる第2のトレンチとを備え、

前記第1トレンチは、その中に導電材料が位置する第1の絶縁部分を有し、

前記第2トレンチは、前記第1のトレンチ内の前記導電材料と前記ドープ領域とに隣接する埋設ストラップと、前記第2トレンチを少なくとも部分的に充填する第2の絶縁部分とを有し、

前記第2の絶縁部分は、前記埋設ストラップ部分の上及びそれに隣接して配置され、

前記第1のトレンチは、該トレンチのトランジスタを駆動する能動ワード線の方向と直角になる2つの端部(第1及び第2の端部)に画定される長手形状に構成され、

前記能動ワード線は、前記第1のトレンチの第1の端部の側に延びて配置され、

前記トランジスタの能動半導体領域は、第1の端部の側に配置されて前記能動ワード線の下に位置づけられ、

前記埋設ストラップは、第1のトレンチの第2の端部の側に位置づけられ、前記能動半導体領域の記憶ノードまで延びること、

を特徴とする半導体デバイス。 - 前記第2トレンチが底部を有し、前記埋設ストラップが前記第2トレンチの底部と接触していることを特徴とする、請求項1に記載の半導体デバイス。

- 前記第2の絶縁部分が、前記埋設ストラップより下に延びることを特徴とする、請求項2に記載の半導体デバイス。

- 前記第2の絶縁部分が、前記第1トレンチの導電材料の上を延び、前記埋設ストラップの底部を除く全てを覆うことを特徴とする、請求項1に記載の半導体デバイス。

- 前記半導体基板の上部表面を覆う絶縁層をさらに備える、請求項1に記載の半導体デバイス。

- 前記絶縁層が酸化シリコンの層を覆う窒化シリコンの層を含むことを特徴とする、請求項5に記載の半導体デバイス。

- 前記トランジスタの能動半導体チャネルが、前記第1トレンチに隣接していることを特徴とする、請求項6に記載の半導体デバイス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/421,714 US5576566A (en) | 1995-04-13 | 1995-04-13 | Semiconductor trench capacitor cell having a buried strap |

| US421714 | 1995-04-13 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH08288474A JPH08288474A (ja) | 1996-11-01 |

| JP3634918B2 true JP3634918B2 (ja) | 2005-03-30 |

Family

ID=23671727

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP08629796A Expired - Fee Related JP3634918B2 (ja) | 1995-04-13 | 1996-04-09 | 埋設ストラップを有する半導体デバイス及びその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US5576566A (ja) |

| EP (1) | EP0738006A3 (ja) |

| JP (1) | JP3634918B2 (ja) |

| KR (1) | KR100193975B1 (ja) |

| TW (1) | TW311239B (ja) |

Families Citing this family (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5545583A (en) * | 1995-04-13 | 1996-08-13 | International Business Machines Corporation | Method of making semiconductor trench capacitor cell having a buried strap |

| US5827765A (en) * | 1996-02-22 | 1998-10-27 | Siemens Aktiengesellschaft | Buried-strap formation in a dram trench capacitor |

| US5953607A (en) * | 1997-06-06 | 1999-09-14 | International Business Machines Corporation | Buried strap for trench storage capacitors in dram trench cells |

| US6100131A (en) * | 1997-06-11 | 2000-08-08 | Siemens Aktiengesellschaft | Method of fabricating a random access memory cell |

| US6236079B1 (en) | 1997-12-02 | 2001-05-22 | Kabushiki Kaisha Toshiba | Dynamic semiconductor memory device having a trench capacitor |

| US6190988B1 (en) | 1998-05-28 | 2001-02-20 | International Business Machines Corporation | Method for a controlled bottle trench for a dram storage node |

| US5981350A (en) * | 1998-05-29 | 1999-11-09 | Micron Technology, Inc. | Method for forming high capacitance memory cells |

| US6074909A (en) * | 1998-07-31 | 2000-06-13 | Siemens Aktiengesellschaft | Apparatus and method for forming controlled deep trench top isolation layers |

| US6110792A (en) * | 1998-08-19 | 2000-08-29 | International Business Machines Corporation | Method for making DRAM capacitor strap |

| US6222218B1 (en) | 1998-09-14 | 2001-04-24 | International Business Machines Corporation | DRAM trench |

| US6194736B1 (en) | 1998-12-17 | 2001-02-27 | International Business Machines Corporation | Quantum conductive recrystallization barrier layers |

| US6297086B1 (en) | 1999-03-11 | 2001-10-02 | International Business Machines Corporation | Application of excimer laser anneal to DRAM processing |

| US6211544B1 (en) * | 1999-03-18 | 2001-04-03 | Infineon Technologies North America Corp. | Memory cell layout for reduced interaction between storage nodes and transistors |

| US6259129B1 (en) | 1999-04-20 | 2001-07-10 | International Business Machines Corporation | Strap with intrinsically conductive barrier |

| US6236077B1 (en) | 1999-04-20 | 2001-05-22 | International Business Machines Corporation | Trench electrode with intermediate conductive barrier layer |

| US6242357B1 (en) * | 1999-05-06 | 2001-06-05 | Mosel Vitelic Inc. | Method for forming a deep trench capacitor of a DRAM cell |

| TW425674B (en) * | 1999-05-07 | 2001-03-11 | Mosel Vitelic Inc | Fabrication method for trench capacitor with sacrificial silicon nitride sidewall |

| US6229173B1 (en) | 1999-06-23 | 2001-05-08 | International Business Machines Corporation | Hybrid 5F2 cell layout for buried surface strap aligned to vertical transistor |

| US6380575B1 (en) | 1999-08-31 | 2002-04-30 | International Business Machines Corporation | DRAM trench cell |

| US6310359B1 (en) * | 2000-04-26 | 2001-10-30 | International Business Machines Corporation | Structures containing quantum conductive barrier layers |

| US6303413B1 (en) * | 2000-05-03 | 2001-10-16 | Maxim Integrated Products, Inc. | Method of forming a shallow and deep trench isolation (SDTI) suitable for silicon on insulator (SOI) substrates |

| US6479394B1 (en) | 2000-05-03 | 2002-11-12 | Maxim Integrated Products, Inc. | Method of low-selective etching of dissimilar materials having interfaces at non-perpendicular angles to the etch propagation direction |

| DE10027913A1 (de) | 2000-05-31 | 2001-12-13 | Infineon Technologies Ag | Speicherzelle mit einem Grabenkondensator |

| US6376324B1 (en) | 2000-06-23 | 2002-04-23 | International Business Machines Corporation | Collar process for reduced deep trench edge bias |

| US6369419B1 (en) | 2000-06-23 | 2002-04-09 | International Business Machines Corporation | Self-aligned near surface strap for high density trench DRAMS |

| US6503798B1 (en) | 2000-06-30 | 2003-01-07 | International Business Machines Corporation | Low resistance strap for high density trench DRAMS |

| EP1265278A1 (en) * | 2001-06-06 | 2002-12-11 | Infineon Technologies AG | Method for manufacturing a trench capacitor with an isolation trench |

| DE10131709B4 (de) | 2001-06-29 | 2006-10-26 | Infineon Technologies Ag | Verfahren zur Herstellung einseitiger Buried-Straps |

| JP4592270B2 (ja) * | 2003-10-06 | 2010-12-01 | 日東電工株式会社 | 半導体ウエハの支持材からの剥離方法およびこれを用いた装置 |

| US7122437B2 (en) * | 2003-12-19 | 2006-10-17 | Infineon Technologies Ag | Deep trench capacitor with buried plate electrode and isolation collar |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4801988A (en) * | 1986-10-31 | 1989-01-31 | International Business Machines Corporation | Semiconductor trench capacitor cell with merged isolation and node trench construction |

| US4918502A (en) * | 1986-11-28 | 1990-04-17 | Hitachi, Ltd. | Semiconductor memory having trench capacitor formed with sheath electrode |

| US4939567A (en) * | 1987-12-21 | 1990-07-03 | Ibm Corporation | Trench interconnect for CMOS diffusion regions |

| JPH01192164A (ja) * | 1988-01-28 | 1989-08-02 | Fujitsu Ltd | 半導体装置とその製造方法 |

| US4965217A (en) * | 1989-04-13 | 1990-10-23 | International Business Machines Corporation | Method of making a lateral transistor |

| KR920004368B1 (ko) * | 1989-09-04 | 1992-06-04 | 재단법인 한국전자통신연구소 | 분리병합형 홈의 구조를 갖는 d램셀과 그 제조방법 |

| US5034787A (en) * | 1990-06-28 | 1991-07-23 | International Business Machines Corporation | Structure and fabrication method for a double trench memory cell device |

| US4988637A (en) * | 1990-06-29 | 1991-01-29 | International Business Machines Corp. | Method for fabricating a mesa transistor-trench capacitor memory cell structure |

| US5198995A (en) * | 1990-10-30 | 1993-03-30 | International Business Machines Corporation | Trench-capacitor-one-transistor storage cell and array for dynamic random access memories |

| US5251373A (en) * | 1991-10-15 | 1993-10-12 | Thomas & Betts Corporation | Method for protection of cable splices |

| US5264716A (en) * | 1992-01-09 | 1993-11-23 | International Business Machines Corporation | Diffused buried plate trench dram cell array |

| US5389559A (en) * | 1993-12-02 | 1995-02-14 | International Business Machines Corporation | Method of forming integrated interconnect for very high density DRAMs |

| US5360758A (en) * | 1993-12-03 | 1994-11-01 | International Business Machines Corporation | Self-aligned buried strap for trench type DRAM cells |

| US5384277A (en) * | 1993-12-17 | 1995-01-24 | International Business Machines Corporation | Method for forming a DRAM trench cell capacitor having a strap connection |

| US5545583A (en) * | 1995-04-13 | 1996-08-13 | International Business Machines Corporation | Method of making semiconductor trench capacitor cell having a buried strap |

-

1995

- 1995-04-13 US US08/421,714 patent/US5576566A/en not_active Expired - Fee Related

- 1995-08-31 US US08/522,204 patent/US5719080A/en not_active Expired - Fee Related

-

1996

- 1996-01-16 TW TW085100479A patent/TW311239B/zh active

- 1996-03-28 EP EP96480036A patent/EP0738006A3/en not_active Withdrawn

- 1996-03-29 KR KR1019960009126A patent/KR100193975B1/ko not_active IP Right Cessation

- 1996-04-09 JP JP08629796A patent/JP3634918B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW311239B (ja) | 1997-07-21 |

| JPH08288474A (ja) | 1996-11-01 |

| KR100193975B1 (ko) | 1999-06-15 |

| EP0738006A2 (en) | 1996-10-16 |

| US5576566A (en) | 1996-11-19 |

| EP0738006A3 (en) | 1999-06-09 |

| US5719080A (en) | 1998-02-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3634918B2 (ja) | 埋設ストラップを有する半導体デバイス及びその製造方法 | |

| KR100193976B1 (ko) | 매립 스트랩을 갖는 반도체 트렌치 커패시터 셀 | |

| US6809368B2 (en) | TTO nitride liner for improved collar protection and TTO reliability | |

| JP4585309B2 (ja) | 集積回路のキャパシタの記憶ノード用接点ペデスタルを形成するための半導体処理方法 | |

| US5706164A (en) | Method of fabricating high density integrated circuits, containing stacked capacitor DRAM devices, using elevated trench isolation and isolation spacers | |

| US6008513A (en) | Dynamic random access memory (DRAM) cells with minimum active cell areas using sidewall-space bit lines | |

| US6787839B2 (en) | Capacitor structure | |

| KR19980063505A (ko) | 트렌치 캐패시터 및 그의 형성 방법과, 디램 저장 셀 형성 방법 | |

| US5250457A (en) | Method of forming a buried bit line array of memory cells | |

| WO2002043111A2 (en) | Method for forming and filling isolation trenches | |

| KR100562235B1 (ko) | 실리콘-온-절연체에 동적 랜덤 액세스 메모리 어레이를포함하는 집적 회로 형성 방법 및 그 집적 회로 | |

| US6693041B2 (en) | Self-aligned STI for narrow trenches | |

| KR100538810B1 (ko) | 반도체소자의 소자분리 방법 | |

| JPH06318680A (ja) | 半導体記憶装置およびその製造方法 | |

| US5674769A (en) | Process for forming deep trench DRAMs with sub-groundrule gates | |

| CN114420642A (zh) | 半导体结构的形成方法以及半导体结构 | |

| KR0138317B1 (ko) | 반도체장치 커패시터 제조방법 | |

| JPH1050952A (ja) | 半導体装置およびその製造方法 | |

| KR100244493B1 (ko) | 반도체소자의 분리구조 제조방법 | |

| CN114420641A (zh) | 半导体结构的形成方法以及半导体结构 | |

| US20220216196A1 (en) | Semiconductor structure and method for preparing semiconductor structure | |

| JP2509912B2 (ja) | 半導体記憶装置の製造方法 | |

| KR960013644B1 (ko) | 캐패시터 제조방법 | |

| KR20010021422A (ko) | 반도체메모리장치 및 그 제조방법 | |

| US20070090433A1 (en) | Isolation collar void and methods of forming the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040518 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20040812 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20040823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041118 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041214 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041227 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |