JP2020501474A - 電圧クランプ回路 - Google Patents

電圧クランプ回路 Download PDFInfo

- Publication number

- JP2020501474A JP2020501474A JP2019551241A JP2019551241A JP2020501474A JP 2020501474 A JP2020501474 A JP 2020501474A JP 2019551241 A JP2019551241 A JP 2019551241A JP 2019551241 A JP2019551241 A JP 2019551241A JP 2020501474 A JP2020501474 A JP 2020501474A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- input

- comparator

- clamping

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/01—Shaping pulses

- H03K5/08—Shaping pulses by limiting; by thresholding; by slicing, i.e. combined limiting and thresholding

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/22—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral

- H03K5/24—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral the characteristic being amplitude

- H03K5/2472—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral the characteristic being amplitude using field effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/124—Sampling or signal conditioning arrangements specially adapted for A/D converters

- H03M1/129—Means for adapting the input signal to the range the converter can handle, e.g. limiting, pre-scaling ; Out-of-range indication

- H03M1/1295—Clamping, i.e. adjusting the DC level of the input signal to a predetermined value

Abstract

Description

Claims (20)

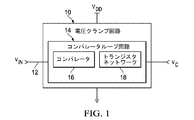

- 電圧クランプ回路であって、

コンパレータループ回路を含み、

前記コンパレータループ回路が、

入力ノードにおいて提供される入力電圧をクランピング電圧と比較するように構成されるコンパレータと、

電圧レール及び前記入力ノードを相互接続するトランジスタネットワークと、

を含み、

前記コンパレータが、前記入力電圧が対応するクランピング電圧を超えることに応答して、前記入力電圧を前記クランピング電圧にほぼ等しくなるように設定するために前記トランジスタネットワークをアクティベートするように構成される、

電圧クランプ回路。 - 請求項1に記載の電圧クランプ回路であって、少なくとも一つの前記コンパレータの各々が、トランジスタの自己バイアス共通・ゲート配置として構成される、電圧クランプ回路。

- 請求項1に記載の電圧クランプ回路であって、

前記コンパレータが、

前記コンパレータの前記出力に対応する共通結合制御端子を含むトランジスタの第1の対であって、トランジスタの前記第1の対の一方が、前記入力ノードに結合される端子を含み、トランジスタの前記第1の対の他方が、前記クランピング電圧に結合される端子を含む、トランジスタの前記第1の対、及び

静的電流源により制御される電流ミラーとして配されるトランジスタの第2の対であって、前記第2の対のトランジスタの各々が、前記電圧レールに結合される第1の端子と、トランジスタの前記第1の対の各々の第2のそれぞれの端子に結合される第2の端子とを含む、前記第2の対のトランジスタ、

を含む、

電圧クランプ回路。 - 請求項1に記載の電圧クランプ回路であって、

前記トランジスタネットワークが、

前記コンパレータの前記出力によりアクティベートされる第1のトランジスタ、

前記入力ノード及び前記電圧レールを相互接続し、前記第1のトランジスタにより制御される第2のトランジスタ、

を含む、

電圧クランプ回路。 - 請求項4に記載の電圧クランプ回路であって、前記トランジスタネットワークが、前記電圧レール及び前記第1のトランジスタに結合される第3のトランジスタを含み、前記第3のトランジスタが、前記第2のトランジスタを制御するため前記第1のトランジスタと協働するように第1のバイアス電圧を介して制御される、電圧クランプ回路。

- 請求項1に記載の電圧クランプ回路であって、前記クランピング電圧がプログラム可能であり、前記コンパレータループ回路が、前記入力電圧を前記クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記クランピング電圧を超えることに応答して、前記入力ノードを前記電圧レールに結合するように構成される、電圧クランプ回路。

- 請求項1に記載の電圧クランプ回路であって、更に、前記電圧レールと前記コンパレータループ回路との間に結合される電圧生成器を含み、前記電圧生成器が、前記クランピング電圧を生成するように構成され、

前記コンパレータループ回路が、前記コンパレータが、前記入力電圧を前記クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記クランピング電圧を超えることを検出することに基づいて、前記入力ノードを前記電圧生成器の前記クランピング電圧に結合するように構成される、

電圧クランプ回路。 - 請求項1に記載の電圧クランプ回路であって、前記クランピング電圧が、低クランピング電圧及び高クランピング電圧を含み、

前記コンパレータループ回路が、

第1のコンパレータループ回路、及び

第2のコンパレータループ回路、

を含み、

前記第1のコンパレータループ回路が、

前記入力電圧を前記低クランピング電圧と比較し、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して前記第1のコンパレータの出力をアサートするように構成される第1のコンパレータと、

前記入力ノード及び前記高電圧レールを相互接続し、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して、前記入力電圧を前記低クランピング電圧にほぼ等しくなるよう設定するため、前記第1のコンパレータが前記第1のトランジスタネットワークをアクティベートするように構成される第1のトランジスタネットワークと、

を含み、

前記第2のコンパレータループ回路が、

前記入力電圧を前記高クランピング電圧と比較し、前記入力電圧が前記高クランピング電圧より大きく増大することに応答して前記第2のコンパレータの出力をアサートするように構成される第2のコンパレータと、

前記入力ノード及び前記低電圧レールを相互接続し、前記入力電圧が前記低クランピング電圧より大きく増大することに応答して、前記入力電圧が前記高クランピング電圧にほぼ等しくなるように設定するため、前記第1のコンパレータが前記第1のトランジスタネットワークをアクティベートするように構成される第2のトランジスタネットワークと、

を含む、

電圧クランプ回路。 - 請求項1の前記電圧クランプ回路を含むアナログデジタルコンバータ(ADC)システムであって、前記ADCシステムが更に、

アナログ電圧入力と前記入力ノードとの間に接続される入力抵抗器であって、前記入力電圧が、前記アナログ電圧入力において提供されるアナログ電圧に基づいて前記入力ノードにおいて生成される、前記入力抵抗器、及び

前記入力ノードに結合され、前記入力電圧に基づいてデジタル信号を生成するように構成されるADC、

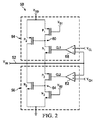

を含む、電圧クランプ回路。 - 電圧クランプ回路であって、

入力電圧を低クランピング電圧と比較するように、及び、前記入力電圧を前記低クランピング電圧にほぼ等しくなるように設定するために、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して第1のトランジスタネットワークをアクティベートするために出力をアサートするように構成される第1のコンパレータを含む第1のコンパレータループ回路、及び

前記入力電圧を高クランピング電圧と比較するように、及び、前記入力電圧を前記高クランピング電圧にほぼ等しくなるように設定するために、前記入力電圧が前記低クランピング電圧より大きく増大することに応答してをアクティベートするために第2のトランジスタネットワーク出力をアサートするように構成される第2のコンパレータを含む第2のコンパレータループ回路、

を含む、電圧クランプ回路。 - 請求項10に記載の電圧クランプ回路であって、前記第1のコンパレータ及び前記第2のコンパレータの各々が、トランジスタの自己バイアス共通・ゲート配置として構成される、電圧クランプ回路。

- 請求項10に記載の電圧クランプ回路であって、

前記第1のトランジスタネットワークが第1のトランジスタ配置を含み、前記第1のトランジスタ配置が、前記第1のコンパレータによりアクティベートされ、前記入力ノード及び高電圧レールを相互接続する第2のトランジスタを制御するように構成され、

前記第2のトランジスタネットワークが第3のトランジスタを含み、前記第3のトランジスタが、前記第2のコンパレータによりアクティベートされ、前記入力ノード及び低電圧レールを相互接続する第4のトランジスタを制御するように構成される、

電圧クランプ回路。 - 請求項12に記載の電圧クランプ回路であって、

前記第2のトランジスタが更に、前記高電圧レールに結合されて第1のバイアス電圧を介して制御される、第5のトランジスタにより制御され、

前記第4のトランジスタが更に、前記低電圧レールに結合されて第2のバイアス電圧を介して制御される、第6のトランジスタにより制御される、

電圧クランプ回路。 - 請求項10に記載の電圧クランプ回路であって、

前記高及び低クランピング電圧の各々がプログラム可能であり、

前記第1のコンパレータループ回路が、前記入力電圧を前記低クランピング電圧にほぼ等しくなるように設定するため、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して前記入力ノードを高電圧レールに結合するように構成され、

前記第2のコンパレータループ回路が、前記入力電圧を前記高クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記低クランピング電圧より大きく増大することに応答して前記入力ノードを低電圧レールに結合するように構成される、

電圧クランプ回路。 - 請求項10に記載の電圧クランプ回路であって、更に、

低電圧レールに結合され、前記低クランピング電圧を生成するように構成される第1の電圧生成器、及び

高電圧レールに結合され、前記高クランピング電圧を生成するように構成される第2の電圧生成器、

を含み、

前記第1のコンパレータループ回路が、前記入力電圧を前記低クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して前記入力ノードを前記第2の電圧生成器に結合するように構成され、

前記第2のコンパレータループ回路が、前記入力電圧を前記高クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記低クランピング電圧より大きく増大することに応答して前記入力ノードを前記第1の電圧生成器に結合するように構成される、

電圧クランプ回路。 - 請求項11に記載の前記電圧クランプ回路を含むアナログデジタルコンバータ(ADC)システムであって、前記ADCシステムが更に、

アナログ電圧入力及び前記入力ノードを相互接続する入力抵抗器であって、前記入力電圧が、前記アナログ電圧入力において提供されるアナログ電圧に基づいて生成される、前記入力抵抗器、及び

前記入力ノードに結合され、前記入力電圧に基づいてデジタル信号を生成するように構成されるADC、

を含む、ADCシステム。 - アナログデジタルコンバータ(ADC)回路システムであって、

アナログ電圧入力とADC入力ノードとの間に接続される入力抵抗器、

前記ADC入力ノードに結合され、コンパレータループ回路を含む電圧クランプ回路であって、前記コンパレータループ回路が、

入力ノードにおいて提供される入力電圧をクランピング電圧と比較するように構成されるコンパレータと、

電圧レール及び前記入力ノードを相互接続するトランジスタネットワークであって、前記コンパレータが、前記入力電圧が対応するクランピング電圧を超えることに応答して、前記入力電圧を前記クランピング電圧にほぼ等しくなるように設定するために前記トランジスタネットワークをアクティベートするように構成される、前記トランジスタネットワークと、

を含む、前記コンパレータループ回路、及び

前記ADC入力ノードに結合され、前記入力電圧に基づいてデジタル信号を生成するように構成されるADC、

を含む、ADC回路システム。 - 請求項17に記載のADC回路システムであって、前記トランジスタネットワークが第1のトランジスタを含み、前記第1のトランジスタが、前記コンパレータによりアクティベートされ、前記入力ノード及び前記電圧レールを相互接続する第2のトランジスタを制御するように構成される、ADC回路システム。

- 請求項17に記載のADC回路システムであって、

前記電圧レールに結合され、前記クランピング電圧を生成するように構成される電圧生成器を更に含み、

前記コンパレータループ回路が、前記入力電圧を前記クランピング電圧にほぼ等しくなるよう設定するため、前記入力電圧が前記クランピング電圧を超えることに応答して前記入力ノードを前記電圧生成器に結合するように構成される、

ADC回路システム。 - 請求項17に記載のADC回路システムであって、

前記クランピング電圧が、低クランピング電圧及び高クランピング電圧を含み、

前記コンパレータループ回路が、第1のコンパレータループ回路、及び第2のコンパレータループ回路を含み、

前記第1のコンパレータループ回路が、

前記入力電圧を前記低クランピング電圧と比較し、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して前記第1のコンパレータの出力をアサートするように構成される、第1のコンパレータと、

前記入力ノード及び前記高電圧レールを相互接続し、前記入力電圧が前記低クランピング電圧より小さく低減することに応答して、前記入力電圧を前記低クランピング電圧にほぼ等しくなるよう設定するため前記第1のコンパレータが前記第1のトランジスタネットワークをアクティベートするように構成される、第1のトランジスタネットワークと、

を含み、

前記第2のコンパレータループ回路が、

前記入力電圧を前記高クランピング電圧と比較し、前記入力電圧が前記高クランピング電圧より大きく増大することに応答して前記第2のコンパレータの出力をアサートするように構成される、第2のコンパレータと、

前記入力ノード及び前記低電圧レールを相互接続し、前記入力電圧が前記高クランピング電圧より大きく増大することに応答して、前記入力電圧が前記高クランピング電圧にほぼ等しくなるように設定するため前記第1のコンパレータが前記第1のトランジスタネットワークをアクティベートするように構成される、第2のトランジスタネットワークと、

を含む、

ADC回路システム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/369,225 US9793882B1 (en) | 2016-12-05 | 2016-12-05 | Voltage clamp circuit |

| US15/369,225 | 2016-12-05 | ||

| PCT/US2017/064528 WO2018106600A1 (en) | 2016-12-05 | 2017-12-04 | Voltage clamp circuit |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020501474A true JP2020501474A (ja) | 2020-01-16 |

| JP2020501474A5 JP2020501474A5 (ja) | 2021-01-21 |

Family

ID=60021800

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019551241A Pending JP2020501474A (ja) | 2016-12-05 | 2017-12-04 | 電圧クランプ回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9793882B1 (ja) |

| EP (1) | EP3548982A4 (ja) |

| JP (1) | JP2020501474A (ja) |

| CN (1) | CN109923493A (ja) |

| WO (1) | WO2018106600A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111162786B (zh) * | 2020-01-20 | 2022-03-29 | 电子科技大学 | 一种消除回踢噪声的比较器 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS49121458A (ja) * | 1973-03-19 | 1974-11-20 | ||

| US5528190A (en) * | 1994-10-03 | 1996-06-18 | Delco Electronics Corporation | CMOS input voltage clamp |

| JPH11150469A (ja) * | 1997-09-11 | 1999-06-02 | Mitsubishi Electric Corp | 半導体集積回路 |

| JP2002237742A (ja) * | 2001-02-07 | 2002-08-23 | Toshiba Microelectronics Corp | 半導体集積回路 |

| JP2003124811A (ja) * | 2001-10-15 | 2003-04-25 | Denso Corp | クランプ回路 |

| US20030090309A1 (en) * | 2001-11-09 | 2003-05-15 | Hunt Ken S. | Voltage clamp circuit |

| JP2003258581A (ja) * | 2002-02-26 | 2003-09-12 | Denso Corp | クランプ回路 |

| JP2013187755A (ja) * | 2012-03-08 | 2013-09-19 | Azbil Corp | レベル制限回路 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SU1027814A2 (ru) * | 1982-02-11 | 1983-07-07 | Предприятие П/Я М-5619 | Аналого-цифровой преобразователь |

| US4445160A (en) * | 1982-03-30 | 1984-04-24 | Westinghouse Electric Corp. | Fault-powered low-level voltage clamp circuit |

| US4751405A (en) * | 1985-08-26 | 1988-06-14 | Gould Inc. | Externally programmable, process and temperature insensitive threshold receiver circuit |

| US5070259A (en) * | 1989-12-26 | 1991-12-03 | Linear Technology Corporation | Constant current, highspeed, auto-zeroed, CMOS comparator |

| JP3058699B2 (ja) * | 1990-02-16 | 2000-07-04 | テキサス インスツルメンツ インコーポレイテツド | 誘導性負荷中の電流制御のための負電圧クランプ回路 |

| US5329252A (en) * | 1992-11-05 | 1994-07-12 | Northern Telecom Limited | Slew-rate limited voltage controlled oscillator control voltage clamp circuit |

| JP3864864B2 (ja) * | 2002-07-11 | 2007-01-10 | 株式会社デンソー | クランプ回路 |

| RU162000U1 (ru) * | 2016-01-11 | 2016-05-20 | федеральное государственное бюджетное образовательное учреждение высшего образования "Ставропольский государственный аграрный университет" | Стабилизатор постоянного напряжения |

-

2016

- 2016-12-05 US US15/369,225 patent/US9793882B1/en active Active

-

2017

- 2017-12-04 CN CN201780069230.5A patent/CN109923493A/zh active Pending

- 2017-12-04 WO PCT/US2017/064528 patent/WO2018106600A1/en unknown

- 2017-12-04 JP JP2019551241A patent/JP2020501474A/ja active Pending

- 2017-12-04 EP EP17877964.1A patent/EP3548982A4/en active Pending

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS49121458A (ja) * | 1973-03-19 | 1974-11-20 | ||

| US5528190A (en) * | 1994-10-03 | 1996-06-18 | Delco Electronics Corporation | CMOS input voltage clamp |

| JPH11150469A (ja) * | 1997-09-11 | 1999-06-02 | Mitsubishi Electric Corp | 半導体集積回路 |

| JP2002237742A (ja) * | 2001-02-07 | 2002-08-23 | Toshiba Microelectronics Corp | 半導体集積回路 |

| JP2003124811A (ja) * | 2001-10-15 | 2003-04-25 | Denso Corp | クランプ回路 |

| US20030090309A1 (en) * | 2001-11-09 | 2003-05-15 | Hunt Ken S. | Voltage clamp circuit |

| JP2003258581A (ja) * | 2002-02-26 | 2003-09-12 | Denso Corp | クランプ回路 |

| JP2013187755A (ja) * | 2012-03-08 | 2013-09-19 | Azbil Corp | レベル制限回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN109923493A (zh) | 2019-06-21 |

| US9793882B1 (en) | 2017-10-17 |

| WO2018106600A1 (en) | 2018-06-14 |

| EP3548982A4 (en) | 2019-12-25 |

| EP3548982A1 (en) | 2019-10-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7548117B2 (en) | Differential amplifier having an improved slew rate | |

| US20070216448A1 (en) | Apparatus for adaptive trip point detection | |

| JP2009098802A (ja) | 基準電圧発生回路 | |

| TW201640126A (zh) | 電流檢測電路 | |

| JP7131965B2 (ja) | ボルテージディテクタ | |

| US7385446B2 (en) | High-impedance level-shifting amplifier capable of handling input signals with a voltage magnitude that exceeds a supply voltage | |

| US9419571B2 (en) | Precision, high voltage, low power differential input stage with static and dynamic gate protection | |

| US6198312B1 (en) | Low level input voltage comparator | |

| JP6065554B2 (ja) | 比較器 | |

| US8130034B2 (en) | Rail-to-rail amplifier | |

| TWI645279B (zh) | 參考電壓緩衝電路 | |

| US9654092B1 (en) | High speed gain stage with analog input and determinable digital output using regenerative feedback | |

| JP2020501474A (ja) | 電圧クランプ回路 | |

| US10095260B2 (en) | Start-up circuit arranged to initialize a circuit portion | |

| US9877104B2 (en) | Audio switch circuit with slow turn-on | |

| US9543905B2 (en) | Amplifier circuit | |

| US6888384B2 (en) | Power-on detector, and power-on reset circuit using the same | |

| US9024603B2 (en) | Low power current comparator for switched mode regulator | |

| US7271614B2 (en) | Buffer circuit with current limiting | |

| US9588540B2 (en) | Supply-side voltage regulator | |

| JP2017005609A (ja) | 過電圧検出回路 | |

| TWI630403B (zh) | 核心電源偵測電路以及輸入/輸出控制系統 | |

| GB2475624A (en) | Compensating for leakage current in a current mirror | |

| US9356587B2 (en) | High voltage comparison circuit | |

| JP6672067B2 (ja) | 安定化電源回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20190605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201130 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201130 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20210218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210323 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210602 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210928 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20220420 |