JP2018166320A - シリアル伝送信号を復号するための復号装置およびその方法 - Google Patents

シリアル伝送信号を復号するための復号装置およびその方法 Download PDFInfo

- Publication number

- JP2018166320A JP2018166320A JP2017126028A JP2017126028A JP2018166320A JP 2018166320 A JP2018166320 A JP 2018166320A JP 2017126028 A JP2017126028 A JP 2017126028A JP 2017126028 A JP2017126028 A JP 2017126028A JP 2018166320 A JP2018166320 A JP 2018166320A

- Authority

- JP

- Japan

- Prior art keywords

- value

- phase

- values

- edge

- transmission signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M7/00—Conversion of a code where information is represented by a given sequence or number of digits to a code where the same, similar or subset of information is represented by a different sequence or number of digits

- H03M7/30—Compression; Expansion; Suppression of unnecessary data, e.g. redundancy reduction

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0045—Arrangements at the receiver end

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M5/00—Conversion of the form of the representation of individual digits

- H03M5/02—Conversion to or from representation by pulses

- H03M5/04—Conversion to or from representation by pulses the pulses having two levels

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M5/00—Conversion of the form of the representation of individual digits

- H03M5/02—Conversion to or from representation by pulses

- H03M5/04—Conversion to or from representation by pulses the pulses having two levels

- H03M5/06—Code representation, e.g. transition, for a given bit cell depending only on the information in that bit cell

- H03M5/08—Code representation by pulse width

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0045—Arrangements at the receiver end

- H04L1/0047—Decoding adapted to other signal detection operation

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Dc Digital Transmission (AREA)

Abstract

Description

PHV(N)

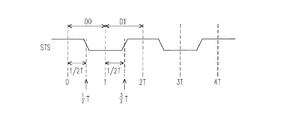

=1/2×T(対応するサンプル値がエッジである場合)

=(PHV(N−1)+1)%T(対応するサンプル値がエッジではない場合) (1)

PHASE(N)=

Pr(対応するサンプル値が立ち上がりエッジである場合)

Pf(対応するサンプル値が立ち下がりエッジである場合)

(PHV(N−1)+1)%T(対応するサンプル値がエッジではない場合) (2)

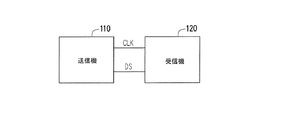

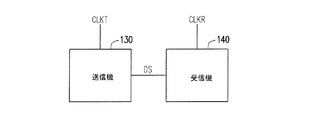

120、140 受信機

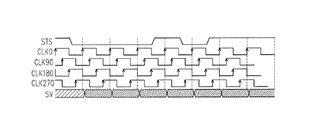

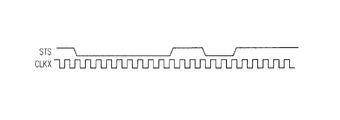

CLK、CLKT、CLK0、CLK90、CLK180、CLK270、CLKX、CLKS クロック信号

CLKR クロック

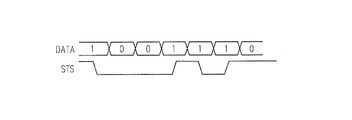

DS、STS シリアル伝送信号

DATA 送信データ

S310〜S350 復号ステップ

T、2T、3T、4T、1/2T、3/2T 時点

D0、D1 データ

SV、SV1、SV2 サンプル値

EDGV、EG1、EG2、EG3 エッジ値

PHV(N)、PV1〜PV5 位相値

BD1〜BDN、BDx 境界

OUT 復号済みデータ

OT1〜OT3 データ・ビット

Pr 立ち上がり値

Pf 立ち下がり値

IDX 指標値

1000 データ復号装置

1010 データ・サンプリング装置

1100、1020 コントローラ

1130 位相検出器

1110 エッジ検出器

1120 位相計算器

T 周期

1140 境界検出器

1150 データ出力回路

Claims (18)

- シリアル伝送信号を復号するための方法であって、

該シリアル伝送信号をサンプリングして、サンプリング周期に応じて複数のサンプル値を取得するステップと、

該サンプル値の遷移状態に応じて、該シリアル伝送信号の周期を取得するステップと、

該周期および該サンプル値の該遷移状態に応じて、複数の位相値を計算するステップと、

該位相値に応じて、複数の境界を取得するステップと、

該境界および該遷移状態に応じて、復号済みデータを出力するステップと

を備える方法。 - 前記シリアル伝送信号をサンプリングして、前記サンプリング周期に応じて前記サンプル値を取得するステップが、

該サンプリング周期を有するサンプリング・クロックによって、該シリアル伝送信号の複数の所定のパターンをサンプリングするステップを備え、

該所定のパターンが、該シリアル伝送信号上でデータを送る前に送られる、

請求項1に記載の方法。 - 前記シリアル伝送信号をサンプリングして、前記サンプリング周期に応じて前記サンプル値を取得するステップが、

該シリアル伝送信号の複数の所定のパターンを、複数のサンプリング・クロックによってサンプリングするステップを備え、

該所定のパターンが、該シリアル伝送信号上でデータを送る前に送られる、

請求項1に記載の方法。 - 前記遷移状態が複数のエッジ値を備え、該エッジ値のそれぞれが、第1のサンプル値と第2のサンプル値との変動に応じて決定され、該第1のサンプル値が、該第2のサンプル値のすぐ隣にある、請求項1から3のいずれか一項に記載の方法。

- 前記シリアル伝送信号をサンプリングして、前記サンプリング周期に応じて前記サンプル値を取得するステップが、

該サンプル値にそれぞれ対応する複数の指標値を生成するステップであって、該指標値が等差数列を形成する、生成するステップをさらに備え、

前記サンプル値の前記遷移状態に応じて、前記シリアル伝送信号の前記周期を取得する前記ステップが、

A番目のエッジ値およびB番目のエッジ値にそれぞれ対応する2つの指標値の差分値を計算するステップ、および該差分値を(A−B)で割って、該シリアル伝送信号の該周期を取得するステップを備える、請求項4に記載の方法。 - 前記周期および前記サンプル値の前記遷移状態に応じて、前記位相値を計算するステップが、

該位相値のそれぞれPHASE(N)が、前記エッジ値のうちの1つに対応する場合には、該位相値のそれぞれPHASE(N)=前記シリアル伝送信号の該周期Tの2分の1、を設定するステップと、

該位相値のそれぞれPHASE(N)に対応するエッジ値がない場合には、該位相値のそれぞれPHASE(N)=((PHASE(N−1)+1)/T)の剰余値、を設定するステップと

を備える、請求項5に記載の方法。 - 前記周期および前記サンプル値の前記遷移状態に応じて、前記位相値を計算するステップが、

C番目のエッジ値とD番目のエッジ値との間の1の数を計算し、該1の数を(C−D)で割って、下降値Pfを取得するステップと、

該C番目のエッジ値と該D番目のエッジ値との間の0の数を計算し、該0の数を(C−D)で割って、立ち上がり値Prを取得するステップと、

該位相値のそれぞれPHASE(N)に対応する前記エッジ値のうちの1つが立ち上がりエッジである場合には、該位相値のそれぞれPHASE(N)=Pr、を設定するステップと、

該位相値のそれぞれPHASE(N)に対応する該エッジ値のうちの1つが立ち下がりエッジである場合には、該位相値のそれぞれPHASE(N)=Pf、を設定するステップと、

該位相値のそれぞれPHASE(N)に対応するエッジ値がない場合には、該位相値のそれぞれPHASE(N)=((PHASE(N−1)+1)/T)の剰余値、を設定するステップと

を備える、請求項5に記載の方法。 - 前記位相値に応じて、前記境界を取得するステップが、

該位相値のそれぞれが前記シリアル伝送信号の前記周期よりも小さいかどうかをチェックすることによって、該境界のそれぞれを取得するステップを備える、請求項1から7のいずれか一項に記載の方法。 - 前記境界および前記遷移状態に応じて、前記復号済みデータを出力するステップが、

該遷移状態にある複数のエッジ値のうちの1つが、2つの連続した境界間に生じたかどうかをチェックするステップを備える、請求項1から8のいずれか一項に記載の方法。 - シリアル伝送信号を復号するように構成されたデータ復号装置であって、

該シリアル伝送信号をサンプリングして、サンプリング周期に応じて複数のサンプル値を取得する信号サンプリング装置と、

該信号サンプリング装置に接続されたコントローラであって、

該シリアル伝送信号の周期を、該サンプル値の遷移状態に応じて取得し、

該周期および該サンプル値の該遷移状態に応じて、複数の位相値を計算し、

該位相値に応じて、複数の境界を取得し、

該境界および該遷移状態に応じて、復号済みデータを出力する

ように構成されたコントローラと

を備える、データ復号装置。 - 前記信号サンプリング装置が、前記サンプリング周期を有するサンプリング・クロックによって前記シリアル伝送信号の複数の所定のパターンをサンプリングし、

該所定のパターンが、該シリアル伝送信号上でデータを送る前に送られる、請求項10に記載のデータ復号装置。 - 前記信号サンプリング装置が、複数のサンプリング・クロックによって、前記シリアル伝送信号の複数の所定のパターンをサンプリングし、

該所定のパターンが、該シリアル伝送信号上でデータを送る前に送られる、請求項10に記載のデータ復号装置。 - 前記遷移状態が複数のエッジ値を備え、該エッジ値のそれぞれが、第1のサンプル値と第2のサンプル値との変動に応じて前記コントローラによって決定され、該第1のサンプル値が、該第2のサンプル値のすぐ隣にある、請求項10から12のいずれか一項に記載のデータ復号装置。

- 前記コントローラが、前記サンプル値にそれぞれ対応する複数の指標値であって、等差数列を形成する指標値を生成し、A番目のエッジ値およびB番目のエッジ値にそれぞれ対応する2つの指標値の差分値を計算し、該差分値を(A−B)で割って、前記シリアル伝送信号の前記周期を取得するようにさらに構成された、請求項13に記載のデータ復号装置。

- 前記コントローラが、

前記位相値のそれぞれPHASE(N)が、前記エッジ値のうちの1つに対応する場合には、該位相値のそれぞれPHASE(N)=前記シリアル伝送信号の前記周期Tの2分の1、を設定し、

該位相値のそれぞれPHASE(N)に対応するエッジ値がない場合には、該位相値のそれぞれPHASE(N)=((PHASE(N−1)+1)/T)の剰余値、を設定する

ようにさらに構成された、請求項14に記載のデータ復号装置。 - 前記コントローラが、

C番目のエッジ値とD番目のエッジ値との間の1の数を計算し、該1の数を(C−D)で割って下降値Pfを取得し、

該C番目のエッジ値と該D番目のエッジ値との間の0の数を計算し、該0の数を(C−D)で割って立ち上がり値Prを取得し、

前記位相値のそれぞれPHASE(N)に対応する前記エッジ値のうちの1つが立ち上がりエッジである場合には、該位相値のそれぞれPHASE(N)=Pr、を設定し

該位相値のそれぞれPHASE(N)に対応する該エッジ値のうちの1つが立ち下がりエッジである場合には、該位相値のそれぞれPHASE(N)=Pf、を設定し、

該位相値のそれぞれPHASE(N)に対応するエッジ値がない場合には、該位相値のそれぞれPHASE(N)=((PHASE(N−1)+1)/T)の剰余値、を設定する

ようにさらに構成された、請求項14に記載のデータ復号装置。 - 前記コントローラが、

前記位相値のそれぞれが前記シリアル伝送信号の前記周期よりも小さいかどうかをチェックすることによって、前記境界のそれぞれを取得する

ようにさらに構成された、請求項10から16のいずれか一項に記載のデータ復号装置。 - 前記コントローラが、

前記遷移状態にある複数のエッジ値のうちの1つが、2つの連続した境界間に生じたかどうかをチェックする

ようにさらに構成された、請求項10から17のいずれか一項に記載のデータ復号装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/470,935 US9722630B1 (en) | 2017-03-28 | 2017-03-28 | Decoding apparatus and method for decoding a serially transmitted signal thereof |

| US15/470,935 | 2017-03-28 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP6401828B1 JP6401828B1 (ja) | 2018-10-10 |

| JP2018166320A true JP2018166320A (ja) | 2018-10-25 |

Family

ID=59382681

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017126028A Active JP6401828B1 (ja) | 2017-03-28 | 2017-06-28 | シリアル伝送信号を復号するための復号装置およびその方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9722630B1 (ja) |

| JP (1) | JP6401828B1 (ja) |

| CN (1) | CN108667562B (ja) |

| TW (1) | TWI639313B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112821915B (zh) * | 2019-10-31 | 2022-04-26 | 瑞昱半导体股份有限公司 | 数据处理装置与方法 |

| CN112838868B (zh) * | 2020-12-30 | 2022-09-09 | 天津瑞发科半导体技术有限公司 | 一种9b/10b编解码方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06104741A (ja) * | 1992-09-22 | 1994-04-15 | Sony Corp | ディジタルpll装置 |

| JP2004328715A (ja) * | 2003-04-09 | 2004-11-18 | Sharp Corp | 波形整形方法、波形整形装置、電子機器、波形整形プログラムおよび記録媒体 |

| JP2008167058A (ja) * | 2006-12-27 | 2008-07-17 | Rohm Co Ltd | 受信回路、受信方法およびそれらを利用した無線装置 |

| JP2016171387A (ja) * | 2015-03-11 | 2016-09-23 | 株式会社日立製作所 | クロックデータリカバリ回路 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3238298A (en) * | 1962-05-07 | 1966-03-01 | Avco Corp | Multiplex communication system with multiline digital buffer |

| US5751773A (en) * | 1992-03-12 | 1998-05-12 | Ntp Incorporated | System for wireless serial transmission of encoded information |

| US6198783B1 (en) * | 1992-03-12 | 2001-03-06 | Ntp Incorporated | System for wireless serial transmission of encoded information |

| US5742644A (en) * | 1992-03-12 | 1998-04-21 | Ntp Incorporated | Receiving circuitry for receiving serially transmitted encoded information |

| US5761254A (en) | 1996-01-31 | 1998-06-02 | Advanced Micro Devices, Inc. | Digital architecture for recovering NRZ/NRZI data |

| US6138190A (en) * | 1997-09-16 | 2000-10-24 | Cirrus Logic, Inc. | Analog front end and digital signal processing device and method |

| US6081783A (en) * | 1997-11-14 | 2000-06-27 | Cirrus Logic, Inc. | Dual processor digital audio decoder with shared memory data transfer and task partitioning for decompressing compressed audio data, and systems and methods using the same |

| US6944248B2 (en) | 2001-05-17 | 2005-09-13 | Bluebrook Associates Llc | Data rate calibration for asynchronous serial communications |

| US6611219B1 (en) | 2002-05-01 | 2003-08-26 | Macronix International Co., Ltd. | Oversampling data recovery apparatus and method |

| CN1234219C (zh) * | 2003-01-29 | 2005-12-28 | 北京邮电大学 | 一种基于循环前缀的调制系统的符号同步及载波同步方法 |

| US8140931B2 (en) | 2003-07-03 | 2012-03-20 | Dtvg Licensing, Inc. | Method and system for generating parallel decodable low density parity check (LDPC) codes |

| JP4676792B2 (ja) * | 2005-03-17 | 2011-04-27 | 株式会社リコー | データリカバリ方法、データリカバリ回路、データ送受信装置及び情報処理装置 |

| US8396180B2 (en) * | 2008-12-18 | 2013-03-12 | Kawasaki Microelectronics America Inc. | High jitter tolerant phase comparator |

| US8594262B2 (en) | 2010-06-17 | 2013-11-26 | Transwitch Corporation | Apparatus and method thereof for clock and data recovery of N-PAM encoded signals using a conventional 2-PAM CDR circuit |

| US9461812B2 (en) | 2013-03-04 | 2016-10-04 | Blackberry Limited | Increased bandwidth encoding scheme |

| DE102014119071A1 (de) * | 2014-12-18 | 2016-06-23 | Intel IP Corporation | Eine Vorrichtung und ein Verfahren zum Erzeugen eines Sendesignals |

-

2017

- 2017-03-28 US US15/470,935 patent/US9722630B1/en active Active

- 2017-05-04 TW TW106114768A patent/TWI639313B/zh active

- 2017-05-25 CN CN201710377151.2A patent/CN108667562B/zh active Active

- 2017-06-28 JP JP2017126028A patent/JP6401828B1/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06104741A (ja) * | 1992-09-22 | 1994-04-15 | Sony Corp | ディジタルpll装置 |

| JP2004328715A (ja) * | 2003-04-09 | 2004-11-18 | Sharp Corp | 波形整形方法、波形整形装置、電子機器、波形整形プログラムおよび記録媒体 |

| JP2008167058A (ja) * | 2006-12-27 | 2008-07-17 | Rohm Co Ltd | 受信回路、受信方法およびそれらを利用した無線装置 |

| JP2016171387A (ja) * | 2015-03-11 | 2016-09-23 | 株式会社日立製作所 | クロックデータリカバリ回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN108667562A (zh) | 2018-10-16 |

| JP6401828B1 (ja) | 2018-10-10 |

| TWI639313B (zh) | 2018-10-21 |

| TW201838347A (zh) | 2018-10-16 |

| CN108667562B (zh) | 2021-02-26 |

| US9722630B1 (en) | 2017-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107623520B (zh) | 改善时钟恢复的方法及相关装置 | |

| JP6461018B2 (ja) | 状態周期ごとに状態を変えるとともにデータのレーン間スキューおよびデータ状態遷移グリッチに | |

| JP5066121B2 (ja) | クロック情報とデータを伝送する装置及び方法 | |

| JP6158447B1 (ja) | 高ジッタ耐性および高速位相ロッキングを有するクロック・データリカバリ | |

| CN112100108B (zh) | 用于多个串行通信信号的异步串行化的方法和系统 | |

| JPH0661992A (ja) | 位相ロックループ発振器を使用せずに直列に伝送されたデータを回復するための装置および方法 | |

| JP5202115B2 (ja) | 伝送システム、受信装置および伝送方法 | |

| US8077063B2 (en) | Method and system for determining bit stream zone statistics | |

| JP6401828B1 (ja) | シリアル伝送信号を復号するための復号装置およびその方法 | |

| TWI436219B (zh) | 串列資料流的取樣時脈選擇模組 | |

| JP5751290B2 (ja) | データ受信装置及び受信ビット列の同一値ビット長判定方法 | |

| JP5369524B2 (ja) | クロック・データ・リカバリ回路 | |

| IL259732A (en) | Serial data multiplication | |

| JP2016171387A (ja) | クロックデータリカバリ回路 | |

| KR100899781B1 (ko) | 클록 정보와 함께 데이터를 전송하는 방법 및 장치 | |

| JP5633132B2 (ja) | データ伝送システム及び方法、データ送信装置及び受信装置 | |

| JP5923730B2 (ja) | クロックデータ復元装置 | |

| JP3371913B2 (ja) | 波形歪補正装置 | |

| TWI818521B (zh) | 測量裝置及測量方法 | |

| US20220271911A1 (en) | Clock and data recovery processor, measurement device and method | |

| JP7647067B2 (ja) | 光トランシーバおよび光トランシーバの制御方法 | |

| JP2003524970A (ja) | 2相コード化データ信号におけるデータ及びクロックのリカバリのための方法及び装置 | |

| US9602094B2 (en) | Decoding circuit and method of decoding signal | |

| JP2017103548A (ja) | 送信装置、受信装置、通信システム及び通信方法 | |

| KR20160069092A (ko) | 클럭 데이터 리커버리 회로 및 이를 이용하는 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180823 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180907 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6401828 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |