JP2017040580A - 電流検出回路 - Google Patents

電流検出回路 Download PDFInfo

- Publication number

- JP2017040580A JP2017040580A JP2015162964A JP2015162964A JP2017040580A JP 2017040580 A JP2017040580 A JP 2017040580A JP 2015162964 A JP2015162964 A JP 2015162964A JP 2015162964 A JP2015162964 A JP 2015162964A JP 2017040580 A JP2017040580 A JP 2017040580A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- voltage

- resistor

- period

- current

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/25—Arrangements for measuring currents or voltages or for indicating presence or sign thereof using digital measurement techniques

- G01R19/2506—Arrangements for conditioning or analysing measured signals, e.g. for indicating peak values ; Details concerning sampling, digitizing or waveform capturing

- G01R19/2509—Details concerning sampling, digitizing or waveform capturing

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R1/00—Details of instruments or arrangements of the types included in groups G01R5/00 - G01R13/00 and G01R31/00

- G01R1/20—Modifications of basic electric elements for use in electric measuring instruments; Structural combinations of such elements with such instruments

- G01R1/203—Resistors used for electric measuring, e.g. decade resistors standards, resistors for comparators, series resistors, shunts

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/25—Arrangements for measuring currents or voltages or for indicating presence or sign thereof using digital measurement techniques

- G01R19/255—Arrangements for measuring currents or voltages or for indicating presence or sign thereof using digital measurement techniques using analogue/digital converters of the type with counting of pulses during a period of time proportional to voltage or current, delivered by a pulse generator with fixed frequency

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/25—Arrangements for measuring currents or voltages or for indicating presence or sign thereof using digital measurement techniques

- G01R19/257—Arrangements for measuring currents or voltages or for indicating presence or sign thereof using digital measurement techniques using analogue/digital converters of the type with comparison of different reference values with the value of voltage or current, e.g. using step-by-step method

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K4/00—Generating pulses having essentially a finite slope or stepped portions

- H03K4/06—Generating pulses having essentially a finite slope or stepped portions having triangular shape

- H03K4/08—Generating pulses having essentially a finite slope or stepped portions having triangular shape having sawtooth shape

- H03K4/48—Generating pulses having essentially a finite slope or stepped portions having triangular shape having sawtooth shape using as active elements semiconductor devices

- H03K4/50—Generating pulses having essentially a finite slope or stepped portions having triangular shape having sawtooth shape using as active elements semiconductor devices in which a sawtooth voltage is produced across a capacitor

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/0092—Arrangements for measuring currents or voltages or for indicating presence or sign thereof measuring current only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0027—Measuring means of, e.g. currents through or voltages across the switch

Abstract

【課題】広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能な電流検出回路を提供する。

【解決手段】高電圧電源1及び負荷2の間に接続された抵抗器R12の両端間に生じる電圧を増幅器31,32で増幅して比較器51,52で鋸波信号の電圧と比較し、鋸波信号の電圧が直線的に漸増又は漸減する傾斜期間における比較器51,52の比較結果を示す信号の長さT2,T3と、上記傾斜期間の長さT1とを検知し、検知した長さの比率に基づいて抵抗器R12に流れる電流を検出する。

【選択図】図1

【解決手段】高電圧電源1及び負荷2の間に接続された抵抗器R12の両端間に生じる電圧を増幅器31,32で増幅して比較器51,52で鋸波信号の電圧と比較し、鋸波信号の電圧が直線的に漸増又は漸減する傾斜期間における比較器51,52の比較結果を示す信号の長さT2,T3と、上記傾斜期間の長さT1とを検知し、検知した長さの比率に基づいて抵抗器R12に流れる電流を検出する。

【選択図】図1

Description

本発明は、電源及び負荷の間で抵抗器を介して流れる電流を検出する電流検出回路に関する。

従来、バッテリ、モータ等の負荷に流れる電流を検出する方法が数多く提案されている。一般的に直流電流を検出するための電流センサには、ホール素子又はシャント抵抗器が用いられている。電流センサによるアナログの検出結果は、必要に応じてデジタル値に変換される。

例えば、特許文献1には、車両のバッテリが充放電する電流の値を、ホール素子を備える電流センサで検出する制御装置が記載されている。この電流センサは鉄心を有しており、残留磁気及びヒステリシスの影響で検出結果にオフセット誤差が含まれるため、特許文献1では、電流センサによる検出結果がオフセット補正装置で補正されるようになっている。

一方、電流センサによる検出結果をA/D変換してデジタル値に変換する場合、例えばマイコン内蔵のA/D変換器ではビット数が不足することがあり、外付けの高価なA/D変換器を用いずに高精度に電流を検出してデジタル値に変換することが望まれる。

これに対し、特許文献2には、PMモータ(永久磁石電動機)に流れる電流を電流センサで検出し、検出結果をΔΣ(デルタ・シグマ)変調器で1ビット信号(ビットストリーム)に変換するモータ制御装置が記載されている。

しかしながら、特許文献1に記載のホール素子を備える電流センサは、広いダイナミックレンジで高精度に電流を検出することが難しく、構造が複雑で比較的高価であるという問題があった。また、特許文献2に記載のΔΣ変調器は、逐次比較方式のA/D変換器と比較して、オーバーサンプリングを行うために消費電力が大きく、且つステップ応答に劣るために変換のセトリング時間が長いという問題があった。

本発明は斯かる事情に鑑みてなされたものであり、その目的とするところは、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能な電流検出回路を提供することにある。

本発明に係る電流検出回路は、電源及び負荷の間で抵抗器を介して流れる電流を検出する電流検出回路において、三角波信号又は鋸波信号を発生する発生部と、該発生部で発生する信号の電圧が直線的に漸増又は漸減する期間を示す信号を生成する第1生成部と、前記抵抗器の両端間の電圧を増幅する増幅部と、該増幅部で増幅した信号の電圧及び前記発生部で発生した電圧を比較する比較部と、前記期間における前記比較部の比較結果を示す信号を生成する第2生成部と、前記第1生成部からの信号の信号幅に対する前記第2生成部からの信号の信号幅の比に基づいて前記抵抗器に流れる電流を検出する検出部とを備えることを特徴とする。

本発明に係る電流検出回路は、前記検出部は、周期信号を計数するカウンタの計数値を、信号幅を検知すべき信号の前縁及び後縁で保持して差分をとることにより、前記第1及び第2生成部夫々からの信号の信号幅を検知することを特徴とする。

本発明に係る電流検出回路は、前記第1及び第2生成部と前記検出部とを電気的に絶縁して前記第1及び第2生成部から前記検出部に信号を伝達する絶縁部を備えることを特徴とする。

本発明に係る電流検出回路は、前記抵抗器の端子の何れか一方の電位を、前記第1及び第2生成部の基準電位とすることを特徴とする。

本発明に係る電流検出回路は、前記第1及び第2生成部からの信号を選択的に切り替えて前記検出部に伝達する選択部を備え、前記検出部は、前記選択部を介して伝達された前記第1生成部からの信号の周期に応じて前記選択部を切り替えることを特徴とする。

本発明にあっては、電源及び負荷の間に接続された抵抗器の両端間に生じる電圧を増幅部で増幅して鋸波信号又は三角波信号の電圧と比較し、鋸波信号又は三角波信号の電圧が直線的に漸増又は漸減する傾斜期間における比較結果を示す信号の長さと、上記傾斜期間を示す信号の長さとを検知し、検知した長さの比率に基づいて上記抵抗器に流れる電流を検出する。

これにより、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗器の抵抗値とに基づいて電流値が検出される。

これにより、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗器の抵抗値とに基づいて電流値が検出される。

本発明にあっては、例えば所謂インプットキャプチャ機能を有するタイマに上記傾斜期間を示す信号及び上記比較結果を示す信号を入力し、夫々の信号の前縁及び後縁で保持されたカウンタの計数値の差分に応じてこれらの信号の長さを検知する。

これにより、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さが高精度に検知される。

これにより、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さが高精度に検知される。

本発明にあっては、上記傾斜期間を示す信号及び上記比較結果を示す信号を生成する生成回路部分と、これらの信号に基づいて電流を検出する検出回路部分とを電気的に絶縁して分離しつつ、上記生成回路部分から上記検出回路部分に信号を伝達する。

これにより、上記検出回路部分を除くその他の回路部分の基準電位の如何にかかわらず、上記抵抗器に流れる電流が検出される。

これにより、上記検出回路部分を除くその他の回路部分の基準電位の如何にかかわらず、上記抵抗器に流れる電流が検出される。

本発明にあっては、抵抗器の両端のうちの何れか一方の電位を基準電位として、上記傾斜期間を示す信号及び上記比較結果を示す信号を生成する。

これにより、上記抵抗器の両端間の微少な電圧が低ノイズで安定に増幅されるため、上記抵抗器に流れる電流が高精度に検出される。

これにより、上記抵抗器の両端間の微少な電圧が低ノイズで安定に増幅されるため、上記抵抗器に流れる電流が高精度に検出される。

本発明にあっては、上記傾斜期間を示す信号及び上記比較結果を示す信号を選択的に切り替えて上記生成回路部分から検出回路部分に伝達する。この切り替えは、上記傾斜期間を示す信号が伝送されているときの信号周期に応じて行われる。

これにより、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅が時系列的に検知される。また、上記比較結果を示す信号が伝達されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流が検出される。

これにより、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅が時系列的に検知される。また、上記比較結果を示す信号が伝達されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流が検出される。

本発明によれば、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗値とに基づいて、時間遅れを伴うフィードバック無しに電流値が検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

以下、本発明をその実施の形態を示す図面に基づいて詳述する。

(実施の形態1)

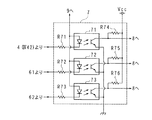

図1は、本発明の実施の形態1に係る電流検出回路の構成例を示すブロック図である。電流検出回路は、高圧のバッテリを含む高電圧電源(電源に相当)1及び負荷2の間に接続された抵抗器R12の両端間の電圧を増幅する増幅器(増幅部に相当)31,32と、鋸波信号を発生する鋸波発生器(発生部に相当)4と、鋸波発生器4が発生した鋸波信号の電圧及び増幅器31,32が増幅した電圧を各別に比較する比較器(比較部に相当)51,52とを備える。鋸波発生器4は、三角波信号を発生する三角波発生器であってもよい。

(実施の形態1)

図1は、本発明の実施の形態1に係る電流検出回路の構成例を示すブロック図である。電流検出回路は、高圧のバッテリを含む高電圧電源(電源に相当)1及び負荷2の間に接続された抵抗器R12の両端間の電圧を増幅する増幅器(増幅部に相当)31,32と、鋸波信号を発生する鋸波発生器(発生部に相当)4と、鋸波発生器4が発生した鋸波信号の電圧及び増幅器31,32が増幅した電圧を各別に比較する比較器(比較部に相当)51,52とを備える。鋸波発生器4は、三角波信号を発生する三角波発生器であってもよい。

電流検出回路は、また、鋸波発生器4からの第2の信号(詳細については後述する)及び比較器51,52の出力信号について負論理のANDを各別にとるAND回路(第2生成部に相当)61,62と、鋸波発生器4及びAND回路61,62を後段の回路から電気的に絶縁して分離しつつ、入力された信号を後段に伝達する絶縁回路(絶縁部に相当)7と、絶縁回路7を介して入力された信号に基づいて抵抗器R12に流れる電流を検出するマイクロコンピュータ(検出部に相当、以下マイコンという)8とを備える。

増幅器31,32、鋸波発生器4、比較器51,52及びAND回路61,62は、抵抗器R12の一端、即ち高電圧電源1及び抵抗器R12の接続点を基準電位としており、この基準電位に対する電源電圧を発生する小信号電源9から電源が供給されている。小信号電源9が供給する電源の電圧は、例えば5Vである。ここでは、抵抗器R12の他端を基準電位にしてもよいが、抵抗器R12に流れる電流が大/小に変化したときに、基準電位が高電圧電源1のマイナス側に対して低/高に変動することに不都合がある場合は、抵抗器R12の一端を基準電位とすることが好ましい。マイコン8及び絶縁回路7は、接地電位を基準電位としており、+5VのVccが供給されている。

増幅器31は、アナログの演算増幅器を含み、出力端子及び反転入力端子の間に抵抗器R31が、非反転入力端子及び抵抗器R12の一端の間に抵抗器R32が、反転入力端子及び抵抗器R12の他端の間に抵抗器R33が夫々接続されている。増幅器32は、演算増幅器を含み、出力端子及び反転入力端子の間に抵抗器R34が、非反転入力端子及び抵抗器R12の他端の間に抵抗器R35が、反転入力端子及び抵抗器R12の一端の間に抵抗器R36が夫々接続されている。

これにより、増幅器31は、抵抗器R12の一端に対する他端の負の電圧信号を反転増幅して正の電圧信号を出力する反転増幅器として動作する。また、増幅器32は、抵抗器R12の一端に対する他端の正の電圧信号を反転せずに増幅して正の電圧信号を出力する非反転増幅器として動作する。なお、本実施の形態1のように、増幅器31及び32を基準電位に対する単一電源で駆動する場合、抵抗器R12の一端に対する他端の電圧が正であるときは、増幅器31の出力信号の電圧(以下、出力電圧という)が0となり、抵抗器R12の一端に対する他端の電圧が負であるときは、増幅器32の出力電圧が0となる。

ここでは、増幅器31及び32夫々の入力オフセット電流を打ち消すために、抵抗器R32の抵抗値は、抵抗器R31及びR33の並列抵抗値と一致させ、抵抗器R35の抵抗値は、抵抗器R34及びR36の並列抵抗値と一致させることが好ましい。また、増幅器31及び32夫々の入力オフセット電圧を打ち消すために、それ自体公知のオフセット補償回路を設けてもよい。更に、抵抗器R21の両端間の電圧をサンプル&ホールドする回路を追加してもよい。

比較器51及び52の夫々は、反転入力端子に増幅器31及び32の出力端子が接続されており、非反転入力端子に鋸波発生器4からの鋸波信号が入力されている。これにより、鋸波信号の電圧が増幅器31及び32夫々の出力電圧を下回る場合(又は上回る場合)、比較器51及び52の出力信号がL(ロウ)レベル(又はH(ハイ)レベル)となる。

AND回路61及び62の夫々は、一の入力端子に比較器51及び52の出力信号が入力されており、他の入力端子に鋸波発生器4からの第2の信号が入力されている。AND回路61及び62の夫々は、第2の信号がLレベルである期間(発生部で発生する信号の電圧が直線的に漸増又は漸減する期間に相当)における比較器51及び52の比較結果を示す信号を出力する。

鋸波信号の立ち下がり時間が無視できる場合は、AND回路61及び62を用いなくてもよい。この場合は、比較器51,52が比較部及び第2生成部に相当する。上記第2の信号及びAND回路61,62の出力信号は、絶縁回路7を介して、所謂インプットキャプチャ機能を有するマイコン8のタイマ用の入力端子に各別に入力される。マイコン8のタイマ用の入力端子に入力される信号のうち、第2の信号は、マイコン8の割込用の入力端子にも入力されており、割込要求を発生する。

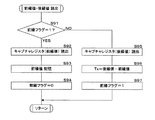

ここで、絶縁回路7について説明する。

図2は、絶縁回路7の構成例を示す回路図である。絶縁回路7は、LED(Light Emitting Diode )及び該LEDが発光したときにオンするフォトトランジスタを含むフォトカプラ71,72,73を有する。各フォトカプラ71,72,73について、LEDのアノードは小信号電源9に接続されており、フォトトランジスタのエミッタは接地電位に接続されている。各フォトカプラ71,72,73は、デジタルアイソレータ、パルストランス等の他のアイソレータに置き換えてもよい。

図2は、絶縁回路7の構成例を示す回路図である。絶縁回路7は、LED(Light Emitting Diode )及び該LEDが発光したときにオンするフォトトランジスタを含むフォトカプラ71,72,73を有する。各フォトカプラ71,72,73について、LEDのアノードは小信号電源9に接続されており、フォトトランジスタのエミッタは接地電位に接続されている。各フォトカプラ71,72,73は、デジタルアイソレータ、パルストランス等の他のアイソレータに置き換えてもよい。

フォトカプラ71に含まれるLEDのカソードは、抵抗器R71を介して鋸波発生器4(より詳しくはインバータIV42の出力端子)に接続されている。フォトカプラ72及び73夫々に含まれるLEDのカソードは、抵抗器R72及びR73を介してAND回路61及び62の出力端子に接続されている。フォトカプラ71に含まれるフォトトランジスタのコレクタは、抵抗器R74によりVccにプルアップされると共にマイコン8のタイマ用の入力端子及び割込用の入力端子に接続されている。フォトカプラ72及び73夫々に含まれるフォトトランジスタのコレクタは、抵抗器R75及び76によりVccにプルアップされると共にマイコン8のタイマ用の入力端子に接続されている。

上述の構成を有する絶縁回路7において、入力側の抵抗器R71,72,73を介してHレベル(又はLレベル)の信号が入力された場合、各LEDが発光せず(又は発光し)、各フォトトランジスタがオフする(又はオンする)ため、マイコン8にHレベル(又はLレベル)の信号が入力される。

図1に戻って、マイコン8は、CPU(Central Processing Unit )81、タイマ82及び割込コントローラ83を有し、これらが不図示のROM(Read Only Memory )及びRAM(Random Access Memory )と共に互いにバス接続されている。タイマ82には、第1タイマ、第2タイマ及び第3タイマが含まれている。

タイマ82に含まれる第1、第2及び第3タイマは、クロック(周期信号に相当)を計数するカウンタの計数値を、夫々のタイマ用の入力端子に入力された信号の立ち下がり及び立ち上がり(信号幅を検知すべき信号の前縁及び後縁に相当)でキャプチャレジスタに保持して割込要求を発生する。CPU81は、キャプチャレジスタに保持された計数値の差分を割込処理で算出して、Lレベルの信号の信号幅を正確に検知することができる。

割込コントローラ83は、割込用の入力端子からの割込要求及びタイマ82からの割込要求を受け付けてCPU81に割込を発生させる。本実施の形態1では、割込用の入力端子に入力された第2の信号の立ち上がりを割込要求として受け付けるが、これに限定されるものではない。

次に、鋸波発生器4について説明する。

図3は、鋸波発生器4の構成例を示す回路図である。鋸波発生器4は、小信号電源9からの電源電圧を分圧する抵抗器R40及びR41からなる分圧器41と、カレントミラー回路42と、小信号電源9からカレントミラー回路42を介して一定の電流で充電されるコンデンサC41と、分圧器41で分圧された電圧及びコンデンサC41の電圧を比較する比較器43と、比較器43の出力信号の立ち上がりを遅延させる遅延器44とを有する。コンデンサ41の電圧は、上述した比較器51及び52の非反転入力端子に入力されている。

図3は、鋸波発生器4の構成例を示す回路図である。鋸波発生器4は、小信号電源9からの電源電圧を分圧する抵抗器R40及びR41からなる分圧器41と、カレントミラー回路42と、小信号電源9からカレントミラー回路42を介して一定の電流で充電されるコンデンサC41と、分圧器41で分圧された電圧及びコンデンサC41の電圧を比較する比較器43と、比較器43の出力信号の立ち上がりを遅延させる遅延器44とを有する。コンデンサ41の電圧は、上述した比較器51及び52の非反転入力端子に入力されている。

カレントミラー回路42は、小信号電源9に抵抗器R42及びR43夫々を介してエミッタが接続されたPNP型のトランジスタQ41及びQ42を含む。トランジスタQ41のコレクタ及びベースとトランジスタQ42のベースとは、抵抗器R44を介して基準電位に接続されている。トランジスタQ42のコレクタは、一端が基準電位に接続されたコンデンサC41の他端に接続されている。この構成により、コンデンサC41の他端には、電圧が直線的に漸増する傾斜期間を有する信号が発生する。

比較器43は、小信号電源9から電源が供給されており、出力端子が抵抗器R45により小信号電源9にプルアップされている。比較器43は、反転入力端子が分圧器41の分圧点に接続されており、非反転入力端子が抵抗器R46を介してコンデンサC41の他端に接続されている。この構成により、コンデンサC41の他端の電圧が分圧器41の分圧電圧を上回った場合、比較器43の出力信号がHレベルとなる。

遅延器44は、比較器43の出力端子に入力端子が接続されたインバータIV41と、インバータIV41の出力電圧を積分する抵抗器R47及びコンデンサC42の直列回路と、抵抗器R47及びコンデンサC42の接続点に入力端子が接続されたシュミットトリガ型のインバータ(第1生成部に相当)IV42とを含む。インバータIV41の出力端子及びインバータIV42の入力端子の間には、カソードがインバータIV41の出力端子側に向けられたショットキバリア型のダイオードD41及び抵抗器R48の直列回路が接続されている。抵抗器R47及びR48夫々の抵抗値は、例えば4.7kΩ及び100Ωであり、コンデンサC42の容量値は、例えば470pFである。この構成により、比較器43の出力電圧の立ち下がりが遅延器44の積分回路により遅延される。

インバータIV42の出力信号は、上述した第2の信号であり、AND回路61及び62の一の入力端子並びに絶縁回路7の入力側に入力されると共に、Nチャネル型のFET(Field Effect Transistor )であるトランジスタQ43のゲートに抵抗器R49を介して印加される。この構成により、比較器43の出力信号がHレベルとなった場合、トランジスタQ43がオンとなり、コンデンサC41に蓄積された電荷が放電する。

次に、高電圧電源1から負荷2に正の電流が流れる場合を例にして、鋸波発生器4を中心に電流検出回路の動作をより詳細に説明する。高電圧電源1から負荷2に負の電流が流れる場合は、以下の説明における増幅器31、比較器51及びAND回路61の夫々を増幅器32、比較器52及びAND回路62と読み替えればよい。

図4は、本発明の実施の形態1に係る電流検出回路の動作を説明するためのタイミング図である。図4に示す7つのタイミング図は、何れも同一の時間軸を横軸としてあり、縦軸には、図の上段から、鋸波信号の電圧(即ちコンデンサC41の電圧)、比較器43の出力信号のレベル、コンデンサC42の電圧、第2の信号(即ちインバータIV42の出力信号)のレベル、トランジスタQ43のオン/オフ状態、比較器51の出力信号のレベル、及びAND回路61の出力信号のレベルを示してある。図中のVthは、分圧器41の分圧電圧であり、鋸波信号のピーク電圧をVpとする。

図4の最上段に示す鋸波信号の電圧が直線的に漸増して時刻t1(又はt11)でVthを上回った場合、比較器43の出力信号がHレベルに立ち上がり、この出力信号がインバータIV41でLレベルに反転されるため、C42の電荷がダイオードD41及び抵抗器R48を介して急速に放電する。その結果、時刻t2(又はt12)でコンデンサC42の電圧がインバータIV42の下側の閾値電圧を下回った場合、インバータIV42の出力信号(即ち第2の信号)がHレベルに立ち上がり、この信号によってトランジスタQ43がオンする。このため、コンデンサC41の電荷が急速に放電して鋸波信号の電圧が急激に低下する。トランジスタQ43がオンする直前の鋸波信号の電圧がVpである。時刻t1からt2(又はt11からt12)までの期間におけるコンデンサC41の電圧の上昇分は、Vpと比較して無視できるほどである。

時刻t2(又はt12)でコンデンサC41の電圧が低下し始めると直ちに比較器43の出力信号がLレベルに立ち下がり、この出力信号がインバータIV41でHレベルに反転されるため、C42が抵抗器R47を介して徐々に充電される。その結果、時刻t3(又はt13)でコンデンサC42の電圧がインバータIV42の上側の閾値電圧を上回った場合、インバータIV42の出力信号(即ち第2の信号)がLレベルに立ち下がり、この信号によってトランジスタQ43がオフする。このため、コンデンサC41への充電が再び開始されて鋸波信号の電圧が直線的に漸増する。なお、コンデンサC41の電荷は、時刻t2からt3(又はt12からt13)までの期間中に完全に放電するように調整される。

一方、鋸波発生器4からの鋸波信号が非反転入力端子に入力される比較器51では、抵抗器R12の両端間の電圧を増幅する増幅器31の出力信号が反転入力端子に入力されているため、鋸波信号の電圧がVpから0に低下する時刻t2からt3(又はt12からt13)までの期間中の何れかの時点で、出力信号がHレベルからLレベルに変化する。これとは逆に、鋸波信号の電圧が0からVpに直線的に漸増する時刻t3からt12までの期間中の例えば時刻t4で、比較器51の出力信号がLレベルからHレベルに変化する。

第2の信号及び比較器51の出力信号について負論理のANDをとるAND回路61の出力信号は、時刻t3(又はt13)でLレベルとなり、時刻t4でHレベルとなる。時刻t3(又はt13)は、鋸波信号の電圧が直線的に漸増する期間の始点である。つまり、AND回路61は、第2の信号がLレベルである期間だけ比較器51からのLレベルの信号を通過させることにより、比較器51からの信号の立ち下がり(前縁)を第2の信号の前縁まで遅らせて出力する。

さて、第2の信号がLレベルである期間、即ち鋸波信号の電圧が直線的に漸増する時刻t3からt12までの期間の長さをT1とし、AND回路61の出力信号がLレベルである時刻t3からt4までの期間の長さをT2とした場合、時刻t4における鋸波信号の電圧はVp×(T2/T1)である。この電圧は、時刻t4で比較器51の反転入力端子に入力される電圧、即ち増幅器31の出力電圧に等しいので、抵抗器R12を介して高電圧電源1から負荷2に流れる電流iは、以下の式(1)により算出される。なお、負荷2から高電圧電源1に流れる電流iを検出する場合は、AND回路62の出力信号がLレベルである期間の長さT3を検知し、式(1)におけるT2をT3に、βを増幅器32の増幅率の絶対値に夫々置き換えればよい。

i=Vp×(T2/T1)/(r×β)・・・・・・・・・・・・・・・・・・・(1)

但し、

r:抵抗器R12の抵抗値

β:増幅器31の増幅率の絶対値

但し、

r:抵抗器R12の抵抗値

β:増幅器31の増幅率の絶対値

次に、電流iの検出精度について説明する。上述したように、第2の信号及びAND回路61の出力信号は、絶縁回路7を介してマイコン8のタイマ用の入力端子に各別に入力されており、キャプチャレジスタに保持されたカウンタの計数値の差分に基づいてT1及びT2が各別に検知される。T1及びT2は、式(1)で用いられる数値であるから、必ずしも時間に換算して検知する必要はない。

タイマ82のカウンタが計数するクロックの周波数をfとした場合、T1及びT2はクロックの周期に相当する1/fの精度で検知される。この場合、T1をnビット(nは自然数)以上の数値として、所謂nビット以上の分解能で検知するには、第2の信号がLレベルである期間、即ち鋸波信号の電圧が直線的に漸増する期間の長さtが、以下の式(2)で表されるようにすればよい。

t≧2^n/f・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

但し、「^」は冪乗を表す。

但し、「^」は冪乗を表す。

一方、CPU81が並列処理可能なビット数がm(mはn以上の自然数)である場合、tは式(2)を考慮して以下の式(3)で示される範囲内の長さにすればよい。

2^n/f≦t≦2^m/f・・・・・・・・・・・・・・・・・・・・・・・・(3)

例えば上述のクロックの周波数が32MHzである場合、T1を15ビットの分解能で検知するには、式(2)における境界値としてt=1024μsとすればよい。また例えば、鋸波信号のピーク電圧Vpが2.0Vとなるように調整し、コンデンサC41の容量値をC=0.1μFとした場合、カレントミラー回路42がコンデンサC41に流入させるべき一定の電流Iは、I×t=C×Vpの関係式より、I=195μAとなる。

電流iの検出精度を低下させる要因としては、小信号電源9の電圧変動、分圧器41の分圧比を決定する抵抗器R40及びR41の抵抗値の変動、高電圧電源1及び負荷2の間に接続された抵抗器R12の抵抗値の変動、増幅器31及び32の増幅率の変動等が挙げられる。なお、その電圧が鋸波信号の電圧となるコンデンサC41については、容量値の変動が式(1)におけるT1の変動となって現れるが、T2も同率で変動するため、式(1)の算出結果に影響を与えることはない。

一方、抵抗器R40及びR41については、抵抗値の変動が分圧比に影響を与えないように温度特性等を選択することが好ましい。また、増幅器31の増幅率の絶対値は、抵抗器R33の抵抗値に対する抵抗器R31の抵抗値の比の値であり、増幅器32の増幅率の絶対値は、抵抗器R36の抵抗値に対する抵抗器R34の抵抗値の比の値に1を加算した値であって、これらの増幅率についても抵抗値の変動の影響が相殺するようにしておくことが好ましい。

以下では、上述したマイコン8の動作を、それを示すフローチャートを用いて詳述する。以下に示す処理は、不図示のROMに予め格納されている制御プログラムに従って、CPU81により実行される。

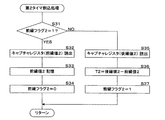

図5は、周期信号割込処理におけるCPU81の処理手順を示すフローチャートであり、図6、図7及び図8の夫々は、第1タイマ割込処理、第2タイマ割込処理及び第3タイマ割込処理におけるCPU81の処理手順を示すフローチャートである。図5の割込処理は、第2の信号の立ち上がりで実行される。図6、図7及び図8夫々の割込処理は、第2の信号、AND回路61の出力信号及びAND回路62の出力信号により、第1タイマ、第2タイマ及び第3タイマのキャプチャレジスタに計数値が保持された時に実行される。

図5は、周期信号割込処理におけるCPU81の処理手順を示すフローチャートであり、図6、図7及び図8の夫々は、第1タイマ割込処理、第2タイマ割込処理及び第3タイマ割込処理におけるCPU81の処理手順を示すフローチャートである。図5の割込処理は、第2の信号の立ち上がりで実行される。図6、図7及び図8夫々の割込処理は、第2の信号、AND回路61の出力信号及びAND回路62の出力信号により、第1タイマ、第2タイマ及び第3タイマのキャプチャレジスタに計数値が保持された時に実行される。

図5の処理で用いるr及びβ夫々は、既に述べたとおり抵抗器R12の抵抗値及び増幅器31,32の増幅率の絶対値である。また、T3は、AND回路62の出力信号がLレベルである期間の長さである。図6、図7及び図8夫々の処理で用いる前縁フラグ1、前縁フラグ2及び前縁フラグ3は、信号幅を検知すべき信号の前縁における割込処理であることを示すフラグであり、不図示のRAMに記憶される。T2及びT3は処理値を0としてRAMに記憶される。T1は、直前に検知された値がRAMに記憶されている。図5の処理で算出される電流iは、高電圧電源1から負荷2に向けて流れる電流を正の電流とする。

図5の周期信号割込処理が実行された場合、CPU81は、RAMに記憶したT3が0であるか否かを判定する(S11)。T3が0である場合(S11:YES)、即ち第2の信号による前回の周期信号割込処理以降にT3が検知されていない場合、CPU81は、T2をT1で除算してDUTYとし(S12)、次回の周期信号割込処理のためにT2を0とする(S13)。その後、CPU81は、Vpをr×βで除算した結果にDUTYを乗算して電流iを算出し(S14)、割り込まれたルーチンにリターンする。なお、第2の信号による前回の周期信号割込処理以降にT2及びT3が共に検知されていない場合、i=0と算出される。

一方、ステップS11でT3が0ではない場合(S11:NO)、CPU81は、T3をT1で除算してDUTYとし(S15)、次回の周期信号割込処理のためにT3を0とする(S16)。その後、CPU81は、Vpをr×βで除算した結果にDUTYを乗算して負の電流iを算出し(S17)、割り込まれたルーチンにリターンする。

次に、図6に示す第1タイマ割込処理が実行された場合、CPU81は、前縁フラグ1が1であるか否かを判定し(S21)、1である場合(S21:YES)、CPU81は、キャプチャレジスタの内容を前縁値1として読み出して(S22)RAMに記憶する(S23)。その後、CPU81は、前縁フラグ1を0にクリアして(S24)、割り込まれたルーチンにリターンする。

一方、ステップS21で前縁フラグ1が1ではない場合(S21:NO)、CPU81は、キャプチャレジスタの内容を後縁値1として読み出し(S25)、後縁値1からRAMに記憶した前縁値1を減算してT1を算出する(S26)。算出されたT1はRAMに記憶される(図示を省略、以下同様)。その後、CPU81は、T1が所定値より大きいか否かを判定し(S27)、大きくない場合(S27:NO)、ステップS28以降をスキップして割り込まれたルーチンにリターンする。

ステップS27でT1と所定値とを比較するのは、算出されたT1が、図4に示す時刻t2からt3までの期間(即ち第2の信号がHレベルである期間)の長さであった場合のT1を廃棄するためである。所定値は、時刻t3からt12までの期間の長さより小さく、時刻t2からt3までの期間の長さより大きい値にしておく。ステップS27から直ちにリターンした場合に、次回の第1タイマ割込処理で算出されるT1は、時刻t2からt12までの期間の長さであり、実際のT1より大きい。但し、その後の第1タイマ割込処理にて、時刻t3からt12までの期間の長さがT1として正しく算出される。

ステップS27でT1が所定値より大きい場合(S27:YES)、CPU81は、次回の第1タイマ割込処理のために前縁フラグ1を1にセットし(S28)、更に第2タイマ割込処理のために前縁フラグ2を1にセットする(S29)と共に、第3タイマ割込処理のために前縁フラグ3を1にセットして(S30)、割り込まれたルーチンにリターンする。

次の図7に示す第2タイマ割込処理におけるステップS31からS35までの処理は、図6に示した第1割込処理におけるステップS21からS25までの処理における前縁フラグ1、前縁値1及び後縁値1の夫々を、前縁フラグ2、前縁値2及び後縁値2に置き換えたものであるため、その説明を省略する。

ステップS35で、キャプチャレジスタの内容を後縁値2として読み出したCPU81は、後縁値2からRAMに記憶した前縁値2を減算してT2を算出する(S36)。その後、CPU81は、次回の第2タイマ割込処理のために前縁フラグ2を1にセットして(S37)、割り込まれたルーチンにリターンする。

次の図8に示す第3タイマ割込処理におけるステップS41からS45までの処理は、図7に示した第2割込処理におけるステップS31からS35までの処理における前縁フラグ2、前縁値2及び後縁値2の夫々を、前縁フラグ3、前縁値3及び後縁値3に置き換えたものであるため、その説明を省略する。

ステップS45で、キャプチャレジスタの内容を後縁値3として読み出したCPU81は、後縁値3からRAMに記憶した前縁値3を減算してT3を算出する(S46)。その後、CPU81は、次回の第3タイマ割込処理のために前縁フラグ3を1にセットして(S47)、割り込まれたルーチンにリターンする。

以上のように本実施の形態1によれば、高電圧電源1及び負荷2の間に接続された抵抗器R12の両端間に生じる電圧を増幅器31,32で増幅して比較器51,52で鋸波信号の電圧と比較し、鋸波信号の電圧が直線的に漸増する傾斜期間における比較器51,52の比較結果を示す信号の長さT2,T3と、上記傾斜期間を示す信号の長さT1とを検知し、検知した長さの比率に基づいて抵抗器R12に流れる電流を検出する。

これにより、鋸波信号のピーク電圧Vpに対する増幅器31,32の出力電圧の比率が算出され、この比率と、ピーク電圧Vp、増幅器31,32の増幅率の絶対値β及び抵抗器R12の抵抗値rとに基づいて電流値iが検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

これにより、鋸波信号のピーク電圧Vpに対する増幅器31,32の出力電圧の比率が算出され、この比率と、ピーク電圧Vp、増幅器31,32の増幅率の絶対値β及び抵抗器R12の抵抗値rとに基づいて電流値iが検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

また、実施の形態1によれば、所謂インプットキャプチャ機能を有するタイマ82に上記傾斜期間を示す第2の信号及び上記比較結果を示すAND回路61,62の出力信号を入力し、夫々の信号の前縁及び後縁で保持されたカウンタの計数値の差分に応じてこれらの信号の長さを検知する。

従って、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さを高精度に検知することが可能となる。

従って、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さを高精度に検知することが可能となる。

更に、実施の形態1によれば、上記傾斜期間を示す信号及び上記比較結果を示す信号を夫々生成する鋸波発生器4及びAND回路61,62と、これらの信号に基づいて電流を検出するマイコン8とを絶縁回路7で電気的に絶縁して分離しつつ、鋸波発生器4及びAND回路61,62からマイコン8に信号を伝達する。

従って、マイコン8を除くその他の回路部分の基準電位の如何にかかわらず、抵抗器R12に流れる電流を検出することが可能となる。

従って、マイコン8を除くその他の回路部分の基準電位の如何にかかわらず、抵抗器R12に流れる電流を検出することが可能となる。

更にまた、実施の形態1によれば、抵抗器R12の両端間の微少な電圧が低ノイズで安定に増幅されるため、抵抗器R12に流れる電流を高精度に検出することが可能となる。

なお、実施の形態1にあっては、鋸波信号における電圧が直線的に漸増する期間を傾斜期間としたが、これに限定されるものではない。例えば、図4に示す時刻t3からt12までの期間に対応する期間中に鋸波信号の電圧が右肩下がりに漸減する場合は、この期間を傾斜期間としてもよい。この場合、AND回路61は、第2の信号がLレベルである期間だけ比較器51からのLレベルの信号を通過させることにより、比較器51からの信号の立ち上がり(後縁)を第2の信号の後縁まで早めて出力する。

また例えば、図4に示す時刻t2からt3までの期間中に鋸波信号の電圧が直線的に漸減する場合は、この期間を傾斜期間としてもよいし、鋸波信号の電圧が直線的に漸増及び漸減する両期間を連結して傾斜期間としてもよい。

上記の2つの場合のうち、前者の場合は、第2の信号がHレベルである期間により上述の傾斜期間が示されるから、第2の信号を反転させた信号をAND回路61,62の他の入力端子及び絶縁回路に入力すればよい。後者の場合は、傾斜期間の長さと鋸波信号の周期とが実質的に一致するため、図4に示す第2の信号を、時刻t2で立ち上がって直ぐに立ち下がる細いパルスにすればよい。この場合は更に、不要なAND回路61,62を削減して、比較器51,52の出力信号を絶縁回路7に入力すればよい。AND回路61,62を削減した場合は、比較器51,52が比較部及び第2生成部に相当する。

更に例えば、鋸波信号に代えて三角波信号を用いてもよい。この場合、三角波信号の電圧が漸増する期間、漸減する期間及び両期間を連結した期間のうち、何れの期間を傾斜期間にしてもよい。何れの期間を傾斜期間とする場合であっても、電流検出回路の動作は、前述の内容で説明し尽くされている。

(変形例)

実施の形態1が、比較器51,52の出力信号をAND回路61,62及び絶縁回路7を介してマイコン8に伝達する形態であるのに対し、実施の形態1の変形例は、比較器51,52の出力信号のORをとった信号をAND回路61及び絶縁回路7を介してマイコン8に伝達する形態である。

実施の形態1が、比較器51,52の出力信号をAND回路61,62及び絶縁回路7を介してマイコン8に伝達する形態であるのに対し、実施の形態1の変形例は、比較器51,52の出力信号のORをとった信号をAND回路61及び絶縁回路7を介してマイコン8に伝達する形態である。

図9は、本発明の実施の形態1の変形例に係る電流検出回路の構成例を示すブロック図である。図9に示す電流検出回路は、実施の形態1の図1に示す電流検出回路と比較して、AND回路62が削減されており、且つ、比較器51及び52の出力信号について負論理のORをとるOR回路63が追加されており、OR回路63の出力端子がAND回路61の一の入力端子に接続されている点が異なる。従って、絶縁回路7は2つのフォトカプラ71,72を含む2回路があれば十分であり、マイコン8のタイマ82には第3タイマが含まれていなくてもよい。

本変形例では、実施の形態1におけるT2及びT3が区別されることなく検知されるため、図4に示したタイミング図と同じタイミング図を用いて電流検出回路の動作を説明することができる。また、図5に示した周期信号割込処理では、ステップS11の判定処理及びステップS15からS17までの処理が不要となる。更に、図8に示した第3タイマ割込処理の全体が不要となる。その他については、実施の形態1の場合と同様である。

以上のように本実施の形態1の変形例によれば、検出される電流の正負が区別されない点を除けば、内蔵するタイマ数が少ないマイコンを用いた場合であっても、実施の形態1と同様の効果を奏する。

(実施の形態2)

実施の形態1が、マイコン8のタイマ82にて3つの信号(第2の信号及びAND回路61,62の出力信号)の信号幅を並列的に検知する形態であるのに対し、実施の形態2は、タイマ82にて上記3つの信号の信号幅を時系列的に検知する形態である。

実施の形態1が、マイコン8のタイマ82にて3つの信号(第2の信号及びAND回路61,62の出力信号)の信号幅を並列的に検知する形態であるのに対し、実施の形態2は、タイマ82にて上記3つの信号の信号幅を時系列的に検知する形態である。

図10は、本発明の実施の形態2に係る電流検出回路の構成例を示すブロック図である。図10に示す電流検出回路は、実施の形態1の図1に示す電流検出回路と比較して、絶縁回路7及びマイコン8の間にマルチプレクサ(選択部に相当、以下MUXという)85が接続されており、マイコン8に出力ポート84が追加されている点が異なる。MUX85からの出力信号は、マイコン8の第1及び第2タイマ用の入力端子に入力されている。マイコン8の割込用入力端子には、信号が入力されていない。

タイマ82は、第1タイマにより、第1タイマ用の入力端子に入力された信号の信号幅を検知し、第2タイマにより、第2タイマ用の入力端子に入力された第2の信号の周期を検知するか、又はMUX85の選択を切り替える周期を計時する。マイコン8のタイマ82には第3タイマが含まれていなくてもよい。第1タイマは、実施の形態1と同様に第1タイマ用の入力端子に入力された信号の立ち下がり及び立ち上がりでカウンタの計数値をキャプチャレジスタに保持して割込要求を発生する。第2タイマは、第2タイマ用の入力端子に入力された第2の信号の周期を検知する場合に、第2の信号の立ち上がりでカウンタの計数値をキャプチャレジスタに保持して割込要求を発生する。第2タイマが周期を計時する場合は、インプットキャプチャ機能が解除される。

MUX85は、Vccから電源が供給されており、4つの被選択入力端子に入力された信号を、マイコン8からの2ビットの選択信号の組み合わせにより選択的に切り替えて、マイコン8の第1及び第2タイマ用の入力端子に伝達すべく出力する。

MUX85の第1から第3の被選択入力端子には、前述の第2の信号及びAND回路61,62の出力信号が、絶縁回路7を介して各別に入力されている。MUX85の第4の被選択入力端子は、接地電位に接続されている。MUX85の2つの選択入力端子には、マイコン8が有する出力ポート84から2ビットの選択信号が入力される。この構成により、CPU81が第2の信号及びAND回路61,62の出力信号のうち、何れの信号をも選択しない場合(以下、この状態を非選択という)は、MUX85から強制的にLレベルの信号が出力される。

次に、高電圧電源1から負荷2に正の電流が流れる場合を例にして、鋸波発生器4の動作をより詳細に説明する。

図11は、本発明の実施の形態2に係る電流検出回路の動作を説明するためのタイミング図である。図11に示す6つのタイミング図は、何れも同一の時間軸を横軸としてあり、縦軸には、図の上段から、第2の信号のレベル、AND回路61の出力信号のレベル、AND回路62の出力信号のレベル、タイマ82に含まれる第1タイマによる検知フェーズの区別、MUX85の出力信号のレベル、及びタイマ82に含まれる第2タイマによる周期タイマの動作期間を示してある。

図11は、本発明の実施の形態2に係る電流検出回路の動作を説明するためのタイミング図である。図11に示す6つのタイミング図は、何れも同一の時間軸を横軸としてあり、縦軸には、図の上段から、第2の信号のレベル、AND回路61の出力信号のレベル、AND回路62の出力信号のレベル、タイマ82に含まれる第1タイマによる検知フェーズの区別、MUX85の出力信号のレベル、及びタイマ82に含まれる第2タイマによる周期タイマの動作期間を示してある。

図11で、第1タイマによる検知フェーズに示されたT1検知フェーズ、T2検知フェーズ及びT3検知フェーズの夫々は、CPU81が、第2の信号、AND回路61の出力信号及びAND回路62の出力信号を選択すべく選択信号を出力しているフェーズを表す。検知フェーズの区別は不図示のRAMに記憶されており、初期状態はT1検知フェーズである。

T1検知フェーズが継続している状態では、MUX85の被選択入力端子に入力される信号のうち第2の信号が選択されているから、時刻t2及びt12における第2の信号の立ち上がりで第2タイマのカウンタの計数値がキャプチャレジスタに保持されて割込要求が発生する。CPU81は、この割込要求に対する割込処理にて、第2の信号の周期T0を検知する。

その後、CPU81は、検知フェーズをT2検知フェーズに更新すると共に、MUX85の被選択入力端子に入力される信号のうちAND回路61の出力信号を選択すべく出力ポート84から選択信号を出力する。CPU81は、更に、第2タイマを用いて周期T0の周期タイマを起動する。

T1検知フェーズでは、更に、時刻t3及びt12における第2の信号の立ち下がり及び立ち上がりで第1タイマのカウンタの計数値がキャプチャレジスタに保持されて割込要求が発生する。CPU81は、この割込要求に対する割込処理にて、第2の信号がLレベルである期間の長さT1を検知する。

続くT2検知フェーズでは、MUX85の被選択入力端子に入力される信号のうちAND回路61の出力信号が選択されているから、時刻t13及びt14におけるAND回路61の出力信号の立ち下がり及び立ち上がりで第1タイマのカウンタの計数値がキャプチャレジスタに保持されて割込要求が発生する。CPU81は、この割込要求に対する割込処理にて、AND回路61の出力信号がLレベルである期間の長さT2を検知する。

時刻t22で第2タイマによる周期タイマがタイムアップして割込要求が発生した場合、CPU81は、この割込要求に対する割込処理にて、検知フェーズをT3検知フェーズに更新すると共に、MUX85の被選択入力端子に入力される信号のうちAND回路62の出力信号を選択すべく出力ポート84から選択信号を出力する。CPU81は、更に、第2タイマを用いて周期T0の周期タイマを再起動する。

続くT3検知フェーズでは、MUX85の被選択入力端子に入力される信号のうちAND回路62の出力信号が選択されているが、本実施の形態2ではこの出力信号がHレベルに維持されているため、AND回路62の出力信号がLレベルである期間の長さT3が検知されることはない。それにもかかわらず、第2タイマによる周期タイマが時刻t32でタイムアップすることにより、CPU81は、T3検知フェーズを時刻t32で終了させることができる。

時刻t32で第2タイマによる周期タイマがタイムアップして割込要求が発生した場合、CPU81は、この割込要求に対する割込処理にて、検知フェーズをT1検知フェーズに更新した後、第2タイマをインプットキャプチャの設定に変更する。CPU81は、更に、MUX85の被選択入力端子に入力される信号のうち接地電位の信号を極く短時間だけ選択した後、第2の信号を選択すべく出力ポート84から選択信号を出力する。これにより、MUX85の出力信号が、時刻t32で必ず立ち上がることとなる。つまり、時刻t32以降のT1検知フェーズでは、時刻t2以降のT1検知フェーズと全く同じ動作が繰り返される。

以下では、上述したマイコン8の動作を、それを示すフローチャートを用いて詳述する。以下に示す処理は、不図示のROMに予め格納されている制御プログラムに従って、CPU81により実行される。

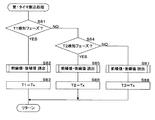

図12は、第2タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図13は、周期タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図14は、第1タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図15は、前縁値・後縁値読出のサブルーチンに係るCPU81の処理手順を示すフローチャートである。図12及び14の割込処理は、夫々第2タイマ及び第1タイマのキャプチャレジスタに計数値が保持された時に実行される。図13の割込処理は、第2タイマによる周期タイマがタイムアップした時に実行される。

図12は、第2タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図13は、周期タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図14は、第1タイマ割込処理におけるCPU81の処理手順を示すフローチャートであり、図15は、前縁値・後縁値読出のサブルーチンに係るCPU81の処理手順を示すフローチャートである。図12及び14の割込処理は、夫々第2タイマ及び第1タイマのキャプチャレジスタに計数値が保持された時に実行される。図13の割込処理は、第2タイマによる周期タイマがタイムアップした時に実行される。

図12の処理で用いる開始フラグは、周期を検知すべき信号の開始時点における割込処理であることを示すフラグであり、不図示のRAMに記憶される。図14の処理で用いる前縁フラグは、信号幅を検知すべき信号の前縁における割込処理であることを示すフラグであり、RAMに記憶される。検知フェーズの区別もRAMに記憶される。T2及びT3は処理値を0としてRAMに記憶される。T1は、直前に検知された値がRAMに記憶されている。第2タイマは、インプットキャプチャの設定になっている。

図12の第2タイマ割込処理が実行された場合、CPU81は、現在がT1検知フェーズであるか否かを判定し(S51)、T1検知フェーズではない場合(S51:NO)、何も処理せずに割り込まれたルーチンにリターンする。一方、現在がT1検知フェーズである場合(S51:YES)、CPU81は、開始フラグが1であるか否かを判定し(S52)、1である場合(S52:YES)、キャプチャレジスタの内容を開始値として読み出して(S53)RAMに記憶する(S54)。

その後、CPU81は、前縁フラグを0にクリアし(S55)、電流検出に係るサブルーチンを呼び出して実行した(S56)後、割り込まれたルーチンにリターンする。

なお、電流検出に係るサブルーチンの処理内容は、時刻t2より前に検知されたT1、T2及びT3に基づいて電流iを検出するものであり、実施の形態1の図5に示す周期信号割込処理におけるステップS11からS17までの内容と全く同一であるため、フローチャートの図示及びその説明を省略する。

なお、電流検出に係るサブルーチンの処理内容は、時刻t2より前に検知されたT1、T2及びT3に基づいて電流iを検出するものであり、実施の形態1の図5に示す周期信号割込処理におけるステップS11からS17までの内容と全く同一であるため、フローチャートの図示及びその説明を省略する。

ステップS52で、開始フラグが1ではない場合(S52:NO)、CPU81は、キャプチャレジスタの内容を終了値として読み出し(S57)、終了値からRAMに記憶した開始値を減算してT0を算出する(S58)。算出されたT0はRAMに記憶される(図示を省略、以下同様)。その後、CPU81は、次回の第2タイマ割込処理のために開始フラグを1にセットし(S59)、検知フェーズをT2検知フェーズに更新した(S60)後、MUX85の被選択入力端子に入力される信号のうちAND回路61の出力信号を選択すべく出力ポート84から選択信号を出力する(S61)。

次いで、CPU81は、第2タイマについて、インプットキャプチャの設定を解除すべく設定変更し(S62)、第2タイマによる周期タイマをスタートさせて(S63)割り込まれたルーチンにリターンする。この場合に周期タイマに設定される周期は、ステップS58で算出したT0である。

次に、図13に示す周期タイマ割込処理が実行された場合、CPU81は、現在がT2検知フェーズであるか否かを判定し(S71)、T2検知フェーズである場合(S71:YES)、検知フェーズをT3検知フェーズに更新する(S72)。その後、CPU81は、MUX85の被選択入力端子に入力される信号のうちAND回路62の出力信号を選択すべく出力ポート84から選択信号を出力し(S73)、第2タイマによる周期タイマを再スタートさせて(S74)割り込まれたルーチンにリターンする。

ステップS71で、現在がT2検知フェーズではない場合(S71:NO)、即ちT3検知フェーズである場合、CPU81は、検知フェーズをT1検知フェーズに更新した(S75)後、第2タイマを再びインプットキャプチャに設定変更する(S76)。更に、CPU81は、一旦MUX85を非選択にした(S77)後、MUX85の被選択入力端子に入力される信号のうち、第2の信号を選択すべく出力ポート84から選択信号を出力して(S78)、割り込まれたルーチンにリターンする。

次に、図14に示す第1タイマ割込処理が実行された場合、CPU81は、現在がT1検知フェーズであるか否かを判定し(S81)、T1検知フェーズである場合(S81:YES)、前縁値・後縁値読出に係るサブルーチンを呼び出して実行し(S82)、サブルーチンで算出されたTxをT1に代入して(S83)割り込まれたルーチンにリターンする。

ステップS81で、現在がT1検知フェーズではない場合(S81:NO)、CPU81は、現在がT2検知フェーズであるか否かを判定し(S84)、T2検知フェーズである場合(S84:YES)、前縁値・後縁値読出に係るサブルーチンを呼び出して実行し(S85)、サブルーチンで算出されたTxをT2に代入して(S86)割り込まれたルーチンにリターンする。

ステップS84で、現在がT2検知フェーズではない場合(S84:NO)、即ちT3検知フェーズである場合、CPU81は、前縁値・後縁値読出に係るサブルーチンを呼び出して実行し(S87)、サブルーチンで算出されたTxをT3に代入して(S88)割り込まれたルーチンにリターンする。

次に、図15に示す前縁値・後縁値読出に係るサブルーチンが呼び出された場合、CPU81は、前縁フラグが1であるか否かを判定する(S91)。前縁フラグが1である場合(S91:YES)、CPU81は、キャプチャレジスタの内容を前縁値として読み出して(S92)RAMに記憶し(S93)、前縁フラグを0にクリアして(S94)、呼び出されたルーチンにリターンする。

一方、ステップS91で前縁フラグが1ではない場合(S91:NO)、CPU81は、キャプチャレジスタの内容を後縁値として読み出し(S95)、後縁値からRAMに記憶した前縁値を減算してTxを算出する(S96)。算出されたTxはRAMに記憶される(図示を省略)。その後、CPU81は、前縁フラグを1にセットして(S97)、呼び出されたルーチンにリターンする。

以上のように本実施の形態2によれば、上述の傾斜期間を示す信号及び比較結果を示す信号をMUX85で選択的に切り替えて鋸波発生器4及びAND回路61,62からマイコン8に伝達する。この切り替えは、上記傾斜期間を示す信号が伝送されているときの信号周期T0に応じて行われる。

従って、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅を時系列的に検知することが可能となり、マイコン8で使用するタイマ数が1つ削減される。なお、上記比較結果を示す信号が伝送されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流を検出することが可能となる。

従って、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅を時系列的に検知することが可能となり、マイコン8で使用するタイマ数が1つ削減される。なお、上記比較結果を示す信号が伝送されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流を検出することが可能となる。

今回開示された実施の形態は、全ての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上述した意味ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内での全ての変更が含まれることが意図される。また、各実施の形態で記載されている技術的特徴は、お互いに組み合わせることが可能である。

1 高電圧電源

2 負荷

31、32 増幅器

4 鋸波発生器

41 分圧器

42 カレントミラー回路

44 遅延器

51、52 比較器

61、62 AND回路

63 OR回路

7 絶縁回路

71、72、73 フォトカプラ

8 マイコン

81 CPU

82 タイマ

83 割込コントローラ

84 出力ポート

85 MUX

9 小信号電源

C41、C42 コンデンサ

IV41、IV42 インバータ

Q43 トランジスタ

2 負荷

31、32 増幅器

4 鋸波発生器

41 分圧器

42 カレントミラー回路

44 遅延器

51、52 比較器

61、62 AND回路

63 OR回路

7 絶縁回路

71、72、73 フォトカプラ

8 マイコン

81 CPU

82 タイマ

83 割込コントローラ

84 出力ポート

85 MUX

9 小信号電源

C41、C42 コンデンサ

IV41、IV42 インバータ

Q43 トランジスタ

本発明の一態様に係る電流検出回路は、電源及び負荷の間で抵抗器を介して流れる電流を検出する電流検出回路において、三角波信号又は鋸波信号を発生する発生部と、該発生部で発生する信号の電圧が直線的に漸増又は漸減する期間を示す信号を生成する第1生成部と、前記抵抗器の両端間の電圧を増幅する増幅部と、該増幅部で増幅した信号の電圧及び前記発生部で発生した電圧を比較する比較部と、前記期間における前記比較部の比較結果を示す信号を生成する第2生成部と、前記第1生成部からの信号の信号幅に対する前記第2生成部からの信号の信号幅の比に基づいて前記抵抗器に流れる電流を検出する検出部とを備えることを特徴とする。

本発明の一態様に係る電流検出回路は、前記検出部は、周期信号を計数するカウンタの計数値を、信号幅を検知すべき信号の前縁及び後縁で保持して差分をとることにより、前記第1及び第2生成部夫々からの信号の信号幅を検知することを特徴とする。

本発明の一態様に係る電流検出回路は、前記第1及び第2生成部と前記検出部とを電気的に絶縁して前記第1及び第2生成部から前記検出部に信号を伝達する絶縁部を備えることを特徴とする。

本発明の一態様に係る電流検出回路は、前記抵抗器の端子の何れか一方の電位を、前記第1及び第2生成部の基準電位とすることを特徴とする。

本発明の一態様に係る電流検出回路は、前記第1及び第2生成部からの信号を選択的に切り替えて前記検出部に伝達する選択部を備え、前記検出部は、前記選択部を介して伝達された前記第1生成部からの信号の周期に応じて前記選択部を切り替えることを特徴とする。

本態様にあっては、電源及び負荷の間に接続された抵抗器の両端間に生じる電圧を増幅部で増幅して鋸波信号又は三角波信号の電圧と比較し、鋸波信号又は三角波信号の電圧が直線的に漸増又は漸減する傾斜期間における比較結果を示す信号の長さと、上記傾斜期間を示す信号の長さとを検知し、検知した長さの比率に基づいて上記抵抗器に流れる電流を検出する。

これにより、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗器の抵抗値とに基づいて電流値が検出される。

これにより、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗器の抵抗値とに基づいて電流値が検出される。

本態様にあっては、例えば所謂インプットキャプチャ機能を有するタイマに上記傾斜期間を示す信号及び上記比較結果を示す信号を入力し、夫々の信号の前縁及び後縁で保持されたカウンタの計数値の差分に応じてこれらの信号の長さを検知する。

これにより、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さが高精度に検知される。

これにより、例えば信号の前縁及び後縁における割込処理で逐次変化するカウンタの計数値を読み出して時間差を検知する場合と比較して、上記傾斜期間を示す信号の長さ及び上記比較結果を示す信号の長さが高精度に検知される。

本態様にあっては、上記傾斜期間を示す信号及び上記比較結果を示す信号を生成する生成回路部分と、これらの信号に基づいて電流を検出する検出回路部分とを電気的に絶縁して分離しつつ、上記生成回路部分から上記検出回路部分に信号を伝達する。

これにより、上記検出回路部分を除くその他の回路部分の基準電位の如何にかかわらず、上記抵抗器に流れる電流が検出される。

これにより、上記検出回路部分を除くその他の回路部分の基準電位の如何にかかわらず、上記抵抗器に流れる電流が検出される。

本態様にあっては、抵抗器の両端のうちの何れか一方の電位を基準電位として、上記傾斜期間を示す信号及び上記比較結果を示す信号を生成する。

これにより、上記抵抗器の両端間の微少な電圧が低ノイズで安定に増幅されるため、上記抵抗器に流れる電流が高精度に検出される。

これにより、上記抵抗器の両端間の微少な電圧が低ノイズで安定に増幅されるため、上記抵抗器に流れる電流が高精度に検出される。

本態様にあっては、上記傾斜期間を示す信号及び上記比較結果を示す信号を選択的に切り替えて上記生成回路部分から検出回路部分に伝達する。この切り替えは、上記傾斜期間を示す信号が伝送されているときの信号周期に応じて行われる。

これにより、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅が時系列的に検知される。また、上記比較結果を示す信号が伝達されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流が検出される。

これにより、上記傾斜期間を示す信号の信号幅及び上記比較結果を示す信号の信号幅が時系列的に検知される。また、上記比較結果を示す信号が伝達されている間に信号幅が検知されない場合は、値が0の信号幅に対応して値が0の電流が検出される。

上記によれば、鋸波信号又は三角波信号のピーク電圧に対する増幅部の出力電圧の比率が算出され、この比率と、上記ピーク電圧の値、増幅部の増幅率及び抵抗値とに基づいて、時間遅れを伴うフィードバック無しに電流値が検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

増幅器31,32、鋸波発生器4、比較器51,52及びAND回路61,62は、抵抗器R12の一端、即ち高電圧電源1の一端及び抵抗器R12の接続点を基準電位としており、この基準電位に対する電源電圧を発生する小信号電源9から電源が供給されている。小信号電源9が供給する電源の電圧は、例えば5Vである。ここでは、抵抗器R12の他端を基準電位にしてもよいが、抵抗器R12に流れる電流が大/小に変化したときに、基準電位が高電圧電源1の一端に対して低/高に変動することに不都合がある場合は、抵抗器R12の一端を基準電位とすることが好ましい。マイコン8及び絶縁回路7は、接地電位を基準電位としており、+5VのVccが供給されている。

フォトカプラ71に含まれるLEDのカソードは、抵抗器R71を介して鋸波発生器4(より詳しくは後述するインバータIV42の出力端子:図3参照)に接続されている。フォトカプラ72及び73夫々に含まれるLEDのカソードは、抵抗器R72及びR73を介してAND回路61及び62の出力端子に接続されている。フォトカプラ71に含まれるフォトトランジスタのコレクタは、抵抗器R74によりVccにプルアップされると共にマイコン8のタイマ用の入力端子及び割込用の入力端子に接続されている。フォトカプラ72及び73夫々に含まれるフォトトランジスタのコレクタは、抵抗器R75及び76によりVccにプルアップされると共にマイコン8のタイマ用の入力端子に接続されている。

次に、高電圧電源1の一端から抵抗器R12を介して負荷2に正の電流が流れる場合を例にして、鋸波発生器4を中心に電流検出回路の動作をより詳細に説明する。高電圧電源1の一端から抵抗器R12を介して負荷2に負の電流が流れる場合は、以下の説明における増幅器31、比較器51及びAND回路61の夫々を増幅器32、比較器52及びAND回路62と読み替えればよい。

図4の最上段に示す鋸波信号の電圧が直線的に漸増して時刻t1(又はt11)でVthを上回った場合、比較器43の出力信号がHレベルに立ち上がり、この出力信号がインバータIV41でLレベルに反転されるため、コンデンサC42の電荷がダイオードD41及び抵抗器R48を介して急速に放電する。その結果、時刻t2(又はt12)でコンデンサC42の電圧がインバータIV42の下側の閾値電圧を下回った場合、インバータIV42の出力信号(即ち第2の信号)がHレベルに立ち上がり、この信号によってトランジスタQ43がオンする。このため、コンデンサC41の電荷が急速に放電して鋸波信号の電圧が急激に低下する。トランジスタQ43がオンする直前の鋸波信号の電圧がVpである。時刻t1からt2(又はt11からt12)までの期間におけるコンデンサC41の電圧の上昇分は、Vpと比較して無視できるほどである。

時刻t2(又はt12)でコンデンサC41の電圧が低下し始めると直ちに比較器43の出力信号がLレベルに立ち下がり、この出力信号がインバータIV41でHレベルに反転されるため、コンデンサC42が抵抗器R47を介して徐々に充電される。その結果、時刻t3(又はt13)でコンデンサC42の電圧がインバータIV42の上側の閾値電圧を上回った場合、インバータIV42の出力信号(即ち第2の信号)がLレベルに立ち下がり、この信号によってトランジスタQ43がオフする。このため、コンデンサC41への充電が再び開始されて鋸波信号の電圧が直線的に漸増する。なお、コンデンサC41の電荷は、時刻t2からt3(又はt12からt13)までの期間中に完全に放電するように調整される。

第2の信号及び比較器51の出力信号について負論理のANDをとるAND回路61の出力信号は、時刻t3(又はt13)でLレベルとなり、時刻t4でHレベルとなる。時刻t3(又はt13)は、鋸波信号の電圧が直線的に漸増する期間の始点である。つまり、AND回路61は、第2の信号がLレベルである期間だけ比較器51からのLレベルの信号を通過させることにより、比較器51からの信号の立ち下がり(前縁)をアクティブロウの第2の信号の前縁まで遅らせて出力する。

さて、第2の信号がLレベルである期間、即ち鋸波信号の電圧が直線的に漸増する時刻t3からt12までの期間の長さをT1とし、AND回路61の出力信号がLレベルである時刻t3からt4までの期間の長さをT2とした場合、時刻t4における鋸波信号の電圧はVp×(T2/T1)である。この電圧は、時刻t4で比較器51の反転入力端子に入力される電圧、即ち増幅器31の出力電圧に等しいので、高電圧電源1から抵抗器R12を介して負荷2に流れる電流iは、以下の式(1)により算出される。なお、負荷2から抵抗器R12を介して高電圧電源1に流れる電流iを検出する場合は、AND回路62の出力信号がLレベルである期間の長さT3を検知し、式(1)におけるT2をT3に、βを増幅器32の増幅率の絶対値に夫々置き換えればよい。

図5の処理で用いるr及びβ夫々は、既に述べたとおり抵抗器R12の抵抗値及び増幅器31,32の増幅率の絶対値である。また、T3は、AND回路62の出力信号がLレベルである期間の長さである。図6、図7及び図8夫々の処理で用いる前縁フラグ1、前縁フラグ2及び前縁フラグ3は、信号幅を検知すべき信号の前縁における割込処理であることを示すフラグであり、不図示のRAMに記憶される。T2及びT3は初期値を0としてRAMに記憶される。T1は、直前に検知された値がRAMに記憶されている。図5の処理で算出される電流iは、高電圧電源1から抵抗器R12を介して負荷2に流れる電流を正の電流とする。

以上のように本実施の形態1によれば、高電圧電源1の一端及び負荷2の間に接続された抵抗器R12の両端間に生じる電圧を増幅器31,32で増幅して比較器51,52で鋸波信号の電圧と比較し、鋸波信号の電圧が直線的に漸増する傾斜期間における比較器51,52の比較結果を示す信号の長さT2,T3と、上記傾斜期間を示す信号の長さT1とを検知し、検知した長さの比率に基づいて抵抗器R12に流れる電流を検出する。

これにより、鋸波信号のピーク電圧Vpに対する増幅器31,32の出力電圧の比率が算出され、この比率と、ピーク電圧Vp、増幅器31,32の増幅率の絶対値β及び抵抗器R12の抵抗値rとに基づいて電流値iが検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

これにより、鋸波信号のピーク電圧Vpに対する増幅器31,32の出力電圧の比率が算出され、この比率と、ピーク電圧Vp、増幅器31,32の増幅率の絶対値β及び抵抗器R12の抵抗値rとに基づいて電流値iが検出される。

従って、広いダイナミックレンジで高精度に、且つ良好なステップ応答で電流を検出することが可能となる。

なお、実施の形態1にあっては、鋸波信号における電圧が直線的に漸増する期間を傾斜期間としたが、これに限定されるものではない。例えば、図4に示す時刻t3からt12までの期間に対応する期間中に鋸波信号の電圧が右肩下がりに漸減する場合は、この期間を傾斜期間としてもよい。この場合、AND回路61は、第2の信号がLレベルである期間だけ比較器51からのLレベルの信号を通過させることにより、比較器51からの信号の立ち上がり(後縁)をアクティブロウの第2の信号の後縁まで早めて出力する。

図12の処理で用いる開始フラグは、周期を検知すべき信号の開始時点における割込処理であることを示すフラグであり、不図示のRAMに記憶される。図14の処理で用いる前縁フラグは、信号幅を検知すべき信号の前縁における割込処理であることを示すフラグであり、RAMに記憶される。検知フェーズの区別もRAMに記憶される。T2及びT3は初期値を0としてRAMに記憶される。T1は、直前に検知された値がRAMに記憶されている。第2タイマは、インプットキャプチャの設定になっている。

Claims (5)

- 電源及び負荷の間で抵抗器を介して流れる電流を検出する電流検出回路において、

三角波信号又は鋸波信号を発生する発生部と、

該発生部で発生する信号の電圧が直線的に漸増又は漸減する期間を示す信号を生成する第1生成部と、

前記抵抗器の両端間の電圧を増幅する増幅部と、

該増幅部で増幅した信号の電圧及び前記発生部で発生した電圧を比較する比較部と、

前記期間における前記比較部の比較結果を示す信号を生成する第2生成部と、

前記第1生成部からの信号の信号幅に対する前記第2生成部からの信号の信号幅の比に基づいて前記抵抗器に流れる電流を検出する検出部と

を備えることを特徴とする電流検出回路。 - 前記検出部は、周期信号を計数するカウンタの計数値を、信号幅を検知すべき信号の前縁及び後縁で保持して差分をとることにより、前記第1及び第2生成部夫々からの信号の信号幅を検知することを特徴とする請求項1に記載の電流検出回路。

- 前記第1及び第2生成部と前記検出部とを電気的に絶縁して前記第1及び第2生成部から前記検出部に信号を伝達する絶縁部を備えることを特徴とする請求項1又は2に記載の電流検出回路。

- 前記抵抗器の端子の何れか一方の電位を、前記第1及び第2生成部の基準電位とすることを特徴とする請求項3に記載の電流検出回路。

- 前記第1及び第2生成部からの信号を選択的に切り替えて前記検出部に伝達する選択部を備え、

前記検出部は、前記選択部を介して伝達された前記第1生成部からの信号の周期に応じて前記選択部を切り替える

ことを特徴とする請求項1から4の何れか1項に記載の電流検出回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015162964A JP2017040580A (ja) | 2015-08-20 | 2015-08-20 | 電流検出回路 |

| CN201680045940.XA CN107850630A (zh) | 2015-08-20 | 2016-08-16 | 电流检测电路 |

| PCT/JP2016/073908 WO2017030118A1 (ja) | 2015-08-20 | 2016-08-16 | 電流検出回路 |

| US15/752,964 US20180238940A1 (en) | 2015-08-20 | 2016-08-16 | Current detection circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015162964A JP2017040580A (ja) | 2015-08-20 | 2015-08-20 | 電流検出回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017040580A true JP2017040580A (ja) | 2017-02-23 |

| JP2017040580A5 JP2017040580A5 (ja) | 2018-02-15 |

Family

ID=58052057

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015162964A Pending JP2017040580A (ja) | 2015-08-20 | 2015-08-20 | 電流検出回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20180238940A1 (ja) |

| JP (1) | JP2017040580A (ja) |

| CN (1) | CN107850630A (ja) |

| WO (1) | WO2017030118A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111263889A (zh) * | 2017-10-24 | 2020-06-09 | 大陆汽车有限责任公司 | 用于运行电池传感器的方法和电池传感器 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109596877B (zh) * | 2018-12-07 | 2021-01-12 | 深圳沃特检验集团有限公司 | 一种多功能检测装置 |

| CN109900950B (zh) * | 2019-04-04 | 2021-07-13 | 上海南芯半导体科技有限公司 | 一种高精度的连续时间双向电流采样电路及实现方法 |

| CN110244111B (zh) * | 2019-07-19 | 2021-06-29 | 广东浪潮大数据研究有限公司 | 一种板端电源近端和远端电压侦测装置 |

| WO2021240192A1 (ja) * | 2020-05-28 | 2021-12-02 | 日産自動車株式会社 | 電流検出装置及び電流検出方法 |

| CN112104294B (zh) * | 2020-09-08 | 2023-03-03 | 西安应用光学研究所 | 一种大转矩永磁同步电机电流精确检测方法 |

| JP2022069990A (ja) * | 2020-10-26 | 2022-05-12 | 株式会社マキタ | 電動作業機 |

| CN114089024B (zh) | 2022-01-20 | 2022-04-26 | 成都齐碳科技有限公司 | 电流测量电路、测量方法及纳米孔测序装置 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS461896A (ja) * | 1970-02-24 | 1971-10-05 | ||

| JPS5322478A (en) * | 1976-08-13 | 1978-03-01 | Hitachi Ltd | Indicator |

| JPS6399277U (ja) * | 1986-12-18 | 1988-06-27 | ||

| JPH04336712A (ja) * | 1991-05-13 | 1992-11-24 | Sankyo Seiki Mfg Co Ltd | アナログ・デジタル変換回路 |

| JPH0690174A (ja) * | 1992-09-08 | 1994-03-29 | Matsushita Electric Ind Co Ltd | 電圧読取装置 |

| JP2002250746A (ja) * | 2001-02-26 | 2002-09-06 | Yaskawa Electric Corp | 絶縁型電流検出器 |

| JP2011015294A (ja) * | 2009-07-03 | 2011-01-20 | Nippon Telegr & Teleph Corp <Ntt> | 電圧制御遅延発生器セル、電圧制御遅延発生器およびアナログ・ディジタル変換器 |

| JP2013253911A (ja) * | 2012-06-08 | 2013-12-19 | Nichicon Corp | 測定装置および該測定装置を備えた充電装置 |

| JP2014049843A (ja) * | 2012-08-30 | 2014-03-17 | Mitsubishi Electric Engineering Co Ltd | 多点同時高速アナログ/デジタル変換装置 |

| JP2015095891A (ja) * | 2013-11-14 | 2015-05-18 | キヤノン株式会社 | Ad変換器、固体撮像素子および撮像システム |

-

2015

- 2015-08-20 JP JP2015162964A patent/JP2017040580A/ja active Pending

-

2016

- 2016-08-16 CN CN201680045940.XA patent/CN107850630A/zh active Pending

- 2016-08-16 US US15/752,964 patent/US20180238940A1/en not_active Abandoned

- 2016-08-16 WO PCT/JP2016/073908 patent/WO2017030118A1/ja active Application Filing

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS461896A (ja) * | 1970-02-24 | 1971-10-05 | ||

| JPS5322478A (en) * | 1976-08-13 | 1978-03-01 | Hitachi Ltd | Indicator |

| JPS6399277U (ja) * | 1986-12-18 | 1988-06-27 | ||

| JPH04336712A (ja) * | 1991-05-13 | 1992-11-24 | Sankyo Seiki Mfg Co Ltd | アナログ・デジタル変換回路 |

| JPH0690174A (ja) * | 1992-09-08 | 1994-03-29 | Matsushita Electric Ind Co Ltd | 電圧読取装置 |

| JP2002250746A (ja) * | 2001-02-26 | 2002-09-06 | Yaskawa Electric Corp | 絶縁型電流検出器 |

| JP2011015294A (ja) * | 2009-07-03 | 2011-01-20 | Nippon Telegr & Teleph Corp <Ntt> | 電圧制御遅延発生器セル、電圧制御遅延発生器およびアナログ・ディジタル変換器 |

| JP2013253911A (ja) * | 2012-06-08 | 2013-12-19 | Nichicon Corp | 測定装置および該測定装置を備えた充電装置 |

| JP2014049843A (ja) * | 2012-08-30 | 2014-03-17 | Mitsubishi Electric Engineering Co Ltd | 多点同時高速アナログ/デジタル変換装置 |

| JP2015095891A (ja) * | 2013-11-14 | 2015-05-18 | キヤノン株式会社 | Ad変換器、固体撮像素子および撮像システム |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111263889A (zh) * | 2017-10-24 | 2020-06-09 | 大陆汽车有限责任公司 | 用于运行电池传感器的方法和电池传感器 |

| CN111263889B (zh) * | 2017-10-24 | 2022-06-21 | 大陆汽车有限责任公司 | 用于运行电池传感器的方法和电池传感器 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2017030118A1 (ja) | 2017-02-23 |

| US20180238940A1 (en) | 2018-08-23 |

| CN107850630A (zh) | 2018-03-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2017030118A1 (ja) | 電流検出回路 | |

| US7731417B2 (en) | Temperature detection circuit | |

| US10447157B2 (en) | Synchronous sensing of inductor current in a buck converter control circuit | |

| KR100892210B1 (ko) | 차지 펌프의 모드 변환 조절 회로 및 방법 | |

| US20130169171A1 (en) | Light emission driver device | |

| US10312806B1 (en) | Voltage converter for simulating inductor current control | |

| JP2006203369A (ja) | 電圧−周波数変換装置、電圧−周波数変換装置の基準電圧発生方法 | |

| US9143151B2 (en) | Pulse generator and analog-digital converter including the same | |

| JP2005150550A (ja) | ソレノイド駆動装置 | |

| US8139385B2 (en) | Inverter control circuit and control method thereof | |

| CN109632118B (zh) | 一种cmos温度传感电路及mems温度传感器系统 | |

| US9857395B2 (en) | Method and apparatus for measuring average inductor current delivered to a load | |

| EP3579328B1 (en) | Charging device | |

| CN109828001B (zh) | 电阻式气体传感器与其气体感测方法 | |

| JP2023109886A (ja) | 電圧変化率検出回路、半導体装置及び電力変換器 | |

| CN101754539B (zh) | 一种采样电路、led驱动电路及其检测电池电量的方法 | |

| CN113050184B (zh) | 光电传感器及其控制方法 | |

| US20160344201A1 (en) | Constant current charging device | |

| JP2003143011A (ja) | アナログ−ディジタル変換回路 | |

| CN106549559A (zh) | 开关电源装置的控制电路 | |

| JP2020010414A (ja) | スイッチング電源およびスイッチング電源制御回路 | |

| KR20110057857A (ko) | 교류전압 피크치 검출장치 | |

| JP2018077077A (ja) | 空燃比センサ制御装置 | |

| WO2023050157A1 (en) | Voltage information detecting circuit, power supply circuit, driving circuit and voltage information detecting method | |

| CN106855588B (zh) | 一种电流检测芯片、电源设备及电子设备 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181023 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20190423 |