JP2016532974A - マルチチップパッケージ上の異種メモリ用の統合メモリコントローラ - Google Patents

マルチチップパッケージ上の異種メモリ用の統合メモリコントローラ Download PDFInfo

- Publication number

- JP2016532974A JP2016532974A JP2016538917A JP2016538917A JP2016532974A JP 2016532974 A JP2016532974 A JP 2016532974A JP 2016538917 A JP2016538917 A JP 2016538917A JP 2016538917 A JP2016538917 A JP 2016538917A JP 2016532974 A JP2016532974 A JP 2016532974A

- Authority

- JP

- Japan

- Prior art keywords

- memory

- interface

- host

- umc

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1694—Configuration of memory controller to different memory types

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0604—Improving or facilitating administration, e.g. storage management

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0658—Controller construction arrangements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0683—Plurality of storage devices

Abstract

Description

202 第1のメモリ

204 第2のメモリ

206 第1のホストインターフェース

208 第2のホストインターフェース

210 統合メモリコントローラ(UMC)

212 中央処理装置(CPU)

214 第1のホストインターフェース回路

216 スタティックランダムアクセスメモリ(SRAM)

217 統合メモリコントローラバス

218 誤り訂正コード回路(ECC)、ECC回路

220 第1のメモリインターフェース回路

222 第2のホストインターフェース回路

224 第2のメモリインターフェース回路

226 コマンドデータバッファ

228 DRAMマネージャ

230 アービタ回路

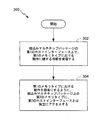

300 メモリインターフェース方法

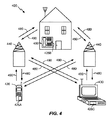

400 ワイヤレス通信システム

420 遠隔ユニット

425A ICデバイス

425B ICデバイス

425C ICデバイス

430 遠隔ユニット

440 基地局

450 遠隔ユニット

480 順方向リンク信号

490 逆方向リンク信号

500 設計用ワークステーション

501 ハードディスク

502 ディスプレイ

503 ドライブ装置

504 記憶媒体

510 回路デザイン

512 半導体構成要素

Claims (21)

- 少なくとも1つの、第1のメモリタイプの第1のメモリと、

少なくとも1つの、前記第1のメモリタイプとは異なる第2のメモリタイプの第2のメモリと、

前記第1のメモリおよび前記第2のメモリに結合された、統合メモリコントローラ(UMC)であって、前記第1のメモリとホストとの間の第1のインターフェース、および前記第2のメモリと前記ホストとの間の第2のインターフェースを含み、前記第1のインターフェースとは独立した前記第2のメモリを制御および利用するように、前記第1のメモリにアクセスするように構成される、UMCと

を備える装置。 - 前記UMCが、前記第2のインターフェースを通じた前記第2のメモリへのホストアクセス中に、前記第2のメモリの管理を実行するために、前記第1のメモリに独立にアクセスするように構成される、請求項1に記載の装置。

- 前記UMCが、前記第2のインターフェースを通じた前記第2のメモリへのホストアクセス中に、前記第2のメモリの性能を高めるために、前記第1のメモリに独立にアクセスするように構成される、請求項1に記載の装置。

- 前記UMCが、前記第2のインターフェースを通じた前記第2のメモリへのホストアクセス中に、前記第2のメモリによる電力使用を低減させるために、前記第1のメモリに独立にアクセスするように構成される、請求項1に記載の装置。

- 前記UMCが、前記第1のメモリおよび前記第2のメモリを制御するように構成される、請求項1に記載の装置。

- マルチチップパッケージ(MCP)であって、前記第1のメモリが、前記MCPの第1のチップ上に構成され、前記第2のメモリが、前記MCPの第2のチップ上に構成される、MCP

をさらに備える、請求項1に記載の装置。 - 前記第1のメモリが、NANDメモリを備え、前記第2のメモリが、ダイナミックランダムアクセスメモリ(DRAM)を備える、請求項1に記載の装置。

- モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込まれる、請求項1に記載の装置。

- 少なくとも1つの、第1のメモリタイプの第1のメモリと、

少なくとも1つの、前記第1のメモリタイプとは異なる第2のメモリタイプの第2のメモリと、

前記第1のメモリおよび前記第2のメモリに結合された、統合メモリコントローラ(UMC)であって、前記第1のメモリとホストとの間の第1のインターフェース、および前記第2のメモリと前記ホストとの間の第2のインターフェースを含み、前記第2のインターフェースを通じた前記第2のメモリへのホストアクセスを補助するように、前記第1のメモリを利用するように構成される、UMCと

を備える装置。 - モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込まれる、請求項9に記載の装置。

- マルチチップパッケージの第1のホストインターフェース上のホストから、前記マルチチップパッケージ上の第1のメモリタイプの第1のメモリにおける動作に関する情報を受信するステップと、

前記第1のメモリにおける前記動作を補助するように、前記マルチチップパッケージ上の第2のメモリタイプの第2のメモリに、前記マルチチップパッケージの第2のホストインターフェースとは独立にアクセスするステップと

を含む、メモリインターフェース方法。 - 前記情報が、記憶させるべきデータを含み、前記動作が、前記データの記憶を含む、請求項11に記載の方法。

- 前記マルチチップパッケージ上の前記第1のメモリと前記第2のメモリの両方を、前記マルチチップパッケージ上の単一のコントローラによって管理するステップをさらに含む、請求項12に記載の方法。

- 前記第2のメモリを管理するために前記第1のメモリにアクセスするステップをさらに含む、請求項12に記載の方法。

- 前記第1のメモリと前記第2のメモリとの間でデータを直接コピーするステップをさらに含む、請求項12に記載の方法。

- 前記情報が、前記第1のメモリに記憶されたデータの要求を含み、前記動作が、前記データの取出しを含む、請求項11に記載の方法。

- 前記マルチチップパッケージを、モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込むステップをさらに含む、請求項11に記載の方法。

- マルチチップパッケージの第1のホストインターフェース上のホストから、前記マルチチップパッケージ上の第1のメモリタイプの第1のメモリに記憶させるべきデータを受信するための手段と、

前記第1のメモリにおける前記データの記憶を補助するように、前記マルチチップパッケージ上の第2のメモリタイプの第2のメモリに、前記マルチチップパッケージの第2のホストインターフェースとは独立にアクセスするための手段と

を備える、メモリインターフェース装置。 - モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込まれる、請求項18に記載の装置。

- マルチチップパッケージの第1のホストインターフェース上のホストから、前記マルチチップパッケージ上の第1のメモリタイプの第1のメモリにおける動作に関する情報を受信するステップと、

前記第1のメモリにおける前記動作を補助するように、前記マルチチップパッケージ上の第2のメモリタイプの第2のメモリに、前記マルチチップパッケージの第2のホストインターフェースとは独立にアクセスするステップと

を含む、メモリインターフェース方法。 - 前記マルチチップパッケージを、モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込むステップをさらに含む、請求項20に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/016,717 US10185515B2 (en) | 2013-09-03 | 2013-09-03 | Unified memory controller for heterogeneous memory on a multi-chip package |

| US14/016,717 | 2013-09-03 | ||

| PCT/US2014/045983 WO2015034580A1 (en) | 2013-09-03 | 2014-07-09 | Unified memory controller for heterogeneous memory on a multi-chip package |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016532974A true JP2016532974A (ja) | 2016-10-20 |

| JP2016532974A5 JP2016532974A5 (ja) | 2017-08-03 |

Family

ID=51293140

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016538917A Ceased JP2016532974A (ja) | 2013-09-03 | 2014-07-09 | マルチチップパッケージ上の異種メモリ用の統合メモリコントローラ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US10185515B2 (ja) |

| EP (1) | EP3042295A1 (ja) |

| JP (1) | JP2016532974A (ja) |

| KR (1) | KR20160048911A (ja) |

| CN (1) | CN105493061B (ja) |

| WO (1) | WO2015034580A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102408613B1 (ko) | 2015-08-27 | 2022-06-15 | 삼성전자주식회사 | 메모리 모듈의 동작 방법, 및 메모리 모듈을 제어하는 프로세서의 동작 방법, 및 사용자 시스템 |

| US10268541B2 (en) | 2016-08-15 | 2019-04-23 | Samsung Electronics Co., Ltd. | DRAM assist error correction mechanism for DDR SDRAM interface |

| KR102482896B1 (ko) | 2017-12-28 | 2022-12-30 | 삼성전자주식회사 | 이종 휘발성 메모리 칩들을 포함하는 메모리 장치 및 이를 포함하는 전자 장치 |

| US20210233585A1 (en) * | 2020-01-29 | 2021-07-29 | Micron Technology, Inc. | Multichip memory package with internal channel |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003091463A (ja) * | 2001-06-13 | 2003-03-28 | Hitachi Ltd | メモリ装置 |

| WO2006132006A1 (ja) * | 2005-06-09 | 2006-12-14 | Matsushita Electric Industrial Co., Ltd. | メモリ制御装置及びメモリ制御方法 |

| US20070147115A1 (en) * | 2005-12-28 | 2007-06-28 | Fong-Long Lin | Unified memory and controller |

| JP2007183961A (ja) * | 2005-12-28 | 2007-07-19 | Silicon Storage Technology Inc | ハードディスクドライブキャッシュメモリ及び再生デバイス |

| WO2008086488A2 (en) * | 2007-01-10 | 2008-07-17 | Mobile Semiconductor Corporation | Adaptive memory system for enhancing the performance of an external computing device |

| JP2011070470A (ja) * | 2009-09-28 | 2011-04-07 | Toshiba Corp | 半導体記憶装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100383774B1 (ko) | 2000-01-26 | 2003-05-12 | 삼성전자주식회사 | 공통 인터페이스 방식의 메모리 장치들을 구비한 시스템 |

| JP4049297B2 (ja) | 2001-06-11 | 2008-02-20 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| KR101085406B1 (ko) | 2004-02-16 | 2011-11-21 | 삼성전자주식회사 | 불 휘발성 메모리를 제어하기 위한 컨트롤러 |

| US20080137399A1 (en) | 2005-01-25 | 2008-06-12 | Chien-Chiang Chan | Single Chip Having Magnetoresistive Memory |

| US20060294295A1 (en) | 2005-06-24 | 2006-12-28 | Yukio Fukuzo | DRAM chip device well-communicated with flash memory chip and multi-chip package comprising such a device |

| US8291295B2 (en) | 2005-09-26 | 2012-10-16 | Sandisk Il Ltd. | NAND flash memory controller exporting a NAND interface |

| US7716411B2 (en) | 2006-06-07 | 2010-05-11 | Microsoft Corporation | Hybrid memory device with single interface |

| US8700830B2 (en) * | 2007-11-20 | 2014-04-15 | Spansion Llc | Memory buffering system that improves read/write performance and provides low latency for mobile systems |

| CN101303885A (zh) | 2008-07-01 | 2008-11-12 | 普天信息技术研究院有限公司 | 多芯片封装存储模块 |

| US7778101B2 (en) | 2008-09-05 | 2010-08-17 | Genesys Logic, Inc. | Memory module and method of performing the same |

-

2013

- 2013-09-03 US US14/016,717 patent/US10185515B2/en active Active

-

2014

- 2014-07-09 KR KR1020167008120A patent/KR20160048911A/ko not_active Application Discontinuation

- 2014-07-09 EP EP14748020.6A patent/EP3042295A1/en not_active Withdrawn

- 2014-07-09 JP JP2016538917A patent/JP2016532974A/ja not_active Ceased

- 2014-07-09 WO PCT/US2014/045983 patent/WO2015034580A1/en active Application Filing

- 2014-07-09 CN CN201480048456.3A patent/CN105493061B/zh not_active Expired - Fee Related

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003091463A (ja) * | 2001-06-13 | 2003-03-28 | Hitachi Ltd | メモリ装置 |

| WO2006132006A1 (ja) * | 2005-06-09 | 2006-12-14 | Matsushita Electric Industrial Co., Ltd. | メモリ制御装置及びメモリ制御方法 |

| US20090235003A1 (en) * | 2005-06-09 | 2009-09-17 | Takaharu Tanaka | Memory control device and memory control method |

| US20070147115A1 (en) * | 2005-12-28 | 2007-06-28 | Fong-Long Lin | Unified memory and controller |

| JP2007183961A (ja) * | 2005-12-28 | 2007-07-19 | Silicon Storage Technology Inc | ハードディスクドライブキャッシュメモリ及び再生デバイス |

| JP2007183962A (ja) * | 2005-12-28 | 2007-07-19 | Silicon Storage Technology Inc | 一体型メモリ及びコントローラ |

| WO2008086488A2 (en) * | 2007-01-10 | 2008-07-17 | Mobile Semiconductor Corporation | Adaptive memory system for enhancing the performance of an external computing device |

| US20090024819A1 (en) * | 2007-01-10 | 2009-01-22 | Mobile Semiconductor Corporation | Adaptive memory system for enhancing the performance of an external computing device |

| JP2011070470A (ja) * | 2009-09-28 | 2011-04-07 | Toshiba Corp | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150067234A1 (en) | 2015-03-05 |

| WO2015034580A1 (en) | 2015-03-12 |

| CN105493061B (zh) | 2020-11-03 |

| CN105493061A (zh) | 2016-04-13 |

| KR20160048911A (ko) | 2016-05-04 |

| EP3042295A1 (en) | 2016-07-13 |

| US10185515B2 (en) | 2019-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107229417B (zh) | 数据存储设备及其操作方法 | |

| US9244853B2 (en) | Tunable multi-tiered STT-MRAM cache for multi-core processors | |

| US10943183B2 (en) | Electronics device performing software training on memory channel and memory channel training method thereof | |

| US10445025B2 (en) | Apparatuses and methods having memory tier structure and recursively searching between tiers for address in a translation table where information is only directly transferred between controllers | |

| US9304913B2 (en) | Mixed memory type hybrid cache | |

| TWI556105B (zh) | 讀取快取記憶體 | |

| US20140376320A1 (en) | Spare memory external to protected memory | |

| KR101799357B1 (ko) | Dram 서브-어레이 레벨 리프레시 | |

| US9269404B1 (en) | Semiconductor package on package memory channels with arbitration for shared calibration resources | |

| US10915264B2 (en) | Apparatus, systems, and methods to reclaim storage associated with cached data | |

| CN105493061B (zh) | 用于多芯片封装上的异构存储器的统一存储器控制器 | |

| KR20160110595A (ko) | 저장 장치, 그것을 포함하는 호스트 시스템, 및 그것의 맵 테이블 업데이트 방법 | |

| JP2015519640A (ja) | 階層メモリの磁気抵抗ランダムアクセスメモリ(mram)アーキテクチャ | |

| JP7007102B2 (ja) | 不揮発性メモリモジュール、及び格納装置の動作方法 | |

| US20130080693A1 (en) | Hybrid memory device, computer system including the same, and method of reading and writing data in the hybrid memory device | |

| US20160371012A1 (en) | Data storage device and data processing system including same | |

| KR20170104107A (ko) | Ecc 관련 데이터를 키-밸류 맵핑 정보에서 관리하는 오브젝트 스토리지 시스템 | |

| US9384810B2 (en) | Monolithic multi-channel adaptable STT-MRAM | |

| US10534545B2 (en) | Three-dimensional stacked memory optimizations for latency and power | |

| US20160041761A1 (en) | Independently controlling separate memory devices within a rank | |

| US8788748B2 (en) | Implementing memory interface with configurable bandwidth | |

| JP2011070470A (ja) | 半導体記憶装置 | |

| US20190187930A1 (en) | Three-dimensional stacked memory access optimization | |

| TW201331951A (zh) | 具有可重組態解碼之具能量效率記憶體 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170622 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170622 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180702 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20181002 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181116 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190513 |

|

| A045 | Written measure of dismissal of application [lapsed due to lack of payment] |

Free format text: JAPANESE INTERMEDIATE CODE: A045 Effective date: 20190917 |