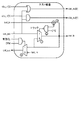

JP2015534673A - リングオシレータのテストソリューション - Google Patents

リングオシレータのテストソリューション Download PDFInfo

- Publication number

- JP2015534673A JP2015534673A JP2015531099A JP2015531099A JP2015534673A JP 2015534673 A JP2015534673 A JP 2015534673A JP 2015531099 A JP2015531099 A JP 2015531099A JP 2015531099 A JP2015531099 A JP 2015531099A JP 2015534673 A JP2015534673 A JP 2015534673A

- Authority

- JP

- Japan

- Prior art keywords

- test

- ring oscillator

- ring

- chain

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000012085 test solution Substances 0.000 title description 5

- 238000012360 testing method Methods 0.000 claims abstract description 307

- 230000010355 oscillation Effects 0.000 claims description 13

- 238000011990 functional testing Methods 0.000 claims description 9

- 230000007853 structural degeneration Effects 0.000 claims description 2

- 230000015556 catabolic process Effects 0.000 claims 1

- 238000006731 degradation reaction Methods 0.000 claims 1

- 238000000034 method Methods 0.000 abstract description 13

- 230000006870 function Effects 0.000 description 20

- 230000007704 transition Effects 0.000 description 16

- 230000006399 behavior Effects 0.000 description 11

- 238000010998 test method Methods 0.000 description 11

- 238000001514 detection method Methods 0.000 description 9

- 230000007547 defect Effects 0.000 description 7

- 238000012512 characterization method Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 238000010200 validation analysis Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 2

- 238000004590 computer program Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000012029 structural testing Methods 0.000 description 2

- 235000012431 wafers Nutrition 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000003745 diagnosis Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000011056 performance test Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 230000001131 transforming effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/03—Astable circuits

- H03K3/0315—Ring oscillators

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/2851—Testing of integrated circuits [IC]

- G01R31/2884—Testing of integrated circuits [IC] using dedicated test connectors, test elements or test circuits on the IC under test

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318502—Test of Combinational circuits

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/31708—Analysis of signal quality

- G01R31/31709—Jitter measurements; Jitter generators

Landscapes

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Tests Of Electronic Circuits (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/605,708 | 2012-09-06 | ||

| US13/605,708 US8841974B2 (en) | 2012-09-06 | 2012-09-06 | Test solution for ring oscillators |

| PCT/US2013/055176 WO2014039226A1 (en) | 2012-09-06 | 2013-08-15 | Test solution for ring oscillators |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015534673A true JP2015534673A (ja) | 2015-12-03 |

| JP2015534673A5 JP2015534673A5 (enExample) | 2016-09-29 |

Family

ID=50186712

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015531099A Pending JP2015534673A (ja) | 2012-09-06 | 2013-08-15 | リングオシレータのテストソリューション |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8841974B2 (enExample) |

| EP (1) | EP2893639A4 (enExample) |

| JP (1) | JP2015534673A (enExample) |

| KR (1) | KR20150054899A (enExample) |

| CN (1) | CN104604131A (enExample) |

| TW (1) | TWI593234B (enExample) |

| WO (1) | WO2014039226A1 (enExample) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021144672A (ja) * | 2020-03-12 | 2021-09-24 | カトリーケ・ユニフェルシテイト・ルーヴァンKatholieke Universiteit Leuven | 乱数発生器 |

| JP2022523558A (ja) * | 2019-03-04 | 2022-04-25 | サイプレス セミコンダクター コーポレーション | 暗号化ギャングプログラミング |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6423277B2 (ja) * | 2015-01-09 | 2018-11-14 | 株式会社メガチップス | 乱数生成装置及び乱数生成方法 |

| US9891276B2 (en) | 2015-07-28 | 2018-02-13 | International Business Machines Corporation | Performance-screen ring oscillator (PSRO) using an integrated circuit test signal distribution network |

| US10078114B2 (en) * | 2015-09-24 | 2018-09-18 | Renesas Electronics Corporation | Test point circuit, scan flip-flop for sequential test, semiconductor device and design device |

| CN106874177A (zh) * | 2015-12-14 | 2017-06-20 | 中国航空工业第六八研究所 | 一种基于场景的锁存器测试方法 |

| CN106656460A (zh) * | 2016-11-22 | 2017-05-10 | 浙江大学 | 一种针对密码芯片电磁脉冲故障分析的防御装置 |

| CN111010880A (zh) * | 2018-08-08 | 2020-04-14 | 深圳市汇顶科技股份有限公司 | 随机数发生器的建模方法、装置、介质及随机数发生器 |

| TWI719917B (zh) * | 2020-07-14 | 2021-02-21 | 金麗科技股份有限公司 | 將類比動態電路運用於數位測試工具的處理方法 |

| CN112504519B (zh) * | 2020-11-23 | 2022-05-20 | 深圳市绘王动漫科技有限公司 | 一种压力检测电路、装置及压力输入装置 |

| KR102925794B1 (ko) | 2021-06-17 | 2026-02-09 | 삼성전자 주식회사 | 오실레이터 클럭 신호의 주기를 조정하는 클럭 생성 회로 및 그 방법 |

| US12032460B2 (en) * | 2022-02-11 | 2024-07-09 | Stmicroelectronics S.R.L. | Systems and methods to test an asynchronous finite machine |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5341096A (en) * | 1989-07-11 | 1994-08-23 | Fujitsu Limited | Semiconductor integrated circuit having a scan circuit provided with a self-contained signal generator circuit |

| JP2000183694A (ja) * | 1998-12-18 | 2000-06-30 | Mitsumi Electric Co Ltd | 発振回路 |

| JP2002311091A (ja) * | 2001-04-10 | 2002-10-23 | Mitsubishi Electric Corp | 半導体装置 |

| US6798230B1 (en) * | 2003-01-15 | 2004-09-28 | Advanced Micro Devices, Inc. | Structure and method for increasing accuracy in predicting hot carrier injection (HCI) degradation in semiconductor devices |

| US7532078B2 (en) * | 2007-02-09 | 2009-05-12 | International Business Machines Corporation | Scannable virtual rail method and ring oscillator circuit for measuring variations in device characteristics |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5963104A (en) * | 1996-04-15 | 1999-10-05 | Vlsi Technology, Inc. | Standard cell ring oscillator of a non-deterministic randomizer circuit |

| US6069849A (en) * | 1996-09-17 | 2000-05-30 | Xilinx, Inc. | Method and system for measuring signal propagation delays using the duty cycle of a ring oscillator |

| JP2004096237A (ja) * | 2002-08-29 | 2004-03-25 | Nec Electronics Corp | 発振回路及び半導体集積回路 |

| US7205854B2 (en) * | 2003-12-23 | 2007-04-17 | Intel Corporation | On-chip transistor degradation monitoring |

| US7233212B2 (en) * | 2005-03-31 | 2007-06-19 | International Business Machines Corporation | Oscillator array with row and column control |

| US7675372B2 (en) * | 2006-08-09 | 2010-03-09 | Qualcomm Incorporated | Circuit simulator parameter extraction using a configurable ring oscillator |

| CN101373203A (zh) * | 2007-08-21 | 2009-02-25 | 中芯国际集成电路制造(上海)有限公司 | 环形振荡器速度测试结构 |

| US8676870B2 (en) * | 2007-09-18 | 2014-03-18 | Seagate Technology Llc | Active test and alteration of sample times for a ring based random number generator |

| JP2009117894A (ja) * | 2007-11-01 | 2009-05-28 | Univ Of Tokyo | 注入同期型発振器 |

| JP4427581B2 (ja) * | 2008-01-08 | 2010-03-10 | 株式会社東芝 | 乱数生成回路 |

| US8081037B2 (en) * | 2008-06-11 | 2011-12-20 | Qualcomm Incorporated | Ring oscillator using analog parallelism |

| DE102008048292B4 (de) * | 2008-09-22 | 2012-07-12 | Siemens Aktiengesellschaft | Vorrichtung und Verfahren zum Erzeugen einer Zufallsbitfolge |

| JP2010087275A (ja) * | 2008-09-30 | 2010-04-15 | Panasonic Corp | 半導体集積回路および電子機器 |

| CN101819515B (zh) * | 2010-02-08 | 2012-06-20 | 清华大学 | 基于环型振荡器的真随机数发生电路及真随机数发生器 |

| US8381144B2 (en) * | 2010-03-03 | 2013-02-19 | Qualcomm Incorporated | System and method of test mode gate operation |

-

2012

- 2012-09-06 US US13/605,708 patent/US8841974B2/en active Active

-

2013

- 2013-08-15 KR KR1020157008839A patent/KR20150054899A/ko not_active Withdrawn

- 2013-08-15 EP EP13835091.3A patent/EP2893639A4/en not_active Withdrawn

- 2013-08-15 CN CN201380046554.9A patent/CN104604131A/zh active Pending

- 2013-08-15 JP JP2015531099A patent/JP2015534673A/ja active Pending

- 2013-08-15 WO PCT/US2013/055176 patent/WO2014039226A1/en not_active Ceased

- 2013-08-27 TW TW102130640A patent/TWI593234B/zh not_active IP Right Cessation

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5341096A (en) * | 1989-07-11 | 1994-08-23 | Fujitsu Limited | Semiconductor integrated circuit having a scan circuit provided with a self-contained signal generator circuit |

| JP2000183694A (ja) * | 1998-12-18 | 2000-06-30 | Mitsumi Electric Co Ltd | 発振回路 |

| JP2002311091A (ja) * | 2001-04-10 | 2002-10-23 | Mitsubishi Electric Corp | 半導体装置 |

| US6798230B1 (en) * | 2003-01-15 | 2004-09-28 | Advanced Micro Devices, Inc. | Structure and method for increasing accuracy in predicting hot carrier injection (HCI) degradation in semiconductor devices |

| US7532078B2 (en) * | 2007-02-09 | 2009-05-12 | International Business Machines Corporation | Scannable virtual rail method and ring oscillator circuit for measuring variations in device characteristics |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2022523558A (ja) * | 2019-03-04 | 2022-04-25 | サイプレス セミコンダクター コーポレーション | 暗号化ギャングプログラミング |

| JP7309893B2 (ja) | 2019-03-04 | 2023-07-18 | サイプレス セミコンダクター コーポレーション | 暗号化ギャングプログラミング |

| JP2021144672A (ja) * | 2020-03-12 | 2021-09-24 | カトリーケ・ユニフェルシテイト・ルーヴァンKatholieke Universiteit Leuven | 乱数発生器 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2893639A1 (en) | 2015-07-15 |

| US8841974B2 (en) | 2014-09-23 |

| US20140062606A1 (en) | 2014-03-06 |

| CN104604131A (zh) | 2015-05-06 |

| WO2014039226A1 (en) | 2014-03-13 |

| EP2893639A4 (en) | 2016-06-22 |

| KR20150054899A (ko) | 2015-05-20 |

| TW201419758A (zh) | 2014-05-16 |

| TWI593234B (zh) | 2017-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2015534673A (ja) | リングオシレータのテストソリューション | |

| Da Rolt et al. | Test versus security: Past and present | |

| Chiu et al. | A secure test wrapper design against internal and boundary scan attacks for embedded cores | |

| US9231567B2 (en) | Test solution for a random number generator | |

| Das et al. | PUF-based secure test wrapper design for cryptographic SoC testing | |

| US9983262B1 (en) | Built-in self test controller for a random number generator core | |

| US20170131355A1 (en) | Using Embedded Time-Varying Code Generator to Provide Secure Access to Embedded Content in an On Chip Access Architecture | |

| Baranowski et al. | Access port protection for reconfigurable scan networks | |

| Sauer et al. | Functional test of small-delay faults using SAT and Craig interpolation | |

| Da Rolt et al. | A smart test controller for scan chains in secure circuits | |

| CN107703442A (zh) | 基于抗差分扫描攻击的数据置乱安全扫描装置 | |

| Kochte et al. | Specification and verification of security in reconfigurable scan networks | |

| Thiemann et al. | On integrating lightweight encryption in reconfigurable scan networks | |

| Petlin et al. | Built-in self-testing of micropipelines | |

| Zadegan et al. | A self-reconfiguring IEEE 1687 network for fault monitoring | |

| Jutman et al. | Reliable health monitoring and fault management infrastructure based on embedded instrumentation and IEEE 1687 | |

| Karmakar et al. | On securing scan obfuscation strategies against ScanSAT attack | |

| Dubrova et al. | Secure and efficient LBIST for feedback shift register-based cryptographic systems | |

| Shi et al. | Robust secure scan design against scan-based differential cryptanalysis | |

| Meschkov et al. | New approaches of side-channel attacks based on chip testing methods | |

| Chittoriya et al. | A low-overhead puf based hardware security technique to prevent scan chain attacks for industry-standard DFT architecture | |

| Di Natale et al. | Manufacturing testing and security countermeasures | |

| Lodha et al. | On-chip comparison based secure output response compactor for scan-based attack resistance | |

| US7962766B2 (en) | Method and system for encryption-based design obfuscation for an integrated circuit | |

| Kumar et al. | PUF-based secure test wrapper for SoC testing |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20160713 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160810 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160810 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20160810 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20160906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160913 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170404 |