JP2014186257A - 表示装置および電子機器 - Google Patents

表示装置および電子機器 Download PDFInfo

- Publication number

- JP2014186257A JP2014186257A JP2013062649A JP2013062649A JP2014186257A JP 2014186257 A JP2014186257 A JP 2014186257A JP 2013062649 A JP2013062649 A JP 2013062649A JP 2013062649 A JP2013062649 A JP 2013062649A JP 2014186257 A JP2014186257 A JP 2014186257A

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- basic color

- sub

- display device

- luminance information

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 claims description 8

- 239000000284 extract Substances 0.000 claims description 6

- 238000001914 filtration Methods 0.000 claims description 4

- 230000002708 enhancing effect Effects 0.000 abstract 1

- 230000004048 modification Effects 0.000 description 70

- 238000012986 modification Methods 0.000 description 70

- 238000012937 correction Methods 0.000 description 48

- 238000010586 diagram Methods 0.000 description 35

- 238000012545 processing Methods 0.000 description 35

- 230000000052 comparative effect Effects 0.000 description 30

- 238000006243 chemical reaction Methods 0.000 description 24

- 238000000605 extraction Methods 0.000 description 19

- 239000008186 active pharmaceutical agent Substances 0.000 description 15

- 239000003795 chemical substances by application Substances 0.000 description 13

- 230000007423 decrease Effects 0.000 description 13

- 238000005401 electroluminescence Methods 0.000 description 11

- 238000000034 method Methods 0.000 description 11

- 239000000758 substrate Substances 0.000 description 11

- 230000006866 deterioration Effects 0.000 description 10

- 241000750042 Vini Species 0.000 description 9

- 230000007704 transition Effects 0.000 description 9

- 101150010989 VCATH gene Proteins 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- 239000000463 material Substances 0.000 description 7

- 230000008569 process Effects 0.000 description 6

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 239000010408 film Substances 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 5

- 101100365011 Arabidopsis thaliana SCL33 gene Proteins 0.000 description 4

- 230000014509 gene expression Effects 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- 101100478293 Arabidopsis thaliana SR34 gene Proteins 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- 241000282414 Homo sapiens Species 0.000 description 2

- -1 SB33 Proteins 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 230000008033 biological extinction Effects 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical class C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000003760 hair shine Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 102220047090 rs6152 Human genes 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2003—Display of colours

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0452—Details of colour pixel setup, e.g. pixel composed of a red, a blue and two green components

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0465—Improved aperture ratio, e.g. by size reduction of the pixel circuit, e.g. for improving the pixel density or the maximum displayable luminance or brightness

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

- G09G2300/0866—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes by means of changes in the pixel supply voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/06—Colour space transformation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

- H10K59/352—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels the areas of the RGB subpixels being different

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

- H10K59/353—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels characterised by the geometrical arrangement of the RGB subpixels

Abstract

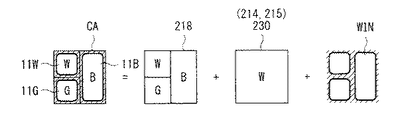

【解決手段】第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セットと、第1の画素と、第3の基本色光を発する第3の画素と、非基本色画素との組み合わせから構成される第2の画素セットとを有し、第1の画素セットおよび第2の画素セットが、第1の方向および第2の方向のいずれか一方または双方において、交互に配置された表示部と、第2の基本色光に対応する第1の輝度情報マップから、第1の画素セットに対応する位置の第1の輝度情報を抽出して第2の画素を駆動するとともに、第3の基本色光に対応する第2の輝度情報マップから、第2の画素セットに対応する位置の第2の輝度情報を抽出して第3の画素を駆動する駆動部とを備える。

【選択図】図2

Description

1.第1の実施の形態

2.第2の実施の形態

3.適用例

[構成例]

図1は、第1の実施の形態に係る表示装置の一構成例を表すものである。表示装置1は、有機EL素子を用いた、アクティブマトリックス方式の表示装置である。

続いて、本実施の形態の表示装置1の動作および作用について説明する。

まず、図1を参照して、表示装置1の全体動作概要を説明する。映像信号処理部30は、外部から供給される映像信号Sdispに対してRGBW変換やガンマ変換などを行い、映像信号Sdisp2を生成する。タイミング生成部22は、外部から供給される同期信号Ssyncに基づいて、走査線駆動部23、電源線駆動部26およびデータ線駆動部27に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する。走査線駆動部23は、タイミング生成部22から供給された制御信号に従って、複数の走査線WSLに対して走査信号WSを順次印加することにより、サブ画素11を順次選択する。電源線駆動部26は、タイミング生成部22から供給された制御信号に従って、複数の電源線PLに対して電源信号DSを順次印加することにより、サブ画素11の発光動作および消光動作の制御を行う。データ線駆動部27は、映像信号処理部30から供給された映像信号Sdisp2およびタイミング生成部22から供給された制御信号に従って、各サブ画素11の輝度に対応する画素電圧Vsig、およびVth補正を行うための電圧Vofsを含む信号Sigを生成し、各データ線DTLに印加する。表示部10は、駆動部20から供給された走査信号WS、電源信号DS、および信号Sigに基づいて表示を行う。

次に、表示装置1の詳細動作を説明する。

表示装置1は、消費電力を低減するために、いくつかの工夫がなされている。以下に、いくつかの比較例を挙げて、それらの技術について詳細に説明する。

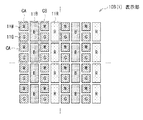

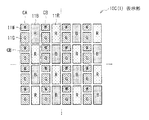

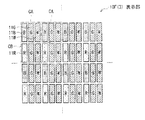

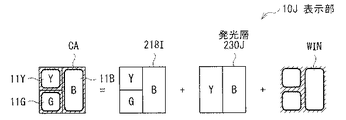

表示装置1では、図2に示したように、4色のサブ画素のうち、赤色(R)のサブ画素を省いてセルCAを構成するとともに、青色(B)のサブ画素を省いてセルCBを構成したので、以下に説明する表示装置1Rと比べて、画質の低下を抑えつつ、消費電力を低減することができる。

また、表示装置1では、図2に示したように、セルCA,CBが白色のサブ画素11Wを有するようにしたので、以下に説明する比較例2に係る表示装置1Sと比べて、消費電力を低減することができるとともに、画質を高めることができる。

また、表示装置1では、図7に示したように、アノード212がデータ線DTLと重ならないようにしたので、以下に説明する比較例3に係る表示装置1Tと比べて、画質の低下を抑えることができる。

以上のように本実施の形態では、赤色、緑色、青色、白色の4色のサブ画素を設けるとともに、白色や緑色のサブ画素と比べて、赤色や青色のサブ画素を少なくしたので、画質の低下を抑えつつ、消費電力を低減することができる。

上記実施の形態では、図2に示したように、3つのサブ画素11W,11G,11BによりセルCAを構成するとともに、3つのサブ画素11W,11G,11RによりセルCBを構成したが、これに限定されるものではない。

上記実施の形態では、図2に示したように、セルCAおよびセルCBを、列方向(垂直方向)に交互に配置するとともに、行方向(水平方向)に交互に配置したが、これに限定されるものではない。これに代えて、例えば、図15に示す表示部10B(1)のように、行方向(水平方向)にはセルCAおよびセルCBを交互に配置し、列方向(垂直方向)には同じセルを繰り返し配置してもよい。また、例えば、図16に示す表示部10B(2)のように、列方向(垂直方向)にはセルCAおよびセルCBを交互に配置し、行方向(水平方向)には同じセルを繰り返し配置してもよい。

上記実施の形態において、サブ画素11R,11G,11B,11Wの開口部WINの開口面積AR,AG,AB,AWは、次のような関係を有しているのが望ましい。

AW≦AG<AR=AB ・・・(1)

AW≦AG<AR<AB ・・・(2)

AW≦AG<AB<AR ・・・(3)

具体的には、例えば、図18に示す表示部10C(1)のように、サブ画素11Wの開口面積AWをサブ画素11Gの開口面積AGよりも小さくしてもよいし、図19に示す表示部10C(2)のように、サブ画素11Rの開口面積ARをサブ画素11Bの開口面積ABよりも小さくしてもよいし、例えば、図20に示す表示部10C(3)のように、サブ画素11Bの開口面積ABをサブ画素11Rの開口面積ARよりも小さくしてもよい。また、例えば、図21に示す表示部10C(4)のように、白色のサブ画素11Wの開口面積AW、および緑色のサブ画素11Gの開口面積AGを、これらの変形例の場合より大きくし、赤色のサブ画素11Rの開口面積AR、および青色のサブ画素11Bの開口面積ABを、これらの変形例の場合よりも小さくてもよい。ここで、サブ画素11Rの開口面積ARと、サブ画素11Bの開口面積ABとの大小関係は、例えば、サブ画素11R,11Bの発光効率などを考慮して決定することができる。

上記実施の形態では、図7に示したように、コンタクト205を回路領域15W,15G,15Bの上端付近または下端付近に設けたが、これに限定されるものではなく、これに代えて、例えば、図22に示す表示部10Dのように、回路領域15W,15G,15Bの中央付近に設けてもよい。この場合には、回路領域15W,15G,15Bにおける、書込トランジスタWSTr、駆動トランジスタDRTr、および容量素子Csのレイアウトを同一にすることができ、設計効率が向上するとともに、サブ画素11間の特性ばらつきを抑えることができる。

上記実施の形態では、図7に示したように、アノード212をデータ線DTLと重ならないように配置したが、これに限定されるものではなく、これに代えて、例えば図23に示す表示部10Eのように、各アノード212(212W,212G,212B)を1本のデータ線DTLと重なるように配置してもよい。この構成では、データ線DTLにおける信号Sigが、カップリングにより、アノード212W,212G,212Bにノイズとして伝わってしまうおそれがある。しかしながら、比較例3の場合と異なり、どのアノード212W,212G,212Bも、1本のデータ線DTLと重なるようにしたので、ノイズの影響がより均一になるため、画質の低下を抑えることができる。

上記実施の形態では、図2に示したように、セルCA,CBにおいて、サブ画素11W,11Gを列方向(垂直方向)に並設したが、これに限定されるものではない。これに代えて、例えば、図24〜図26に示す表示部10F(1)〜10F(3)のように、行方向(水平方向)に並設してもよい。この例では、セルCAにおいて、左から、サブ画素11B、サブ画素11G、サブ画素11Wをこの順で配置し、セルCBにおいて、左から、サブ画素11R、サブ画素11G、サブ画素11Wをこの順で配置している。表示部10F(1)(図24)では、セルCAおよびセルCBを、列方向に交互に配置するとともに、行方向に交互に配置している。表示部10F(2)(図25)では、行方向にはセルCAおよびセルCBを交互に配置し、列方向には同じセルを繰り返し配置している。表示部10F(3)(図26)では、列方向にはセルCAおよびセルCBを交互に配置し、行方向には同じセルを繰り返し配置している。

上記実施の形態では、トップエミッション型の発光素子19により表示部10を構成したが、これに限定されるものではなく、これに代えて、例えば、図29に示す表示部10Gのように、いわゆるボトムエミッション型の発光素子19Gにより構成してもよい。表示部10Gは、アノード232と、カソード236と、カラーフィルタ238とを有している。アノード232は、例えば、スズ酸化インジウムスズ(ITO;Indium Tin Oxide)により構成されている。すなわち、アノード232は、透明または半透明なものである。このアノード232は、例えば数十〜数百nmの膜厚で形成されている。カソード236は、光を反射する性質を有するものであり、例えば、マグネシウム銀(MgAg)により構成することができる。このカソード236は、例えば数十nm〜数百nm程度の膜厚で形成されている。カラーフィルタ238は、絶縁層204の上の、開口WINに対応する領域に形成されている。この構成により、黄色発光層214から射出した黄色の光と、青色発光層215から射出した青色の光は、混ざり合って白色光となり、支持基板である透明基板200の方向に進む。そして、この白色光は、赤色(R)、緑色(G)、青色(B)、白色(W)のカラーフィルタ238を介して表示面より出力される。

上記実施の形態では、図6A,6Bに示したように、発光層230(黄色発光層214および青色発光層215)が合成光として白色の光を発し、この白色光が赤色、緑色、青色、白色のカラーフィルタ218を介して出力されるようにしたが、これに限定されるものではない。

上記実施の形態では、図2,7などに示したように、サブ画素11の開口部WINの形状を長方形に近い形にしたが、これに限定されるものではなく、これに代えて、例えば、図33に示す表示部10Kのように、サブ画素14の開口部WINの形状を円形にしてもよい。表示部10Kは、赤色(R)、緑色(G)、青色(B)、および白色(W)のサブ画素14R,14G,14B,14Wを有している。表示部10には、3つのサブ画素14W,14G,14Bにより構成されるセルCA(CA1,CA2)と、3つのサブ画素14W,14G,14Rにより構成されるセルCB(CB1,CB2)とが並設されている。各セルCA1,CA2,CB1,CB2では、3つのサブ画素14が互いに隣り合うように配置されている。言い換えれば、これらの3つのサブ画素14は、それらの中心を結ぶ線が正3角形の各辺をなすように配置されている。具体的には、セルCA1において、白色(W)のサブ画素14Wが右上に配置され、緑色(G)のサブ画素14Gが下側に配置され、青色(B)のサブ画素14Bが左上に配置され、また、セルCA2において、白色(W)のサブ画素14Wが右下に配置され、緑色(G)のサブ画素14Gが上側に配置され、青色(B)のサブ画素14Bが左下に配置されている。また、セルCB1において、白色(W)のサブ画素14Wが右上に配置され、緑色(G)のサブ画素14Gが下側に配置され、赤色(R)のサブ画素14Rが左上に配置され、また、セルCB2において、白色(W)のサブ画素14Wが右下に配置され、緑色(G)のサブ画素14Gが上側に配置され、赤色(R)のサブ画素14Rは左下に配置されている。行方向(水平方向)には、セルCA1,CA2が交互に配置されるとともに、セルCB1,CB2が交互に配置される。また、列方向(垂直方向)には、セルCA1,CB1が交互に配置されるとともに、セルCA2,CB2が交互に配置される。このように、表示部10Kでは、サブ画素14がいわゆる最密充填配置になるように配置されている。このように、開口部WINを円形にしても、上記実施の形態と同様の効果を得ることができる。なお、この例では、開口部WINの形状を円形にしたが、これに限定されるものではなく、これに代えて、例えば楕円形にしてもよい。

上記実施の形態等において、開口部WINの形状、および絶縁層213,217の材料等を工夫することにより、発光層230から射出した光の外部への取り出し効率を高めるようにしてもよい。以下に、本変形例について詳細に説明する。なお、この例では、サブ画素の開口部WINは円形として説明するが、これに限定されるものではなく、楕円形や、長方形に近い形などであってもよい。

1.1≦n1≦1.8 ・・・(4)

n1−n2≧0.20 ・・・(5)

また、絶縁層213Lの高さをHとし、絶縁層213Lの開口部分の、アノード電極212側における直径をR1とし、絶縁層213Lの開口部分の、表示面側の直径をR2とすると、高さH、直径R1,R2は、以下の式を満たすように設定されている。

0.5≦R1/R2≦0.8 ・・・(6)

0.5≦H/R1≦2.0 ・・・(7)

上記実施の形態では、図3に示したように、各セルCA,CB内の3つのサブ画素11を、互いに異なるデータ線DTLに接続したが、これに限定されるものではない。以下に、本変形例について詳細に説明する。

以上、第1の実施の形態およびその変形例について説明したが、これらのうちの2以上を組み合わせてもよい。

次に、第2の実施の形態に係る表示装置2について説明する。本実施の形態は、データ線DTLの波形が、上記第1の実施の形態に係る表示装置1の場合と異なるものである。上記第1の実施の形態に係る表示装置1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

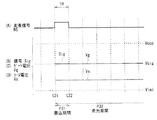

図43は、表示装置2における表示動作のタイミング図を表すものである。この図は、着目した1つのサブ画素11に対する表示駆動の動作例を表すものである。図43において、(A)は走査信号WSの波形を示し、(B)は電源信号DSの波形を示し、(C)は信号Sigの波形を示し、(D)は駆動トランジスタDRTrのゲート電圧Vgの波形を示し、(E)は駆動トランジスタDRTrのソース電圧Vsの波形を示す。図43(B)〜(E)では、同じ電圧軸を用いて各波形を示している。

上述したように、Ids補正期間P22では、駆動トランジスタDRTrのドレインからソースに電流Idsが流れ、ソース電圧Vsが上昇し、ゲート・ソース間電圧Vgsが徐々に低下する。これにより、駆動トランジスタDRTrのドレインからソースに流れる電流Idsも徐々に低下する。

表示装置2では、図41に示したように、アノード312W,312Gを、3本のデータ線DTLと重なるように配置し、アノード312Rを、データ線DTLと重ならないように配置している。これにより、以下に示すように、画質を高めることができる。

上記実施の形態では、走査信号WSの立ち下がり部分の電圧が短時間で変化するものとしたが、これに限定されるものではなく、これに代えて、例えば、この立ち下がり部分の電圧が徐々に下がるようにしてもよい。以下に、本変形例について、詳細に説明する。

上記実施の形態では、Ids補正を行うようにしたが、これに限定されるものではなく、これに代えて、このIds補正を行わないようにしてもよい。以下に、本変形例について詳細に説明する。

上記実施の形態では、アノード312W,312Gを3本のデータ線DTLと重なるように配置したが、これに限定されるものではなく、これに代えて、例えば、上記第1の実施の形態の場合(図7)と同様に、各アノード212をデータ線DTLと重ならないように配置してもよいし、上記第1の実施の形態の変形例1−5の場合(図23)と同様に、各アノード212を1本のデータ線DTLと重なるように配置してもよい。

以上、第2の実施の形態およびその変形例について説明したが、これらのうちの2以上を組み合わせてもよい。また、これらに、上記第1の実施の形態の変形例のうちの1以上を組み合わせてもよい。

次に、上記実施の形態および変形例で説明した表示装置の適用例について説明する。

前記第2の基本色光に対応する第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出し、その第1の輝度情報に基づいてその第1の画素セットに含まれる第2の画素を駆動するとともに、前記第3の基本色光に対応する第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出し、その第2の輝度情報に基づいてその第2の画素セットに含まれる第3の画素を駆動する駆動部と

を備えた表示装置。

前記(1)に記載の表示装置。

前記(1)または(2)に記載の表示装置。

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、画素電極を含む発光素子を有し、

前記第1の画素の画素電極は、前記複数の信号線のうちの、その第1の画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、

前記非基本色画素の画素電極は、前記複数の信号線のうちの、その非基本色画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置されている

前記(1)から(3)のいずれかに記載の表示装置。

前記(4)に記載の表示装置。

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のうちの1本と重なるように配置された画素電極を含む発光素子を有する

前記(1)から(3)のいずれかに記載の表示装置。

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のいずれとも重ならないように配置された画素電極を含む発光素子を有する

前記(1)から(3)のいずれかに記載の表示装置。

前記画素信号では、各画素の輝度を画定する輝度信号部分が時間軸上で連なっている

前記(4)から(7)のいずれかに記載の表示装置。

前記画素信号は、直流信号部分と、各画素の輝度を画定する輝度信号部分とを含み、

前記輝度信号部分と前記直流信号部分とが時間軸上で交互に配置されている

前記(6)または(7)に記載の表示装置。

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第2の画素と前記第2の方向において配列され、

前記第2の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第3の画素と前記第2の方向において配列されている

前記(1)から(9)のいずれかに記載の表示装置。

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、前記第2の方向に配列されている

前記(1)から(9)のいずれかに記載の表示装置。

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素の開口部は円形または楕円形であり、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列されている

前記(1)から(9)のいずれかに記載の表示装置。

前記第2の画素セットは、複数の第2の画素セル内に、互いに異なる配置パターンとなるように配置されている

前記(10)から(12)のいずれかに記載の表示装置。

前記(1)から(13)のいずれかに記載の表示装置。

前記(14)に記載の表示装置。

前記第2の基本色光は青色光であり、

前記第3の基本色光は赤色光である

前記(1)から(15)のいずれかに記載の表示装置。

容量素子と、

ドレインと、前記容量素子の一端に接続されたゲートと、前記容量素子の他端に接続されたソースとを含むトランジスタと

を有する

前記(1)から(16)のいずれかに記載の表示装置。

前記表示装置に対して動作制御を行う制御部と

を備え、

前記表示装置は、

第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セットと、前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットとを有し、前記第1の画素セットおよび前記第2の画素セットが、第1の方向および前記第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置された表示部と、

前記第2の基本色光に対応する第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出し、その第1の輝度情報に基づいてその第1の画素セットに含まれる第2の画素を駆動するとともに、前記第3の基本色光に対応する第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出し、その第2の輝度情報に基づいてその第2の画素セットに含まれる第3の画素を駆動する駆動部と

を有する

電子機器。

Claims (18)

- 第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セットと、前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットとを有し、前記第1の画素セットおよび前記第2の画素セットが、第1の方向および前記第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置された表示部と、

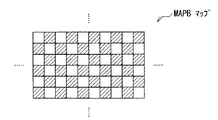

前記第2の基本色光に対応する第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出し、その第1の輝度情報に基づいてその第1の画素セットに含まれる第2の画素を駆動するとともに、前記第3の基本色光に対応する第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出し、その第2の輝度情報に基づいてその第2の画素セットに含まれる第3の画素を駆動する駆動部と

を備えた表示装置。 - 前記駆動部は、前記第1の輝度情報マップおよび前記第2の輝度情報マップに対してそれぞれフィルタ処理を行い、フィルタ処理された第1の輝度情報マップから前記第1の輝度情報を抽出するとともに、フィルタ処理された第2の輝度情報マップから前記第2の輝度情報を抽出する

請求項1に記載の表示装置。 - 前記駆動部は、前記第1の基本色光に対応する第3の輝度情報マップにおける第3の輝度情報に基づいて前記第1の画素を駆動するとともに、前記非基本色光に対応する第4の輝度情報マップにおける第4の輝度情報に基づいて前記非基本色画素を駆動する

請求項1に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、画素電極を含む発光素子を有し、

前記第1の画素の画素電極は、前記複数の信号線のうちの、その第1の画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置され、

前記非基本色画素の画素電極は、前記複数の信号線のうちの、その非基本色画素が属する画素セットの配置領域内に配置された所定数の信号線のいずれとも重なるように配置されている

請求項1に記載の表示装置。 - 前記第2の画素の画素電極および前記第3の画素の画素電極は、前記複数の信号線のいずれとも重ならないように配置されている

請求項4に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のうちの1本と重なるように配置された画素電極を含む発光素子を有する

請求項1に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、前記複数の信号線のいずれとも重ならないように配置された画素電極を含む発光素子を有する

請求項1に記載の表示装置。 - 前記駆動部は、前記信号線に画素信号を印加し、

前記画素信号では、各画素の輝度を画定する輝度信号部分が時間軸上で連なっている

請求項4に記載の表示装置。 - 前記駆動部は、前記信号線に画素信号を印加し、

前記画素信号は、直流信号部分と、各画素の輝度を画定する輝度信号部分とを含み、

前記輝度信号部分と前記直流信号部分とが時間軸上で交互に配置されている

請求項6に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第2の画素と前記第2の方向において配列され、

前記第2の画素セルにおいて、前記第1の画素および前記非基本色画素は、前記第1の方向に配列されるとともに、前記第3の画素と前記第2の方向において配列されている

請求項1に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、前記第2の方向に配列されている

請求項1に記載の表示装置。 - 前記第1の方向に延伸する複数の信号線をさらに備え、

前記第1の画素セットが、第1の画素セル内に配置され、

前記第2の画素セットが、第2の画素セル内に配置され、

前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素の開口部は円形または楕円形であり、

前記第1の画素セルにおいて、前記第1の画素、前記第2の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列され、

前記第2の画素セルにおいて、前記第1の画素、前記第3の画素、および前記非基本色画素は、互いに隣り合うように配置されるとともに、そのうちの2つは、前記第2の方向に配列されている

請求項1に記載の表示装置。 - 前記第1の画素セットは、複数の第1の画素セル内に、互いに異なる配置パターンとなるように配置され、

前記第2の画素セットは、複数の第2の画素セル内に、互いに異なる配置パターンとなるように配置されている

請求項10に記載の表示装置。 - 前記第2の画素における開口領域、および前記第3の画素における開口領域は、前記第1の画素における開口領域、および前記非基本色画素における開口領域のいずれよりも大きい

請求項1に記載の表示装置。 - 前記第1の画素における開口領域は、前記非基本色画素の開口領域以上の大きさである

請求項14に記載の表示装置。 - 前記第1の基本色光は緑色光であり、

前記第2の基本色光は青色光であり、

前記第3の基本色光は赤色光である

請求項1に記載の表示装置。 - 前記第1の画素、前記第2の画素、前記第3の画素、および前記非基本色画素は、それぞれ、

容量素子と、

ドレインと、前記容量素子の一端に接続されたゲートと、前記容量素子の他端に接続されたソースとを含むトランジスタと

を有する

請求項1に記載の表示装置。 - 表示装置と

前記表示装置に対して動作制御を行う制御部と

を備え、

前記表示装置は、

第1の基本色光を発する第1の画素と、第2の基本色光を発する第2の画素と、基本色光以外の一の色光を発する非基本色画素との組み合わせから構成される第1の画素セットと、前記第1の基本色光を発する第1の画素と、第3の基本色光を発する第3の画素と、前記一の色光を発する非基本色画素との組み合わせから構成される第2の画素セットとを有し、前記第1の画素セットおよび前記第2の画素セットが、第1の方向および前記第1の方向と交差する第2の方向のいずれか一方または双方において、交互に配置された表示部と、

前記第2の基本色光に対応する第1の輝度情報マップから、前記第1の画素セットに対応する位置の第1の輝度情報を抽出し、その第1の輝度情報に基づいてその第1の画素セットに含まれる第2の画素を駆動するとともに、前記第3の基本色光に対応する第2の輝度情報マップから、前記第2の画素セットに対応する位置の第2の輝度情報を抽出し、その第2の輝度情報に基づいてその第2の画素セットに含まれる第3の画素を駆動する駆動部と

を有する

電子機器。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013062649A JP2014186257A (ja) | 2013-03-25 | 2013-03-25 | 表示装置および電子機器 |

| US14/192,929 US9224334B2 (en) | 2013-03-25 | 2014-02-28 | Display and electronic apparatus |

| TW103107310A TW201437994A (zh) | 2013-03-25 | 2014-03-04 | 顯示器及電子裝置 |

| CN201410101182.1A CN104078000B (zh) | 2013-03-25 | 2014-03-18 | 显示装置和电子设备 |

| KR1020140031400A KR102167309B1 (ko) | 2013-03-25 | 2014-03-18 | 표시 장치 및 전자 기기 |

| CN201420123693.9U CN204348299U (zh) | 2013-03-25 | 2014-03-18 | 显示装置和电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013062649A JP2014186257A (ja) | 2013-03-25 | 2013-03-25 | 表示装置および電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014186257A true JP2014186257A (ja) | 2014-10-02 |

| JP2014186257A5 JP2014186257A5 (ja) | 2015-04-02 |

Family

ID=51568831

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013062649A Pending JP2014186257A (ja) | 2013-03-25 | 2013-03-25 | 表示装置および電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9224334B2 (ja) |

| JP (1) | JP2014186257A (ja) |

| KR (1) | KR102167309B1 (ja) |

| CN (2) | CN104078000B (ja) |

| TW (1) | TW201437994A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016090812A (ja) * | 2014-11-05 | 2016-05-23 | 株式会社ジャパンディスプレイ | 表示装置 |

| WO2016117181A1 (ja) * | 2015-01-19 | 2016-07-28 | ソニー株式会社 | 表示装置及び電子機器 |

| JP7339402B2 (ja) | 2015-12-11 | 2023-09-05 | 株式会社半導体エネルギー研究所 | El表示装置、電子機器 |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014186257A (ja) * | 2013-03-25 | 2014-10-02 | Sony Corp | 表示装置および電子機器 |

| TWI674671B (zh) * | 2013-05-28 | 2019-10-11 | 日商新力股份有限公司 | 顯示裝置及電子機器 |

| JP2015079107A (ja) * | 2013-10-17 | 2015-04-23 | ソニー株式会社 | 表示装置、表示装置の駆動方法、及び、電子機器 |

| JP6486660B2 (ja) * | 2013-11-27 | 2019-03-20 | 株式会社半導体エネルギー研究所 | 表示装置 |

| CN103928496B (zh) * | 2014-01-27 | 2016-06-01 | 北京京东方光电科技有限公司 | 一种显示面板及其显示方法、显示装置 |

| CN103886809B (zh) * | 2014-02-21 | 2016-03-23 | 北京京东方光电科技有限公司 | 显示方法和显示装置 |

| CN104023219B (zh) * | 2014-05-30 | 2015-09-09 | 京东方科技集团股份有限公司 | 一种rgb信号到rgbw信号的图像转换方法及装置 |

| KR102280452B1 (ko) * | 2014-11-05 | 2021-07-23 | 삼성디스플레이 주식회사 | 표시장치 및 그의 구동방법 |

| EP3043558B1 (en) * | 2014-12-21 | 2022-11-02 | Production Resource Group, L.L.C. | Large-format display systems having color pixels and white pixels |

| CN104599599B (zh) * | 2015-02-13 | 2017-05-24 | 京东方科技集团股份有限公司 | 显示基板及其驱动方法和显示装置 |

| CN104614882B (zh) * | 2015-02-13 | 2017-06-16 | 京东方科技集团股份有限公司 | 显示基板及其驱动方法和显示装置 |

| CN104616597B (zh) * | 2015-02-13 | 2017-03-29 | 京东方科技集团股份有限公司 | 显示基板及其驱动方法和显示装置 |

| KR102326806B1 (ko) * | 2015-04-24 | 2021-11-15 | 엘지디스플레이 주식회사 | 서브 픽셀 배열 구조를 갖는 표시장치 |

| KR102401965B1 (ko) * | 2015-07-06 | 2022-05-25 | 삼성디스플레이 주식회사 | 반사형 액정 표시 장치 및 그 제조 방법 |

| JP2017040733A (ja) * | 2015-08-19 | 2017-02-23 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN105158997A (zh) * | 2015-08-31 | 2015-12-16 | 深超光电(深圳)有限公司 | 薄膜晶体管阵列基板 |

| KR101887533B1 (ko) * | 2015-12-04 | 2018-08-13 | 엘지디스플레이 주식회사 | 유기발광 표시장치 |

| TWI560495B (en) * | 2016-01-28 | 2016-12-01 | Au Optronics Corp | Display apparatus and display control method thereof |

| CN108628044B (zh) | 2017-03-22 | 2021-10-26 | 鸿富锦精密工业(深圳)有限公司 | 显示面板 |

| KR102490894B1 (ko) * | 2018-02-08 | 2023-01-25 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| JP7105098B2 (ja) * | 2018-05-01 | 2022-07-22 | Tianma Japan株式会社 | 表示装置 |

| WO2019216198A1 (ja) * | 2018-05-11 | 2019-11-14 | ソニーセミコンダクタソリューションズ株式会社 | 表示装置、表示装置の製造方法、及び、電子機器 |

| CN108681167B (zh) * | 2018-06-22 | 2021-09-03 | 厦门天马微电子有限公司 | 显示面板及显示装置 |

| CN109036257B (zh) * | 2018-10-24 | 2022-04-29 | 上海天马微电子有限公司 | 一种显示面板及其驱动方法和显示装置 |

| CN111933077A (zh) * | 2019-05-13 | 2020-11-13 | 三星显示有限公司 | 显示装置及其驱动方法 |

| CN112309329B (zh) * | 2019-08-02 | 2024-03-01 | 天马日本株式会社 | 显示装置 |

| KR20210043047A (ko) * | 2019-10-10 | 2021-04-21 | 삼성디스플레이 주식회사 | 표시장치 |

| KR20210069895A (ko) * | 2019-12-04 | 2021-06-14 | 엘지디스플레이 주식회사 | 표시 장치 |

| US11386835B2 (en) * | 2020-04-07 | 2022-07-12 | Rockwell Collins, Inc. | Pixel control architecture for micro-LED micro-display with reduced transistor count |

| CN115528192A (zh) * | 2020-06-17 | 2022-12-27 | 京东方科技集团股份有限公司 | 显示面板和显示装置 |

| KR20220006675A (ko) * | 2020-07-08 | 2022-01-18 | 삼성디스플레이 주식회사 | 표시 장치 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11266462A (ja) * | 1998-03-16 | 1999-09-28 | Nec Corp | 動画像符号化装置のプレフィルタ |

| JP2002359807A (ja) * | 2001-06-01 | 2002-12-13 | Sony Corp | ディジタルスチルカメラ |

| JP2004199071A (ja) * | 2002-12-17 | 2004-07-15 | Samsung Electronics Co Ltd | 映像信号の表示方法および表示装置 |

| JP2008096549A (ja) * | 2006-10-10 | 2008-04-24 | Hitachi Displays Ltd | カラー表示装置,液晶表示装置、および半透過液晶表示装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1388818B1 (en) * | 2002-08-10 | 2011-06-22 | Samsung Electronics Co., Ltd. | Method and apparatus for rendering image signal |

| US7515122B2 (en) * | 2004-06-02 | 2009-04-07 | Eastman Kodak Company | Color display device with enhanced pixel pattern |

| KR101064466B1 (ko) | 2009-07-29 | 2011-09-16 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시장치 |

| KR20110129531A (ko) | 2010-05-26 | 2011-12-02 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시장치의 화소배열구조 |

| JP5849981B2 (ja) * | 2013-03-25 | 2016-02-03 | ソニー株式会社 | 表示装置および電子機器 |

| JP2014186257A (ja) * | 2013-03-25 | 2014-10-02 | Sony Corp | 表示装置および電子機器 |

-

2013

- 2013-03-25 JP JP2013062649A patent/JP2014186257A/ja active Pending

-

2014

- 2014-02-28 US US14/192,929 patent/US9224334B2/en active Active

- 2014-03-04 TW TW103107310A patent/TW201437994A/zh unknown

- 2014-03-18 CN CN201410101182.1A patent/CN104078000B/zh active Active

- 2014-03-18 CN CN201420123693.9U patent/CN204348299U/zh not_active Withdrawn - After Issue

- 2014-03-18 KR KR1020140031400A patent/KR102167309B1/ko active IP Right Grant

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11266462A (ja) * | 1998-03-16 | 1999-09-28 | Nec Corp | 動画像符号化装置のプレフィルタ |

| JP2002359807A (ja) * | 2001-06-01 | 2002-12-13 | Sony Corp | ディジタルスチルカメラ |

| JP2004199071A (ja) * | 2002-12-17 | 2004-07-15 | Samsung Electronics Co Ltd | 映像信号の表示方法および表示装置 |

| JP2008096549A (ja) * | 2006-10-10 | 2008-04-24 | Hitachi Displays Ltd | カラー表示装置,液晶表示装置、および半透過液晶表示装置 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016090812A (ja) * | 2014-11-05 | 2016-05-23 | 株式会社ジャパンディスプレイ | 表示装置 |

| US10263047B2 (en) | 2014-11-05 | 2019-04-16 | Japan Display Inc. | Display device |

| WO2016117181A1 (ja) * | 2015-01-19 | 2016-07-28 | ソニー株式会社 | 表示装置及び電子機器 |

| CN107111974A (zh) * | 2015-01-19 | 2017-08-29 | 索尼公司 | 显示装置和电子设备 |

| US10553143B2 (en) | 2015-01-19 | 2020-02-04 | Sony Corporation | Display apparatus and electronic appliance |

| CN107111974B (zh) * | 2015-01-19 | 2020-09-11 | 索尼公司 | 显示装置和电子设备 |

| JP7339402B2 (ja) | 2015-12-11 | 2023-09-05 | 株式会社半導体エネルギー研究所 | El表示装置、電子機器 |

| US11881489B2 (en) | 2015-12-11 | 2024-01-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN104078000A (zh) | 2014-10-01 |

| TW201437994A (zh) | 2014-10-01 |

| US9224334B2 (en) | 2015-12-29 |

| CN204348299U (zh) | 2015-05-20 |

| KR102167309B1 (ko) | 2020-10-19 |

| KR20140116805A (ko) | 2014-10-06 |

| CN104078000B (zh) | 2017-04-12 |

| US20140285542A1 (en) | 2014-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102339431B1 (ko) | 표시 장치 및 전자 기기 | |

| KR102167309B1 (ko) | 표시 장치 및 전자 기기 | |

| TWI623094B (zh) | 顯示單元及電子裝置 | |

| JP6074587B2 (ja) | 表示パネル、表示装置ならびに電子機器 | |

| JP6159965B2 (ja) | 表示パネル、表示装置ならびに電子機器 | |

| US10504396B2 (en) | Display device and electronic apparatus | |

| JP6074585B2 (ja) | 表示装置および電子機器、ならびに表示パネルの駆動方法 | |

| JP2012194256A (ja) | 表示装置および電子機器 | |

| TWI569246B (zh) | A display device, a driving device, a driving method, and an electronic device | |

| KR102554380B1 (ko) | 전계발광표시장치 | |

| WO2015170614A1 (ja) | 表示装置および電子機器 | |

| KR102653574B1 (ko) | 투명 표시 장치 | |

| TW202312131A (zh) | 顯示面板及包含該顯示面板的顯示裝置 | |

| KR20210084084A (ko) | 표시 장치 | |

| JP2010152222A (ja) | 表示装置、表示装置の画素レイアウト方法および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150625 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150804 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150916 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160405 |