JP2014138048A - 炭化珪素半導体装置 - Google Patents

炭化珪素半導体装置 Download PDFInfo

- Publication number

- JP2014138048A JP2014138048A JP2013005132A JP2013005132A JP2014138048A JP 2014138048 A JP2014138048 A JP 2014138048A JP 2013005132 A JP2013005132 A JP 2013005132A JP 2013005132 A JP2013005132 A JP 2013005132A JP 2014138048 A JP2014138048 A JP 2014138048A

- Authority

- JP

- Japan

- Prior art keywords

- region

- electric field

- silicon carbide

- guard ring

- width

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims abstract description 145

- 229910010271 silicon carbide Inorganic materials 0.000 title claims abstract description 142

- 239000004065 semiconductor Substances 0.000 title claims abstract description 74

- 230000005684 electric field Effects 0.000 claims abstract description 242

- 239000000758 substrate Substances 0.000 claims abstract description 116

- 230000002093 peripheral effect Effects 0.000 claims description 45

- 230000004888 barrier function Effects 0.000 claims description 7

- 239000012535 impurity Substances 0.000 description 92

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 42

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 32

- 239000000463 material Substances 0.000 description 26

- 229910052782 aluminium Inorganic materials 0.000 description 25

- 238000000034 method Methods 0.000 description 25

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 24

- 230000001681 protective effect Effects 0.000 description 24

- 230000008569 process Effects 0.000 description 22

- 238000009826 distribution Methods 0.000 description 20

- 239000010410 layer Substances 0.000 description 20

- 229910052759 nickel Inorganic materials 0.000 description 19

- 239000010936 titanium Substances 0.000 description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 18

- 229910052757 nitrogen Inorganic materials 0.000 description 16

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 15

- 238000010586 diagram Methods 0.000 description 15

- 229910052719 titanium Inorganic materials 0.000 description 15

- 230000015556 catabolic process Effects 0.000 description 13

- 238000005468 ion implantation Methods 0.000 description 13

- 238000004519 manufacturing process Methods 0.000 description 13

- 230000007423 decrease Effects 0.000 description 12

- 238000010438 heat treatment Methods 0.000 description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 229910052710 silicon Inorganic materials 0.000 description 10

- 239000010703 silicon Substances 0.000 description 10

- 230000004048 modification Effects 0.000 description 9

- 238000012986 modification Methods 0.000 description 9

- 235000012239 silicon dioxide Nutrition 0.000 description 9

- 239000000377 silicon dioxide Substances 0.000 description 9

- 229910045601 alloy Inorganic materials 0.000 description 7

- 239000000956 alloy Substances 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 230000008859 change Effects 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 229910052709 silver Inorganic materials 0.000 description 6

- 239000004332 silver Substances 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 5

- 238000004364 calculation method Methods 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 230000004913 activation Effects 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 238000002360 preparation method Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- -1 for example Chemical compound 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 3

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000003763 carbonization Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000002050 diffraction method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000001294 propane Substances 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/6606—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by variation of the electric current supplied or the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. two-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System

- H01L29/1608—Silicon carbide

Abstract

【課題】素子領域を狭くしすぎることなく耐圧を向上させることができる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置1は、炭化珪素基板10を備えている。炭化珪素基板10は、半導体素子部7が設けられた素子領域IRと、平面視において素子領域IRを取り囲む終端領域ORとからなる。半導体素子部7は第1導電型のドリフト領域12を含む。終端領域ORは、素子領域IRと接し、かつ第1導電型とは異なる第2導電型の第1の電界緩和領域2と、平面視において第1の電界緩和領域よりも外側に配置され、第2導電型を有し、かつ第1の電界緩和領域2と離間している第2の電界緩和領域3とを含む。第1の電界緩和領域2の幅W1をドリフト領域12の厚みTで除した比は、0.5以上1.83以下である。

【選択図】図1

【解決手段】炭化珪素半導体装置1は、炭化珪素基板10を備えている。炭化珪素基板10は、半導体素子部7が設けられた素子領域IRと、平面視において素子領域IRを取り囲む終端領域ORとからなる。半導体素子部7は第1導電型のドリフト領域12を含む。終端領域ORは、素子領域IRと接し、かつ第1導電型とは異なる第2導電型の第1の電界緩和領域2と、平面視において第1の電界緩和領域よりも外側に配置され、第2導電型を有し、かつ第1の電界緩和領域2と離間している第2の電界緩和領域3とを含む。第1の電界緩和領域2の幅W1をドリフト領域12の厚みTで除した比は、0.5以上1.83以下である。

【選択図】図1

Description

本発明は、炭化珪素半導体装置に関するものであり、より特定的には、終端領域を有する炭化珪素半導体装置に関するものである。

近年、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)などの半導体装置の高耐圧化、低損失化、高温環境下での使用などを可能とするため、半導体装置を構成する材料として炭化珪素の採用が進められつつある。炭化珪素は、従来から半導体装置を構成する材料として広く使用されている珪素に比べてバンドギャップが大きいワイドバンドギャップ半導体である。そのため、半導体装置を構成する材料として炭化珪素を採用することにより、半導体装置の高耐圧化、オン抵抗の低減などを達成することができる。また、炭化珪素を材料として採用した半導体装置は、珪素を材料として採用した半導体装置に比べて、高温環境下で使用された場合の特性の低下が小さいという利点も有している。

たとえば特開2003−101039号公報(特許文献1)には、複数のガードリングが同心円状に設けられ、最内周のガードリング部の内部に、当該最内周のガードリング部よりも高い不純物濃度を有する領域を有する高耐圧炭化珪素半導体装置が記載されている。また特開2008−270412号公報(特許文献2)には、p型リサーフ部の外周側に複数のp型ガードリング部が設けられた炭化珪素SBD(Schottky Barrier Diode)が開示されている。

さらに、松波弘之、外3名、「半導体SiC技術と応用 第2版」、日刊工業新聞社、2011年9月20日、p352−p353(非特許文献1)には、空乏化する程度の低濃度のp型層を形成して電界強度を緩和する構造のJTE(Junction Termination Extension)領域を有する炭化珪素SBDが記載されている。当該文献によれば、外側にいくほど不純物濃度が低くなるガードリング部を形成することで耐圧を向上させることが記載されている。

松波弘之、外3名、「半導体SiC技術と応用 第2版」、日刊工業新聞社、2011年9月20日、p352−p353

炭化珪素半導体装置の耐圧を高くするためには、炭化珪素半導体装置の終端領域を広くする必要がある。しかしながら、単に炭化珪素半導体装置の終端領域を広くすると炭化珪素半導体装置の素子領域が狭くなってしまう。

本発明は、上記課題に鑑みてなされたものであり、その目的は、素子領域を狭くしすぎることなく耐圧を向上させることができる炭化珪素半導体装置を提供することである。

発明者らは、炭化珪素半導体装置の終端領域の構造と電界強度との関係について鋭意研究を行った結果、以下の知見を得て本発明を見出した。終端領域の幅を一定に保った状態で、JTE領域の幅およびガードリング部の本数を変化させて、電界強度のシミュレーションを行った。その結果、JTE領域の幅をドリフト領域の厚みで除した比がある値より大きくなると、JTE領域の端部における電界強度が急激に減少することが分かった。またJTE領域の幅をドリフト領域の厚みで除した比がある値より大きくなると、最外周のガードリング部の端部における電界強度が急激に増加することが分かった。

具体的には、図1を参照して、MOSFETの素子領域における、ウェル領域の角部(位置A)の電界強度と、ウェル領域とJTE領域(第1の電界緩和領域)の角部との接点(位置B)の電界強度と、MOSFETの終端領域におけるJTE領域(第1の電界緩和領域)の外周側の角部(位置C)の電界強度と、最外周のガードリング部の外周側の角部(位置D)における電界強度とを計算し、各位置における電界強度を比較した。

電界強度シミュレーションの結果、JTE領域の幅をドリフト領域の厚みで除した比が0.5以上になると、ウェル領域とJTE領域との境界領域における電界強度が急激に減少することが分かった。またJTE領域の幅をドリフト領域の厚みで除した比が1.83より大きくなると、最外周のガードリング部の外周側の角部における電界強度が急激に増加することが分かった。つまり、JTE領域の幅をドリフト領域の厚みで除した比が0.5以上1.83以下の場合、ウェル領域とJTE領域との境界領域およびガードリング部の角部の双方の電界強度を低減することができる。

本発明に係る炭化珪素半導体装置は、炭化珪素基板を備えている。炭化珪素基板は、半導体素子部が設けられた素子領域と、平面視において素子領域を取り囲む終端領域とからなる。半導体素子部は第1導電型のドリフト領域を含む。終端領域は、素子領域と接し、かつ第1導電型とは異なる第2導電型の第1の電界緩和領域と、平面視において第1の電界緩和領域よりも外側に配置され、第2導電型を有し、かつ第1の電界緩和領域と離間している第2の電界緩和領域とを含む。第1の電界緩和領域の幅をドリフト領域の厚みで除した比は、0.5以上1.83以下である。なお、本発明において、幅とは炭化珪素基板の第1の主面と平行な方向の距離を示し、厚みとは炭化珪素基板の第1の主面と垂直な方向の距離を示す。

本発明に係る炭化珪素半導体装置によれば、第1の電界緩和領域の幅をドリフト領域の厚みで除した比は、0.5以上1.83以下である。これにより、第1の電界緩和領域およびの第2の電界緩和領域の双方の電界強度を低減することができる。結果として、炭化珪素半導体装置の素子領域を狭くしすぎることなく耐圧を向上させることができる。

上記に係る炭化珪素半導体装置において好ましくは、第2の電界緩和領域は、複数のガードリング部を含む。これにより、終端領域の電界強度をさらに低減することができる。

上記に係る炭化珪素半導体装置において好ましくは、複数のガードリング部の各々の幅は、第1の電界緩和領域の幅よりも小さい。これにより、終端領域の電界強度をさらに低減することができる。

上記に係る炭化珪素半導体装置において好ましくは、複数のガードリング部から任意の2つのガードリング部を選択した場合において、平面視において外周側に配置されているガードリング部の幅は、内周側に配置されているガードリング部の幅以下であり、かつ最外周側に配置されているガードリング部の幅は最内周側に配置されているガードリング部の幅よりも小さい。

これにより、炭化珪素基板の中心から外周に向かう方向における等電界線の変化が緩やかになる。結果として、繰り返し電圧を印加する場合における耐圧寿命(信頼性)を向上することができる。

上記に係る炭化珪素半導体装置において好ましくは、複数のガードリング部の本数は、6本以上15本以下である。これにより、終端領域の電界強度を効率的に低減することができる。

上記に係る炭化珪素半導体装置において好ましくは、複数のガードリング部の本数は、12本以上15本以下である。これにより、終端領域の電界強度を効率的に低減することができる。

上記に係る炭化珪素半導体装置において好ましくは、炭化珪素半導体装置は、MOSFET、IGBT(Insulated Gate Bipolar Transistor)、ショットキーバリアダイオードおよびP/Nダイオードのいずれかである。これにより、素子領域を狭くしすぎることなく耐圧を向上させることができるMOSFET、IGBT、ショットキーバリアダイオードおよびP/Nダイオードを得ることができる。

本発明によれば、素子領域を狭くしすぎることなく耐圧を向上可能な炭化珪素半導体装置を提供することができる。

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付し、その説明は繰返さない。また、本明細書中の結晶学的記載においては、個別方位を[]、集合方位を<>、個別面を()、集合面を{}でそれぞれ示している。また、負の指数については、結晶学上、”−”(バー)を数字の上に付けることになっているが、本明細書中では、数字の前に負の符号を付けている。また角度の記載には、全方位角を360度とする系を用いている。

(実施の形態1)

まず本発明の実施の形態1に係る炭化珪素半導体装置としてのMOSFET1の構成について説明する。

(実施の形態1)

まず本発明の実施の形態1に係る炭化珪素半導体装置としてのMOSFET1の構成について説明する。

図1を参照して、MOSFET1は、炭化珪素基板10と、絶縁膜15と、ゲート電極27と、ソース電極16と、ドレイン電極20とを主に有する。

図1および図2を参照して、MOSFET1の炭化珪素基板10は、素子領域IR(活性領域)と、平面視において素子領域IRを取り囲む終端領域OR(無効領域)とにより構成されている。終端領域ORは、第1の電界緩和領域2と、第2の電界緩和領域3とを含む。素子領域IRには半導体素子部7としてのMOSFET部が設けられている。半導体素子部7はn型(第1導電型)のドリフト領域12を含む。

第1の電界緩和領域2はJTE領域であり、素子領域IRと接し、n型(第1導電型)とは異なるp型(第2導電型)を有する領域である。第2の電界緩和領域3はガードリング領域であり、平面視において第1の電界緩和領域よりも外側に配置され、かつp型を有している。第2の電界緩和領域3は、第1の電界緩和領域2と離間している設けられている。

第1の電界緩和領域2および第2の電界緩和領域3の各々に含まれる不純物の濃度は、ウェル領域の不純物濃度よりも低い。第1の電界緩和領域2および第2の電界緩和領域3の各々のドーズ量は、たとえば1.3×1013cm-2以上1.4×1013cm-2以下である。第1の電界緩和領域2の幅W1は、15μm程度以上55μm程度以下であることが好ましく、31μm程度以上55μm程度以下であることがより好ましく、15μm程度以上39μm程度以下であってもよい。第1の電界緩和領域2および第2の電界緩和領域3の各々の厚みは、たとえば0.5μm程度以上0.8μm程度以下である。

好ましくは、第2の電界緩和領域3は、複数のガードリング部3a、3b、3cを含んでいる。第2の電界緩和領域3は、6本以上15本以下のガードリング部から構成されていることが好ましく、9本以上15本以下のガードリング部から構成されていることがより好ましく、12本以上15本以下のガードリング部から構成されていることがさらに好ましい。なお、本実施の形態においるMOSFET1の耐圧はたとえば1.7kV程度以上4.0kV程度以下であり、たとえば2.2kV程度以上3.8kV程度以下であってもよい。

炭化珪素基板10は、たとえばポリタイプ4Hの六方晶炭化珪素からなり、互いに対向する第1の主面10aおよび第2の主面10bを有している。炭化珪素基板10の素子領域IRの半導体素子部7は、n+基板11と、ドリフト領域12と、ウェル領域13と、ソース領域14と、p+領域18とを主に有する。

n+基板11は、たとえばポリタイプ4Hの六方晶炭化珪素からなり導電型がn型の基板である。n+基板11は、たとえばN(窒素)などの不純物を高濃度で含んでいる。n+基板11に含まれる窒素などの不純物濃度はたとえば1.0×1018cm-3程度である。なお、n+基板11などのn型領域に、窒素などのドナー不純物とアルミニウムなどのアクセプタ不純物とを含んでいる場合、当該n型領域の不純物濃度は、不純物濃度=ドナー不純物の不純物濃度(Nd)−アクセプタ不純物の不純物濃度(Na)として計算される。

ドリフト領域12は、たとえばポリタイプ4Hの六方晶炭化珪素からなり、n型(第1導電型)を有するエピタキシャル層である。ドリフト領域12に含まれる不純物は、たとえば窒素である。ドリフト領域12における不純物濃度は、n+基板11における不純物濃度よりも低い。ドリフト領域12に含まれる窒素などの不純物濃度はたとえば2.0×1015cm-3程度以上5.0×1015cm-3程度以下である。好ましくは、ドリフト領域12の厚みTは20μm程度以上35μm程度以下であり、より好ましくは23μm程度以上30μm程度以下である。

第1の電界緩和領域としてのJTE領域2の幅W1をドリフト領域12の厚みTで除した比は、0.5以上1.83以下であり、好ましくは、1.03以上1.83以下である。第1の電界緩和領域としてのJTE領域2の幅W1をドリフト領域12の厚みTで除した比は、0.65以上1.70以下であってもよい。

ウェル領域13はn型とは異なるp型を有する領域である。ウェル領域13に含まれる不純物は、たとえばAl(アルミニウム)、B(ホウ素)などである。好ましくは、ウェル領域13の表面(つまり第1の主面10a)に含まれるアルミニウムなどの不純物濃度は1×1016cm-3程度以上5×1017cm-3程度以下である。またウェル領域13の深部における不純物濃度は1×1018cm-3程度である。ウェル領域13の厚みは、たとえば0.5μm程度以上1.0μm程度以下である。ウェル領域13と第1の電界緩和領域2とは素子領域IRおよび終端領域ORの境界線2aにおいて接している。なお、ウェル領域13などのp型領域に、窒素などのドナー不純物とアルミニウムなどのアクセプタ不純物とを含んでいる場合、当該p型領域の不純物濃度は、不純物濃度=アクセプタ不純物の不純物濃度(Na)−ドナー不純物の不純物濃度(Nd)として計算される。

ソース領域14はn型を有する領域である。ソース領域14は、ウェル領域13によっておよびドリフト領域12と隔てられている。またソース領域14は、第1の主面10aを含み、かつウェル領域13に取り囲まれるように、ウェル領域13の内部に形成されている。ソース領域14は、たとえばP(リン)などの不純物を、たとえば1×1020cm-3程度の濃度で含んでいる。ソース領域14に含まれる不純物の濃度は、ドリフト領域12に含まれる不純物の濃度よりも高い。

p+領域18はp型を有する領域である。p+領域18は、ウェル領域13およびソース領域14と接して形成されている。p+領域18は、たとえばアルミニウムやホウ素などの不純物を、たとえば1×1020cm-3程度の濃度で含んでいる。p+領域18に含まれる不純物の濃度は、ウェル領域13に含まれる不純物の濃度よりも高い。

絶縁膜15は、ウェル領域13に形成されるチャネル領域CHと対向する位置に設けられたゲート絶縁膜部15aと、炭化珪素基板10の端部10cに露出し、かつ第1の電界緩和領域2および第2の電界緩和領域3に接する絶縁膜部15bとを含む。ゲート絶縁膜部15aは、一方のソース領域14の上部表面から他方のソース領域14の上部表面にまで延在するように、ウェル領域13、ソース領域14およびドリフト領域12に接して形成されている。絶縁膜15はたとえば二酸化珪素からなっている。好ましくは、絶縁膜15の厚み(第1の主面10aの法線方向に沿った絶縁膜15の距離)は、45nm程度以上55nm程度以下である。

ゲート電極27は、一方のソース領域14上から他方のソース領域14上にまで延在するように、ゲート絶縁膜部15a上に接触して配置されている。ゲート電極27は、たとえば不純物の添加されたポリシリコン、アルミニウムなどの導電体からなっている。

ソース電極16は、絶縁膜15、ソース領域14およびp+領域18と接している。好ましくは、ソース電極16は、好ましくは、ニッケルおよびシリコンを有する材料からなる。ソース電極16は、チタン、アルミニウムおよびシリコンを有する材料からなっていてもよい。好ましくは、ソース電極16はソース領域14およびp+領域18とオーミック接合している。

ドレイン電極20は、炭化珪素基板10の第2の主面10bに接触して形成されている。このドレイン電極20は、たとえば上記ソース電極16と同様の構成を有していてもよいし、ニッケルなど、n+基板11とオーミック接合可能な他の材料からなっていてもよい。これにより、ドレイン電極20はn+基板11と電気的に接続されている。

パッド電極65は、ソース電極16に接し、かつ層間絶縁膜71を覆うように形成されている。パッド電極65はたとえばアルミニウムからなる。パッド電極65および絶縁膜部15bに接して保護膜70が形成されている。また、n+基板11と接してドレイン電極20が配置されている。ドレイン電極20はたとえばニッケルからなる。さらに、ドレイン電極20に接してたとえばチタン、ニッケル、銀やそれらからなる合金からなる裏面保護電極50が配置されている。

なお、JTE領域2の内周側の端部から最外周のガードリング部3cの外周側の端部までの距離はたとえば20μm程度以上200μm程度以下であり、好ましくは39μm程度以上200μm程度以下である。またJTE領域2の内周側の端部から最外周のガードリング部3cの外周側の端部までの距離は、ドリフト領域12の厚みTの2倍以上であることが好ましい。

図3を参照して、本実施の形態のMOSFETの第1の変形例の構成について説明する。

図3に示すように、第1の変形例に係るMOSFET1の炭化珪素基板10の素子領域IRに設けられた半導体素子部7は、ウェル領域13を含み、ウェル領域13に接して第1の電界緩和領域2が配置されている。ウェル領域13は、ソース電極16に接しているp+領域18と、ゲート絶縁膜部15aおよびソース電極16に接しているソース領域14とを含む。第1の変形例における半導体素子部7の構造は、図1で説明した半導体素子部7の構造と同様であってもよい。

第1の電界緩和領域2の外周側に、第2の電界緩和領域3が設けられており、第2の電界緩和領域3は、互いに離間した9本のガードリング部3a〜3iを含む。第2の電界緩和領域3は、同じ幅を有する複数のガードリング部3a〜3iを含んでいてもよい。第1の電界緩和領域2の幅W1はたとえば15μmであり、9本のガードリング部3a〜3gの各々の幅W2〜W10はたとえば5μmである。第1の電界緩和領域2と第2の電界緩和領域3との間隔d1はたとえば3μm程度以上5μm程度以下であり、隣接するガードリング部3a〜3gの間隔d2はたとえば3μm程度以上5μm程度以下である。

図4を参照して、本実施の形態のMOSFETの第2の変形例の構成について説明する。

図4に示すように、第2の変形例に係るMOSFETの第2の電界緩和領域は7本のガードリング部3a〜3bから構成されている。各ガードリング部3a〜3gの幅W2〜W8は、内周側から外周側にいくにつれて小さくなることが好ましい。各ガードリング部3a〜3gの幅は単調に減少してもよいし段階的に減少してもよい。つまり、複数のガードリング部の任意の2つのガードリング部の内、平面視において外周側のガードリング部の幅は、内周側のガードリング部の幅以下であり、かつ最外周側のガードリング部の幅は最内周側のガードリング部の幅よりも小さいことが好ましい。

第2の変形例における、第1の電界緩和領域2の幅W1はたとえば15μmである。最内周側のガードリング部3aの幅を幅W2とし、最外周側のガードリング部3iの幅をW8としたとき、最内周側のガードリング部3aおよび最外周側のガードリング部3iの間の各ガードリング部の幅は、幅W2=10μm、幅W3=8μm、幅W4=8μm、幅W5=6μm、幅W6=5μm、幅W7=5μm、幅W8=5μmである。なお、第1の電界緩和領域2と第2の電界緩和領域3との間隔d1はたとえば3μm程度以上5μm程度以下であり、隣接するガードリング部3a〜3iの間隔d2はたとえば3μm程度以上5μm程度以下である。

次にMOSFET1の動作について説明する。ゲート電極27に閾値以下の電圧を与えた状態、すなわちオフ状態では、ゲート絶縁膜部15aの直下に位置するウェル領域13とドリフト領域12との間が逆バイアスとなり、非導通状態となる。一方、ゲート電極27に正の電圧を印加していくと、ウェル領域13のゲート絶縁膜部15aと接触する付近であるチャネル領域CHにおいて、反転層が形成される。その結果、ソース領域14とドリフト領域12とが電気的に接続され、ソース電極16とドレイン電極20との間に電流が流れる。

次に、本実施の形態に係るMOSFET1の製造方法について説明する。

図5を参照して、まず基板準備工程によって炭化珪素基板10が準備される。具体的には、六方晶炭化珪素からなるn+基板11の一方の主面上にエピタキシャル成長によりドリフト領域12が形成される。エピタキシャル成長は、たとえば原料ガスとしてSiH4(シラン)とC3H8(プロパン)との混合ガスを採用して実施することができる。このとき、不純物として、たとえばN(窒素)が導入される。これにより、n+基板11に含まれる不純物よりも低い濃度の不純物を含むドリフト領域12が形成される。

図5を参照して、まず基板準備工程によって炭化珪素基板10が準備される。具体的には、六方晶炭化珪素からなるn+基板11の一方の主面上にエピタキシャル成長によりドリフト領域12が形成される。エピタキシャル成長は、たとえば原料ガスとしてSiH4(シラン)とC3H8(プロパン)との混合ガスを採用して実施することができる。このとき、不純物として、たとえばN(窒素)が導入される。これにより、n+基板11に含まれる不純物よりも低い濃度の不純物を含むドリフト領域12が形成される。

炭化珪素基板10は互いに対向する第1の主面10aおよび第2の主面10bを有する。炭化珪素基板10の第1の主面10aは、たとえば{0001}面である。

次に、たとえばCVDにより、炭化珪素基板10の第1の主面10a上に二酸化珪素からなる酸化膜が形成される。そして、酸化膜の上にレジストが塗布された後、露光および現像が行なわれ、所望のウェル領域13の形状に応じた領域に開口を有するレジスト膜が形成される。そして、当該レジスト膜をマスクとして用いて、たとえばRIE(Reactive Ion Etching;反応性イオンエッチング)により酸化膜が部分的に除去されることによって、ドリフト領域12上に開口パターンを有する酸化膜からなるマスク層が形成される。

次に、イオン注入工程が実施される。図6を参照して、イオン注入工程では、炭化珪素基板10の第1の主面10a対してイオンが注入されることにより、炭化珪素基板10の素子領域IRにウェル領域13、ソース領域14およびp+領域18が形成され、炭化珪素基板10の終端領域ORに第1の電界緩和領域としてのJTE領域2および第2の電界緩和領域3が形成される。

具体的には、上記レジスト膜を除去した上で、当該マスク層をマスクとして用いて、Alなどの不純物をドリフト領域12に対してイオン注入することにより、ウェル領域13が形成される。また、P(リン)などのn型不純物がドリフト領域12にイオン注入により導入されることによりソース領域14が形成される。次に、Al、Bなどの不純物がドリフト領域12にイオン注入により導入されることによりp+領域18が形成される。300℃から500℃に炭化珪素基板10を加熱してイオン注入が行われてもよい。

またAlなどの不純物をドリフト領域12に対してイオン注入することにより、JTE領域2および第2の電界緩和領域3が形成される。なお、JTE領域2はウェル領域13と接するように形成される。JTE領域2における不純物濃度はウェル領域13における不純物濃度よりも低いことが好ましい。p+領域18はJTE領域2に接して形成されてもよいし、JTE領域2に接することなくウェル領域13内に形成されてもよい。

次に、活性化アニール工程が実施される。上記イオン注入によって導入された不純物を活性化させる熱処理が実施される。具体的には、イオン注入が実施された炭化珪素基板10が、たとえばAr(アルゴン)雰囲気中において1700℃程度に加熱され、30分間程度保持される。

次に、熱酸化膜形成工程が実施される。具体的には、図7を参照して、イオン注入領域が形成された炭化珪素基板10が熱酸化される。熱酸化は、たとえば酸素雰囲気中で1300℃程度に加熱し、40分間程度保持することにより実施することができる。これにより、炭化珪素基板10の第1の主面10a上に二酸化珪素からなる絶縁膜15が形成される。窒素やNO、N2Oを含む雰囲気中で1100℃から1300℃に加熱することによってSiO2/SiCの界面に形成されるエネルギー準位を低減する工程を行ってもよい。またAr雰囲気中での熱処理を行っても良い。

次に、ゲート電極形成工程が実施される。具体的には、図1を参照して、たとえば導電体であるポリシリコン、アルミニウムなどからなるゲート電極27が、一方のソース領域14上から他方のソース領域14上にまで延在するとともに、絶縁膜15に接触するように形成される。ゲート電極27の材料としてポリシリコンを採用する場合、当該ポリシリコンは、リンが1×1020cm-3を超える高い濃度で含まれていてもよい。その後、ゲート電極27を覆うように、たとえば二酸化珪素からなる層間絶縁膜71が形成される。

次に、電極形成工程が実施される。具体的には、図1を参照して、たとえばニッケルおよびシリコンを含む材料からなるソース電極16がソース領域14およびp+領域18に接して形成される。ソース電極16は、チタン、アルミニウムおよびシリコンを含む材料であってもよい。同様に、炭化珪素基板10の第2の主面10bに接するドレイン電極20が形成される。ドレイン電極20を形成する材料は、ニッケルおよびシリコンを含む材料であってもよいし、チタン、アルミニウムおよびシリコンを含む材料であってもよい。その後、ソース電極16が形成された炭化珪素基板10を1000℃程度に加熱することにより、炭化珪素基板10のソース領域14およびp+領域18とオーミック接触するソース電極16が形成される。ソース電極16と接し、たとえばアルミニウムからなるパッド電極65が形成される。また、たとえばチタン、ニッケルおよび銀を含む裏面保護電極50が形成される。以上の様に、図1に示すMOSFET1が完成する。

なお、本実施の形態ではとしてプレナー型MOSFETを例に挙げて説明したが、トレンチ型MOSFETであってもよい。

次に、本実施の形態に係るMOSFET1の作用効果について説明する。

本実施の形態に係るMOSFETによれば、JTE領域2の幅W1をドリフト領域12の厚みTで除した比は、0.5以上1.83以下である。これにより、ウェル領域13とJTE領域2との境界領域(位置B)および第2の電界緩和領域3の外周側の角部(位置D)の双方における電界強度を低減することができる。結果として、素子領域を狭くしすぎることなく耐圧を向上させることができるMOSFETを得ることができる。

本実施の形態に係るMOSFETによれば、JTE領域2の幅W1をドリフト領域12の厚みTで除した比は、0.5以上1.83以下である。これにより、ウェル領域13とJTE領域2との境界領域(位置B)および第2の電界緩和領域3の外周側の角部(位置D)の双方における電界強度を低減することができる。結果として、素子領域を狭くしすぎることなく耐圧を向上させることができるMOSFETを得ることができる。

また本実施の形態に係るMOSFETによれば、第2の電界緩和領域3は、複数のガードリング部を含む。これにより、終端領域ORの電界強度をさらに低減することができる。

さらに本実施の形態に係るMOSFETによれば、複数のガードリング部の各々の幅は、JTE領域2の幅W1よりも小さい。これにより、終端領域ORの電界強度をさらに低減することができる。また複数のガードリング部の各々の幅は3μm以上である。これにより、容易にガードリング部を製造することができる。

さらに本実施の形態に係るMOSFETによれば、複数のガードリング部から任意の2つのガードリング部を選択した場合において、平面視において外周側に配置されているガードリング部の幅は、内周側に配置されているガードリング部の幅以下であり、かつ最外周側に配置されているガードリング部の幅は最内周側に配置されているガードリング部の幅よりも小さい。これにより、炭化珪素基板10の中心から端部10cに向かう方向における等電界線の変化が緩やかになる。結果として、繰り返し電圧を印加する場合における耐圧寿命(信頼性)を向上することができる。

さらに本実施の形態に係るMOSFETによれば、複数のガードリング部の本数は、6本以上15本以下である。これにより、特にゲート電圧が2.2kVの場合において、終端領域ORの電界強度を効率的に低減することができる。

さらに本実施の形態に係るMOSFETによれば、複数のガードリング部の本数は、12本以上15本以下である。これにより、特にゲート電圧が3.3kVの場合において、終端領域ORの電界強度を効率的に低減することができる。

さらに本実施の形態に係る炭化珪素半導体装置によれば、炭化珪素半導体装置は、MOSFETである。これにより、素子領域を狭くしすぎることなく耐圧を向上させることができるMOSFETを得ることができる。

(実施の形態2)

次に、本発明の実施の形態2に係る炭化珪素半導体装置としてのIGBTの構成について説明する。

(実施の形態2)

次に、本発明の実施の形態2に係る炭化珪素半導体装置としてのIGBTの構成について説明する。

図2および図8を参照して、IGBT101の炭化珪素基板10は、素子領域IR(活性領域)と、平面視において素子領域IRを取り囲む終端領域OR(無効領域)とにより構成されている。終端領域ORは、第1の電界緩和領域2と、第2の電界緩和領域3を含む。素子領域IRには半導体素子部7としてのIGBT部が設けられている。半導体素子部7はn型(第1導電型)のドリフト領域12を含む。なお、本実施の形態に係るIGBT101の終端領域ORの構造は、実施の形態1で説明したMOSFET1の終端領域ORの構造と同様である。

図8を参照して、本実施の形態のIGBT101は、炭化珪素基板10と、ゲート絶縁膜215と、ゲート電極227と、層間絶縁膜221と、エミッタコンタクト電極208と、エミッタ配線219と、コレクタ電極230と、コレクタ配線240とを主に有する。

炭化珪素基板10は、互いに対向する第1の主面10aおよび第2の主面10bを有する。炭化珪素基板10の素子領域IRに設けられている半導体素子部7は、コレクタ層211と、ドリフト領域212と、ウェル領域213と、エミッタ領域214と、p+領域202とを含む。コレクタ層211は、炭化珪素基板10の第2の主面10bに接して配置されたp型領域(第2のp型領域)である。コレクタ層211、ドリフト領域212、ウェル領域213、エミッタ領域214、p+領域202の各々は、六方晶炭化珪素から作られており、好ましくはその結晶構造がポリタイプ4Hを有する。コレクタ層211、ウェル領域213およびp+領域202の各々はp型を有し、ドリフト領域212およびエミッタ領域214の各々はn型を有する。エミッタ領域214の不純物濃度はドリフト領域212の不純物濃度よりも高い。p+領域202の不純物濃度はウェル領域213の不純物濃度よりも高い。p型を付与するためのアクセプタ不純物は、たとえばアルミニウム(Al)または硼素(B)である。n型を付与するためのドナー不純物は、たとえば窒素(N)またはリン(P)である。

コレクタ層211が有するアクセプタ型不純物はコレクタ層211のエピタキシャル成長時に導入されたものであり、アクセプタ不純物濃度は、好ましくは1×1017cm3以上1×1021cm3以下であり、より好ましくは1×1019cm3以上1×1020cm3以下である。コレクタ層211の厚さは、好ましくは5μm以上である。

ドリフト領域212は、コレクタ層211上に接して設けられている。ドリフト領域212の厚さは、好ましくは75μm以上である。ウェル領域213は、ドリフト領域212の上に設けられている。エミッタ領域214は、ウェル領域213によってドリフト領域212から隔てられるようにウェル領域213の上に設けられている。p+領域202は、エミッタ領域214およびウェル領域213に接して設けられている。

ゲート絶縁膜215は、ドリフト領域212とエミッタ領域214とをつなぐようにウェル領域213の上に設けられている。ウェル領域213の、ゲート絶縁膜215に対向する面(つまり炭化珪素基板10の第1の主面10a)は、好ましくは{0001}面である。ゲート絶縁膜215は、たとえば二酸化珪素膜である。ゲート電極227は、ゲート絶縁膜215の上に設けられている。ゲート電極227は、導電体から作られており、たとえば、不純物が添加されたポリシリコン、またはアルミニウム(Al)から作られている。

エミッタコンタクト電極208は、エミッタ領域214およびp+領域202の各々にオーミックに接続された電極であり、好ましくはシリサイドから作られており、たとえばニッケルシリサイドから作られている。エミッタコンタクト電極208は、チタン、アルミニウムおよびシリコンを含む材料であってもよい。

エミッタ配線219は、エミッタコンタクト電極208および層間絶縁膜221の各々の上に設けられている。層間絶縁膜221は、ゲート電極227とエミッタ配線219との間を電気的に絶縁するように設けられている。層間絶縁膜221は、たとえば二酸化珪素膜である。

コレクタ電極230は第2の主面10bにおいてコレクタ層211と接して設けられている。コレクタ電極230は、コレクタ層211にオーミックに接続された電極であり、好ましくはシリサイドから作られており、たとえばニッケルシリサイドから作られている。コレクタ電極230はエミッタコンタクト電極208と同じ材料であってもよい。

なお、本実施の形態に係るIGBT101の製造方法は、実施の形態1で説明したMOSFET1の製造方法と同様である。

本実施の形態に係る炭化珪素半導体装置によれば、炭化珪素半導体装置は、IGBTである。これにより、素子領域を狭くしすぎることなく耐圧を向上させることができるIGBTを得ることができる。

(実施の形態3)

次に、本発明の実施の形態3に係る炭化珪素半導体装置であるSBD100の構造について説明する。

(実施の形態3)

次に、本発明の実施の形態3に係る炭化珪素半導体装置であるSBD100の構造について説明する。

図2および図9を参照して、SBD100の炭化珪素基板10は、素子領域IR(活性領域)と、平面視において素子領域IRを取り囲む終端領域OR(無効領域)とにより構成されている。終端領域ORは、第1の電界緩和領域2と、第2の電界緩和領域3を含む。素子領域IRには半導体素子部7としてのSBD部が設けられている。半導体素子部7はn型(第1の導電型)のドリフト領域12を含む。なお、本実施の形態における終端領域ORの構造は、実施の形態1における終端領域の構造と同様である。

図9に示すように本実施の形態のSBD100は、炭化珪素基板10と、ショットキー電極4と、パッド電極60と、オーミック電極30と、保護膜70とを主に有している。炭化珪素基板10は、たとえばポリタイプ4Hの六方晶炭化珪素からなり、かつn型を有している。炭化珪素基板10は、互いに対向する第1の主面10aおよび第2の主面10bを有している。

炭化珪素基板10は、n+基板11と、ドリフト領域12と、第1の電界緩和領域2と、第2の電界緩和領域3とを主に含んでいる。n+基板11は、たとえば窒素(N)などの不純物を含み、単結晶炭化珪素からなる基板である。n+基板11に含まれる不純物濃度は、たとえば5×1018cm-3程度である。

ドリフト領域12は、n+基板上に形成された炭化珪素エピタキシャル層である。ドリフト領域12はたとえば窒素などの不純物を含み、当該不純物の濃度はたとえば1×1016cm-3である。ドリフト領域12の不純物濃度は、n+基板11の不純物濃度よりも低い。ドリフト領域12の厚みTはたとえば15μm以上40μm以下である。

第1の電界緩和領域2はたとえばJTE領域であり、第2の電界緩和領域3はたとえばガードリング領域である。第1の電界緩和領域2および第2の電界緩和領域3は、たとえばアルミニウム(Al)やホウ素(B)などの不純物がイオン注入されたp型領域である。また炭化珪素基板10は、第1の主面10aの法線方向から見て、JTE領域3を取り囲むようにフィールドストップ領域(図示せず)を有していてもよい。フィールドストップ領域は、たとえばリン(P)などがイオン注入されたn+型領域である。フィールドストップ領域における不純物濃度は、ドリフト領域12における不純物濃度よりも高い。

ショットキー電極4は、炭化珪素基板10の第1の主面10a上に設けられており、ドリフト領域12、第1の電界緩和領域2および保護膜70と接している。ショットキー電極4は、たとえばチタン(Ti)、ニッケル(Ni)、窒化チタン(TiN)、金(Au)、モリブデン(Mo)およびタングステン(W)などの材料およびそれらの合金からなる。ショットキー電極4は、ドリフト領域12とショットキー接合している。

パッド電極60はショットキー電極4に接して形成されている。パッド電極60はたとえばアルミニウムからなる。パッド電極60、ショットキー電極8および炭化珪素基板10の第1の主面10aに接して保護膜70が形成されている。

保護膜70は、たとえば二酸化珪素からなり、第1の電界緩和領域2、第2の電界緩和領域3と接している。保護膜70は、ショットキー電極4およびパッド電極60に接し、ショットキー電極4から炭化珪素基板10の端部10cまで延在するように第1の主面10aに接して配置されている。第1の電界緩和領域2は、保護膜70およびショットキー電極4に接している。第1の電界緩和領域2の内周側の端部は、炭化珪素基板10の素子領域IRおよび終端領ORの境界線2aである。

n+基板11と接してオーミック電極30が配置されている。オーミック電極30はたとえばニッケルからなる。さらに、オーミック電極30に接してたとえばチタン、ニッケル、銀やそれらからなる合金からなる裏面保護電極40が配置されている。

次に、本発明の実施の形態に係る炭化珪素ダイオードであるSBD100の製造方法について説明する。

まず、基板準備工程が実施される。具体的には、たとえばポリタイプが4Hである六方晶炭化珪素からなるインゴット(図示しない)をスライスすることにより、導電型がn型のn+基板11が準備される。n+基板には、たとえば窒素(N)などの不純物が含まれている。n+基板に含まれる不純物濃度は、たとえば5×1018cm-3程度である。

次に、n+基板11上にドリフト領域12がエピタキシャル成長により形成される。ドリフト領域12は、導電型がn型である炭化珪素層である。ドリフト領域12に含まれる窒素などの不純物濃度はたとえば7×1015cm-3である。

次に、イオン注入工程が実施される。図10を参照して、たとえばAl(アルミニウム)イオンが、炭化珪素基板10のドリフト領域12内に注入されることにより、導電型がp型の第1の電界緩和領域2および第2の電界緩和領域3が形成される。以上の様に、n+基板11と、ドリフト領域12と、第1の電界緩和領域2と、第2の電界緩和領域3とを含み、互いに対向する第1の主面10aおよび第2の主面10bを有する炭化珪素基板10が準備される。

次に、活性化アニール工程が実施される。具体的には、たとえばアルゴンなどの不活性ガス雰囲気中、1800℃程度の温度で炭化珪素基板10が加熱されることにより、第1の電界緩和領域2および第2の電界緩和領域3を含む炭化珪素基板10がアニールされ、上記イオン注入工程にて導入された不純物が活性化される。これにより、不純物が導入された領域において所望のキャリアが生成する。

次に、電極形成工程が実施される。具体的には、図11を参照して、次に、たとえばチタン(Ti)、ニッケル(Ni)、モリブデン(Mo)、タングステン(W)、窒化チタン(TiN)などを含むショットキー電極4が、炭化珪素基板10の第1の電界緩和領域2および第2の電界緩和領域3に接して形成される。ショットキー電極4が形成された後、300℃以下程度500℃以上程度に加熱される。これにより、炭化珪素基板10と接合するショットキー電極4のショットキーバリアハイトを制御するとともに高温安定性の高い接合界面が形成される。

次に、オーミック電極形成工程が実施される。具体的には、炭化珪素基板10の第2の主面10bの研削が行われ、第2の主面10bと接触してたとえばニッケルからなるオーミック電極30が形成される。その後、オーミック電極30と接してたとえばチタン、ニッケル、銀やそれらからなる合金からなる裏面保護電極40が形成される。

次に、保護膜形成工程が実施される。具体的には、図9を参照して、たとえばプラズマCVD(Chemical Vapor Deposition)法により、パッド電極60、ショットキー電極4および炭化珪素基板10の第1の主面10aに接する保護膜70が形成される。保護膜70は、たとえば二酸化珪素(SiO2)、窒化珪素(SiN)、ポリイミドまたはそれらの積層膜からなる。これにより、図9に示す炭化珪素ダイオードとしてのSBD100が完成する。

本実施の形態に係る炭化珪素半導体装置によれば、炭化珪素半導体装置は、SBDである。これにより、素子領域を狭くしすぎることなく耐圧を向上させることができるSBDを得ることができる。

(実施の形態4)

次に、本発明の実施の形態4に係る炭化珪素半導体装置であるMPSの構造について説明する。

(実施の形態4)

次に、本発明の実施の形態4に係る炭化珪素半導体装置であるMPSの構造について説明する。

図2および図12を参照して、MPS200の炭化珪素基板10は、素子領域IR(活性領域)と、平面視において素子領域IRを取り囲む終端領域OR(無効領域)とにより構成されている。終端領域ORは、第1の電界緩和領域2と、第2の電界緩和領域3を含む。素子領域IRには半導体素子部7としてのMPS部が設けられている。半導体素子部7はn型(第1の導電型)のドリフト領域12を含む。なお、本実施の形態における終端領域ORの構造は、実施の形態1における終端領域の構造と同様である。

図12を参照して、本実施の形態に係るMPS200は、炭化珪素基板10と、電極4と、パッド電極60と、保護膜70と、オーミック電極30と、裏面保護電極40とを主に有している。

炭化珪素基板10は、n+基板11と、ドリフト領域12と、p型領域17と、第1の電界緩和領域2と、第2の電界緩和領域3とを含んでいる。n+基板11は、たとえば窒素(N)などの不純物を含む、単結晶炭化珪素からなる基板である。n+基板11に含まれる不純物濃度は、たとえば5×1018cm-3程度である。

ドリフト領域12は、n+基板11上に形成された炭化珪素エピタキシャル層である。ドリフト領域12はたとえば窒素などの不純物を含み、ドリフト領域12における不純物濃度はたとえば1×1016cm-3である。p型領域17におけるアルミニウムなどの不純物濃度はたとえば1×1019cm-3程度である。ドリフト領域12の厚みTは、たとえば15μm程度以上40μm程度以下である。

第1の電界緩和領域2および第2の電界緩和領域3の各々は、たとえばアルミニウム(Al)やホウ素(B)などの不純物がイオン注入されたp型領域である。第1の電界緩和領域2を貫通するように、第1の電界緩和領域2よりも不純物濃度の高いp型領域17が形成されていている。また炭化珪素基板10は、第1の電界緩和領域2および第2の電界緩和領域3を取り囲むようにフィールドストップ領域(図示せず)を有していても構わない。フィールドストップ領域は、たとえばリン(P)などがイオン注入されたn+型領域であり、ドリフト領域12よりも高い不純物濃度を有する。

電極4は、炭化珪素基板10の第1の主面10a上に設けられており、たとえばチタン(Ti)からなる。電極4として、チタン以外にもたとえばニッケル(Ni)、窒化チタン(TiN)、金(Au)、モリブデン(Mo)およびタングステン(W)などを用いても構わない。電極4はたとえば単一の材料から構成されていてもよい。単一の材料とは、同じ元素からなる単体から成っている場合および同じ化合物から成っている場合を含む。また、当該材料をたとえばスパッタリングやメッキで形成した後に、当該材料の一部を加熱することにより当該材料の一部における結合状態が変化した場合であっても、結合状態が変化した部分と結合状態が変化していない部分とは単一の材料である。

電極4は、ドリフト領域12とショットキー接合する第1の領域4aと、p型領域17とオーミック接合する第2の領域4bとを含む。断面視(図11の視野)において第2の領域4bは間隔をあけて複数配置されていてもよい。また断面視において第1の領域4aと第2の領域4bとが交互に配置されていてもよい。p型領域17は炭化珪素基板10の第1の主面10aからオーミック電極30に向かって伸長して形成されている。第1の領域4aおよび第2の領域4bは単一の材料からなってもよいし、異なった材料であってもよい。たとえば第1の領域4aと第2の領域4bとは同じ金属または同じ合金から形成されている。

図13を参照して、炭化珪素基板10の法線方向から観察すると(言いかれば平面視において)、電極4はほぼ正方形の形状を有している。第1の電界緩和領域2は、電極4の外周4cに沿って形成されている第1のp型領域2bと、電極4の外周4cの内側に配置された第2のp型領域2cとを有している。またp型領域17は電極4の外周4cに囲まれて配置されている。p型領域17は、たとえば柵状を有している。第1のp型領域2bと第2のp型領域2cとに挟まれてp型領域17が形成されていてもよい。また、p型領域17は、第1の電界緩和領域2と接しない領域を有していてもよい。

再び図12を参照して、電極4の第1の領域4aおよび第2の領域4bに接してパッド電極60が形成されている。パッド電極60はたとえばアルミニウムからなる。パッド電極60、第1の領域4aおよび炭化珪素基板10の第1の主面10aに接してたとえば二酸化珪素からなる保護膜70が形成されている。また、n+基板11と接してオーミック電極30が配置されている。オーミック電極30はたとえばニッケルからなる。さらに、オーミック電極30に接してたとえばチタン、ニッケル、銀やそれらからなる合金からなる裏面保護電極40が配置されている。第1の電界緩和領域2は、保護膜70および電極4の第1の領域4aに接している。第1の電界緩和領域2の内周側の端部は、炭化珪素基板10の素子領域IRおよび終端領ORの境界線2aである。

なお、MPS200は、n型のドリフト領域12と接続されたp型領域17を有する、P/Nダイオードである。

次に、本実施の形態に係る炭化珪素半導体装置であるMPS200の製造方法について説明する。

まず、基板準備工程が実施される。基板準備工程では、たとえばポリタイプが4Hである単結晶炭化珪素からなるインゴット(図示しない)をスライスすることにより、導電型がn型(第1導電型)のn+基板11が準備される。n+基板には、たとえば窒素などの不純物が含まれている。n+基板に含まれる不純物濃度は、たとえば5×1018cm-3程度である。

次に、n+基板11上にに導電型がn型(第1導電型)であるドリフト領域12がエピタキシャル成長により形成される。ドリフト領域12の不純物濃度はたとえば1×1016cm-3である。

次に、イオン注入工程が実施される。図14を参照して、イオン注入工程では、たとえばAl(アルミニウム)イオンが、炭化珪素基板10内に注入されることにより、導電型がp型(第2導電型)の第1の電界緩和領域2および第2の電界緩和領域3が形成される。同様に、たとえばAl(アルミニウム)イオンが、ドリフト領域12および第1の電界緩和領域2に注入されることにより、導電型がp型(第2導電型)のp型領域17が形成される。p型領域17は、断面視(第1の主面10aに平行な方向の視野)において、第1の電界緩和領域2と接する部分と、第1の電界緩和領域2と接しない部分とを有する。p型領域17の不純物濃度は、たとえば1×1019cm-3程度である。これにより、p型領域17と、第1の電界緩和領域2と、第2の電界緩和領域3とを有する炭化珪素基板10が準備される。

次に、活性化アニール工程が実施される。活性化アニール工程では、たとえばアルゴンなどの不活性ガス雰囲気中、1800℃程度の温度で炭化珪素基板10が加熱されることにより、p型領域17と、第1の電界緩和領域2と、第2の電界緩和領域3とがアニールされ、イオン注入工程にて導入された不純物が活性化される。これにより、不純物が導入された領域において所望のキャリアが生成する。

次に、電極形成工程が実施される。図15を参照して、電極形成工程は、好ましくは、金属膜形成工程、ショットキー接合工程およびオーミック接合工程を含んでいる。たとえば、金属膜形成工程において、単一の材料からなる電極4が炭化珪素基板10のドリフト領域12、p型領域17および第1の電界緩和領域2に接して形成される。電極4は、たとえばチタン(Ti)、ニッケル(Ni)、モリブデン(Mo)、タングステン(W)、窒化チタン(TiN)などの金属膜である。具体的には、電極4は、炭化珪素基板10の第1の主面10aにおいて、ドリフト領域12と、p型領域17と、第1の電界緩和領域2とに接して形成される。

次に、ショットキー接合工程が実施される。ショットキー接合工程では、炭化珪素基板10の第1の主面10aに形成された電極4の全体が加熱される。電極4全体の加熱はたとえばレーザーアニールを用いて行われる。電極4が形成された炭化珪素基板10を加熱炉配置して、不活性ガス雰囲気中において電極4全体が加熱されても構わない。電極4は、たとえば500℃程度にまで加熱される。これにより、ショットキーバリアハイトを制御するとともに高温安定性の高くドリフト領域12と第1の領域4aとがショットキー接合される。なお、電極4の第1の領域4aを局所的に加熱することにより、ドリフト領域12と第1の領域4aとがショットキー接合されても構わない。

次に、オーミック接合工程が実施される。オーミック接合工程では、図16を参照して、p型領域17と接触する電極4の第2の領域4bを局所的に加熱することにより、p型領域17と第2の領域4bとがオーミック接合される。第2の領域4bを局所的に加熱することによりp型領域17と第2の領域4bとをオーミック接合させる工程は、好ましくは第2の領域4bをレーザーアニールすることにより行われる。第2の領域4bの局所加熱は電子ビーム(Electron Beam)によって行われても構わない。また第2の領域4bは、たとえば1000℃程度まで加熱される。オーミック接合工程における電極4の加熱温度は、ショットキー工程における電極4の加熱温度よりも高い。

次に、パッド電極および保護膜形成工程が実施される。具体的には、電極4上に接して、たとえばアルミニウムからなるパッド電極60が形成される。その後、パッド電極60、電極4の第2の領域4bおよび炭化珪素基板10の第1の主面10aと接して保護膜70が形成される。

次に、オーミック電極形成工程が実施される。具体的には、炭化珪素基板10の第1の主面10aとは反対の第2の主面10bの研削が行われ、第2の主面10bと接触するオーミック電極30が形成される。オーミック電極30はたとえばニッケルを含む。その後、オーミック電極30と接してたとえばチタン、ニッケル、銀やそれらからなる合金からなる裏面保護電極40が形成される。以上により、図11に示すMPS200が完成する。

本実施の形態に係る炭化珪素半導体装置によれば、炭化珪素半導体装置は、P/Nダイオード(MPS)である。これにより、素子領域を狭くしすぎることなく耐圧を向上させることができるP/Nダイオード(MPS)を得ることができる。

本実施例では、第1の電界緩和領域2(JTE領域2)の幅W1をドリフト領域12の厚みTで除した比を変化させた場合における電界強度を調査した。

まず、実施の形態の図1に示したような構造を有し、JTE領域2の幅W1をドリフト領域12の厚みTで除した比を変化させた6種類のMOSFETのモデルを準備した。ドリフト領域12の不純物濃度を4.5×1015cm-3とした。ドリフト領域12の厚みTを23μmとした。JTE領域2の幅W1を、7μm、15μm、23μm、31μm、39μmおよび47μmと変化させることで、JTE領域2の幅W1をドリフト領域12の厚みTで除した比(百分率表記)を約30%、約65%、100%、約135%、約170%および約204%とした。ウェル領域13の不純物濃度を5×1016cm-3とした。ウェル領域13の厚みを0.9μmとした。JTE領域2およびガードリング部の各々のドーズ量を1.35×1013cm-2とした。JTE領域2およびガードリング部の各々の厚みを0.7μmとした。

JTE領域2の幅W1が7μm、15μm、23μm、31μm、39μmおよび47μmの場合におけるガードリング部の本数を、それぞれ10本、9本、8本、7本、6本、5本とした。ガードリング部の各々の幅を5μmとした。JTE領域2と最内周のガードリング部3aとの間隔d1および隣接するガードリング部同士の間隔d2を5μmとした。

上記6種類のMOSFETのモデルの電界強度分布を計算した。ウェル領域13の角部(位置A)の電界強度と、ウェル領域13とJTE領域2の角部との接点(位置B)の電界強度と、MOSFETの終端領域ORにおけるJTE領域2の外周側の角部(位置C)の電界強度と、最外周のガードリング部の外周側の角部(位置D)における電界強度とを計算し、各位置における電界強度を見積もった。電界強度分布計算におけるドレイン電圧を2.2kVとした。

図17を参照して、電界強度のJTE2の幅W1をドリフト領域12の厚みTで除した比(百分率表示)依存性について説明する。位置Bにおける電界強度(図17のEbody/jte)は、JTE2の幅W1をドリフト領域12の厚みTで除した比が約30%において高い値を示すが、当該比が30%よりも大きくなると、位置Bにおける電界強度が低くなる。また当該比が204%の場合、位置Dにおける電界強度(図17のEgr端)は高い値を示すが、当該比が204%より小さくなると、位置Dにおける電界強度は小さくなる。つまり、当該比が30%より大きく204%より小さい場合において、すべての位置における電界強度が小さくなることが確認された。

また電界強度のJTE2の幅W1をドリフト領域12の厚みTで除した比が65%以上170%以下の場合において、位置Aにおける電界強度(図17のEpn)が、位置Aにおける電界強度以外の電界強度(図17のEbody/jte、Ejte端およびEgr端)よりも高くなることが確認された。

次に、実施の形態の図1に示したような構造を有し、JTE領域2の幅W1をドリフト領域12の厚みTで除した比を変化させた8種類のMOSFETのモデルを準備した。ドリフト領域12の不純物濃度を3.0×1015cm-3とした。ドリフト領域の厚みTを30μmとした。JTE領域2の幅W1を、7μm、15μm、23μm、31μm、39μm、47μm、55μmおよび81μmと変化させることで、JTE領域2の幅W1をドリフト領域12の厚みT除した比(百分率表記)を約47%、約50%、77%、約103%、約130%、約157%、約183%および約237%とした。ウェル領域13の不純物濃度を5×1016cm-3とした。ウェル領域13の厚みを0.9μmとした。JTE領域2およびガードリング部の各々のドーズ量を1.35×1013cm-2とした。JTE領域2およびガードリング部の各々の厚みを0.7μmとした。

JTE領域2の幅W1が7μm、15μm、23μm、31μm、39μm、47μm、55μmおよび81μmの場合におけるガードリング部の本数を、それぞれ16本、15本、14本、13本、12本、11本、10本、9本、8本とした。ガードリング部の各々の幅を5μmとした。JTE領域2と最内周のガードリング部3aとの間隔d1および隣接するガードリング部同士の間隔d2を5μmとした。

上記8種類のMOSFETのモデルの電界強度分布を計算した。ウェル領域13の角部(位置A)の電界強度と、ウェル領域13とJTE領域2の角部との接点(位置B)の電界強度と、MOSFETの終端領域ORにおけるJTE領域2の外周側の角部(位置C)の電界強度と、最外周のガードリング部の外周側の角部(位置D)における電界強度とを計算し、各位置における電界強度を見積もった。電界強度分布計算におけるドレイン電圧を3.3kVとした。

図18を参照して、電界強度のJTE2の幅W1をドリフト領域12の厚みTで除した比(百分率表示)依存性について説明する。位置Bにおける電界強度(図17のEbody/jte)は、JTE2の幅W1をドリフト領域12の厚みTで除した比が約47%において高い値を示すが、当該比が50%以上になると、位置Bにおける電界強度が低くなる。また当該比が237%の場合、位置Dにおける電界強度(図17のEgr端)は高い値を示すが、当該比が183%以下になると、位置Dにおける電界強度は小さくなる。つまり、当該比が50%以上183%以下の場合において、すべての位置における電界強度が小さくなることが確認された。

また電界強度のJTE2の幅W1をドリフト領域12の厚みTで除した比が103%以上183%以下の場合において、位置Aにおける電界強度(図17のEpn)が、位置Aにおける電界強度以外の電界強度(図17のEbody/jte、Ejte端およびEgr端)以上になることが確認された。

以上の結果より、電界強度のJTE2の幅W1をドリフト領域12の厚みTで除した比が、50%以上183%以下であることが好ましく、103%以上183%以下がより好ましく、65%以上170%以下であることが好ましいことが確認された。

本実施例では、ガードリング部の本数を変化させた場合における電界強度の変化を調査した。

まず、実施の形態の図1に示したような構造を有し、JTE領域2の幅W1をドリフト領域12の厚みTで除した比を約65%で固定し、かつガードリング部の本数を変化させた6種類のMOSFETのモデルを準備した。ガードリング部の本数を2本、3本、6本、9本、12本、15本とした。ドリフト領域12の不純物濃度を4.5×1015cm-3とした。ドリフト領域12の厚みTを23μmとした。ウェル領域13の不純物濃度を5×1016cm-3とした。ウェル領域13の厚みを0.9μmとした。JTE領域2およびガードリング部の各々のドーズ量を1.35×1013cm-2とした。JTE領域2およびガードリング部の各々の厚みを0.7μmとした。ガードリング部の各々の幅を5μmとした。JTE領域2と最内周のガードリング部3aとの間隔d1および隣接するガードリング部同士の間隔d2を5μmとした。

上記6種類のMOSFETのモデルの電界強度分布を計算した。ウェル領域13の角部(位置A)の電界強度と、ウェル領域13とJTE領域2の角部との接点(位置B)の電界強度と、MOSFETの終端領域ORにおけるJTE領域2の外周側の角部(位置C)の電界強度と、最外周のガードリング部の外周側の角部(位置D)における電界強度とを計算し、各位置における電界強度を見積もった。電界強度分布計算におけるドレイン電圧を2.2kVとした。

図19を参照して、電界強度のガードリング本数(GR本数)依存性について説明する。なお、ガードリング部が2本のMOSFETに関しては、位置Bにおける電界強度のみの結果を示す。ガードリング部の本数が2本の場合、位置Bにおける電界強度(図19のEbody/jte)は3MV/cm超と高い値を示すが、ガードリング部の本数が3本以上になると、位置Bにおける電界強度が急激に低減する。またガードリング部の本数が6本以上になると、位置Bにおける電界強度がさらに低減する。さらにガードリング部の本数が6本以上15本以下であれば、位置Aにおける電界強度(図19のEpn)が、位置Aにおける電界強度以外の電界強度(図19のEbody/jte、Ejte端およびEgr端)よりも高くなることが確認された。

次に、実施の形態の図1に示したような構造を有し、JTE領域2の幅W1をドリフト領域12の厚みTで除した比を約50%で固定し、かつガードリング部の本数を変化させた6種類のMOSFETのモデルを準備した。ガードリング部の本数を2本、3本、6本、9本、12本、15本とした。ドリフト領域12の不純物濃度を3.0×1015cm-3とした。ドリフト領域の厚みTを30μmとした。ウェル領域13の不純物濃度を5×1016cm-3とした。ウェル領域13の厚みを0.9μmとした。JTE領域2およびガードリング部の各々のドーズ量を1.35×1013cm-2とした。JTE領域2およびガードリング部の各々の厚みを0.7μmとした。ガードリング部の各々の幅を5μmとした。JTE領域2と最内周のガードリング部3aとの間隔d1および隣接するガードリング部同士の間隔d2を5μmとした。

上記6種類のMOSFETのモデルの電界強度分布を計算した。ウェル領域13の角部(位置A)の電界強度と、ウェル領域13とJTE領域2の角部との接点(位置B)の電界強度と、MOSFETの終端領域ORにおけるJTE領域2の外周側の角部(位置C)の電界強度と、最外周のガードリング部の外周側の角部(位置D)における電界強度とを計算し、各位置における電界強度を見積もった。電界強度分布計算におけるドレイン電圧を3.3kVとした。

図20を参照して、電界強度のガードリング本数(GR本数)依存性について説明する。なお、ガードリング部が2本のMOSFETに関しては、位置Bにおける電界強度のみの結果を示す。ガードリング部の本数が2本の場合、位置Bにおける電界強度(図20のEbody/jte)は3MV/cm超と高い値を示すが、ガードリング部の本数が3本以上になると、位置Bにおける電界強度が急激に低減する。またガードリング部の本数が6本以上になると、位置Bにおける電界強度がさらに低減する。さらにガードリング部の本数が12本以上になると、位置Bにおける電界強度がさらに低減する。ガードリング部の本数が12本以上15本以下であれば、位置Aにおける電界強度(図20のEpn)が、位置Aにおける電界強度以外の電界強度(図20のEbody/jte、Ejte端およびEgr端)よりも高くなることが確認された。

以上の結果より、ガードリング部の本数は、3本以上15本以下であることが好ましく、6本以上15本以下であることがより好ましく、12本以上15本以下であればさらに好ましいことが確認された。

本実施例では、第2の電界緩和領域3(ガードリング部)を有しないMOSFETの電界強度分布を調査した。まず、ガードリング部を有さず、JTE領域2の幅W1を変化させた6種類のMOSFETのモデルを準備した。ドリフト領域12の不純物濃度を4.5×1015cm-3とした。ドリフト領域の厚みTを23μmとした。ウェル領域13の不純物濃度を5×1016cm-3とした。ウェル領域13の厚みを0.9μmとした。JTE領域2のドーズ量を1.35×1013cm-2とした。JTE領域2の厚みを0.7μmとした。JTE領域2の幅W1を7μm、15μm、23μm、31μm、39μmおよび47μmとした。

上記6種類のMOSFETのモデルの電界強度分布を計算した。ウェル領域13の角部(位置A)の電界強度と、ウェル領域13とJTE領域2の角部との接点(位置B)の電界強度と、MOSFETの終端領域ORにおけるJTE領域2の外周側の角部(位置C)の電界強度とを計算し、各位置における電界強度を見積もった。電界強度分布計算におけるドレイン電圧を2.2kVとした。

図21を参照して、電界強度のJTE領域2の幅W1依存性について説明する。JTE領域2の幅W1が15μm以上55μm以下の領域において、位置Aにおける電界強度(図21のEpn)が、位置Cにおけるの電界強度(図21のEjte端)よりも高くなることが確認された。また、JTE領域2の幅W1が15μm以上55μm以下の領域において、位置Cにおける電界強度(図21のEjte端)は2.7MV/cm超と高い値を示す。一方、図17を参照すると、ガードリング部を有するMOSFETの位置Cにおける電界強度(図21のEjte端)は2.4MV/cm未満である。つまり、ガードリング部を有するMOSFET

はガードリング部を有しないMOSFETよりも位置Cにおける電界強度を低減可能であることが確認された。

はガードリング部を有しないMOSFETよりも位置Cにおける電界強度を低減可能であることが確認された。

本実施例では、複数のガードリング部の各々の幅を変化させた場合における電界強度分布を調査した。まず、比較例として、JTE領域2と、複数のガードリング部を有し、複数のガードリング部の各々の幅が一定である構造を有するMOSFETを準備した。具体的には、比較例として、図3の構造を有するMOSFETを準備した。図22に係るMOSFETのJTE領域2の幅W1を15μmとした。第2の電界緩和領域3は9本のガードリング部を含んでいた。各ガードリング部の幅を5μmとした。JTE領域2と最内周のガードリング部の間隔d1を3μmとした。隣接するガードリング部の間隔d2を3μmとした。

一方、本発明例として、JTE領域2と、複数のガードリング部を有し、複数のガードリング部の各々の幅が、炭化珪素基板10の中心から外周に向かって小さくなる構造を有するMOSFETを準備した。具体的には、本発明例として、図4の構造を有するMOSFETを準備した。図23に係るMOSFETのJTE領域2の幅W1を15μmとした。第2の電界緩和領域3は7本のガードリング部を含んでいた。ガードリング部の幅を、内周側から外周側に向かって、10μm、8μm、8μm、6μm、5μm、5μm、5μmとした。図24に係るMOSFETのJTE領域2の幅W1を20μmとした。第2の電界緩和領域3は6本のガードリング部を含んでいた。ガードリング部の幅を、内周側から外周側に向かって、15μm、10μm、5μm、5μm、5μm、5μmとした。図25に係るMOSFETのJTE領域2の幅W1を20μmとした。第2の電界緩和領域3は6本のガードリング部を含んでいた。ガードリング部の幅を、内周側から外周側に向かって、15μm、12μm、8μm、5μm、5μm、5μmとした。なお、JTE領域2と第2の電界緩和領域3との間隔d1を3μmとした。隣接するガードリング部の間隔d2を3μmとした。

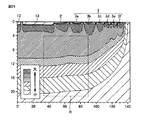

次に、比較例および本発明例の電界強度分布のシミュレーションを実施した。電界強度分布結果を図22〜図25に示す。なお、図22〜図25において同じ種類のハッチングは、同じ程度の電界強度を有することを示している。

図22は比較例の電界強度分布であり、図23〜図25は本発明例の電界強度分布である。横軸の数字は、炭化珪素基板10の第1の主面10aに平行な方向の位置を示し、縦軸の数字は、第1の主面10aの法線方向の位置を示す。縦軸および横軸の数字の単位はμmである。

図22を参照して、比較例のJTE領域2と第2の電界緩和領域3との境界付近(図中の領域R)において等電界線が急激に変化している。たとえば、第1の主面10aから8μm離れた位置において、炭化珪素基板10の中心から外周に向かう方向(図22における右方向)に向かって、電界強度が急減に減少している。一方、図23〜図25を参照すると、本発明例の第1の電界緩和領域2と第2の電界緩和領域3との境界付近(図中の領域R)において等電界線が緩やかに変化している。たとえば、第1の主面10aから8μm離れた位置において、炭化珪素基板10の中心から外周に向かう方向(図23〜図25における右方向)に向かって、電界強度が緩やかに減少している。

以上の結果により、複数のガードリング部の各々の幅が、炭化珪素基板10の中心から外周に向かって小さくなる構造を有するMOSFETは、複数のガードリング部の各々の幅が同じである構造を有するMOSFETと比べて、炭化珪素基板10の中心から外周に向かう方向における等電界線の変化が緩やかになることが確認された。なお、等電界線の変化が緩やかなMOSFETは、等電界線の変化が急激なMOSFETよりも、繰り返し電圧を印加する場合における耐圧寿命(信頼性)を向上することができる。

今回開示された実施の形態および実施例はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなく特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

1 MOSFET、2 第1の電界緩和領域(JTE領域)、2b 第1のp型領域、2c 第2のp型領域、3 第2の電界緩和領域、3a〜3i,3a〜3g,3a〜3b,3a,3i ガードリング部、4 ショットキー電極(電極)、4a 第1の領域、4b 第2の領域、4c 外周、7 半導体素子、10 炭化珪素基板、10a 第1の主面、10b 第2の主面、10c 端部、11 n+基板、12,212 ドリフト領域、13,213 ウェル領域、14 ソース領域、15 絶縁膜、15a ゲート絶縁膜部、15b 絶縁膜部、16 ソース電極、17 p型領域、18,202 p+領域、20 ドレイン電極、27,227 ゲート電極、30 オーミック電極、40,50 裏面保護電極、60,65 パッド電極、70 保護膜、71,221 層間絶縁膜、208 エミッタコンタクト電極、211 コレクタ層、212 ドリフト層、214 エミッタ領域、215 ゲート絶縁膜、219 エミッタ配線、230 コレクタ電極、240 コレクタ配線、A,B,C,D 位置、CH チャネル領域、IR 素子領域、OR 終端領域、T 厚み、W1〜W10 幅、d1,d2 間隔。

Claims (7)

- 半導体素子部が設けられた素子領域と、平面視において前記素子領域を取り囲む終端領域とにより構成された炭化珪素基板を備え、

前記半導体素子部は第1導電型のドリフト領域を含み、

前記終端領域は、

前記素子領域と接し、かつ前記第1導電型とは異なる第2導電型の第1の電界緩和領域と、

前記平面視において前記第1の電界緩和領域よりも外側に配置され、前記第2導電型を有し、かつ前記第1の電界緩和領域と離間している第2の電界緩和領域とを含み、

前記第1の電界緩和領域の幅を前記ドリフト領域の厚みで除した比は、0.5以上1.83以下である、炭化珪素半導体装置。 - 前記第2の電界緩和領域は、複数のガードリング部を含む、請求項1に記載の炭化珪素半導体装置。

- 前記複数のガードリング部の各々の幅は、前記第1の電界緩和領域の幅よりも小さい、請求項2に記載の炭化珪素半導体装置。

- 前記複数のガードリング部から任意の2つのガードリング部を選択した場合において、平面視において外周側に配置されているガードリング部の幅は、内周側に配置されているガードリング部の幅以下であり、かつ最外周側に配置されているガードリング部の幅は最内周側に配置されているガードリング部の幅よりも小さい、請求項2または3に記載の炭化珪素半導体装置。

- 前記複数のガードリング部の本数は、6本以上15本以下である、請求項2〜4のいずれか1項に記載の炭化珪素半導体装置。

- 前記複数のガードリング部の本数は、12本以上15本以下である、請求項5に記載の炭化珪素半導体装置。

- 前記炭化珪素半導体装置は、MOSFET、IGBT、ショットキーバリアダイオードおよびP/Nダイオードのいずれかである、請求項1〜6のいずれか1項に記載の炭化珪素半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013005132A JP2014138048A (ja) | 2013-01-16 | 2013-01-16 | 炭化珪素半導体装置 |

| DE112013006438.3T DE112013006438T5 (de) | 2013-01-16 | 2013-11-22 | Siliziumkarbid-Halbleitervorrichtung |

| CN201380065816.6A CN104871316A (zh) | 2013-01-16 | 2013-11-22 | 碳化硅半导体器件 |

| PCT/JP2013/081497 WO2014112204A1 (ja) | 2013-01-16 | 2013-11-22 | 炭化珪素半導体装置 |

| US14/104,975 US8981385B2 (en) | 2013-01-16 | 2013-12-12 | Silicon carbide semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013005132A JP2014138048A (ja) | 2013-01-16 | 2013-01-16 | 炭化珪素半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2014138048A true JP2014138048A (ja) | 2014-07-28 |

Family

ID=51164512

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013005132A Pending JP2014138048A (ja) | 2013-01-16 | 2013-01-16 | 炭化珪素半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8981385B2 (ja) |

| JP (1) | JP2014138048A (ja) |

| CN (1) | CN104871316A (ja) |

| DE (1) | DE112013006438T5 (ja) |

| WO (1) | WO2014112204A1 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016058660A (ja) * | 2014-09-11 | 2016-04-21 | 富士電機株式会社 | 半導体装置 |

| JP2017059711A (ja) * | 2015-09-17 | 2017-03-23 | 株式会社デンソー | 半導体装置 |

| JP2018018903A (ja) * | 2016-07-26 | 2018-02-01 | トヨタ自動車株式会社 | 半導体装置 |

| JP2018157040A (ja) * | 2017-03-16 | 2018-10-04 | ローム株式会社 | 半導体装置 |

| JP2018186160A (ja) * | 2017-04-25 | 2018-11-22 | パナソニックIpマネジメント株式会社 | 半導体素子 |

| CN109524397A (zh) * | 2017-09-19 | 2019-03-26 | 株式会社东芝 | 半导体装置 |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014241367A (ja) * | 2013-06-12 | 2014-12-25 | 三菱電機株式会社 | 半導体素子、半導体素子の製造方法 |

| US10347489B2 (en) * | 2013-07-02 | 2019-07-09 | General Electric Company | Semiconductor devices and methods of manufacture |

| JP2015032627A (ja) * | 2013-07-31 | 2015-02-16 | 株式会社東芝 | 半導体装置 |

| US20150236151A1 (en) * | 2014-02-18 | 2015-08-20 | General Electric Company | Silicon carbide semiconductor devices, and methods for manufacturing thereof |

| EP2942805B1 (en) * | 2014-05-08 | 2017-11-01 | Nexperia B.V. | Semiconductor device and manufacturing method |

| JP6274968B2 (ja) * | 2014-05-16 | 2018-02-07 | ローム株式会社 | 半導体装置 |

| US9224816B2 (en) * | 2014-05-21 | 2015-12-29 | Sumitomo Electric Industries, Ltd. | Silicon carbide semiconductor device |

| DE112015003559T5 (de) | 2014-08-01 | 2017-04-20 | Sumitomo Electric Industries, Ltd. | Epitaxialer Wafer und Herstellungsverfahren dafür |

| JP5910802B1 (ja) * | 2014-08-29 | 2016-04-27 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| WO2016091488A1 (en) * | 2014-12-08 | 2016-06-16 | Abb Technology Ag | Method for manufacturing a wide bandgap junction barrier schottky diode |

| JP2016181591A (ja) * | 2015-03-24 | 2016-10-13 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| WO2017090285A1 (ja) | 2015-11-24 | 2017-06-01 | 住友電気工業株式会社 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

| WO2018084020A1 (ja) * | 2016-11-01 | 2018-05-11 | 三菱電機株式会社 | 炭化珪素半導体装置および電力変換装置 |

| JP6887244B2 (ja) | 2016-12-09 | 2021-06-16 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6673174B2 (ja) * | 2016-12-12 | 2020-03-25 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| US10014405B1 (en) * | 2016-12-30 | 2018-07-03 | Texas Instruments Incorporated | Semiconductor device with extended electrically-safe operating area |

| JP6624101B2 (ja) | 2017-02-03 | 2019-12-25 | 株式会社デンソー | 半導体装置 |

| CN111480239B (zh) * | 2017-12-19 | 2023-09-15 | 三菱电机株式会社 | 碳化硅半导体装置以及电力变换装置 |

| DE102018102279A1 (de) * | 2018-02-01 | 2019-08-01 | Infineon Technologies Ag | Halbleiterbauelement mit randabschlussbereich |

| DE102018115728B4 (de) * | 2018-06-29 | 2021-09-23 | Infineon Technologies Ag | Halbleitervorrichtung, die einen Siliziumcarbidkörper und Transistorzellen enthält |

| US10998418B2 (en) * | 2019-05-16 | 2021-05-04 | Cree, Inc. | Power semiconductor devices having reflowed inter-metal dielectric layers |

| EP3971987A1 (en) * | 2020-09-21 | 2022-03-23 | Infineon Technologies AG | Silicon carbide device with stripe-shaped gate electrode and source metallization |

| CN113161408B (zh) * | 2020-12-28 | 2022-06-07 | 全球能源互联网研究院有限公司 | 高压SiC肖特基二极管的结终端结构及其制备方法 |

| US11916152B2 (en) * | 2020-12-30 | 2024-02-27 | Texas Instruments Incorporated | Segmented Schottky diode |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200090A (ja) * | 1997-01-06 | 1998-07-31 | Nissan Motor Co Ltd | 半導体装置 |

| JP2008004643A (ja) * | 2006-06-20 | 2008-01-10 | Toshiba Corp | 半導体装置 |

| JP2011171374A (ja) * | 2010-02-16 | 2011-09-01 | Sumitomo Electric Ind Ltd | 炭化珪素絶縁ゲート型半導体素子およびその製造方法 |

| JP2011204710A (ja) * | 2010-03-24 | 2011-10-13 | Fuji Electric Co Ltd | 半導体装置 |

| JP2012195519A (ja) * | 2011-03-18 | 2012-10-11 | Kyoto Univ | 半導体素子及び半導体素子の製造方法 |

| WO2012137412A1 (ja) * | 2011-04-05 | 2012-10-11 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP2012195324A (ja) * | 2011-03-14 | 2012-10-11 | Shindengen Electric Mfg Co Ltd | 高耐圧半導体装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3708057B2 (ja) | 2001-07-17 | 2005-10-19 | 株式会社東芝 | 高耐圧半導体装置 |

| JP2006073740A (ja) * | 2004-09-01 | 2006-03-16 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4356764B2 (ja) | 2007-04-18 | 2009-11-04 | 株式会社デンソー | 炭化珪素半導体装置 |

| WO2009116444A1 (ja) * | 2008-03-17 | 2009-09-24 | 三菱電機株式会社 | 半導体装置 |

-

2013

- 2013-01-16 JP JP2013005132A patent/JP2014138048A/ja active Pending

- 2013-11-22 DE DE112013006438.3T patent/DE112013006438T5/de not_active Withdrawn

- 2013-11-22 CN CN201380065816.6A patent/CN104871316A/zh active Pending

- 2013-11-22 WO PCT/JP2013/081497 patent/WO2014112204A1/ja active Application Filing

- 2013-12-12 US US14/104,975 patent/US8981385B2/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200090A (ja) * | 1997-01-06 | 1998-07-31 | Nissan Motor Co Ltd | 半導体装置 |

| JP2008004643A (ja) * | 2006-06-20 | 2008-01-10 | Toshiba Corp | 半導体装置 |

| JP2011171374A (ja) * | 2010-02-16 | 2011-09-01 | Sumitomo Electric Ind Ltd | 炭化珪素絶縁ゲート型半導体素子およびその製造方法 |

| JP2011204710A (ja) * | 2010-03-24 | 2011-10-13 | Fuji Electric Co Ltd | 半導体装置 |

| JP2012195324A (ja) * | 2011-03-14 | 2012-10-11 | Shindengen Electric Mfg Co Ltd | 高耐圧半導体装置 |

| JP2012195519A (ja) * | 2011-03-18 | 2012-10-11 | Kyoto Univ | 半導体素子及び半導体素子の製造方法 |

| WO2012137412A1 (ja) * | 2011-04-05 | 2012-10-11 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016058660A (ja) * | 2014-09-11 | 2016-04-21 | 富士電機株式会社 | 半導体装置 |

| JP2017059711A (ja) * | 2015-09-17 | 2017-03-23 | 株式会社デンソー | 半導体装置 |

| JP2018018903A (ja) * | 2016-07-26 | 2018-02-01 | トヨタ自動車株式会社 | 半導体装置 |

| JP2018157040A (ja) * | 2017-03-16 | 2018-10-04 | ローム株式会社 | 半導体装置 |

| JP2018186160A (ja) * | 2017-04-25 | 2018-11-22 | パナソニックIpマネジメント株式会社 | 半導体素子 |

| CN109524397A (zh) * | 2017-09-19 | 2019-03-26 | 株式会社东芝 | 半导体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE112013006438T5 (de) | 2015-10-08 |

| CN104871316A (zh) | 2015-08-26 |

| US8981385B2 (en) | 2015-03-17 |

| US20140197422A1 (en) | 2014-07-17 |

| WO2014112204A1 (ja) | 2014-07-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2014112204A1 (ja) | 炭化珪素半導体装置 | |

| JP5939127B2 (ja) | 炭化珪素半導体装置 | |

| US9716157B2 (en) | Silicon carbide semiconductor device | |

| JP6206339B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| WO2015015926A1 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2017092355A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2015076592A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| WO2015166754A1 (ja) | 半導体装置 | |

| WO2017051616A1 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| US9806167B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| JP2014127660A (ja) | 炭化珪素ダイオード、炭化珪素トランジスタおよび炭化珪素半導体装置の製造方法 | |

| US9722027B2 (en) | Silicon carbide semiconductor device and method for manufacturing the same | |

| JP2015153854A (ja) | 炭化珪素半導体装置 | |

| WO2014192437A1 (ja) | 炭化珪素半導体装置 | |

| JP2017092364A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2014060272A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2016058661A (ja) | 半導体装置 | |

| JP5895750B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2016167632A (ja) | 炭化珪素半導体装置 | |

| US10319820B2 (en) | Semiconductor device having silicon carbide layer provided on silicon carbide substrate | |

| JP2016122697A (ja) | 炭化珪素半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160412 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161115 |