WO2015166754A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- WO2015166754A1 WO2015166754A1 PCT/JP2015/059968 JP2015059968W WO2015166754A1 WO 2015166754 A1 WO2015166754 A1 WO 2015166754A1 JP 2015059968 W JP2015059968 W JP 2015059968W WO 2015166754 A1 WO2015166754 A1 WO 2015166754A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- cell

- region

- semiconductor device

- base region

- trench

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims description 47

- 238000009792 diffusion process Methods 0.000 claims description 24

- 230000001681 protective effect Effects 0.000 claims description 23

- 230000015556 catabolic process Effects 0.000 abstract description 33

- 238000000034 method Methods 0.000 abstract description 21

- 239000010410 layer Substances 0.000 description 90

- 230000002093 peripheral effect Effects 0.000 description 28

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 21

- 230000005684 electric field Effects 0.000 description 20

- 229910010271 silicon carbide Inorganic materials 0.000 description 19

- 239000012535 impurity Substances 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 15

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 14

- 229910052814 silicon oxide Inorganic materials 0.000 description 14

- 239000000758 substrate Substances 0.000 description 13

- 238000005530 etching Methods 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 11

- 230000000694 effects Effects 0.000 description 10

- 238000005468 ion implantation Methods 0.000 description 10

- 238000002513 implantation Methods 0.000 description 6

- 230000001629 suppression Effects 0.000 description 6

- 230000006378 damage Effects 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 239000010432 diamond Substances 0.000 description 3

- 229910003460 diamond Inorganic materials 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910002601 GaN Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

- H01L29/0623—Buried supplementary region, e.g. buried guard ring

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0856—Source regions

- H01L29/0865—Disposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

- H01L29/0852—Source or drain regions of field-effect devices of field-effect transistors with insulated gate of DMOS transistors

- H01L29/0856—Source regions

- H01L29/0869—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/1608—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41741—Source or drain electrodes for field effect devices for vertical or pseudo-vertical devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

Definitions

- the present invention relates to a trench gate type semiconductor device.

- Insulated gate semiconductor devices such as IGBTs (Insulated Gate Bipolar Transistors) and MOSFETs (Metal Oxide Semiconductor Semiconductor Field Field Effect Transistors) are widely used in power electronics equipment as switching elements that control power supply to motors and other loads.

- IGBTs Insulated Gate Bipolar Transistors

- MOSFETs Metal Oxide Semiconductor Semiconductor Field Field Effect Transistors

- power control MOSFETs the resistance during on-operation is small and the breakdown voltage during off-operation is required to be high.

- trench gate MOSFETs there is a trade-off between increasing the breakdown voltage and reducing the on-resistance. is there.

- MOSFETs and IGBTs using wide band gap semiconductors such as silicon carbide (SiC) are attracting attention as next-generation switching elements that can realize high breakdown voltage and low loss, and high voltages of about 1 kV or higher are attracting attention. It is considered promising for application in the technical field.

- a wide band gap semiconductor there are, for example, gallium nitride (GaN) -based material, diamond and the like in addition to SiC.

- MOSFETs for power control are handled as a single MOSFET by connecting a plurality of unit MOSFETs in parallel.

- MOSFETs can be classified according to the arrangement pattern of individual unit MOSFETs constituting the MOSFET.

- a source region is formed in a square pattern

- a cell type consisting of one unit MOSFET (cell) surrounded by a gate trench

- a source region is formed in an elongated stripe pattern

- the electric field is different from the inside of the MOSFET region at the outer periphery of the MOSFET region. For this reason, in a configuration in which cells having the same structure as the inside of the MOSFET region are arranged in the outer peripheral portion of the MOSFET region, avalanche breakdown may occur in the outer peripheral portion. Since the breakdown voltage of the entire MOSFET is determined by the lowest one of the breakdown voltages of the individual cells, the cells disposed in the outer peripheral portions having different electric field states are required to have a breakdown voltage equivalent to that of the internal cells. Therefore, for the purpose of increasing the breakdown voltage, it has been proposed that the cells arranged on the outer peripheral portion have a structure or dimensions different from those of the cells arranged inside.

- Patent Document 1 discloses a technique for suppressing the generation of a high electric field in the outer peripheral portion by extending a cell trench disposed in the outer peripheral portion to reach the electric field relaxation portion.

- Patent Document 2 discloses a technique for forming a structure dedicated to electric field relaxation in the outer peripheral portion, such as omitting the gate trench from all cells arranged in the outer peripheral portion. According to these techniques, the breakdown voltage in the outer peripheral cell where avalanche breakdown is likely to occur is improved, and the breakdown voltage of the entire MOSFET can be improved.

- the wiring for taking out the gate electrode and the source electrode of the MOSFET is connected to the gate pad and the source pad, respectively.

- the corners of the gate pad and the source pad may be formed in a curved shape. According to the analysis by the inventors, a tendency that avalanche breakdown frequently occurs in cells formed in a region facing the corner (curved portion) of the gate pad among the cells in the outer peripheral portion.

- Patent Documents 1 and 2 disclose a technique related to a cell in the outer peripheral portion, but suppress avalanche breakdown in a cell in which avalanche breakdown frequently occurs, that is, in a cell facing a corner (curved part) of the gate pad. That is not disclosed.

- the present invention has been made in view of the above problems, and an object thereof is to provide a technique capable of suppressing avalanche breakdown in a cell facing a corner of a gate pad.

- the semiconductor device includes a gate pad, a first cell disposed in a region facing a corner of the gate pad in plan view, and the gate pad opposite to the gate pad in plan view. 2nd cell arrange

- Each of the first and second cells includes a first conductive type semiconductor layer, a second conductive type base region formed on the semiconductor layer, and a lower portion of the base region through the base region.

- the trench reaching the semiconductor layer is disposed through a gate insulating film, and has a pattern corresponding to the outer shape of the first and second cells in plan view, and is electrically connected to the gate pad. Connected gate electrodes and a protective diffusion layer of the second conductivity type formed at the bottom of the trench.

- At least the second cell of the first and second cells includes a source region of a first conductivity type formed in a portion of the upper portion of the base region adjacent to the gate insulating film, the base region, and the base region.

- a source electrode electrically connected to the source region;

- the outline shape of the first and second cells is a quadrilateral or more polygonal shape, and each shortest distance between the longest side and each side facing the side in the outline shape of the first cell. Among these, the longest distance is equal to or less than twice the length of the equivalent one side or the short side of the second cell.

- the first cell disposed in a region facing the corner of the gate pad in plan view, and the second cell disposed in a region opposite to the gate pad with respect to the first cell,

- the longest distance is the length of an equal side or short side of the second cell. Less than twice. Therefore, avalanche breakdown in the first cell facing the corner portion of the gate pad can be suppressed.

- FIG. 3 is a plan view showing a configuration of a MOSFET according to the first embodiment.

- FIG. 3 is a plan view showing a configuration of a MOSFET according to the first embodiment.

- FIG. 3 is a plan view showing a configuration of a MOSFET according to the first embodiment.

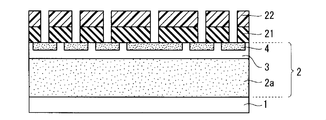

- 3 is a cross-sectional view showing a configuration of a MOSFET according to the first embodiment.

- FIG. 3 is a cross-sectional view showing a configuration of a MOSFET according to the first embodiment.

- FIG. It is a top view which shows the structure of a part of related MOSFET. It is sectional drawing which shows the structure of a part of related MOSFET. It is a figure which shows the relationship between cell dimension ratio and electric field strength.

- FIG. 3 is a plan view showing a configuration of a MOSFET according to the first embodiment.

- 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. 6 is a cross-sectional view showing the method of manufacturing the MOSFET according to the first embodiment.

- FIG. FIG. 6 is a plan view showing a configuration of a MOSFET according to a modification of the first embodiment.

- FIG. 6 is a plan view showing a configuration of a MOSFET according to a modification of the first embodiment.

- FIG. 6 is a plan view showing a configuration of a MOSFET according to a second embodiment.

- FIG. 6 is a cross-sectional view showing a configuration of a MOSFET according to a second embodiment.

- 7 is a cross-sectional view showing a configuration of a MOSFET according to a third embodiment.

- FIG. FIG. 6 is a plan view showing a configuration of a MOSFET according to a fourth embodiment.

- FIG. 6 is a cross-sectional view showing a configuration of a MOSFET according to a fourth embodiment.

- FIG. 1 is a plan view showing the overall configuration of the MOSFET according to the first embodiment.

- the MOSFET of FIG. 1 includes a gate pad 13 and a cell region 31, and has a generally rectangular shape as a whole.

- a gate pad 13 and a cell region 31 has a generally rectangular shape as a whole.

- the outer shape of the cell region 31 corresponds to the outer shape of the source pad.

- the gate pad 13 and the source pad (cell region 31) are formed with curved corners in order to avoid electric field concentration.

- the corners of the gate pad 13 and the source pad are sharp when viewed macroscopically, but are rounded when viewed microscopically.

- FIG. 2 is a plan view showing a part of the configuration of the MOSFET according to the first embodiment. Specifically, FIG. 2 is an enlarged plan view of a region surrounded by a broken line in FIG. In the cell region 31 of FIG. 1, a plurality of cells (cells 14, 15, 17) indicated by broken lines in FIG.

- the cell 15 is a cell (hereinafter referred to as an “outer periphery”) in a cell region 31 in a plan view in an outer peripheral region that does not face the gate pad 13 and a region that faces a side portion (straight line portion) of the gate pad 13. Part cell 15 ”).

- the outer shape of the outer peripheral cell 15 in plan view is a rectangular shape.

- the cell 17 (first cell) is a cell (hereinafter referred to as “corner cell 17”) disposed in a region (inner corner portion) of the cell region 31 facing the corner (curved portion) of the gate pad 13 in plan view. ).

- the outline shape of the corner cell 17 in plan view is two types of pentagonal shapes (polygonal shape of quadrilateral or more).

- the interior angles of the pentagonal shape of the corner cell 17 are all 90 ° or more.

- FIG. 3 is a diagram showing a region 41 facing the corner of the gate pad 13 in which the corner cell 17 is disposed.

- a region 41 facing the corner of the gate pad 13 corresponds to a region surrounded by a one-dot chain line in FIG.

- the cell region 31 overlapping the region is defined as the first region.

- a square or rectangular region having a line connecting the ends opposite to the gate pad 13 as a diagonal line is defined as the second region. It is prescribed.

- a region where the first region and the second region overlap is defined as a region 41 facing the corner of the gate pad 13 according to the first embodiment.

- the cell 14 (second cell) is arranged in an internal region of the cell region 31 such as the region opposite to the gate pad 13 with respect to the peripheral cell 15 or the corner cell 17 in the plan view.

- This is a cell (hereinafter referred to as “internal cell 14”).

- the internal cell 14 occupies many of the cells arranged in the cell region 31.

- the outer shape of the internal cell 14 in a plan view is a regular square shape (polygonal shape greater than or equal to a square shape).

- the outline shape of the internal cell 14 in plan view may be a rectangle or a square.

- the polygonal vertex of the corner cell 17 is larger than the polygonal vertex of the internal cell 14.

- FIG. 4 and 5 are cross-sectional views showing a part of the structure of the MOSFET according to the first embodiment. Specifically, FIG. 4 is a cross-sectional view taken along the line AA in FIG. 2 and shows a cross-sectional configuration of the internal cell 14. FIG. 5 is a cross-sectional view taken along the line BB in FIG. 2 and shows a cross-sectional configuration of the internal cell 14 and the corner cell 17.

- the internal cell 14 and the corner cell 17 include an n-type SiC substrate 1, an n-type (first conductivity type) epitaxial layer (semiconductor layer) 2, and a p-type (second conductivity type).

- Base region 3 n-type source region 4, gate insulating film 6, protective diffusion layer 7, gate electrode 8, interlayer insulating film 9, source electrode 10, ohmic electrode 11, and drain electrode 12.

- Each of the internal cell 14 and the corner cell 17 has a function of a MOSFET (switching element) by itself.

- MOSFET switching element

- the epitaxial layer 2 is formed by epitaxially growing a SiC layer on the SiC substrate 1. For example, as the SiC substrate 1 and the epitaxial layer 2, an epitaxial substrate in which the epitaxial layer 2 is previously grown on the SiC substrate 1 is applied.

- the base region 3 has a conductivity type opposite to that of the epitaxial layer 2 and is formed on the upper portion (upper surface) of the epitaxial layer 2.

- the remaining epitaxial layer 2 in which the base region 3 is not formed becomes a drift layer 2a.

- a trench (gate trench) 5 is formed in the epitaxial layer 2 and the base region 3. The trench 5 passes through the base region 3, and the bottom of the trench 5 reaches the drift layer 2 a (the epitaxial layer 2 below the base region 3).

- the gate insulating film 6 is provided on the inner surface (bottom surface and side surface) of the trench 5, and the gate electrode 8 is disposed in the trench 5 through the gate insulating film 6.

- the trench 5 is shown to have a pattern (generally a lattice pattern) corresponding to the outer shape of the inner cell 14, the outer peripheral cell 15, and the corner cell 17.

- the gate insulating film 6 and the gate electrode 8 (and thus the interlayer insulating film 9 and the source electrode 10 described later) are omitted from the viewpoint of simplifying the drawing, but the gate disposed in the trench 5.

- the electrode 8 also has a pattern (generally a lattice pattern) corresponding to the outer shape of the internal cell 14, the outer peripheral cell 15, and the corner cell 17 in plan view.

- a silicon oxide film, a gate wiring (polycrystalline silicon), and a silicon film (not shown) are not shown. These are disposed on the SiC substrate 1 in order.

- a contact hole is provided under the gate insulating film 6 adjacent to the gate pad lower well 32, and the gate electrode 8 is electrically connected to the gate pad 13 through the contact hole and the gate wiring. Yes.

- the protective diffusion layer 7 is formed in the drift layer 2 a adjacent to the bottom of the trench 5, that is, the lower portion of the trench 5.

- the protective diffusion layer 7 also has a substantially lattice-like pattern in plan view like the gate electrode 8.

- the protective diffusion layer 7 has a function of promoting the depletion of the drift layer 2a when the MOSFET is turned off and reducing the concentration of the electric field at the bottom of the trench 5 to suppress the breakdown of the gate insulating film 6. .

- a source region 4 is formed in a portion adjacent to the gate insulating film 6 in the upper part of the base region 3.

- the interlayer insulating film 9 is disposed on the source region 4 so as to cover a portion close to the gate insulating film 6 and the gate insulating film 6 and the gate electrode 8.

- a contact hole reaching the base region 3 and a portion far from the gate insulating film 6 in the source region 4 is provided, and a low-resistance ohmic electrode 11 is provided in the contact hole. Yes.

- the source electrode 10 constituting the source pad is disposed on the interlayer insulating film 9 and is electrically connected to the source region 4 and the base region 3 through the ohmic electrode 11.

- Drain electrode 12 is disposed on the lower surface of SiC substrate 1.

- the longest distance among the shortest distances between the longest side and each side facing the side is, for example, the inside

- the cell 14 is configured to be equal to or less than twice the uniform side.

- FIG. 6 is a plan view showing a part of the structure of the related MOSFET in the same manner as FIG.

- the same components as those described above are denoted by the same reference numerals, and components and problems different from the above-described components of the related MOSFET will be described.

- the related MOSFET includes one related corner cell 16 instead of the above-described corner cell 17.

- the outline shape of the related corner cell 16 in plan view has a longer side than the long side of the outer peripheral cell 15.

- the dimensions of the peripheral cell 15 and the internal cell 14 are made different in order to reduce the electric field applied to the peripheral cell 15.

- the corners of the outer shape such as the gate pad 13 have a certain curvature.

- the inventor found that the avalanche breakdown frequently occurs in the related corner cells 16. Therefore, the inventor found that the avalanche breakdown occurs in the related corner cell 16 because the cell on the termination region side of the entire MOSFET in FIG. 1 (for example, the outer peripheral cell 15 disposed at the other corner or side of the cell region 31). ) was considered to be different from the reason that avalanche destruction occurred. Then, the inventor considered the cause of the avalanche breakdown in the related corner cell 16 as follows.

- FIG. 7 is a cross-sectional view showing a part of the configuration of the related MOSFET, specifically, a cross-sectional view taken along the line CC in FIG. FIG. 7 shows a depletion layer end 18 assumed in the related MOSFET.

- the related corner cell 16 is greatly different in size and shape compared to the internal cell 14, and the distance between two opposing sides of the outer shape of the related corner cell 16 is relatively large. It has become. For this reason, as shown in FIG. 7, the depletion layer end 18 is close to the base region 3 at the center of the related corner cell 16. Along with this, the electric field strength at the center of the related corner cell 16 increases, and it is considered that avalanche breakdown is likely to occur. In the terminal region of the cell region 31, the electric field is suppressed by the effect of the termination structure. However, in the inner corner portion away from the terminal region, a unique electric field state is formed. This is thought to have some influence on the likelihood of avalanche destruction.

- FIG. 8 is a diagram showing the results. As shown in FIG. 8, the relationship between the cell size ratio and the electric field strength is not linear in a range where the cell size ratio is small (a range such as 2 or less). This is considered to be because the depletion layer extending from the trench 5 and the protective diffusion layer 7 reaches the center of the related corner cell 16.

- the depletion layer thickness is so small that the depletion layer extending from the trench 5 and the protective diffusion layer 7 does not reach the center of the related corner cell 16, and as a result, the related corner cell 16. It is considered that avalanche destruction frequently occurs in

- the longest distance among the shortest distances between the longest side and each side facing the side is appropriately shortened.

- the distance to be appropriately shortened is not more than twice the length of the uniform side of the internal cell 14.

- the distance to be appropriately shortened is set to be twice or less the length of the short side of the internal cell 14.

- the distance that should be appropriately shortened in the corner cell 17 is 1.5 times the length of the uniform side of the internal cell 14.

- the depletion layer extending from the long-side trench 5 and the protective diffusion layer 7 can suppress the depletion layer thickness from being reduced at the center of the corner cell 17.

- FIG. 9 is a diagram for explaining a distance that should be appropriately shortened in one of the corner cells 17 shown in FIG.

- the long side 17a of the corner cell 17 is indicated by a solid line

- the sides 17b and 17c facing the long side 17a are indicated by a two-dot chain line and a one-dot chain line, respectively.

- the shortest distance between the long side 17a and the opposite side 17b (the shortest distance among any points on the long side 17a and any point on the side 17b) is L1.

- the shortest distance between the long side 17a and the opposite side 17c (the shortest distance among any points on the long side 17a and any point on the side 17c) is L2.

- the longest distance is L2.

- the distance to be appropriately shortened is L2.

- FIG. 10 to 16 are diagrams showing the steps of the manufacturing method. Specifically, FIG. 10 to FIG. 16 are cross-sectional views along the line BB in FIG. 2, as in FIG.

- an epitaxial layer (semiconductor layer) 2 is formed on SiC substrate 1.

- an n-type low-resistance SiC substrate 1 having a 4H polytype is prepared, and an n-type epitaxial layer 2 is epitaxially grown thereon by a chemical vapor deposition (CVD) method.

- the finally formed drift layer 2a is epitaxially formed so as to ensure an impurity concentration of 1 ⁇ 10 14 cm ⁇ 3 to 1 ⁇ 10 17 cm ⁇ 3 and a thickness of 5 to 200 ⁇ m. Layer 2 was formed.

- a base region 3 and a source region 4 are formed by ion-implanting a predetermined dopant into the surface of the epitaxial layer 2. Thereby, the structure shown in FIG. 10 is obtained.

- the base region 3 is formed by ion implantation of aluminum (Al) which is a p-type impurity.

- Al aluminum

- the depth of Al ion implantation is set to a depth not exceeding the thickness of the epitaxial layer 2 (for example, about 0.5 to 3 ⁇ m).

- the impurity concentration of Al to be implanted is higher than the n-type impurity concentration of the epitaxial layer 2.

- the region of the epitaxial layer 2 deeper than the Al implantation depth remains as the n-type drift layer 2a.

- the base region 3 may be formed by p-type epitaxial growth. Also in this case, the impurity concentration and thickness of the base region 3 are the same as those formed by ion implantation.

- the source region 4 is formed by selectively ion-implanting nitrogen (N) into the surface of the base region 3.

- the outline shape of the source region 4 in plan view is formed in a pattern along the layout of the gate electrode 8 (trench 5) formed in the subsequent process (see FIG. 2).

- the depth of N ion implantation in this step is made shallower than the thickness of the base region 3.

- the impurity concentration of N to be implanted is higher than the p-type impurity concentration of the base region 3 and is, for example, in the range of 1 ⁇ 10 18 cm ⁇ 3 to 1 ⁇ 10 21 cm ⁇ 3 .

- a depletion suppression layer (not shown) formed by ion implantation of nitrogen (N) or phosphorus (P) that is an n-type impurity may be provided below the base region 3.

- N nitrogen

- P phosphorus

- a so-called JFET resistance is generated between the two, in which a current path is exploited by a depletion layer extending from both the base region 3 and the protective diffusion layer 7.

- the depletion suppression layer since the depletion layer is suppressed from extending from the base region 3 or the like at the time of ON, the JFET resistance can be reduced.

- the depletion suppression layer is deeper than the base region 3 and does not exceed the thickness of the epitaxial layer 2, and the thickness is, for example, about 0.5 to 3 ⁇ m.

- the impurity concentration of N in this step is preferably higher than the n-type impurity concentration of the epitaxial layer 2 and 1 ⁇ 10 17 cm ⁇ 3 or more.

- the depletion suppression layer may be formed by n-type epitaxial growth. In this case, the impurity concentration and thickness of the depletion suppression layer are the same as those formed by ion implantation.

- a silicon oxide film 21 of about 1 to 2 ⁇ m is deposited on the surface of the epitaxial layer 2, and an etching mask 22 made of a resist material is formed thereon.

- the etching mask 22 is formed by a photolithography technique in a pattern in which the formation region of the trench 5 in the source region 4 is opened. Since the trench 5 has a substantially lattice pattern in plan view, the pattern of the etching mask 22 includes a matrix pattern obtained by inverting the pattern.

- the silicon oxide film 21 is patterned by a reactive ion etching (RIE) process using the etching mask 22 as a mask. That is, the pattern of the etching mask 22 is transferred to the silicon oxide film 21. Thereby, the structure shown in FIG. 11 is obtained.

- the patterned silicon oxide film 21 becomes an etching mask for the next step.

- RIE reactive ion etching

- a trench 5 that penetrates the source region 4 and the base region 3 and reaches the drift layer 2a is formed by RIE processing using the patterned silicon oxide film 21 as a mask.

- the depth of the trench 5 is not less than the depth of the base region 3 and is, for example, about 1.0 to 6.0 ⁇ m.

- an implantation mask 23 having a pattern exposing the trench 5 (a pattern similar to the etching mask 22) is formed, and ion implantation using the implantation mask 23 as a mask is performed at the bottom of the trench 5.

- a p-type protective diffusion layer 7 is formed.

- Al is used as the p-type impurity of the protective diffusion layer 7.

- the impurity concentration of Al implanted in this step is preferably in the range of 1 ⁇ 10 17 cm ⁇ 3 to 1 ⁇ 10 19 cm ⁇ 3 , for example.

- a (patterned) silicon oxide film 21 which is an etching mask for forming the trench 5 may be used. Thereby, simplification of a manufacturing process and cost reduction can be aimed at.

- the silicon oxide film 21 is used instead of the implantation mask 23, the thickness and etching conditions of the silicon oxide film 21 are adjusted so that the silicon oxide film 21 having a certain thickness remains after the trench 5 is formed. There is a need to.

- annealing for activating the impurities implanted in the above process is performed using a heat treatment apparatus. This annealing is performed, for example, in an inert gas atmosphere such as argon (Ar) gas or in vacuum under processing conditions of 1300 to 1900 ° C. for 30 seconds to 1 hour.

- an inert gas atmosphere such as argon (Ar) gas or in vacuum under processing conditions of 1300 to 1900 ° C. for 30 seconds to 1 hour.

- a silicon oxide film is formed on the entire surface of the epitaxial layer 2 (including the inner surface of the trench 5)

- polysilicon is deposited by a low pressure CVD method so as to fill the trench 5.

- a gate insulating film 6 and a gate electrode 8 are formed in the trench 5 as shown in FIG.

- the silicon oxide film to be the gate insulating film 6 may be formed by thermally oxidizing the surface of the epitaxial layer 2 or may be formed by being deposited on the epitaxial layer 2.

- an interlayer insulating film 9 covering the gate electrode 8 is formed on the entire surface of the epitaxial layer 2 by a low pressure CVD method. Then, as shown in FIG. 15, contact holes reaching the source region 4 and the base region 3 are formed by patterning the interlayer insulating film 9.

- an ohmic electrode 11 is formed on the epitaxial layer 2 (source region 4 and base region 3) exposed at the bottom of the contact hole.

- a metal film mainly composed of nickel (Ni) is formed on the entire surface of the epitaxial layer 2 exposed at the bottom of the contact hole, and silicon carbide and silicon carbide are heat-treated at 600 to 1100 ° C.

- a silicide film to be the ohmic electrode 11 is formed by reaction.

- the unreacted metal film remaining on the interlayer insulating film 9 is removed by wet etching using nitric acid, sulfuric acid or hydrochloric acid, or a mixed solution thereof with hydrogen peroxide.

- the heat treatment may be performed again after the metal film remaining on the interlayer insulating film 9 is removed. In this case, if it is performed at a higher temperature than the previous heat treatment, an ohmic contact with even lower contact resistance is formed.

- an electrode material such as an Al alloy is deposited on the structure obtained in FIG. 15, thereby forming the source electrode 10 on the interlayer insulating film 9 and in the contact hole.

- the drain electrode 12 is formed by depositing an electrode material such as an Al alloy on the lower surface of the SiC substrate 1.

- the outermost shape of the corner cell 17 in plan view is the longest of the shortest distances between the longest side and each side facing the side.

- the long distance is configured to be equal to or less than twice the length of the uniform side or the short side of the internal cell 14.

- the corner cell 17 has more vertices on the polygon than the inner cell 14 on the polygon. Thereby, the layout of the corner cell 17 can be designed more easily than the internal cell 14.

- the interior angles on the polygons of the corner cells 17 are all 90 ° or more. As a result, avalanche breakdown in the corner cell 17 due to electric field concentration can be suppressed, so that the breakdown voltage can be improved.

- the corner cell 17 includes the source region 4 and the source electrode 10 and has a function of a MOSFET alone.

- the epitaxial layer (semiconductor layer) 2 includes a wide band gap semiconductor such as SiC.

- a wide band gap semiconductor such as SiC.

- the wide band gap is not limited to SiC, and may be, for example, a GaN-based material or diamond.

- the drift layer 2a and the SiC substrate 1 serving as the buffer layer have the same conductivity type in the above description, the drift layer 2a and the SiC substrate 1 have different conductivity types. It can also be applied to IGBTs. For example, in the configuration shown in FIGS. 4 and 5, an IGBT configuration is obtained by replacing the n conductivity type of the SiC substrate 1 with a p conductivity type. In such a configuration, the source region 4 and source electrode 10 of the MOSFET correspond to the emitter region and emitter electrode of the IGBT, respectively, and the drain electrode 12 of the MOSFET corresponds to the collector electrode.

- the gate electrode 8 (outer shape of the cell) has a substantially lattice pattern, but the present invention is not limited to this.

- the gate electrode 8 (the outer shape of the cell) may have a generally hexagonal pattern as shown in FIG. 17, for example, or may have a stripe pattern as shown in FIG. Alternatively, other patterns may be used. The same effect as described above can be obtained regardless of the pattern of the gate electrode 8 (the outer shape of the cell).

- the semiconductor device made of SiC which is one of the wide band gap semiconductors, has been described.

- the present invention is not limited to this, and the present invention can also be applied to semiconductor devices made of other wide band gap semiconductors such as gallium nitride (GaN) -based materials and diamond.

- GaN gallium nitride

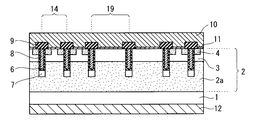

- FIG. 19 is a plan view showing a part of the configuration of the MOSFET according to the second embodiment of the present invention in the same manner as FIG.

- FIG. 20 is a cross-sectional view showing a part of the structure of the MOSFET according to the second embodiment. Specifically, it is a cross-sectional view along the line DD in FIG. 19, and shows the internal cell 14 and the corner cell. 17 shows a cross-sectional configuration.

- the same or similar components as those described above are denoted by the same reference numerals, and different portions will be mainly described.

- the MOSFET according to the second embodiment is different in that a corner cell 19 is provided instead of the corner cell 17 described in the first embodiment.

- the corner cell 17 according to the first embodiment includes the source region 4.

- the corner cell 19 according to the second embodiment includes the source region 4. It is comprised so that it may not be provided.

- corner cell 19 according to the second embodiment does not include the source region 4, the punch-through phenomenon can be suppressed.

- the corner cell 19 In order to suppress the punch-through phenomenon in the corner cell 19, a method of increasing the impurity concentration of the base region 3 and reducing the depletion layer extending into the base region 3 can be employed. The number of ion implantations increases.

- the corner cell 19 does not include the source region 4, and therefore, as a manufacturing method thereof, the source region 4 is formed in the process of FIG. 10 of the first embodiment. What is necessary is just to change the pattern of the corner cell 19 among patterns. Therefore, the MOSFET can be formed with the same man-hours as in the first embodiment.

- the corner cell 19 according to the second embodiment does not have the function of a MOSFET alone, the on-resistance of the MOSFET is equal to that of the first embodiment corresponding to the area of the corner cell 19 occupying the entire cell region 31. Although it increases above the on-resistance, it is negligibly small compared to variations in MOSFET manufacturing.

- the techniques described in Patent Documents 1 and 2 since all the cells in the outer peripheral portion of the cell region 31 lose the MOSFET function, compared to the increase in the on-resistance of the MOSFET according to the second embodiment. Much bigger.

- the corner cell 19 is configured not to include the source region 4.

- the on-resistance increases to a level that can be almost ignored, but it is possible to realize a high breakdown voltage by suppressing the occurrence of the punch-through phenomenon.

- the longest distance among the shortest distances between the longest side and each side facing the side is the inner side.

- the cell 14 may not be configured to be twice or less the length of the short side of the cell 14.

- FIG. 21 is a cross-sectional view showing a part of the configuration of the MOSFET according to the third embodiment in the same manner as FIG.

- the same or similar components as those described above are denoted by the same reference numerals, and different portions will be mainly described.

- the MOSFET according to the third embodiment is different in that a corner cell 20 is provided instead of the corner cell 17 described in the first embodiment.

- a corner cell 20 is provided instead of the corner cell 17 described in the first embodiment.

- the source electrode 10 and the source region 4 and the base region 3 are electrically connected in the corner cell 17, but as shown in FIG.

- the corner cell 20 according to the third embodiment may be configured not to include the source region 4 as in the second embodiment.

- the source electrode 10, the source region 4, and the base region 3 are configured to be electrically insulated.

- the on-resistance increases to a level that can be almost ignored, but it is possible to realize a high breakdown voltage by suppressing the occurrence of the punch-through phenomenon.

- the longest distance among the shortest distances between the longest side and each side facing the side is the inner

- the cell 14 may not be configured to be twice or less the length of the short side of the cell 14.

- the present invention can be freely combined with each embodiment and each modification, or can be appropriately modified and omitted with each embodiment and each modification.

- FIG. 22 is a plan view showing a part of the configuration of the MOSFET according to the fourth embodiment of the present invention in the same manner as FIG.

- FIG. 23 is a cross-sectional view showing a part of the configuration of the MOSFET according to the fourth embodiment in the same manner as in FIG. 20, and more specifically, a cross-sectional view taken along the line CC in FIG.

- the same or similar components as those described above are denoted by the same reference numerals, and different portions will be mainly described.

- the MOSFET according to the fourth embodiment is provided with an ineffective region 42 in which cells (inner cell 14, outer peripheral cell 15, corner cell 17) do not exist, instead of corner cell 17 described in the first embodiment. Is different. That is, as shown in FIG. 4, in the first embodiment, the corner cells 17 are arranged in the region 41 facing the gate pad 13, but as shown in FIG. An invalid area 42 is provided in the area 41.

- a trench 51 which is a second trench that reaches the epitaxial layer 2 below the base region 3 through the base region 3 such as the internal cell 14, is disposed.

- the trench 51 is wider than the trench 5 that is the first trench.

- the invalid region 42 includes an n-type protective diffusion layer 52 that is a second protective diffusion layer.

- the protective diffusion layer 52 is formed at the bottom of the trench 51, like the protective diffusion layer 7 that is the first protective diffusion layer.

- the etching mask 22 on the region 41 may be removed and the silicon oxide film 21 may be removed by RIE.

- RIE is performed using the silicon oxide film 21 as a mask in FIG. 12

- the trenches 51 are all disposed in the region 41, and the bottom of the trench 51 corresponding to the region 41 is protected by subsequent ion implantation.

- a diffusion layer 52 is formed. Thereby, the invalid region 42 can be formed.

- the invalid region 42 according to the fourth embodiment does not have the function of a MOSFET alone, but the increase in the on-resistance associated therewith is substantially negligible as in the second and third embodiments. It is.

- the invalid region 42 including the protective diffusion layer 52 formed at the bottom of the trench 51 is disposed in the region 41 facing the gate pad 13.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

<構成>

以下、本実施の形態1に係る半導体装置は、炭化珪素(SiC)半導体装置であってトレンチゲート型MOSFETである場合を例にして説明する。図1は、本実施の形態1に係るMOSFETの全体構成を示す平面図である。

図6は、関連MOSFETの一部の構成を図2と同様に示す平面図である。以下、関連MOSFETにおいて、以上で説明した構成要素と同一ものについては同じ参照符号を付して、関連MOSFETのうち上述の構成要素と異なる構成要素と問題点とについて説明する。

そこで、発明者は、これを利用することで、平面視においてゲートパッド13の曲部に対向する領域41に配設されたセル中心部での空乏層厚の減少を抑制することを想起した。

次に、本実施の形態1に係るMOSFETの製造方法について説明する。図10~図16は、当該製造方法の工程を示す図であり、具体的には、図5と同様に図2のB-B線に沿った断面図である。

以上に構成された本実施の形態1に係るMOSFETでは、コーナーセル17の平面視での外郭形状において、最も長い辺と、当該辺に対向する各辺との間の各最短距離のうち、最も長い距離が、内部セル14の均等な一辺または短辺の長さの2倍以下となるように構成される。これにより、コーナーセル17においても内部セル14と同等の空乏層厚を得ることができるため、アバランシェ破壊を抑制することができる。

なお、以上の説明では、ドリフト層2aと、バッファ層であるSiC基板1とが同じ導電型を有する構造のMOSFETについて述べたが、ドリフト層2aとSiC基板1とが異なる導電型を有する構造のIGBTに対しても適用可能である。例えば、図4及び図5に示した構成において、SiC基板1のn導電型をp導電型に代えればIGBTの構成となる。そして、そのような構成では、MOSFETのソース領域4及びソース電極10は、それぞれIGBTのエミッタ領域及びエミッタ電極に対応し、MOSFETのドレイン電極12はコレクタ電極に対応することになる。

<構成>

図19は、本発明の実施の形態2に係るMOSFETの構成の一部を、図2と同様に示す平面図である。図20は、本実施の形態2に係るMOSFETの構成の一部を示す断面図であり、具体的には、図19のD-D線に沿った断面図であり、内部セル14及びコーナーセル17の断面構成を示している。以下、本実施の形態2に係るMOSFETにおいて、以上で説明した構成要素と同一または類似するものについては同じ参照符号を付し、異なる部分について主に説明する。

図5及び図20を参照して、本実施の形態2に係るコーナーセル19の効果について説明する。コーナーセル17,19が配設された内側コーナー部では、電界状態がセル領域31の内部や他の外周部とは異なる状態となっているため、空乏層の延びが異なる。これに伴って、ソース領域4を備える実施の形態1のコーナーセル17では、ベース領域3内で上部のソース領域4から延びる空乏層と下部のドリフト層2aから延びる空乏層とが接触し、ドリフト層2aとソース領域4との間の絶縁が破れてキャリアが流れるパンチスルー現象が生じる可能性が多少ある。

<構成>

図21は、本実施の形態3に係るMOSFETの構成の一部を、図20と同様に示す断面図である。以下、本実施の形態3に係るMOSFETにおいて、以上で説明した構成要素と同一または類似するものについては同じ参照符号を付し、異なる部分について主に説明する。

図21を参照して、本実施の形態3に係るコーナーセル20の効果について説明する。コーナーセル20などの各種セルにアバランシェ電流が流れる経路は、ドレイン電極12とソース電極10との間である。このため、耐圧の低いコーナーセル20において、ソース電極10と、ソース領域4及びベース領域3とが電気的に絶縁されている本実施の形態3によれば、全体の耐圧を向上させることができる。また、本実施の形態3に係るMOSFETの製造方法としては、実施の形態1の図15の工程において、コーナーセル20における層間絶縁膜9を除去しないようにするだけでよく、容易に実現することができる。また、本実施の形態3に係るコーナーセル20は、単独でMOSFETの機能を有さないが、それに伴うオン抵抗の増加分は、実施の形態2と同様、実質的にほぼ無視できる程度である。

<構成>

図22は、本発明の実施の形態4に係るMOSFETの構成の一部を、図2と同様に示す平面図である。図23は、本実施の形態4に係るMOSFETの構成の一部を、図20と同様に示す断面図であり、具体的には図22のC-C線に沿った断面図である。以下、本実施の形態4に係るMOSFETにおいて、以上で説明した構成要素と同一または類似するものについては同じ参照符号を付し、異なる部分について主に説明する。

図21を参照して、本実施の形態4に係る無効領域42の効果について説明する。コーナーセル17などが配設される領域41(図3)がセル領域31に占める割合は実質的に無視できる程度である。しかし、当該領域41はこれまで説明してきたようにアバランシェ破壊が生じやすいため通常のセルを配設することが難しい。そこで、当該領域41全体をトレンチ51とし、その底部に保護拡散層52を設けることで当該領域41での耐圧低下を防ぎ、全体の耐圧を向上させることができる。

Claims (9)

- ゲートパッドと、

平面視において前記ゲートパッドの角部に対向する領域に配設された第1セルと、

平面視において前記第1セルに対して前記ゲートパッドと逆側の領域に配設された第2セルと

を備え、

前記第1及び第2セルのそれぞれは、

第1導電型の半導体層と、

前記半導体層の上部に形成された第2導電型のベース領域と、

前記ベース領域を貫通して前記ベース領域下の前記半導体層に達するトレンチ内に、ゲート絶縁膜を介して配設されるとともに、前記第1及び第2セルの平面視での外郭形状に対応するパターンを有し、かつ、前記ゲートパッドと電気的に接続されたゲート電極と、

前記トレンチの底部に形成された第2導電型の保護拡散層と

を備え、

前記第1及び第2セルのうち少なくとも前記第2セルは、

前記ベース領域の上部のうち、前記ゲート絶縁膜に隣接する部分に形成された第1導電型のソース領域と、

前記ベース領域及び前記ソース領域と電気的に接続されたソース電極と

をさらに備え、

前記第1及び第2セルの前記外郭形状は、四角形以上の多角形状であり、

前記第1セルの前記外郭形状において、最も長い辺と、当該辺に対向する各辺との間の各最短距離のうち、最も長い距離が、前記第2セルの均等な一辺または短辺の長さの2倍以下である、半導体装置。 - 請求項1に記載の半導体装置であって、

前記第1セルの前記多角形状の頂点は、前記第2セルの前記多角形状の頂点よりも多い、半導体装置。 - 請求項1に記載の半導体装置であって、

前記第1セルの前記多角形状の内角は全て90°以上である、半導体装置。 - 請求項1に記載の半導体装置であって、

前記第1セルは前記ソース領域を備えない、半導体装置。 - 請求項1に記載の半導体装置であって、

前記第1セルにおいて、前記ソース電極と、前記ベース領域及び前記ソース領域とが電気的に絶縁されている、半導体装置。 - 請求項1に記載の半導体装置であって、

前記第1セルは、

前記ソース領域及び前記ゲート電極をさらに備え、単独でスイッチング素子の機能を有する、半導体装置。 - ゲートパッドと、

セルと、

前記セルが存在しない、平面視において前記ゲートパッドの角部に対向する領域である無効領域と

を備え、

前記セルは、

第1導電型の半導体層と、

前記半導体層の上部に形成された第2導電型のベース領域と、

前記ベース領域を貫通して前記ベース領域下の前記半導体層に達する第1トレンチ内に、ゲート絶縁膜を介して配設されるとともに、前記セルの平面視での外郭形状に対応するパターンを有し、かつ、前記ゲートパッドと電気的に接続されたゲート電極と、

前記第1トレンチの底部に形成された第2導電型の第1保護拡散層と、

前記ベース領域の上部のうち、前記ゲート絶縁膜に隣接する部分に形成された第1導電型のソース領域と、

前記ベース領域及び前記ソース領域と電気的に接続されたソース電極と

を備え、

前記無効領域は、

前記ベース領域を貫通して前記ベース領域下の前記半導体層に達する第2トレンチの底部に形成された第2導電型の第2保護拡散層を備え、前記第2トレンチは前記第1トレンチよりも幅が大きい、半導体装置。 - 請求項1から請求項7のうちいずれか1項に記載の半導体装置であって、

前記半導体層は、ワイドバンドギャップ半導体を含む、半導体装置。 - 請求項1から請求項7のうちいずれか1項に記載の半導体装置であって、

前記ゲートパッドの前記角部は曲部を含む、半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201580021852.1A CN106463539B (zh) | 2014-05-01 | 2015-03-30 | 半导体装置 |

| US15/307,668 US9698221B2 (en) | 2014-05-01 | 2015-03-30 | Semiconductor device |

| JP2016500421A JP5985105B2 (ja) | 2014-05-01 | 2015-03-30 | 半導体装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014094383 | 2014-05-01 | ||

| JP2014-094383 | 2014-05-01 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2015166754A1 true WO2015166754A1 (ja) | 2015-11-05 |

Family

ID=54358491

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2015/059968 WO2015166754A1 (ja) | 2014-05-01 | 2015-03-30 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9698221B2 (ja) |

| JP (1) | JP5985105B2 (ja) |

| CN (1) | CN106463539B (ja) |

| WO (1) | WO2015166754A1 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170072496A (ko) * | 2015-12-17 | 2017-06-27 | 삼성전자주식회사 | 수직형 메모리 소자 및 그 형성 방법 |

| WO2022034636A1 (ja) * | 2020-08-11 | 2022-02-17 | 三菱電機株式会社 | 炭化珪素半導体装置および電力変換装置 |

| JP2023011834A (ja) * | 2019-09-13 | 2023-01-24 | 株式会社 日立パワーデバイス | 半導体装置および電力変換装置 |

| WO2023139931A1 (ja) * | 2022-01-20 | 2023-07-27 | 富士電機株式会社 | 半導体装置 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101949514B1 (ko) * | 2017-06-27 | 2019-02-19 | 현대오트론 주식회사 | 전력 반도체 소자 |

| JP7371335B2 (ja) * | 2019-03-13 | 2023-10-31 | 富士電機株式会社 | 半導体装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000323707A (ja) * | 1999-05-07 | 2000-11-24 | Hitachi Ltd | 半導体装置 |

| JP2005116822A (ja) * | 2003-10-08 | 2005-04-28 | Toyota Motor Corp | 絶縁ゲート型半導体装置およびその製造方法 |

| JP2006012960A (ja) * | 2004-06-23 | 2006-01-12 | Renesas Technology Corp | パワートランジスタ装置及びそれを用いたパワー制御システム |

| JP2009004655A (ja) * | 2007-06-22 | 2009-01-08 | Toyota Motor Corp | 半導体装置 |

| JP2010251422A (ja) * | 2009-04-13 | 2010-11-04 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| JP2011029675A (ja) * | 2010-11-11 | 2011-02-10 | Renesas Electronics Corp | 半導体装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4860102B2 (ja) * | 2003-06-26 | 2012-01-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US7470953B2 (en) | 2003-10-08 | 2008-12-30 | Toyota Jidosha Kabushiki Kaisha | Insulated gate type semiconductor device and manufacturing method thereof |

| JP2005322949A (ja) | 2005-08-05 | 2005-11-17 | Renesas Technology Corp | 半導体装置 |

| JP4735237B2 (ja) | 2005-12-20 | 2011-07-27 | トヨタ自動車株式会社 | 絶縁ゲート型半導体装置 |

| JP2011100877A (ja) | 2009-11-06 | 2011-05-19 | Toshiba Corp | 半導体装置及びその製造方法 |

-

2015

- 2015-03-30 WO PCT/JP2015/059968 patent/WO2015166754A1/ja active Application Filing

- 2015-03-30 US US15/307,668 patent/US9698221B2/en active Active

- 2015-03-30 JP JP2016500421A patent/JP5985105B2/ja active Active

- 2015-03-30 CN CN201580021852.1A patent/CN106463539B/zh active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000323707A (ja) * | 1999-05-07 | 2000-11-24 | Hitachi Ltd | 半導体装置 |

| JP2005116822A (ja) * | 2003-10-08 | 2005-04-28 | Toyota Motor Corp | 絶縁ゲート型半導体装置およびその製造方法 |

| JP2006012960A (ja) * | 2004-06-23 | 2006-01-12 | Renesas Technology Corp | パワートランジスタ装置及びそれを用いたパワー制御システム |

| JP2009004655A (ja) * | 2007-06-22 | 2009-01-08 | Toyota Motor Corp | 半導体装置 |

| JP2010251422A (ja) * | 2009-04-13 | 2010-11-04 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| JP2011029675A (ja) * | 2010-11-11 | 2011-02-10 | Renesas Electronics Corp | 半導体装置 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170072496A (ko) * | 2015-12-17 | 2017-06-27 | 삼성전자주식회사 | 수직형 메모리 소자 및 그 형성 방법 |

| KR102508897B1 (ko) | 2015-12-17 | 2023-03-10 | 삼성전자주식회사 | 수직형 메모리 소자 및 그 형성 방법 |

| JP2023011834A (ja) * | 2019-09-13 | 2023-01-24 | 株式会社 日立パワーデバイス | 半導体装置および電力変換装置 |

| JP7503612B2 (ja) | 2019-09-13 | 2024-06-20 | 株式会社 日立パワーデバイス | 半導体装置および電力変換装置 |

| WO2022034636A1 (ja) * | 2020-08-11 | 2022-02-17 | 三菱電機株式会社 | 炭化珪素半導体装置および電力変換装置 |

| JPWO2022034636A1 (ja) * | 2020-08-11 | 2022-02-17 | ||

| JP7332812B2 (ja) | 2020-08-11 | 2023-08-23 | 三菱電機株式会社 | 炭化珪素半導体装置および電力変換装置 |

| WO2023139931A1 (ja) * | 2022-01-20 | 2023-07-27 | 富士電機株式会社 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2015166754A1 (ja) | 2017-04-20 |

| CN106463539B (zh) | 2019-05-07 |

| US9698221B2 (en) | 2017-07-04 |

| JP5985105B2 (ja) | 2016-09-06 |

| US20170053984A1 (en) | 2017-02-23 |

| CN106463539A (zh) | 2017-02-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6049784B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| US8648349B2 (en) | Semiconductor device | |

| JP6038391B2 (ja) | 半導体装置 | |

| JP5985105B2 (ja) | 半導体装置 | |

| US10361266B2 (en) | Semiconductor device | |

| JP6099749B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP7029710B2 (ja) | 半導体装置 | |

| JP6312933B2 (ja) | 電力用半導体装置 | |

| JP6140823B2 (ja) | 炭化珪素半導体装置 | |

| JP6463214B2 (ja) | 半導体装置 | |

| JP6705155B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US9613809B2 (en) | Method of manufacturing silicon carbide semiconductor device | |

| JP2017112161A (ja) | 半導体装置 | |

| JP4972293B2 (ja) | 半導体装置およびその製造方法 | |

| JP2011040431A (ja) | 半導体装置およびその製造方法 | |

| JP6862782B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP6589263B2 (ja) | 半導体装置 | |

| JP6771433B2 (ja) | 半導体装置 | |

| JP5907097B2 (ja) | 半導体装置 | |

| JP7074173B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| WO2015076020A1 (ja) | 半導体装置 | |

| JP2017092364A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2016058661A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 15786556 Country of ref document: EP Kind code of ref document: A1 |

|

| ENP | Entry into the national phase |

Ref document number: 2016500421 Country of ref document: JP Kind code of ref document: A |

|

| WWE | Wipo information: entry into national phase |

Ref document number: 15307668 Country of ref document: US |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 15786556 Country of ref document: EP Kind code of ref document: A1 |