JP2014006518A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2014006518A JP2014006518A JP2013112886A JP2013112886A JP2014006518A JP 2014006518 A JP2014006518 A JP 2014006518A JP 2013112886 A JP2013112886 A JP 2013112886A JP 2013112886 A JP2013112886 A JP 2013112886A JP 2014006518 A JP2014006518 A JP 2014006518A

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- layer

- film

- light receiving

- oxide semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims description 163

- 239000004973 liquid crystal related substance Substances 0.000 claims abstract description 39

- 239000013078 crystal Substances 0.000 claims description 49

- 239000000758 substrate Substances 0.000 claims description 42

- 239000003990 capacitor Substances 0.000 claims description 14

- 239000000463 material Substances 0.000 claims description 10

- 238000003860 storage Methods 0.000 claims description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 8

- 206010034972 Photosensitivity reaction Diseases 0.000 abstract 1

- 230000036211 photosensitivity Effects 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 201

- 239000010408 film Substances 0.000 description 120

- 238000012546 transfer Methods 0.000 description 22

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 17

- 230000003287 optical effect Effects 0.000 description 17

- 230000006870 function Effects 0.000 description 14

- 238000010438 heat treatment Methods 0.000 description 14

- 238000000034 method Methods 0.000 description 13

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 239000000203 mixture Substances 0.000 description 12

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- 229910052733 gallium Inorganic materials 0.000 description 10

- 229910052738 indium Inorganic materials 0.000 description 10

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 229910052757 nitrogen Inorganic materials 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 229910052710 silicon Inorganic materials 0.000 description 9

- 239000010703 silicon Substances 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- 230000003321 amplification Effects 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- 238000003199 nucleic acid amplification method Methods 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 239000011701 zinc Substances 0.000 description 8

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000000843 powder Substances 0.000 description 7

- 238000005477 sputtering target Methods 0.000 description 7

- 101000653510 Homo sapiens TATA box-binding protein-like 2 Proteins 0.000 description 6

- 101000735431 Homo sapiens Terminal nucleotidyltransferase 4A Proteins 0.000 description 6

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 6

- 102100030631 TATA box-binding protein-like 2 Human genes 0.000 description 6

- 102000007315 Telomeric Repeat Binding Protein 1 Human genes 0.000 description 6

- 108010033711 Telomeric Repeat Binding Protein 1 Proteins 0.000 description 6

- 102000007316 Telomeric Repeat Binding Protein 2 Human genes 0.000 description 6

- 108010033710 Telomeric Repeat Binding Protein 2 Proteins 0.000 description 6

- 102100034939 Terminal nucleotidyltransferase 4A Human genes 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 229910007541 Zn O Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 239000007789 gas Substances 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 230000035945 sensitivity Effects 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 206010021143 Hypoxia Diseases 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 125000004430 oxygen atom Chemical group O* 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910001868 water Inorganic materials 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- -1 ITO Substances 0.000 description 1

- 125000002066 L-histidyl group Chemical group [H]N1C([H])=NC(C([H])([H])[C@](C(=O)[*])([H])N([H])[H])=C1[H] 0.000 description 1

- 239000004988 Nematic liquid crystal Substances 0.000 description 1

- 229910002668 Pd-Cu Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000006355 external stress Effects 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 229910021389 graphene Inorganic materials 0.000 description 1

- 239000005431 greenhouse gas Substances 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000012905 input function Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 230000035882 stress Effects 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/042—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by opto-electronic means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14641—Electronic components shared by two or more pixel-elements, e.g. one amplifier shared by two pixel elements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/13338—Input devices, e.g. touch panels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/1446—Devices controlled by radiation in a repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/1461—Pixel-elements with integrated switching, control, storage or amplification elements characterised by the photosensitive area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14678—Contact-type imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by at least one potential-jump barrier or surface barrier, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/102—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier

- H01L31/105—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier or surface barrier the potential barrier being of the PIN type

Abstract

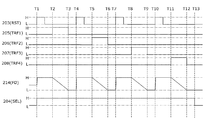

【解決手段】複数の単位画素で、アンプ回路部を共有することにより、単位画素に対応するアンプ回路部の面積を低減させ、単位画素の開口率を高める。また、より多くの単位画素で同一のアンプ回路部を共有することで、受光感度を高めても、単位画素に対応する光センサ回路の面積の増大を防ぐ。更に、単位画素の開口率を高めることで、液晶表示装置におけるバックライトの消費電力を下げる。

【選択図】図1

Description

本実施の形態では、1個のアンプ回路部を複数の単位画素で共有することにより、単位画素に対応する光センサ回路の面積を低減させた半導体装置について説明する。表示部内におけるデッドスペースを低減させることで、結果的に単位画素の開口率を高められる。

本実施の形態では、本発明の一態様に係る半導体装置が反射型液晶表示領域を有する場合について説明する。

本実施の形態では、本発明の一態様に係る半導体装置が透過型液晶表示領域を有する場合について説明する。なお本実施の形態において、実施の形態2と同じものは同じ符号で示し、その説明は省略する。

本実施の形態では、画像表示を行う表示部を有する電気機器の一例を図6(A)及び図6(B)に示す。

本実施の形態では、実施の形態2で示した半導体装置とは異なる反射型液晶表示領域を有する半導体装置について、図7を用いて説明する。

12 アンプ回路部

13 受光部

14 デッドスペース

15 単位画素

100 表示部

101 画素回路

102 光センサ回路

103 アンプ回路部

104 単位画素

105 受光部

106 受光素子

107 転送トランジスタ

108 リセットトランジスタ

109 増幅トランジスタ

110 選択トランジスタ

111 トランジスタ

112 液晶素子

113 保持容量

201 電源線

204 選択信号線

207 信号線

208 信号線

209 グランド線

211 走査線

212 信号線

213 グランド線

214 ノード

221 トランジスタ

222 保持容量

223 液晶素子

224 容量配線

227 走査線

228 酸化物半導体層

230 基板

231 絶縁層

232 ゲート絶縁層

233 酸化物半導体層

234 電極層

237 絶縁層

240 非単結晶半導体層

241 絶縁層

242 反射電極層

243 接続電極層

244 配向膜

245 接続電極層

260 信号線

262 電極層

263 接続電極層

264 電源線

273 電極層

278 電極層

301 基板

302 遮光層

303 カラーフィルタ

304 導電膜

305 液晶層

306 配向膜

311 光センサ回路

312 アンプ回路部

313 受光部

315 単位画素

1030 電気機器

1031 ボタン

1032 表示部

1033 領域

1034 スイッチ

1035 電源スイッチ

1036 キーボード表示スイッチ

Claims (7)

- 液晶素子を含む複数の画素と、

第1のトランジスタ及び第2のトランジスタを含むアンプ回路と、

非単結晶半導体層を含む複数の受光素子と、

各前記受光素子に対して設ける第3のトランジスタと、を有し、

前記第1のトランジスタの一方の端子と、前記第2のトランジスタのゲート端子と、ノードとは、電気的に接続され、

各前記第3のトランジスタの一方の端子と、前記ノードとは、電気的に接続され、

前記アンプ回路は、4個以上20個以下の前記画素に対して1個設ける

ことを特徴とする半導体装置。 - 請求項1において、

前記非単結晶半導体層は、アモルファスシリコン層である

ことを特徴とする半導体装置。 - 請求項1又は請求項2において、

前記トランジスタの半導体層として、酸化物半導体材料を用いる

ことを特徴とする半導体装置。 - 請求項1乃至請求項3のいずれか一項において、

前記アンプ回路は、一方の端子が前記第2のトランジスタの一方の端子と電気的に接続され、他方の端子が出力信号線と電気的に接続される第4のトランジスタを含む

ことを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一項において、

前記画素は、前記第1乃至第4のトランジスタと同一基板上に形成される第5のトランジスタと、保持容量とを有する

ことを特徴とする半導体装置。 - 請求項1乃至請求項5のいずれか一項において、

前記半導体装置は、透過型液晶表示領域を有する

ことを特徴とする半導体装置。 - 請求項1乃至請求項6のいずれか一項において、

前記半導体装置は、反射型液晶表示領域を有する

ことを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112886A JP2014006518A (ja) | 2012-05-29 | 2013-05-29 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012122521 | 2012-05-29 | ||

| JP2012122521 | 2012-05-29 | ||

| JP2013112886A JP2014006518A (ja) | 2012-05-29 | 2013-05-29 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014006518A true JP2014006518A (ja) | 2014-01-16 |

| JP2014006518A5 JP2014006518A5 (ja) | 2016-04-07 |

Family

ID=49669121

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013112886A Withdrawn JP2014006518A (ja) | 2012-05-29 | 2013-05-29 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9147706B2 (ja) |

| JP (1) | JP2014006518A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021005088A (ja) * | 2020-08-18 | 2021-01-14 | 株式会社ジャパンディスプレイ | 入力機能付き表示装置 |

| JP2021158375A (ja) * | 2015-10-09 | 2021-10-07 | 株式会社半導体エネルギー研究所 | 撮像装置 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9153699B2 (en) * | 2012-06-15 | 2015-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor with multiple oxide semiconductor layers |

| US9817520B2 (en) | 2013-05-20 | 2017-11-14 | Semiconductor Energy Laboratory Co., Ltd. | Imaging panel and imaging device |

| KR102092844B1 (ko) * | 2013-10-25 | 2020-04-14 | 엘지디스플레이 주식회사 | 액정 디스플레이 장치와 이의 제조 방법 |

| KR102234434B1 (ko) * | 2013-12-27 | 2021-04-02 | 삼성디스플레이 주식회사 | 표시패널 및 그 제조방법 |

| US9881954B2 (en) | 2014-06-11 | 2018-01-30 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device |

| JP6570417B2 (ja) | 2014-10-24 | 2019-09-04 | 株式会社半導体エネルギー研究所 | 撮像装置および電子機器 |

| US10522693B2 (en) | 2015-01-16 | 2019-12-31 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and electronic device |

| US10161031B2 (en) * | 2015-02-27 | 2018-12-25 | Jx Nippon Mining & Metals Corporation | Oxide sintered compact and sputtering target formed from said oxide sintered compact |

| JP2016173814A (ja) * | 2015-03-17 | 2016-09-29 | 株式会社半導体エネルギー研究所 | 情報処理装置、プログラム |

| WO2016152349A1 (ja) * | 2015-03-23 | 2016-09-29 | Jx金属株式会社 | 酸化物焼結体及び該酸化物焼結体からなるスパッタリングターゲット |

| US11036321B2 (en) * | 2018-07-27 | 2021-06-15 | Lg Display Co., Ltd. | Light control film and display apparatus including the same |

| US20200111815A1 (en) * | 2018-10-09 | 2020-04-09 | Innolux Corporation | Display device |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009271308A (ja) * | 2008-05-07 | 2009-11-19 | Seiko Epson Corp | 表示装置および電子機器 |

| JP2012034354A (ja) * | 2010-07-01 | 2012-02-16 | Semiconductor Energy Lab Co Ltd | 固体撮像装置、半導体表示装置 |

| US20120050196A1 (en) * | 2010-08-27 | 2012-03-01 | Semiconductor Energy Laboratory Co., Ltd. | Input/output device |

Family Cites Families (110)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| EP0820644B1 (en) | 1995-08-03 | 2005-08-24 | Koninklijke Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| US6195183B1 (en) * | 1997-07-15 | 2001-02-27 | Rohm Co., Ltd. | Image reading apparatus and image sensor chip thererfor |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| US6972753B1 (en) | 1998-10-02 | 2005-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Touch panel, display device provided with touch panel and electronic equipment provided with display device |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| US6747638B2 (en) | 2000-01-31 | 2004-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Adhesion type area sensor and display device having adhesion type area sensor |

| US7430025B2 (en) | 2000-08-23 | 2008-09-30 | Semiconductor Energy Laboratory Co., Ltd. | Portable electronic device |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| WO2003040441A1 (en) | 2001-11-05 | 2003-05-15 | Japan Science And Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| AU2003289448A1 (en) | 2003-01-08 | 2004-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and its fabricating method |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| KR20070116888A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 및 박막 트랜지스터 |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| JP5118811B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 発光装置及び表示装置 |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| BRPI0517568B8 (pt) | 2004-11-10 | 2022-03-03 | Canon Kk | Transistor de efeito de campo |

| EP1815530B1 (en) | 2004-11-10 | 2021-02-17 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI412138B (zh) | 2005-01-28 | 2013-10-11 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7608531B2 (en) | 2005-01-28 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| JP4609168B2 (ja) | 2005-02-28 | 2011-01-12 | セイコーエプソン株式会社 | 電気泳動表示装置の駆動方法 |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| EP1998375A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101358954B1 (ko) | 2005-11-15 | 2014-02-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 다이오드 및 액티브 매트릭스 표시장치 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP4395622B2 (ja) * | 2007-08-31 | 2010-01-13 | カシオ計算機株式会社 | 光センサ及びそれを備える表示装置 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| TWI585955B (zh) | 2008-11-28 | 2017-06-01 | 半導體能源研究所股份有限公司 | 光感測器及顯示裝置 |

| KR101889382B1 (ko) | 2010-01-20 | 2018-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 전자 기기 및 전자 시스템 |

| WO2011111504A1 (en) | 2010-03-08 | 2011-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device and electronic system |

-

2013

- 2013-05-21 US US13/898,716 patent/US9147706B2/en active Active

- 2013-05-29 JP JP2013112886A patent/JP2014006518A/ja not_active Withdrawn

-

2015

- 2015-08-17 US US14/827,567 patent/US9471182B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009271308A (ja) * | 2008-05-07 | 2009-11-19 | Seiko Epson Corp | 表示装置および電子機器 |

| JP2012034354A (ja) * | 2010-07-01 | 2012-02-16 | Semiconductor Energy Lab Co Ltd | 固体撮像装置、半導体表示装置 |

| US20120050196A1 (en) * | 2010-08-27 | 2012-03-01 | Semiconductor Energy Laboratory Co., Ltd. | Input/output device |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021158375A (ja) * | 2015-10-09 | 2021-10-07 | 株式会社半導体エネルギー研究所 | 撮像装置 |

| JP2021005088A (ja) * | 2020-08-18 | 2021-01-14 | 株式会社ジャパンディスプレイ | 入力機能付き表示装置 |

| JP7095038B2 (ja) | 2020-08-18 | 2022-07-04 | 株式会社ジャパンディスプレイ | 入力機能付き透明ディスプレイ |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150355744A1 (en) | 2015-12-10 |

| US20130320333A1 (en) | 2013-12-05 |

| US9147706B2 (en) | 2015-09-29 |

| US9471182B2 (en) | 2016-10-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9471182B2 (en) | Semiconductor device having sensor circuits with amplifier circuits and light-receiving elements | |

| JP6317412B2 (ja) | 表示装置及び表示装置の作製方法 | |

| JP6538099B2 (ja) | 電子機器 | |

| JP6154660B2 (ja) | タッチパネル | |

| JP5174988B2 (ja) | 回路基板および表示装置 | |

| US8619208B2 (en) | Display and method for manufacturing display | |

| US8803151B2 (en) | Semiconductor device | |

| CN102997993B (zh) | 光感测装置、驱动方法、以及光学触摸屏装置 | |

| TWI453805B (zh) | 顯示器及其製作方法 | |

| US20130088460A1 (en) | Optical touch screen apparatus and method of manufacturing the optical touch screen apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170310 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170822 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20171020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171221 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20180327 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20180622 |