JP2012503866A - キャリア基板および複数の放射放出半導体部品を備えたオプトエレクトロニクスモジュール、およびその製造方法 - Google Patents

キャリア基板および複数の放射放出半導体部品を備えたオプトエレクトロニクスモジュール、およびその製造方法 Download PDFInfo

- Publication number

- JP2012503866A JP2012503866A JP2011528181A JP2011528181A JP2012503866A JP 2012503866 A JP2012503866 A JP 2012503866A JP 2011528181 A JP2011528181 A JP 2011528181A JP 2011528181 A JP2011528181 A JP 2011528181A JP 2012503866 A JP2012503866 A JP 2012503866A

- Authority

- JP

- Japan

- Prior art keywords

- radiation

- emitting semiconductor

- semiconductor component

- carrier substrate

- contact region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 234

- 239000000758 substrate Substances 0.000 title claims abstract description 86

- 238000000034 method Methods 0.000 title claims abstract description 34

- 230000005693 optoelectronics Effects 0.000 title claims abstract description 20

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 16

- 230000005855 radiation Effects 0.000 claims abstract description 80

- 239000004020 conductor Substances 0.000 claims abstract description 37

- 230000005670 electromagnetic radiation Effects 0.000 claims abstract description 6

- 238000006243 chemical reaction Methods 0.000 claims description 25

- 238000010292 electrical insulation Methods 0.000 claims description 11

- 238000007639 printing Methods 0.000 claims description 8

- 238000007740 vapor deposition Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 149

- 239000010408 film Substances 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 230000003287 optical effect Effects 0.000 description 10

- 239000000463 material Substances 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 3

- 239000012777 electrically insulating material Substances 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 229910000679 solder Inorganic materials 0.000 description 3

- 238000003892 spreading Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- 238000010521 absorption reaction Methods 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000007613 environmental effect Effects 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 238000007649 pad printing Methods 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920001296 polysiloxane Polymers 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 238000003491 array Methods 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 238000013139 quantization Methods 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24105—Connecting bonding areas at different heights

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/24137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/24221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/24225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/24226—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the HDI interconnect connecting to the same level of the item at which the semiconductor or solid-state body is mounted, e.g. the item being planar

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/2499—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids

- H01L2224/24996—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids being formed on an item to be connected not being a semiconductor or solid-state body

- H01L2224/24998—Reinforcing structures, e.g. ramp-like support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

- H01L2924/12036—PN diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Led Device Packages (AREA)

Abstract

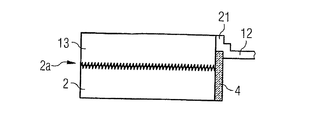

【選択図】図2

Description

a)複数の放射放出半導体部品をキャリア基板上に配置するステップであって、キャリア基板が、放射放出半導体部品との電気接続を形成するための構造化された導体トラックを有し、放射放出半導体部品それぞれが、電磁放射を発生させるのに適している活性層と、第1のコンタクト領域と、第2のコンタクト領域と、を備えており、第1のコンタクト領域それぞれが、キャリア基板とは反対側の放射放出半導体部品の面に配置されている、ステップと、

b)放射放出半導体部品に電気絶縁層を形成するステップであって、電気絶縁層が、それぞれの放射放出半導体部品の第1のコンタクト領域の範囲に切取り部を有する、ステップと、

c)電気絶縁層の部分領域に導電性構造を形成するステップであって、導電性構造の1つが、放射放出半導体部品の少なくとも第1のコンタクト領域を、さらなる放射放出半導体部品のさらなる第1のコンタクト領域に、またはキャリア基板の導体トラックに、導電接続する、ステップと、

を含んでいる。

Claims (15)

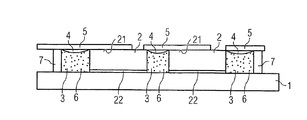

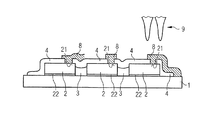

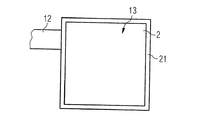

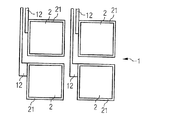

- キャリア基板(1)および複数の放射放出半導体部品(2)を備えているオプトエレクトロニクスモジュールであって、

− 前記キャリア基板(1)が、前記放射放出半導体部品(2)との電気接続を形成するための構造化された導体トラックを有し、

− 前記放射放出半導体部品(2)それぞれが、電磁放射を生成するのに適している活性層(2a)と、第1のコンタクト領域(21)と、第2のコンタクト領域(22)と、を備えており、前記第1のコンタクト領域(21)それぞれが、前記キャリア基板(1)とは反対側の前記放射放出半導体部品(2)の面に配置されており、

− 前記放射放出半導体部品(2)に電気絶縁層(4)が設けられており、前記電気絶縁層(4)それぞれが、前記放射放出半導体部品(2)の前記第1のコンタクト領域(21)の範囲に切取り部を有し、

− 前記電気絶縁層(4)の一部分の上に導電性構造(8)が配置されており、

− 前記導電性構造の1つが、放射放出半導体部品(2)の少なくとも前記第1のコンタクト領域(21)を、さらなる放射放出半導体部品(2)のさらなる第1のコンタクト領域に、または前記キャリア基板(1)の導体トラックに、導電接続している、

オプトエレクトロニクスモジュール。 - 少なくとも前記放射放出半導体部品(2)の間に平坦化層(3)が配置されている、

請求項1に記載のモジュール。 - 前記平坦化層(3)が少なくとも1種類の変換要素を含んでいる、

請求項2に記載のモジュール。 - 前記電気絶縁層(4)が少なくとも1種類の変換要素(6)を含んでいる、

請求項1から請求項3のいずれかに記載のモジュール。 - 前記放射放出半導体部品(2)が、前記キャリア基板(1)上に配置されているフレーム(7)によって一緒に囲まれている、

請求項1から請求項4のいずれかに記載のモジュール。 - 前記キャリア基板(1)がフレキシブル基板である、

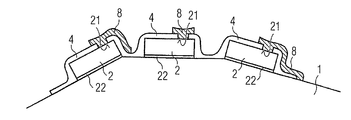

請求項1から請求項5のいずれかに記載のモジュール。 - 前記放射放出半導体部品(2)が上に配置されている、前記キャリア基板(1)の面が、非平面的である、

請求項1から請求項6のいずれかに記載のモジュール。 - 前記導電性構造(8)が、前記電気絶縁層(4)の上に配置されている異方性層によって形成されており、前記異方性層それぞれが、前記放射放出半導体部品(2)の少なくとも前記第1のコンタクト領域(21)の範囲に導電性領域(8a)を有する、

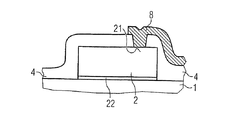

請求項1から請求項7のいずれかに記載のモジュール。 - 前記電気絶縁層(4)が、構造化された回路基板によって形成されており、前記導電性構造(8)が、前記回路基板から突き出している導電性ウェブによって形成されている、

請求項1から請求項7のいずれかに記載のモジュール。 - 前記電気絶縁層(4)が、それぞれの前記放射放出半導体部品(2)の周囲、それぞれの前記放射放出半導体部品(2)の側面領域の一部分に延在しており、前記放射放出半導体部品(2)それぞれの前記第1のコンタクト領域(21)が、前記キャリア基板(1)とは反対側の前記放射放出半導体部品(2)の面に前記第1のコンタクト領域(21)が存在しないように、前記電気絶縁層(4)の上に配置されている、

請求項1から請求項9のいずれかに記載のモジュール。 - オプトエレクトロニクスモジュールを製造する方法であって、

− 複数の放射放出半導体部品(2)をキャリア基板(1)上に配置するステップであって、前記キャリア基板(1)が、前記放射放出半導体部品(2)との電気接続を形成するための構造化された導体トラックを有し、前記放射放出半導体部品(2)それぞれが、電磁放射を発生させるのに適している活性層(2a)と、第1のコンタクト領域(21)と、第2のコンタクト領域(22)と、を備えており、前記第1のコンタクト領域(21)それぞれが、前記キャリア基板(1)とは反対側の前記放射放出半導体部品(2)の面に配置されている、前記ステップと、

− 前記放射放出半導体部品(2)に電気絶縁層(4)を形成するステップであって、前記電気絶縁層(4)が、それぞれの前記放射放出半導体部品(2)の前記第1のコンタクト領域(21)の範囲に切取り部(4a)を有する、前記ステップと、

− 前記電気絶縁層(4)の部分領域に導電性構造(8)を形成するステップであって、前記導電性構造(8)の1つが、放射放出半導体部品(2)の少なくとも前記第1のコンタクト領域(21)を、さらなる放射放出半導体部品(2)のさらなる第1のコンタクト領域(21)に、または前記キャリア基板(1)の導体トラックに、導電接続する、前記ステップと、

を含んでいる、方法。 - 前記導電性構造(8)が印刷法によって形成される、

請求項11に記載の方法。 - 前記導電性構造(8)が蒸着によって形成される、

請求項11に記載の方法。 - 前記導電性構造(8)が、前記電気絶縁層(4)の上に配置される異方性層によって形成され、前記異方性層が、前記放射放出半導体部品(2)の少なくとも前記第1のコンタクト領域(21)の範囲において導電性として具体化される、

請求項11に記載の方法。 - 前記導電性構造(8)それぞれが導電性ウェブとして具体化され、前記ウェブそれぞれが、前記放射放出半導体部品(2)の前記第1のコンタクト領域(21)に、スタンピングウェッジ工程によって導電接続される、

請求項11に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008049188A DE102008049188A1 (de) | 2008-09-26 | 2008-09-26 | Optoelektronisches Modul mit einem Trägersubstrat und einer Mehrzahl von strahlungsemittierenden Halbleiterbauelementen und Verfahren zu dessen Herstellung |

| DE102008049188.8 | 2008-09-26 | ||

| PCT/DE2009/001217 WO2010034278A1 (de) | 2008-09-26 | 2009-08-25 | Optoelektronisches modul mit einem trägersubstrat und einer mehrzahl von strahlungsemittierenden halbleiterbauelementen und verfahren zu dessen herstellung |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012503866A true JP2012503866A (ja) | 2012-02-09 |

| JP2012503866A5 JP2012503866A5 (ja) | 2012-10-11 |

Family

ID=41602690

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011528181A Pending JP2012503866A (ja) | 2008-09-26 | 2009-08-25 | キャリア基板および複数の放射放出半導体部品を備えたオプトエレクトロニクスモジュール、およびその製造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US8461604B2 (ja) |

| EP (1) | EP2297780B1 (ja) |

| JP (1) | JP2012503866A (ja) |

| KR (1) | KR20110057263A (ja) |

| CN (1) | CN102165588B (ja) |

| DE (1) | DE102008049188A1 (ja) |

| TW (1) | TWI438888B (ja) |

| WO (1) | WO2010034278A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013539604A (ja) * | 2010-09-07 | 2013-10-24 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツング | オプトエレクトロニクス半導体部品の製造方法 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011145794A1 (ko) * | 2010-05-18 | 2011-11-24 | 서울반도체 주식회사 | 파장변환층을 갖는 발광 다이오드 칩과 그 제조 방법, 및 그것을 포함하는 패키지 및 그 제조 방법 |

| DE102011055549A1 (de) | 2011-09-30 | 2013-04-04 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Bauelements mit einer drahtlosen Kontaktierung |

| DE102012209325B4 (de) * | 2012-06-01 | 2021-09-30 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Optoelektronisches Modul |

| US9673254B2 (en) * | 2013-07-22 | 2017-06-06 | Lg Innotek Co., Ltd. | Light emitting device |

| KR101503403B1 (ko) * | 2013-09-09 | 2015-03-17 | 삼성디스플레이 주식회사 | 발광소자모듈 및 그 제조방법 |

| US9195358B1 (en) * | 2014-04-16 | 2015-11-24 | Eastman Kodak Company | Z-fold multi-element substrate structure |

| DE102016208431A1 (de) * | 2016-05-17 | 2017-11-23 | Osram Opto Semiconductors Gmbh | Anordnung mit einem elektrischen Bauteil |

| DE102018120637A1 (de) * | 2018-08-23 | 2020-02-27 | Osram Opto Semiconductors Gmbh | Leiterplatte und verfahren zur herstellung einer leiterplatte mit mindestens einem in die leiterplatte integrierten optoelektronischen bauelement |

| DE102019100794A1 (de) * | 2018-12-20 | 2020-06-25 | Osram Opto Semiconductors Gmbh | Laservorrichtung und verfahren zur herstellung einer laservorrichtung |

| DE102019114315A1 (de) * | 2019-05-28 | 2020-12-03 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Anordnung und verfahren zur herstellung einer anordnung |

| KR20210072194A (ko) * | 2019-12-06 | 2021-06-17 | 삼성디스플레이 주식회사 | 발광 소자의 정렬 방법, 이를 이용한 표시 장치의 제조 방법 및 표시 장치 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55120081A (en) * | 1979-03-08 | 1980-09-16 | Tokyo Shibaura Electric Co | Led display unit |

| JPS575356A (en) * | 1980-06-13 | 1982-01-12 | Toshiba Corp | Hybrid integrated circuit device |

| JPH038384U (ja) * | 1989-06-12 | 1991-01-25 | ||

| JPH04131958U (ja) * | 1991-05-28 | 1992-12-04 | 三洋電機株式会社 | 発光ダイオード表示装置 |

| JPH0832112A (ja) * | 1994-07-20 | 1996-02-02 | Toyoda Gosei Co Ltd | 3族窒化物半導体発光素子 |

| JP2004172578A (ja) * | 2002-09-02 | 2004-06-17 | Matsushita Electric Ind Co Ltd | 発光装置 |

| JP2007517378A (ja) * | 2003-12-24 | 2007-06-28 | 松下電器産業株式会社 | 半導体発光装置、照明モジュール、照明装置、表示素子、および半導体発光装置の製造方法 |

Family Cites Families (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS575359A (en) * | 1980-06-11 | 1982-01-12 | Hitachi Ltd | Semiconductor device |

| JPS61290780A (ja) | 1985-06-19 | 1986-12-20 | Hitachi Vlsi Eng Corp | 光電変換装置 |

| US5519332A (en) * | 1991-06-04 | 1996-05-21 | Micron Technology, Inc. | Carrier for testing an unpackaged semiconductor die |

| DE19638667C2 (de) | 1996-09-20 | 2001-05-17 | Osram Opto Semiconductors Gmbh | Mischfarbiges Licht abstrahlendes Halbleiterbauelement mit Lumineszenzkonversionselement |

| US6529027B1 (en) * | 2000-03-23 | 2003-03-04 | Micron Technology, Inc. | Interposer and methods for fabricating same |

| DE10051159C2 (de) * | 2000-10-16 | 2002-09-19 | Osram Opto Semiconductors Gmbh | LED-Modul, z.B. Weißlichtquelle |

| KR20040029385A (ko) | 2001-08-01 | 2004-04-06 | 남 영 김 | 화상표시장치 |

| US6784540B2 (en) * | 2001-10-10 | 2004-08-31 | International Rectifier Corp. | Semiconductor device package with improved cooling |

| TW200405790A (en) * | 2002-08-08 | 2004-04-01 | Dainippon Printing Co Ltd | Electromagnetic wave shielding sheet |

| DE10245945A1 (de) * | 2002-09-30 | 2004-04-08 | Osram Opto Semiconductors Gmbh | Lichtquellenmodul sowie Verfahren zu dessen Herstellung |

| DE10353679A1 (de) | 2003-11-17 | 2005-06-02 | Siemens Ag | Kostengünstige, miniaturisierte Aufbau- und Verbindungstechnik für LEDs und andere optoelektronische Module |

| US7858994B2 (en) * | 2006-06-16 | 2010-12-28 | Articulated Technologies, Llc | Solid state light sheet and bare die semiconductor circuits with series connected bare die circuit elements |

| DE102004021233A1 (de) * | 2004-04-30 | 2005-12-01 | Osram Opto Semiconductors Gmbh | Leuchtdiodenanordnung |

| US20060035036A1 (en) * | 2004-08-16 | 2006-02-16 | Telephus Inc. | Anisotropic conductive adhesive for fine pitch and COG packaged LCD module |

| DE102004050371A1 (de) * | 2004-09-30 | 2006-04-13 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement mit einer drahtlosen Kontaktierung |

| TWI277222B (en) * | 2004-10-29 | 2007-03-21 | Lighthouse Technology Co Ltd | LED module and method of packing the same |

| US20060124953A1 (en) * | 2004-12-14 | 2006-06-15 | Negley Gerald H | Semiconductor light emitting device mounting substrates and packages including cavities and cover plates, and methods of packaging same |

| US7563658B2 (en) * | 2004-12-27 | 2009-07-21 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US7821023B2 (en) * | 2005-01-10 | 2010-10-26 | Cree, Inc. | Solid state lighting component |

| EP2259318A3 (en) * | 2005-02-04 | 2014-01-08 | Seoul Opto Device Co., Ltd. | Light emitting device having a plurality of light emitting cells and method of fabricating the same |

| KR101047683B1 (ko) * | 2005-05-17 | 2011-07-08 | 엘지이노텍 주식회사 | 와이어 본딩이 불필요한 발광소자 패키징 방법 |

| DE102006023123B4 (de) * | 2005-06-01 | 2011-01-13 | Infineon Technologies Ag | Abstandserfassungsradar für Fahrzeuge mit einem Halbleitermodul mit Komponenten für Höchstfrequenztechnik in Kunststoffgehäuse und Verfahren zur Herstellung eines Halbleitermoduls mit Komponenten für ein Abstandserfassungsradar für Fahrzeuge in einem Kunststoffgehäuse |

| JP2008544540A (ja) * | 2005-06-22 | 2008-12-04 | ソウル オプト デバイス カンパニー リミテッド | 発光素子及びその製造方法 |

| KR100599012B1 (ko) * | 2005-06-29 | 2006-07-12 | 서울옵토디바이스주식회사 | 열전도성 기판을 갖는 발광 다이오드 및 그것을 제조하는방법 |

| TWI285442B (en) * | 2005-08-29 | 2007-08-11 | Gigno Technology Co Ltd | Package structure of light emitting diode |

| US8039849B2 (en) * | 2005-11-23 | 2011-10-18 | Taiwan Oasis Technology Co., Ltd. | LED module |

| JP2007158262A (ja) * | 2005-12-08 | 2007-06-21 | Rohm Co Ltd | 半導体発光素子の製造方法 |

| TWI331406B (en) * | 2005-12-14 | 2010-10-01 | Advanced Optoelectronic Tech | Single chip with multi-led |

| US20070263408A1 (en) * | 2006-05-09 | 2007-11-15 | Chua Janet Bee Y | Backlight module and method of making the module |

| US20100224890A1 (en) * | 2006-09-18 | 2010-09-09 | Cree, Inc. | Light emitting diode chip with electrical insulation element |

| WO2008038910A1 (en) * | 2006-09-25 | 2008-04-03 | Seoul Opto Device Co., Ltd. | Light emitting diode having alingap active layer and method of fabricating the same |

| US7781781B2 (en) * | 2006-11-17 | 2010-08-24 | International Business Machines Corporation | CMOS imager array with recessed dielectric |

| US20080117619A1 (en) * | 2006-11-21 | 2008-05-22 | Siew It Pang | Light source utilizing a flexible circuit carrier and flexible reflectors |

| DE102007009351A1 (de) * | 2007-02-23 | 2008-08-28 | Noctron Holding S.A. | Leuchtmittel |

| DE102007011123A1 (de) | 2007-03-07 | 2008-09-11 | Osram Opto Semiconductors Gmbh | Licht emittierendes Modul und Herstellungsverfahren für ein Licht emittierendes Modul |

| US8058669B2 (en) * | 2008-08-28 | 2011-11-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Light-emitting diode integration scheme |

| US8169540B2 (en) * | 2008-09-10 | 2012-05-01 | Panasonic Corporation | Compact camera body to which interchangeable lens unit is mountable |

-

2008

- 2008-09-26 DE DE102008049188A patent/DE102008049188A1/de not_active Withdrawn

-

2009

- 2009-08-25 CN CN2009801381690A patent/CN102165588B/zh active Active

- 2009-08-25 EP EP09740632.6A patent/EP2297780B1/de active Active

- 2009-08-25 KR KR1020117009227A patent/KR20110057263A/ko not_active Application Discontinuation

- 2009-08-25 WO PCT/DE2009/001217 patent/WO2010034278A1/de active Application Filing

- 2009-08-25 US US13/121,128 patent/US8461604B2/en active Active

- 2009-08-25 JP JP2011528181A patent/JP2012503866A/ja active Pending

- 2009-09-24 TW TW098132250A patent/TWI438888B/zh active

-

2013

- 2013-06-06 US US13/911,798 patent/US20140030829A1/en not_active Abandoned

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55120081A (en) * | 1979-03-08 | 1980-09-16 | Tokyo Shibaura Electric Co | Led display unit |

| JPS575356A (en) * | 1980-06-13 | 1982-01-12 | Toshiba Corp | Hybrid integrated circuit device |

| JPH038384U (ja) * | 1989-06-12 | 1991-01-25 | ||

| JPH04131958U (ja) * | 1991-05-28 | 1992-12-04 | 三洋電機株式会社 | 発光ダイオード表示装置 |

| JPH0832112A (ja) * | 1994-07-20 | 1996-02-02 | Toyoda Gosei Co Ltd | 3族窒化物半導体発光素子 |

| JP2004172578A (ja) * | 2002-09-02 | 2004-06-17 | Matsushita Electric Ind Co Ltd | 発光装置 |

| JP2007517378A (ja) * | 2003-12-24 | 2007-06-28 | 松下電器産業株式会社 | 半導体発光装置、照明モジュール、照明装置、表示素子、および半導体発光装置の製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013539604A (ja) * | 2010-09-07 | 2013-10-24 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツング | オプトエレクトロニクス半導体部品の製造方法 |

| US9224931B2 (en) | 2010-09-07 | 2015-12-29 | Osram Opto Semiconductors Gmbh | Method for producing an optoelectronic semiconductor component |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI438888B (zh) | 2014-05-21 |

| TW201019458A (en) | 2010-05-16 |

| CN102165588B (zh) | 2013-09-25 |

| EP2297780A1 (de) | 2011-03-23 |

| US20140030829A1 (en) | 2014-01-30 |

| DE102008049188A1 (de) | 2010-04-01 |

| US8461604B2 (en) | 2013-06-11 |

| EP2297780B1 (de) | 2019-06-12 |

| WO2010034278A1 (de) | 2010-04-01 |

| KR20110057263A (ko) | 2011-05-31 |

| US20110309377A1 (en) | 2011-12-22 |

| CN102165588A (zh) | 2011-08-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012503866A (ja) | キャリア基板および複数の放射放出半導体部品を備えたオプトエレクトロニクスモジュール、およびその製造方法 | |

| EP3454372B1 (en) | Light emitting diode | |

| KR101546929B1 (ko) | 발광 다이오드 및 그것을 갖는 발광 다이오드 모듈 | |

| JP5550550B2 (ja) | 複数のオプトエレクトロニクスコンポーネントを製造する方法およびオプトエレクトロニクスコンポーネント | |

| US8791548B2 (en) | Optoelectronic semiconductor chip, optoelectronic component and a method for producing an optoelectronic component | |

| US8513682B2 (en) | Optoelectronic component and production method for an optoelectronic component | |

| US10629790B2 (en) | Light-emitting device | |

| JP2006245032A (ja) | 発光装置およびledランプ | |

| JP2006086469A (ja) | 半導体発光装置、照明モジュール、照明装置及び半導体発光装置の製造方法 | |

| JP2010505252A (ja) | 発光ダイオード装置及びその作製方法 | |

| JP2010505252A5 (ja) | ||

| JP5568476B2 (ja) | オプトエレクトロニクス部品 | |

| US9831379B2 (en) | Method of manufacturing light emitting device | |

| US9543479B2 (en) | Method for producing an optoelectronic component and optoelectronic component produced in such a way | |

| JP2018510508A (ja) | オプトエレクトロニクス半導体チップ、オプトエレクトロニクス半導体部品及びオプトエレクトロニクス半導体チップの生産方法 | |

| JP4894354B2 (ja) | 発光装置 | |

| US20170331019A1 (en) | Optoelectronic semiconductor component and method of producing an optoelectronic semiconductor component | |

| US9029902B2 (en) | Optoelectronic semiconductor device comprising a semiconductor chip, a carrier substrate and a film | |

| KR20130062985A (ko) | 복사 방출 소자 및 복사 방출 소자의 제조 방법 | |

| CN102484186B (zh) | 具有带有辐射出射侧和绝缘层的至少一个第一半导体本体的光电子模块及其制造方法 | |

| TW201123540A (en) | Optoelectronic component with a semiconductor body, an insulation layer and a planar conductive structure and method for its production | |

| US11424226B2 (en) | Light-emitting device and method for producing a plurality of light-emitting devices | |

| KR102149911B1 (ko) | 발광 다이오드 및 그것을 갖는 발광 다이오드 모듈 | |

| US20210376212A1 (en) | Semiconductor light emitting device and method of manufacturing the same | |

| GB2551154B (en) | Light-emitting diode package and method of manufacture |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120824 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120824 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131029 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131105 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140122 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140129 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140502 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141014 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20150106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150409 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150512 |