KR20110057263A - 캐리어 기판 및 복수 개의 복사 방출 반도체 소자를 포함한 광전 모듈 및 그 제조 방법 - Google Patents

캐리어 기판 및 복수 개의 복사 방출 반도체 소자를 포함한 광전 모듈 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20110057263A KR20110057263A KR1020117009227A KR20117009227A KR20110057263A KR 20110057263 A KR20110057263 A KR 20110057263A KR 1020117009227 A KR1020117009227 A KR 1020117009227A KR 20117009227 A KR20117009227 A KR 20117009227A KR 20110057263 A KR20110057263 A KR 20110057263A

- Authority

- KR

- South Korea

- Prior art keywords

- emitting semiconductor

- radiation emitting

- radiation

- contact surface

- carrier substrate

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 233

- 239000000758 substrate Substances 0.000 title claims abstract description 87

- 238000000034 method Methods 0.000 title claims abstract description 49

- 230000005693 optoelectronics Effects 0.000 title claims abstract 3

- 238000004519 manufacturing process Methods 0.000 title claims description 15

- 230000005855 radiation Effects 0.000 claims abstract description 218

- 238000010292 electrical insulation Methods 0.000 claims abstract description 25

- 230000005670 electromagnetic radiation Effects 0.000 claims abstract description 7

- 238000006243 chemical reaction Methods 0.000 claims description 27

- 239000004020 conductor Substances 0.000 claims description 21

- 238000007639 printing Methods 0.000 claims description 7

- 238000007740 vapor deposition Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 145

- 230000015572 biosynthetic process Effects 0.000 description 17

- 238000005755 formation reaction Methods 0.000 description 17

- 239000010408 film Substances 0.000 description 15

- 239000002184 metal Substances 0.000 description 13

- 229910052751 metal Inorganic materials 0.000 description 13

- 230000003287 optical effect Effects 0.000 description 10

- 239000000463 material Substances 0.000 description 5

- 239000012777 electrically insulating material Substances 0.000 description 4

- 230000007613 environmental effect Effects 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- 239000004922 lacquer Substances 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000007649 pad printing Methods 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 230000035939 shock Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000012938 design process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000013139 quantization Methods 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24105—Connecting bonding areas at different heights

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/24137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/241—Disposition

- H01L2224/24151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/24221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/24225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/24226—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the HDI interconnect connecting to the same level of the item at which the semiconductor or solid-state body is mounted, e.g. the item being planar

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

- H01L2224/2499—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids

- H01L2224/24996—Auxiliary members for HDI interconnects, e.g. spacers, alignment aids being formed on an item to be connected not being a semiconductor or solid-state body

- H01L2224/24998—Reinforcing structures, e.g. ramp-like support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

- H01L2924/12036—PN diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Led Device Packages (AREA)

Abstract

광전 모듈이 제공되고, 상기 광전 모듈은 캐리어 기판(1) 및 복수 개의 복사 방출 반도체 소자들(2)을 포함한다. 캐리어 기판(1)은 구조화된 도전로들을 포함한다. 복사 방출 반도체 소자들(2)은 각각 전자기 복사의 생성에 적합한 활성층(2a), 제1접촉면(21) 및 제2접촉면(22)을 포함하고, 이때 상기 제1접촉면(21)은 각각 상기 캐리어 기판(1)과 반대 방향을 향해 있는 복사 방출 반도체 소자들(2)의 측에 배치된다. 복사 방출 반도체 소자들(2)은 전기 절연층(4)을 구비하고, 상기 전기 절연층은 각각 상기 제1접촉면(21)의 영역에서 리세스를 포함한다. 전기 절연층(4)상에 국부적으로 도전 구조체들(8)이 배치된다. 도전 구조체들(8) 중 하나는 적어도, 복사 방출 반도체 소자(2)의 제1접촉면(21)을 다른 복사 방출 반도체 소자(2)의 다른 제1접촉면(21)과 전기 전도적으로 연결하거나, 상기 캐리어 기판(1)의 도전로와 전기 전도적으로 연결한다. 또한, 이러한 모듈의 제조 방법이 제공된다.

Description

본 특허 출원은 독일 특허 출원 10 2008 049188.8의 우선권을 청구하고, 그 공개 내용은 참조로 포함된다.

본 발명은 캐리어 기판 및 복수 개의 복사 방출 반도체 소자들을 포함한 광전 모듈에 관한 것이다. 또한, 본 발명은 광전 모듈의 제조 방법에 관한 것이기도 하다.

종래의 광전 모듈의 경우 칩과 캐리어 사이의 전기 접촉 기술로서 주로 와이어본딩, 납땜 또는 도전 접착제를 이용한 칩 실장이 사용되어 왔다. 이러한 방식으로, 예를 들면 조명 모듈을 위한 LED 어레이가 생성된다. 초소형 추세에 따라 항상 더 작은 치수의 모듈, 예를 들면 모듈 높이 및/또는 모듈의 밑면에 있어 더 작은 치수가 필요하다.

LED를 위한 초소형 구조 및 결합 기술은 공개 문헌 DE 10 353 679 A1에 공지되어 있다. 이때의 소자는 캐리어 및 그 위에 배치된 반도체칩을 포함하고, 상기 반도체칩은 평면으로 접촉되어 있다.

평면 접촉된 반도체칩을 포함하는 모듈은 소자의 높이가 작다는 이점이 있어서, 바람직하게는 반도체칩의 광 출사면과 기존의 광학 소자들 사이의 간격이 최소로 얻어질 수 있다. 그러나, 평면 접촉에 의해 모듈의 밑면이 즉각적으로 감소하진 않는데, 반도체칩의 전기 접촉을 위해 역할하며 캐리어상에 배치되는 도전 구조체들은 전기 절연 상태로 모듈안에 통합되어야 하기 때문이다.

특히, 복수 개의 복사 방출 반도체 소자들을 포함하는 모듈의 경우 캐리어 기판상에 광전 소자들이 콤팩트하게 배치되는 것이 필요하다.

본 발명의 과제는 광전 모듈을 제공하되 특히 설계 높이가 작으면서도 그와 동시에 복수 개의 복사 방출 반도체 소자들이 콤팩트하게 배치되어 있는 광전 모듈을 제공하는 것이다.

이러한 과제는 특허청구범위 제1항의 특징을 포한한 광전 모듈 및 특허청구범위 제11항의 특징을 포함한 그 제조 방법에 의하여 해결된다. 모듈 및 방법에 대한 유리한 실시예 및 바람직한 발전예는 종속항들의 주제이다.

본 발명에 따르면, 캐리어 기판 및 복수 개의 복사 방출 반도체 소자들을 포함한 광전 모듈이 제공된다. 캐리어 기판은 복사 방출 반도체 소자들의 전기 접촉을 위해 구조화된 도전로들을 포함한다. 복사 방출 반도체 소자들은 각각 전자기 복사의 생성을 위해 적합한 활성층, 제1접촉면 및 제2접촉면을 포함하고, 이때 제1접촉면은 각각 캐리어 기판과 반대 방향을 향해 있는 복사 방출 반도체 소자들의 측에 배치된다. 복사 방출 반도체 소자들은 전기 절연층을 구비하고, 전기 절연층은 각각 복사 방출 반도체 소자의 제1접촉면의 영역에서 리세스(recess)를 포함한다. 전기 절연층상에 국부적으로 도전 구조체들이 배치된다. 도전 구조체들 중 하나는 적어도, 복사 방출 반도체 소자의 제1접촉면을 다른 복사 방출 반도체 소자의 다른 제1접촉면과 전기 전도적으로 연결하거나, 캐리어 기판의 도전로와 전기 전도적으로 연결한다.

복사 방출 반도체 소자의 전기 접촉은 캐리어 기판과 이격되어 안내되는 와이어에 의해 이루어지지 않고, 적어도 부분적으로 전기 절연층상에 안내되는 도전 구조체에 의해 이루어진다. 이러한 방식의 전기 접촉에 의해 매우 낮은 설계 높이를 가진 모듈이 얻어져서 유리하다. 또한, 복사 방출 반도체 소자들을 상호간에 전기 전도적으로 연결하거나 캐리어 기판의 도전로와 전기 전도적으로 연결하는 도전 구조체에 의해 콤팩트한 모듈이 제공될 수 있다. 그러므로, 모듈의 복사 방출 반도체 소자들은 공간 절약적 방식으로 캐리어 기판상에 배치될 수 있다. 모듈의 밑면도 축소한다는 이점이 있다.

또한, 도전 구조체가 복사 방출 반도체 소자들에 근접하여 배치될 수 있다. 이러한 방식의 복사 방출 반도체 소자들 접촉에 의해, 매우 낮은 설계 높이를 가진 모듈이 얻어지고, 이러한 설계 높이에 의해 특히 예를 들면 광학 부재들이 복사 방출 반도체 소자들에 근접하여 배치될 수 있으므로 유리하다.

광학 부재들이란 예를 들면 렌즈를 의미할 수 있다. 특히, 광학 부재들이란 반도체 소자로부터 방출된 복사에 대해 목적한 바에 따라 영향을 미치고, 특히 방출 특성을 변경하는 부재들을 의미한다.

복사 방출 반도체 소자는 바람직하게는 반도체칩, 더욱 바람직하게는 광 방출 다이오드(LED)이다.

복사 방출 반도체 소자는 각각 활성층을 포함한다. 활성층은 복사 생성을 위해 각각 pn 접합, 이중이종구조, 단일양자우물구조(SQW, single quantum well) 또는 다중양자우물구조(MQW, multi quantum well)를 포함한다. 양자우물구조란 명칭은 양자화의 차원성에 대한 의미를 전개하진 않는다. 상기 명칭은 특히 양자상자, 양자선, 양자점 및 이들 구조들의 각 조합을 포괄한다.

바람직하게는, 복사 방출 반도체 소자들은 각각 질화물-, 인화물- 또는 비화물 화합물 반도체계이다. 이와 관련하여 "질화물-, 인화물- 또는 비화물 화합물 반도체계"란, 활성 에피택시층 시퀀스 또는 그 중 적어도 하나의 층이 각각 0≤x≤1, 0≤y≤1, x+y≤1일 때 InxGayAl1-x-yP, InxGayAl1-x-yN 또는 InxGayAl1-x-yAs 라는 조성을 가지는 III/V 반도체 물질을 포함한다는 것을 의미한다.

바람직한 형성예에서, 복사 방출 반도체 소자는 각각 박막 반도체 소자로서 형성된다. 본 출원의 틀에서 박막 반도체 소자란, 상기 소자의 제조 동안에 반도체층 시퀀스가 예를 들면 에피택시얼 방식으로 성장되었던 성장 기판이 분리되어 있는 반도체 소자를 가리킨다. 이때 상기 반도체층 시퀀스는 박막 반도체 소자의 반도체 몸체를 포함한다. 복사 방출 반도체 소자는 각각 캐리어 기판과 결합되고, 상기 캐리어 기판은 반도체 소자의 반도체층 시퀀스를 위한 성장 기판과는 상이하다.

캐리어 기판은 가령 결정 구조와 관련하여 성장 기판이 충족해야 하는 것과 같은 요건이 비교적 까다롭지 않아 유리하다. 성장 기판의 물질을 선택할 때보다 캐리어 기판의 물질을 선택할 때 더 많은 물질이 가능하다.

바람직하게는, 전기 절연층은 복사 방출 반도체 소자의 활성층으로부터 방출된 복사에 대하여 적어도 부분적으로 복사 투과성이다. 복사 방출 반도체 소자들로부터 방출된 복사는 전기 절연층을 통해 아웃커플링될 수 있고, 이때 현저한 광학적 손실은 없다. 유리하게도, 활성층으로부터 방출된 복사가 전기 절연층에서 흡수되는 경우가 줄어들 수 있어서, 모듈의 효율이 증가한다는 이점이 있다. 바람직하게는, 활성층으로부터 방출된 복사 방출 반도체 소자의 복사가 전기 절연층에서 흡수되는 것은 40%미만, 더욱 바람직하게는 20% 미만이다.

바람직하게는, 전기 절연층은 필름, 래커 또는 폴리머층이다.

바람직한 형성예에서, 전기 절연층은 적어도 하나의 변환 부재를 포함한다. 가령 YAG:Ce 분말과 같은 적합한 변환 부재는 예를 들면 WO 98/12757 에 기술되어 있고, 그 내용은 참조로 포함된다.

바람직하게는, 복사 방출 반도체 소자들은 각각 파장(λ0)을 가진 1차 복사를 방출한다. 바람직하게는, 전기 절연층의 변환 부재는 파장(λ0)의 복사를 적어도 부분적으로 흡수하고, 다른 파장 영역에서 2차 복사를 방출한다. 이를 통해 모듈은 혼합 복사를 방출하며, 상기 혼합 복사는 복사 방출 반도체 소자의 1차 복사 및 변환 부재의 2차 복사를 포함한다.

변환 부재를 목적에 따라 선택함으로써, 복사 방출 반도체 소자로부터 방출도니 복사의 색 위치가 변경될 수 있다. 이를 통해, 유리하게도, 모듈로부터 방출된 복사의 원하는 색 위치가 달성될 수 있다.

이하에서 색 위치란, CIE 색 공간에서 모듈의 방출된 광의 색을 나타내는 수치값을 의미한다.

또는, 전기 절연층은 2개 이상의 변환 부재를 포함할 수 있다. 이를 통해, 모듈로부터 방출된 복사는 혼합 복사로 얻어지는데, 상기 혼합 복사는 1차 복사 및 복수 개의 변환 부재들의 복수 개의 2차 복사를 포함한다. 2개 이상의 변환 부재를 사용함으로써, 색 위치의 색 선택이 정확해진다는 이점이 있어, 모듈의 방출된 복사의 색 위치가 원하는 대로 얻어진다.

덧붙여 말하자면, 복사 방출 반도체 소자가 각각 동일한 파장 영역에서 1차 복사를 반드시 방출할 필요는 없다. 오히려, 복사 방출 반도체 소자는, 상기 소자가 적어도 부분적으로 서로 다른 파장 영역에서 복사를 방출하도록 형성될 수 있다. 반도체 소자들로부터 방출된 복사가 겹침으로써, 모듈로부터 방출된 혼합 복사가 발생할 수 있고, 이러한 혼합 복사는 CIE 색 공간의 백색의 색 영역에 위치하는 것이 바람직하다.

바람직한 형성예에서, 개별 복사 방출 반도체 소자들 사이에는 평탄화층이 적어도 배치된다.

평탄화층에 의해, 캐리어 기판과 반대 방향인 모듈의 표면이 평활하게 얻어질 수 있어 유리하다. 바람직하게는, 전기 절연층은 이러한 평활한 표면상에 배치된다. 더욱 바람직하게는, 평탄화층은 전기 절연성이다.

모듈의 일 형성예에서, 평탄화층은 적어도 하나의 변환 부재를 포함한다. 더욱 바람직하게는, 변환 부재는 복사 방출 반도체 소자들 중 적어도 하나로부터 방출된 복사를 흡수하고, 이러한 복사를 다른 파장의 복사로 변환하여, 모듈로부터 방출된 복사가 혼합 복사로서 생성된다.

변환 부재 또는 변환 부재들이 전기 절연층 및/또는 평탄화층에 직접적으로 통합됨으로써, 유리하게는 다른 광학층들이 필요하지 않다. 광학층들은 특히, 복사 방출 반도체 소자들로부터 방출된 복사의 색 위치를 목적에 맞게 변경하거나/변경하고 보정하는 층들이다. 변환 부재가 전기 절연층 및/또는 평탄화층에 통합되고, 복사 방출 반도체 소자가 바람직하게는 평탄화층 및/또는 전기 절연층에 의해 직접적으로 둘러싸임으로써, 유리하게는 복사 방출 반도체 소자로부터 방출된 복사가 복사 방출 반도체 소자에서 거의 변환된다. 이를 통해 유리하게도 콤팩트한 모듈이 가능하다.

이 경우, 전기 절연층은 광 변환층의 기능, 도전 구조체를 위한 캐리어층의 기능 및 복사 방출 소자를 위한 보호층의 기능을 가질 수 있다.

바람직한 모듈의 형성예에서, 복사 방출 반도체 소자들은 캐리어 기판상에 배치된 프레임에 의해 함께 둘러싸인다.

바람직하게는, 프레임은 세라믹 또는 플라스틱을 포함한다. 프레임을 이용하면, 복사 방출 반도체 소자는 주면 매질로부터 공간적으로 분리된다. 또한, 프레임은 복사 방출 반도체 소자를 예를 들면 환경 영향으로부터 보호하여 유리하다. 환경 영향은 예를 들면 충격 또는 침습이 있다.

모듈의 바람직한 형성예에서, 캐리어 기판은 연성 기판이다.

따라서, 캐리어 기판이 반드시 경성으로 형성될 필요는 없다. 특히, 캐리어 기판은 필름으로 형성될 수 있다.

모듈의 바람직한 형성예에서, 캐리어 기판에서 복사 방출 반도체 소자가 배치된 표면은 평활하지 않다.

캐리어 기판은 예를 들면 아치 곡면을 포함할 수 있다. 특히, 복사 방출 반도체 소자가 캐리어 기판의 표면 중 하나에 실장될 수 있는 경우에 한하여, 캐리어 기판의 표면은 다른 형상을 가질 수 있다.

모듈의 바람직한 형성예에서, 도전 구조체들은 이방성 층으로 형성되고, 상기 이방성층은 전기 절연층상에 배치되며, 각각의 복사 방출 반도체 소자의 제1접촉면의 영역에서 전기 전도 영역들을 적어도 포함한다.

이방성 필름은 부분적으로, 도전 영역들을 포함한다. 전도도는 예를 들면 국부적으로 인가된 압력 또는 조사에 의해 발생할 수 있다. 이방성 필름의 도전 영역들에 의해, 각각 복사 방출 반도체 소자의 전기적 연결이 보장된다.

바람직하게는, 이방성 필름은 적어도 부분적으로, 반도체 소자로부터 방출된 복사에 대하여 복사 투과성이다. 특히, 이방성 필름은, 더욱 바람직하게는 반도체 소자로부터 방출된 복사에 대해 일부 영역들에서 적어도 부분적으로 복사 투과성이며, 이러한 영역은 전도도가 없다.

또는, 이방성 필름은 국부적으로 제거될 수 있다. 특히, 이 경우, 이방성 필름은 바람직하게는 복사 방출 반도체 소자의 복사 출사측의 영역에서 제거된다.

모듈의 바람직한 형성예에서, 전기 절연층은 구조화된 도체판 및 도전 구조체들에 의해, 상기 도체판으로부터 돌출한 전기 전도 웹(web)을 이용하여 형성된다.

바람직하게는, 웹들은 각각 도체판의 도전로의 접촉 지점으로부터 복사 방출 반도체 소자의 제1접촉면까지 이어진다. 이때, 바람직하게는, 웹은 각각, 상기 웹이 상기 도체판으로부터 멀어지면서 반도체 소자의 방향으로 가며 굴곡지도록 형성된다. 바람직하게는, 도체판은 리세스를 포함하고, 더욱 바람직하게는 상기 리세스는 각각 복사 방출 반도체 소자의 제1접촉면 상부에 배치된다. 바람직하게는, 웹은 금속웹이다.

바람직하게는, 도체판은 도전로들을 포함한다. 도체판의 도전로는 각각 바람직하게는 전기적으로 서로 절연되어 배치된다. 더욱 바람직하게는, 이러한 전기적 절연은 리세스에 의해 이루어지며, 상기 리세스는 도체판의 도전로들사이의 간격을 이룬다.

모듈의 이러한 형성예에서, 복수 개의 도체판들은 포개어져 배치될 수 있어서, 다겹의 배열이 형성된다. 이를 통해, 유리하게는 모듈의 복수 개의 회로면이 가능하고, 따라서 모듈에서 회로 집적도가 더 높게 달성되어 유리하다.

모듈의 또 다른 바람직한 형성예에서, 전기 절연층은 각각 국부적으로, 각 복사 방출 반도체 소자의 측면에서 각각의 복사 방출 반도체 소자의 둘레에 이어진다. 각각, 복사 방출 반도체 소자의 제1접촉면은 전기 절연층상에서 이어짐으로써, 각각 캐리어 기판과 반대 방향을 향해 있는 복사 방출 반도체 소자의 표면은 제1접촉면을 포함하지 않는다.

제1접촉층이 이와 같이 이어짐으로써, 복사 방출 반도체 소자의 전원 공급이 균일하게 보장된다. 또한, 제1접촉층의 임의의 영역들에 복사 방출 반도체 소자의 외부 전기 연결부가 배치될 수 있다.

바람직하게는, 전기 절연층은 반도체 소자의 측면에서 반도체 소자의 활성층을 경유한다.

이와 같이 이어지는 반도체 소자의 제1접촉면에 의해, 반도체 소자의 전기적 연결 또는 반도체 소자들간의 복합 회로 형성이 가능하다. 이를 통해, 캐리어 기판상에 반도체 소자들이 공간 절약적으로 배치될 수 있어 유리하다.

본 발명에 따른 광전 모듈의 제조 방법은 특히 이하의 단계를 포함한다:

a) 캐리어기판상에 복수 개의 복사 방출 반도체 소자들을 배치하되, 이때 캐리어 기판은 복사 방출 반도체 소자의 전기 접촉을 위해 구조화된 도전로들을 포함하며, 상기 복사 방출 반도체 소자들은 각각 전자기 복사의 생성을 위해 적합한 활성층, 제1접촉면 및 제2접촉면을 포함하고, 이때 각각 제1접촉면은 복사 방출 반도체 소자에서 상기 캐리어 기판과 반대 방향을 향하는 측에 배치되도록 하는 단계;

b) 복사 방출 반도체 소자상에 전기 절연층을 적층되는 단계로, 이때 전기 절연층은 각각의 복사 방출 반도체 소자의 제1접촉면의 영역에서 각각 리세스를 포함하도록 하는 단계, 그리고

c) 상기 전기 절연층의 부분 영역들상에 도전 구조체들이 적층되는 단계로, 이때 도전 구조체들 중 하나는 적어도, 복사 방출 반도체 소자의 제1접촉면을 다른 복사 방출 반도체 소자의 다른 제1접촉면과 전기 전도적으로 연결하거나, 캐리어 기판의 도전로와 전기 전도적으로 연결하는 단계.

방법의 유리한 형성예는 모듈의 유리한 형성예와 유사하게 얻어지며, 그 반대의 경우도 그러하다.

반도체 소자가 평면 도전 구조체들에 의해 전기 접촉됨으로써, 유리하게도 모듈의 높이가 최소화된다. 이와 동시에, 유리하게는 모듈의 밑면이 비교적 종래의 모듈보다 작아진다.

전기 절연층이 사용되고, 상기 전기 절연층상에 반도체 소자의 전기 접촉을 위한 도전 구조체들이 안내됨으로써, 유리하게도 모듈의 설계 공정이 간단해진다. 유리하게는, 반도체 소자의 회로, 반도체 소자의 봉지 및 경우에 따라서 광 변환이 각각 코팅 공정을 이용하여 이루어진다. 상기 광 변환은 바람직하게는 전기 절연층에 통합된 변환 부재에 의해 이루어진다.

방법의 바람직한 형성예에서, 도전 구조체들은 압력 방법을 이용하여 적층된다.

바람직하게는, 도전 구조체들은 스크린 인쇄 방법, 스텐실 인쇄(stencil printing) 방법 또는 패드 인쇄 방법을 이용하여 전기 절연층상에 적층된다.

또는, 도전 구조체들은 기상 증착을 이용하여 적층될 수 있다.

이때, 도전 구조체들은 물리 기상 증착(PVD 공정) 또는 화학 기상 증착(CVD 공정)을 이용하여 적층될 수 있다.

더욱 바람직하게는, 도전 구조체들은 국부적으로 적층된다. 바람직하게는, 인쇄, 분사 또는 마스크 기술과 연계된, 특히 스텐실과 연계된 PVD/CVD를 이용하여 도전 구조체들이 선택적으로 적층된다.

도전 구조체들의 적층을 위한 다른 가능성은 전기 절연층상에 도전로들이 직접 인쇄되는 것이다.

다른 바람직한 형성예에서, 도전 구조체들은 이방성층을 이용하여 형성되고, 상기 이방성층은 전기 절연층상에 배치되고, 각각의 복사 방출 반도체 소자의 제1접촉면의 영역에서 전기 전도적으로 적어도 형성된다.

바람직하게는, 이방성층의 전기 전도 영역들이 형성되는 것은 인쇄 방법, 온도 방법, 또는 예를 들면 UV 레이저를 이용한 조사 방법을 이용한다.

또는, 도전 구조체들은 필름안에 통합될 수 있고, 상기 필름은 전기 절연 필름상에 라미네이팅된다. 이 경우, 라미네이팅된 필름은 도전 구조체들, 예를 들면 금속배선을 포함한다. 이러한 도전 구조체들은 바람직하게는 이미 필름안에 배치되어, 복사 방출 반도체 소자의 전기 접촉이 소정의 방식으로 가능하다. 더욱 바람직하게는, 자동화된 접촉 방법이 사용될 수 있다(TAB 방법: tape automated bonding).

방법의 바람직한 형성예에서, 전기 절연층의 적층 이전에 평탄화층이 적어도, 복사 방출 반도체 소자들 사이의 간극에 삽입된다. 이러한 방식으로, 모듈이 평탄화되어, 캐리어 기판과 반대 방향을 향해 있는 모듈의 표면이 평활하게 형성된다.

방법의 다른 바람직한 형성예에서, 도전 구조체들은 각각 전기 전도 웹으로서 형성되고, 이때 상기 웹은 각각 스템핑 웨지(stamping wedge) 공정을 이용하여 복사 방출 반도체 소자의 제1접촉면과 전기 전도적으로 연결된다.

광전 모듈 및 그 제조 방법의 다른 특징, 이점, 바람직한 형성예 및 합목적성은 이하에서 도 1 내지 도 9와 관련하여 설명한 실시예로부터 도출된다.

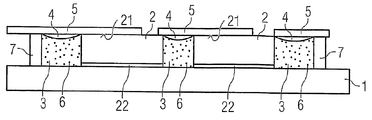

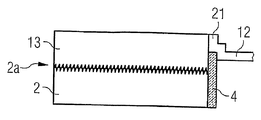

도 1은 제조 방법의 중간 단계에서 모듈의 제1실시예에 대한 개략적 횡단면도를 도시한다.

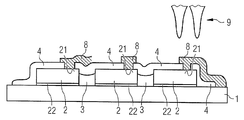

도 2는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 횡단면도를 도시한다.

도 3은 본 발명에 따른 모듈의 실시예에 대한 개략적 횡단면도를 도시한다.

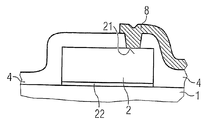

도 4는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

도 5는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

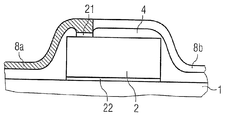

도 6은 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 횡단면도를 도시한다.

도 7a는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

도 7b는 도 7a의 실시예의 일부분에 대한 개략적 평면도를 도시한다.

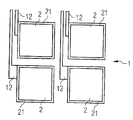

도 7c는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 평면도를 도시한다.

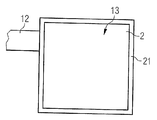

도 2는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 횡단면도를 도시한다.

도 3은 본 발명에 따른 모듈의 실시예에 대한 개략적 횡단면도를 도시한다.

도 4는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

도 5는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

도 6은 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 횡단면도를 도시한다.

도 7a는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 부분도를 도시한다.

도 7b는 도 7a의 실시예의 일부분에 대한 개략적 평면도를 도시한다.

도 7c는 본 발명에 따른 모듈의 다른 실시예에 대한 개략적 평면도를 도시한다.

동일하거나 동일한 기능의 구성요소는 각각 동일한 참조번호를 가진다. 도시된 구성요소들 및 그 구성요소들간의 크기비는 정확한 치수로 볼 수 없다.

도 1에는 광전 모듈이 도시되어 있고, 광전 모듈은 캐리어 기판(1) 및 복수 개의 복사 방출 반도체 소자들(2)을 포함한다. 복사 방출 반도체 소자들(2)은 각각 전자기 복사의 생성을 위한 활성층, 제1접촉면(21) 및 제2접촉면(22)을 포함한다. 제1접촉면(21)은 캐리어 기판(1)과 반대 방향을 향해 있는 복사 방출 반도체 소자(2)의 표면에 배치된다.

복사 방출 반도체 소자(2)는 바람직하게는 반도체칩으로서 형성되고, 더욱 바람직하게는 각각 광 방출 다이오드(LED)로서 형성된다.

복사 방출 반도체 소자(2)의 활성층은 각각 복사 생성을 위해 각각 pn 접합, 이중이종구조, 단일양자우물구조 또는 다중양자우물구조를 포함한다. 바람직하게는, 복사 방출 반도체 소자(2)는 각각 질화물-, 인화물 - 또는 비화물 화합물 반도체계이다.

캐리어 기판(1)은 복사 방출 반도체 소자(2)의 전기 접촉을 위해 구조화된 도전로들을 포함한다. 특히, 바람직하게는, 각각 하나의 복사 방출 반도체 소자(2)가 캐리어 기판(1)의 도전로상에 배치된다. 이는, 각각 제2접촉면(22)이 캐리어 기판(1)의 도전로와 기계적 및 전기적으로 접촉하고 있음을 의미한다.

바람직하게는, 각각 하나의 복사 방출 반도체 소자(2)가 배치된 도전로들은 전기적으로 서로 절연된다. 복사 방출 반도체 소자(2)는 캐리어 기판(1)의 도전로들상에 전기적으로 서로 절연되어 배치된다.

바람직하게는, 개별 복사 방출 반도체 소자들(2) 사이에 평탄화층(3)이 배치된다. 평탄화층(3)에 의해, 유리하게는 캐리어 기판(1)과 반대 방향을 향해 있는 모듈의 표면이 평활하게 생성될 수 있다. 바람직하게는, 평탄화층(3)은 전기 절연성이고, 더욱 바람직하게는, 평탄화층(3)은 유전체 물질을 함유한다.

바람직하게는, 평탄화층(3)은 실리콘계이다. 특히, 평탄화층(3)은 실리콘을 함유한다. 부가적 또는 대안적으로, 평탄화층(3)은 다른 폴리머 또는 무기 물질을 함유할 수 있다.

평탄화층(3)의 높이는 복사 방출 반도체 소자(2)의 높이를 초과할 수 있다. 특히, 평탄화층(3)은 복사 방출 반도체 소자(2)의 높이를 초과하여 이어질 수 있어서, 상기 평탄화층은 적어도 부분적으로, 캐리어 기판(1)과 반대 방향인 복사 방출 반도체 소자(2)의 표면 상부에 연장된다. 이를 통해, 특히 복사 방출 반도체 소자(2)의 전기 절연성이 개선된다. 이 경우, 평탄화층(3)은 바람직하게는, 복사 방출 반도체 소자(2)로부터 방출된 복사에 대해 적어도 부분적으로 복사 투과성인 물질로 구성된다.

평탄화층(3)은 적어도 하나의 변환 부재(6)를 더 포함할 수 있다. 바람직하게는, 변환 부재(6)는 복사 방출 반도체 소자(2) 중 적어도 하나로부터 방출된 복사를 흡수하고 이러한 복사를 다른 파장 영역의 복사로 변환하여, 모듈로부터 방출된 복사가 혼합 복사로 생성된다.

변화 부재(6)가 목적에 맞게 선택됨으로써, 복사 방출 반도체 소자(2)로부터 방출된 복사의 색 위치가 변경될 수 있다. 이를 통해, 유리하게도, 모듈로부터 방출된 복사의 원하는 색 위치가 얻어질 수 있다. 더욱 바람직하게는, 모듈은 백색의 색 위치 영역에서 복사를 방출한다.

바람직하게는, 복사 방출 반도체 소자들(2)은 프레임(7)에 의해 함께 둘러싸이고, 프레임은 캐리어 기판(1)상에 배치된다.

바람직하게는, 프레임(7)은 세라믹 또는 플라스틱을 함유한다. 도 1의 실시예에서, 프레임(7)을 이용하여 복사 방출 반도체 소자(2) 및 평탄화층(3)은 공간적으로 주변으로부터 분리된다. 유리하게는, 프레임(7)은 복사 방출 반도체 소자(2)를 예를 들면 환경 영향으로부터 보호한다. 환경 영향이란 예를 들면 충격이 있다.

복사 방출 반도체 소자(2)상에, 그리고 평탄화층(3)상에 바람직하게는 적어도 부분적으로 전기 절연층(4)이 배치된다. 전기 절연층(4)은 각각 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에서 리세스를 포함한다.

바람직하게는, 전기 절연층(4)은 활성층으로부터 방출된 복사 방출 반도체 소자(2)의 복사에 대해 적어도 부분적으로 복사 투과성이다. 복사 방출 반도체 소자(2)로부터 방출된 복사는 전기 절연층(4)을 통해 아웃커플링될 수 있고, 이때 현저한 광학적 손실을 입지는 않는다.

복사 방출 반도체 소자(2)로부터 방출된 복사가 모듈로부터 아웃커플링되는 것은, 도 1 내지 7의 실시예에서 바람직하게는 캐리어 기판(1)과 반대 방향을 향해 있는 모듈의 측에서 이루어진다.

바람직하게는, 전기 절연층(4)은 필름, 래커 또는 폴리머층이다.

전기 절연층(4)은 평탄화층(3)과 마찬가지로 적어도 하나의 변환 부재를 포함할 수 있다(미도시). 전기 절연층에서 변환 부재는, 바람직하게는 복사 방출 반도체 소자(2)로부터 방출된 복사를 적어도 부분적으로 흡수하고, 다른 파장 영역에서 2차 복사를 방출한다. 이를 통해, 모듈은 혼합 복사를 방출하고, 상기 혼합 복사는 복사 방출 반도체 소자(2)의 1차복사 및 변환 부재의 2차 복사를 포함한다.

변환 부재 또는 변환 부재들이 직접적으로 전기 절연층(4) 및/또는 평탄화층(3)에 통합됨으로써, 유리하게는 다른 부가적 광학층들이 필요하지 않다. 광학층이란 예를 들면 반도체 소자로부터 방출된 복사의 색 위치를 목적에 맞게 변경하거나/변경하고 보정하는 층이다. 따라서, 유리하게는, 반도체 소자(2)로부터 방출된 복사가 반도체 소자(2)에서 거의 변환될 수 있다. 모듈은 콤팩트하게 얻어진다.

전기 절연층(4)은 국부적으로 리세스를 포함한다. 바람직하게는, 각각, 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에서 전기 절연층(4)안에 리세스가 형성된다.

바람직하게는, 전기 절연층(4)은 일체형으로 형성된다.

캐리어 기판(1)과 반대 방향을 향해 있는 모듈의 표면상에서, 국부적으로 전기 절연층(4)상에 도전 구조체들이 배치된다(미도시).

도 1의 실시예에서, 모듈은 도전 구조체들이 적층되기 이전의 상태로 도시되어 있다. 실시예(1)의 모듈은 제조 공정 중의 모듈을 나타낸다.

도 1의 실시예에서, 스텐실(5)은 캐리어 기판(1)과 반대 방향을 향해 있는 모듈의 측에 배치된다. 스텐실(5)은 도전 구조체들이 적층되는 제조 단계 중에 사용된다.

스텐실(5)은 도전 구조체들의 구조화를 위해 사용된다. 특히, 스텐실(5)은 바람직하게는 전기 절연층(4)의 리세스의 영역에서 리세스를 포함한다.

바람직하게는, 도전 구조체들은 인쇄 방법을 이용하여 전기 절연층(4) 또는 스텐실(5) 상에 적층된다. 인쇄 방법, 특히 스크린 인쇄 방법 또는 패드 인쇄 방법을 이용하여, 바람직하게는 한겹의 도전 구조체, 특히 금속배선층이 복사 방출 반도체 소자(2)의 회로 형성을 위한 목적으로 적층될 수 있다.

바람직하게는, 도전 구조체들의 구조화는 스텐실(5)을 통해 형성되어, 복사 방출 반도체 소자(2)가 도전 구조체들을 이용하여 소정의 방식으로 상호 간에 전기 전도적으로 연결되거나, 캐리어 몸체의 도전로들과 전기 전도적으로 연결된다. 따라서, 도전 구조체들은 적어도, 복사 방출 반도체 소자(2)의 제1접촉면을 다른 복사 방출 반도체 소자(2)의 다른 제1접촉면과 전기적으로 연결하거나, 캐리어 기판(1)의 도전로와 전기적으로 연결한다(미도시).

도전 구조체들의 적층 이후에, 스텐실(5)은 제거된다. 스텐실(5)은 다만 일시적으로 제조 공정 중에 모듈상에 배치된다.

도 2의 실시예에서, 완성된 모듈의 실시예가 도시되어 있으며, 상기 모듈은 도전 구조체들(8)을 포함한다.

도 1에 도시된 실시예와 달리, 도 2의 모듈은, 캐리어 기판(1)상에 배치되어 복사 방출 반도체 소자(2) 및 평탄화층(3)을 둘러싸는 프레임을 포함하지 않는다.

바람직하게는, 복사 방출 반도체 소자(2)는 납땜 또는 전기 전도 접착제를 이용하여 캐리어 기판(1)의 구조화된 도전로상에 고정된다.

도 1의 실시예의 경우와 같이, 전기 절연층(4)은 복사 방출 소자(2) 및 평탄화층(3)상에 적층된다. 전기 절연층(4)은 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역들에서 리세스를 포함한다. 이러한 리세스는 바람직하게는 레이저 방법 또는 리소그라피 방법을 이용하여 제조된다.

도 1의 실시예와 달리, 도전 구조체들(8)은 예를 들면 젯 인쇄 방법을 이용하여 전기 절연층(4)상에 적층된다. 도전 구조체들(8)의 적층은 바람직하게는 노즐(9)을 이용한다. 노즐(9)은 캐리어 기판(1)과 반대 방향을 향해 있는 모듈의 측에서 도전 구조체들, 바람직하게는 1겹의 금속 경로를 설계한다. 특히, 도전 구조체들(8)은 전기 절연층(4)상에 적층되어, 복사 방출 반도체 소자들(2)의 상호간 전기 접촉 또는 캐리어 기판(1)의 도전로와의 전기 접촉이 이루어진다. 특히, 도전 구조체들(8)은 각각 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에 위치한다.

복사 방출 반도체 소자(2)는 별도로 접지될 수 있다. 또는, 복사 방출 반도체 소자(2)는 상호간에 전기 전도적으로 연결될 수 있다.

도 3의 실시예는 도 2의 실시예에 비해, 캐리어 기판(1)이 연성 기판이라는 점에서 상이하다. 특히, 캐리어 기판(1)에서 복사 방출 반도체 소자(2)가 배치된 표면은 평활하지 않다. 캐리어 기판(1)은 예를 들면 아치 곡면을 포함할 수 있다. 특히, 캐리어 기판(1)의 표면은 복사 방출 반도체 소자(2)의 실장이 가능한 경우에 한하여 다른 형상도 가질 수 있다.

특히, 모듈은 도 3의 실시예에서 회전 가능하게 배치될 수 있다. 이를 통해, 유리하게는 예를 들면 모듈의 제조가 간단해진다. 노즐을 이용하여 도전 구조체들을 설계하는 방법 단계동안 모듈은 예를 들면 원하는 도전 구조체들의 구조화에 상응하여 움직이고 예를 들면 회전할 수 있다.

도 4의 실시예에서, 광전 모듈의 일부가 도시되어 있다. 특히, 모듈의 복사 방출 반도체 소자(2)만이 도시되어 있다. 모듈의 다른 복사 방출 반도체 소자들은 개관상의 이유로 도시되지 않았다.

캐리어 기판(1)상에서 복사 방출 반도체 소자(2)는 바람직하게는 접착성 층을 이용하여 접착되거나, 땜납을 이용하여 납땜된다. 도 4에 도시된 바와 같이, 바람직하게는 복사 방출 반도체 소자(2)상에 그리고 캐리어 기판(1)상에 전기 절연층(4)이 배치된다. 전기 절연층(4)은 예를 들면 라미네이팅된 필름 또는 유리를 함유한 층이다.

전기 절연층(4)은 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에서 리세스를 포함한다. 바람직하게는, 전기 절연층(4)은 유전체층이다.

바람직하게는, 모듈의 제조 공정 동안 전기 절연층(4)상에 도전 구조체, 더욱 바람직하게는 금속층이 기상 증착을 이용하여 전면으로(whole surface) 증착된다(미도시). 바람직하게는, 전면적인 도전 구조체는 물리 기상 증착 또는 화학 기상 증착을 이용하여 증착된다. 이어서, 전면으로 형성된 도전 구조체는 예를 들면 포토리소그래피 및 식각을 이용하여 복사 방출 소자(2)의 원하는 회로에 상응하여 구조화된다. 특히, 전면적 도전 구조체는 바람직하게는 복사 방출 반도체 소자가 상호간 전기 전도적으로 연결되거나, 복사 방출 반도체 소자(2)가 캐리어 기판(1)의 도전로와 전기 전도적으로 연결되도록 구조화된다.

바람직하게는, 공정을 더욱 간단하고 개선된 방식으로 실시하기 위해, 전기 절연층, 특히 유전체층이 도전 구조체들의 증착 이전에 평탄화되고, 예를 들면 SOG 방법을 이용하여 평탄화된다.

도 5의 실시예에서, 다른 광전 모듈의 일부가 도시되어 있다. 이 경우에도, 개관상의 이유로 복사 방출 반도체 소자(2)만이 도시되어 있다.

도 4에 도시된 실시예와 달리, 도전 구조체(8)는 이방성층(8a, 8b)으로 형성된다. 바람직하게는, 이방성층(8a, 8b)은, 라미네이팅되는 것이 바람직한 이방성 필름이다.

바람직하게는, 이방성층은 2개의 부분 영역들(8a, 8b)을 포함한다. 부분 영역들 중 하나(8a)는 전도성으로 형성되는 것이 바람직하다. 그에 반해, 다른 부분 영역(8b)은 전기 절연성이다.

이방성층의 영역(8a)에서 전도도의 형성은 바람직하게는 국부적으로 인가된 압력 또는 조사에 의해 이루어진다. 이를 통해, 유리하게는 복사 방출 반도체 소자(2)의 전기적 연결이 제1접촉면(21)의 영역에서 보장된다.

바람직하게는, 이방성층(8a, 8b)은 제2부분 영역(8b)에서 복사 방출 반도체 소자(2)로부터 방출된 복사에 대해 적어도 부분적으로 복사 투과성이다. 또는, 상기 제2부분 영역(8b)에서 이방성층(8a,8b)은 라미네이팅된 이후 선택적으로 제거될 수 있다. 이 경우, 이방성층(8a, 8b)은 복사 투과성이 아니어야 한다.

도 6에 도시된 광전 모듈의 실시예는 복수 개의 복사 방출 반도체 소자들(2)을 포함하고, 상기 반도체 소자들은 땜납 또는 접착성층(10)을 이용하여 캐리어 기판(1)상에 고정된다. 바람직하게는, 복사 방출 반도체 소자(2)의 제2접촉면(22)은 캐리어 기판(1)상에 배치된 도전로와 전기 접촉한다. 바람직하게는, 복사 방출 반도체 소자(2)의 도전로는 서로 전기적으로 절연되어 배치된다.

선행한 실시예에 도시된 모듈과 달리, 도 6의 실시예에서는 구조화된 도체판 및 도전 구조체들(8)에 의한 전기 절연층(4)이 상기 도체판으로부터 돌출된 전기 전도웹, 예를 들면 금속웹으로 형성된다.

도체판은 특히 전기 절연 물질을 포함하고, 상기 전기 절연 물질안에 전기 전도적 도전로가 포함되어 있다. 더욱 바람직하게는, 도체판의 전기 절연 물질은 복사 방출 반도체 소자(2)로부터 방출된 복사에 대해 적어도 부분적으로 복사 투과성이다. 도체판의 전기 절연 물질은 복사 방출 반도체 소자(2)로부터 방출된 복사를 변환하기 위해 적어도 하나의 변환 부재를 더 포함할 수 있다.

도체판의 전기 절연 물질에 포함된 도전로는 바람직하게는 적어도 부분적으로 금속웹(8)과 전기 전도적으로 연결된다. 또한, 금속웹(8)은, 각각, 바람직하게는 복사 방출 반도체 소자(2)의 제1접촉면(21)과 전기 전도적으로 연결된다. 이를 위해, 도체판(4)은 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에서 리세스를 각각 포함한다.

웹(8) 및 도체판(4)의 도전로를 경유하여, 복사 방출 반도체 소자(2)는 각각 전기적으로 접촉된다. 이때, 복사 방출 반도체 소자(2)는 전기 전도적으로 상호간 연결되거나, 전기 전도적으로 각각 캐리어 기판(1)의 도전로와 연결될 수 있다.

바람직하게는, 금속웹(8)은 상기 금속웹이 도체판의 접촉 지점으로부터 복사 방출 반도체 소자(2)의 방향으로 굴곡지도록 형성된다.

이러한 실시예에서, 복수 개의 도체판들이 포개어져 배치될 수 있어서, 다겹의 배열 및 그로 인한 다겹의 회로면이 모듈내에 형성된다(미도시).

금속웹(8)은 예를 들면 각각 스템핑 웨지 공정을 이용하여 복사 방출 반도체 소자(2)의 제1접촉면(21)과 전기적 및 기계적으로 연결될 수 있다.

도 7a, 7b에서 각각 광전 모듈의 개략적 일부가 도시되어 있다. 도 7a는 모듈의 일부를 횡단면도로 도시한다. 도 7b는 도 7a의 일부분을 평면도로 도시한다.

도 7a에는 복사 방출 반도체 소자(2)가 도시되어 있다. 광전 모듈은 바람직하게는 예를 들면 도 7a에 도시된 바와 같은 복수 개의 복사 방출 반도체 소자들(2)로 구성되고, 이때 복사 방출 반도체 소자(2)는 바람직하게는 캐리어 기판(1)상에 배치된다.

도 1 내지 6의 실시예와 달리, 도 7a의 복사 방출 반도체 소자(2)는 제1접촉면(21)을 포함하고, 상기 제1접촉면은 전기 절연층(4)상에 이어진다. 전기 절연층(4)은 각각 국부적으로 복사 방출 반도체 소자(2)의 측면에서 각각의 복사 방출 반도체 소자(2)의 둘레에서 이어진다. 바람직하게는, 전기 절연층(4)은 복사 방출 반도체 소자(2)의 측면에서 반도체 소자(2)의 활성층(2a)을 경유하여 이어진다.

바람직하게는, 제1접촉면(21)도 마찬가지로 반도체 소자(2)의 측면에서 이어진다. 특히, 제1접촉면(21)은 전기 절연층(4)상에 이어진다. 캐리어 기판과 반대 방향을 향해 있는 복사 방출 반도체 소자(2)의 표면은 바람직하게는 제1접촉면(21)을 포함하지 않는다.

반도체 소자(2)의 측면을 따라 제1접촉층(21)이 이어짐으로써, 복사 방출 반도체 소자(2)의 전원 공급이 균일하게 보장된다.

바람직하게는, 제1접촉층(21)의 영역에 전기적 공급부(12)가 연결된다. 반도체 소자(2)의 측면을 따라 제1접촉층(21)이 이어짐으로써, 제1접촉층(21)의 임의의 영역들에서 반도체 소자(2)의 전기적 회로를 위한 전기적 공급부들(12)이 이어질 수 있다. 모듈의 반도체 소자들은 공급부들(12)을 경유하여 상호간에 전기 접속될 수 있다. 또는, 반도체 소자들은 각각 별도로 전기적으로 연결될 수 있다.

도 7b에는 도 7a의 반도체 소자의 접촉 방식에 대한 평면도가 도시되어 있다. 제1접촉면(21)은 반도체 소자(2)의 복사 아웃커플링면의 측에 배치된다. 바람직하게는, 제1접촉층(21)은 프레임형으로 형성된다. 특히, 제1접촉층(21)은 닫힌 경로를 형성한다. 제1접촉층(21)에서 국부적으로, 전기적 공급부(12)가 배치되며, 상기 전기적 공급부는 반도체 소자(2)의 회로를 위해 역할한다.

바람직하게는, 도 7a, 7b의 실시예에서 복사 방출 반도체 소자(2)상에 전류 분포층(13)이 배치된다. 특히, 전류 분포층(13)은 반도체 소자(2)로부터 방출된 복사에 대해 적어도 부분적으로 복사 투과성이다. 예를 들면, 전류 분포층(13)은 ITO층 또는 ZnO층이다.

바람직하게는, 제1접촉층(21)은 금속배선이다. 바람직하게는, 반도체 소자(2)의 복사 아웃커플링면은 금속배선을 포함하지 않는다. 바람직하게는, 금속배선은 반도체 소자(2)를 중심으로 그 둘레에 이어짐으로써, 예를 들면 종래에 사용되는 본딩 패드를 이용한 경우보다 더 균일한 전원 공급이 보장된다.

도 7c에는 도 7a의 복수 개의 복사 방출 반도체 소자(2)를 포함한 모듈의 평면도가 도시되어 있다. 이 경우, 모듈은 4개의 복사 방출 반도체 소자들(2)을 포함한다. 그러나, 각각의 사용 범위 및 모듈의 사용 목적에 따라 다른 개수의 반도체 소자(2)도 가능하다.

반도체 소자(2)의 제1접촉면(21)이 측면에 배치되어 전기적으로 이어짐으로써, 반도체 소자(2)의 복합 회로가 구현될 수 있다. 이를 통해, 유리하게도, 캐리어 기판(1)상에 반도체 소자들(2)이 공간 절약적으로 배치될 수 있다.

특히, 반도체 소자들(2)은 개별적으로 캐리어 기판(1)상에 실장되고, 서로가 각각 전기 전도적으로 연결될 수 있다. 이 경우, 캐리어 기판(1)은 반도체 소자(2)를 위한 실장측에서 각각 서로 전기적으로 절연된 도전로들을 포함하고, 상기 도전로들상에 각각 하나의 반도체 소자가 기계적 및 전기적으로 연결되어 있다.

또는, 반도체 소자들(2)은 상호간에 전기적으로 접속될 수 있다. 이때, 바람직하게는, 캐리어 기판(1) 자체는 전기 전도성으로 형성되어, 반도체 소자들(2)이 공통의 전기 전위에 놓인다. 또는, 캐리어 기판(1)상에 도전로가 배치될 수 있고, 상기 도전로상에 반도체 소자들(2)이 공통으로 배치되어 있다. 반도체 소자들(2)의 전기적 공급부(12)는 바람직하게는 다른 전기적 연결부로 이어진다(미도시).

본 발명은 실시예에 의거한 설명에 의하여 이러한 실시예에 한정되지 않는다. 오히려 본 발명은 각각의 새로운 특징 및 특징들의 각 조합을 포함하고, 이러한 점은 특히, 비록 이러한 특징 또는 이러한 조합이 그 자체로 명백하게 특허청구범위 또는 실시예에 제공되지 않더라도 특허청구범위에서의 특징들의 각 조합을 포괄한다.

Claims (15)

- 캐리어 기판(1) 및 복수 개의 복사 방출 반도체 소자들(2)을 포함하는 광전 모듈에 있어서,

상기 캐리어 기판(1)은 상기 복사 방출 반도체 소자들(2)의 전기 접촉을 위해 구조화된 도전로들을 포함하고,

상기 복사 방출 반도체 소자들(2)은 각각 전자기 복사의 생성을 위해 적합한 활성층(2a), 제1접촉면(21) 및 제2접촉면(22)을 포함하고, 이때 상기 제1접촉면(21)은 각각 상기 캐리어 기판(1)과 반대 방향을 향해 있는 복사 방출 반도체 소자들(2)의 측에 배치되고,

상기 복사 방출 반도체 소자들(2)은 전기 절연층(4)을 구비하며, 상기 전기 절연층은 각각 상기 복사 방출 반도체 소자들(2)의 제1접촉면(21)의 영역에서 리세스를 가지며,

상기 전기 절연층(4)상에 국부적으로 도전 구조체들(8)이 배치되고, 그리고

상기 도전 구조체들 중 하나는 적어도, 복사 방출 반도체 소자(2)의 제1접촉면(21)을 다른 복사 방출 반도체 소자(2)의 다른 제1접촉면과 전기 전도적으로 연결하거나, 상기 캐리어 기판(1)의 도전로와 전기 전도적으로 연결하는 것을 특징으로 하는 광전 모듈. - 청구항 1에 있어서,

상기 복사 방출 반도체 소자들(2) 사이에 평탄화층(3)이 적어도 배치되는 것을 특징으로 하는 광전 모듈. - 청구항 2에 있어서,

상기 평탄화층(3)은 적어도 하나의 변환 부재를 포함하는 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

상기 전기 절연층(4)은 적어도 하나의 변환 부재(6)를 포함하는 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 4 중 어느 한 항에 있어서,

상기 복사 방출 반도체 소자들(2)은 공통적으로, 상기 캐리어 기판(1)상에 배치된 프레임(7)에 의해 둘러싸이는 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 5 중 어느 한 항에 있어서,

상기 캐리어 기판(1)은 연성 기판인 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 6 중 어느 한 항에 있어서,

상기 캐리어 기판(1)에서 상기 복사 방출 반도체 소자들(2)이 배치된 표면은 평활하지 않은 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 7 중 어느 한 항에 있어서,

상기 도전 구조체들(8)은 이방성층으로 형성되고, 상기 이방성층은 상기 전기 절연층(4)상에 배치되며, 각각의 복사 방출 반도체 소자들(2)의 제1접촉면(21)의 영역에서 전기 전도 영역들(8a)을 적어도 포함하는 것을 특징으로 하는 광전 모듈. - 청구항 1 내지 청구항 7 중 어느 한 항에 있어서,

상기 전기 절연층(4)은 구조화된 도체판 및 상기 도전 구조체들(8)에 의해, 상기 도체판으로부터 돌출한 전기 전도 웹을 이용하여 형성되는 것을 특징으로 하는 모듈. - 청구항 1 내지 청구항 9 중 어느 한 항에 있어서,

상기 전기 절연층(4)은 국부적으로 각각의 복사 방출 반도체 소자(2)의 측면에서 각각의 복사 방출 반도체 소자(2)의 둘레에 이어지고, 각각의 복사 방출 반도체 소자(2)의 제1접촉면(21)은 상기 전기 절연층(4)상에 배치되어, 상기 캐리어 기판(1)과 반대 방향을 향해 있는 복사 방출 반도체 소자들(2)의 표면은 상기 제1접촉면(21)을 포함하지 않는 것을 특징으로 하는 모듈. - 광전 모듈의 제조 방법에 있어서,

캐리어 기판(1)상에 복수 개의 복사 방출 반도체 소자들(2)을 배치하는 단계로, 이때 상기 캐리어 기판(1)은 상기 복사 방출 반도체 소자들(2)의 전기 접촉을 위해 구조화된 도전로들을 포함하고, 상기 복사 방출 반도체 소자들(2)은 각각 전자기 복사의 생성을 위해 적합한 활성층(2a), 제1접촉면(21) 및 제2접촉면(22)을 포함하며, 이때 상기 제1접촉면(21)은 각각 상기 캐리어 기판(1)과 반대 방향을 향해 있는 상기 복사 방출 반도체 소자들(2)의 측에 배치되도록 하는 단계,

상기 복사 방출 반도체 소자들(2)상에 전기 절연층(4)을 적층하는 단계로, 이때 상기 전기 절연층(4)은 각각의 복사 방출 반도체 소자(2)의 제1접촉면(21)의 영역에서 리세스(4a)를 각각 포함하도록 하는 단계,

상기 전기 절연층(4)의 일부 영역들상에 도전 구조체들(8)을 적층하는 단계로, 이때 상기 도전 구조체들(8) 중 하나는 적어도, 복사 방출 반도체 소자(2)의 제1접촉면(21)을 다른 복사 방출 반도체 소자(2)의 다른 제1접촉면(21)과 전기 전도적으로 연결하거나, 상기 캐리어 기판(1)의 도전로와 전기 전도적으로 연결하는 단계를 포함하는 것을 특징으로 하는 광전 모듈의 제조 방법. - 청구항 11에 있어서,

상기 도전 구조체들(8)은 인쇄 방법을 이용하여 적층되는 것을 특징으로 하는 광전 모듈의 제조 방법. - 청구항 11에 있어서,

상기 도전 구조체들(8)은 기상 증착을 이용하여 적층되는 것을 특징으로 하는 광전 모듈의 제조 방법. - 청구항 11에 있어서,

상기 도전 구조체들(8)은 이방성층을 이용하여 형성되고, 상기 이방성층은 상기 전기 절연층(4)상에 배치되며, 각각의 복사 방출 반도체 소자들(2)의 제1접촉면(21)의 영역에서 전기 전도적으로 적어도 형성되는 것을 특징으로 하는 광전 모듈의 제조 방법. - 청구항 11에 있어서,

상기 도전 구조체들(8)은 각각 전기 전도 웹으로서 형성되고, 이때 상기 웹은 각각 스템핑-웨지 공정을 이용하여 복사 방출 반도체 소자(2)의 제1접촉면(21)과 전기 전도적으로 연결되는 것을 특징으로 하는 광전 모듈의 제조 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008049188.8 | 2008-09-26 | ||

| DE102008049188A DE102008049188A1 (de) | 2008-09-26 | 2008-09-26 | Optoelektronisches Modul mit einem Trägersubstrat und einer Mehrzahl von strahlungsemittierenden Halbleiterbauelementen und Verfahren zu dessen Herstellung |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20110057263A true KR20110057263A (ko) | 2011-05-31 |

Family

ID=41602690

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117009227A KR20110057263A (ko) | 2008-09-26 | 2009-08-25 | 캐리어 기판 및 복수 개의 복사 방출 반도체 소자를 포함한 광전 모듈 및 그 제조 방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US8461604B2 (ko) |

| EP (1) | EP2297780B1 (ko) |

| JP (1) | JP2012503866A (ko) |

| KR (1) | KR20110057263A (ko) |

| CN (1) | CN102165588B (ko) |

| DE (1) | DE102008049188A1 (ko) |

| TW (1) | TWI438888B (ko) |

| WO (1) | WO2010034278A1 (ko) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011145794A1 (ko) | 2010-05-18 | 2011-11-24 | 서울반도체 주식회사 | 파장변환층을 갖는 발광 다이오드 칩과 그 제조 방법, 및 그것을 포함하는 패키지 및 그 제조 방법 |

| DE102010044560A1 (de) * | 2010-09-07 | 2012-03-08 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterbauelements |

| DE102011055549A1 (de) | 2011-09-30 | 2013-04-04 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Bauelements mit einer drahtlosen Kontaktierung |

| DE102012209325B4 (de) * | 2012-06-01 | 2021-09-30 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Optoelektronisches Modul |

| EP2830094B1 (en) * | 2013-07-22 | 2020-02-26 | LG Innotek Co., Ltd. | Light emitting device |

| KR101503403B1 (ko) * | 2013-09-09 | 2015-03-17 | 삼성디스플레이 주식회사 | 발광소자모듈 및 그 제조방법 |

| US9195358B1 (en) * | 2014-04-16 | 2015-11-24 | Eastman Kodak Company | Z-fold multi-element substrate structure |

| DE102016208431A1 (de) * | 2016-05-17 | 2017-11-23 | Osram Opto Semiconductors Gmbh | Anordnung mit einem elektrischen Bauteil |

| DE102018120637A1 (de) * | 2018-08-23 | 2020-02-27 | Osram Opto Semiconductors Gmbh | Leiterplatte und verfahren zur herstellung einer leiterplatte mit mindestens einem in die leiterplatte integrierten optoelektronischen bauelement |

| DE102019100794A1 (de) * | 2018-12-20 | 2020-06-25 | Osram Opto Semiconductors Gmbh | Laservorrichtung und verfahren zur herstellung einer laservorrichtung |

| KR20210072194A (ko) * | 2019-12-06 | 2021-06-17 | 삼성디스플레이 주식회사 | 발광 소자의 정렬 방법, 이를 이용한 표시 장치의 제조 방법 및 표시 장치 |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55120081A (en) * | 1979-03-08 | 1980-09-16 | Tokyo Shibaura Electric Co | Led display unit |

| JPS575359A (en) * | 1980-06-11 | 1982-01-12 | Hitachi Ltd | Semiconductor device |

| JPS575356A (en) * | 1980-06-13 | 1982-01-12 | Toshiba Corp | Hybrid integrated circuit device |

| JPS61290780A (ja) | 1985-06-19 | 1986-12-20 | Hitachi Vlsi Eng Corp | 光電変換装置 |

| JPH0723827Y2 (ja) * | 1989-06-12 | 1995-05-31 | 株式会社小糸製作所 | 表示装置用光源体 |

| JP2581083Y2 (ja) * | 1991-05-28 | 1998-09-17 | 三洋電機株式会社 | 発光ダイオード表示装置 |

| US5519332A (en) * | 1991-06-04 | 1996-05-21 | Micron Technology, Inc. | Carrier for testing an unpackaged semiconductor die |

| JPH0832112A (ja) * | 1994-07-20 | 1996-02-02 | Toyoda Gosei Co Ltd | 3族窒化物半導体発光素子 |

| DE19638667C2 (de) | 1996-09-20 | 2001-05-17 | Osram Opto Semiconductors Gmbh | Mischfarbiges Licht abstrahlendes Halbleiterbauelement mit Lumineszenzkonversionselement |

| US6529027B1 (en) * | 2000-03-23 | 2003-03-04 | Micron Technology, Inc. | Interposer and methods for fabricating same |

| DE10051159C2 (de) * | 2000-10-16 | 2002-09-19 | Osram Opto Semiconductors Gmbh | LED-Modul, z.B. Weißlichtquelle |

| WO2003012884A1 (en) | 2001-08-01 | 2003-02-13 | Nam-Young Kim | Display system |

| US6784540B2 (en) * | 2001-10-10 | 2004-08-31 | International Rectifier Corp. | Semiconductor device package with improved cooling |

| TW200405790A (en) * | 2002-08-08 | 2004-04-01 | Dainippon Printing Co Ltd | Electromagnetic wave shielding sheet |

| JP3782411B2 (ja) * | 2002-09-02 | 2006-06-07 | 松下電器産業株式会社 | 発光装置 |

| DE10245945A1 (de) * | 2002-09-30 | 2004-04-08 | Osram Opto Semiconductors Gmbh | Lichtquellenmodul sowie Verfahren zu dessen Herstellung |

| DE10353679A1 (de) | 2003-11-17 | 2005-06-02 | Siemens Ag | Kostengünstige, miniaturisierte Aufbau- und Verbindungstechnik für LEDs und andere optoelektronische Module |

| EP1700344B1 (en) * | 2003-12-24 | 2016-03-02 | Panasonic Intellectual Property Management Co., Ltd. | Semiconductor light emitting device and lighting module |

| US7858994B2 (en) * | 2006-06-16 | 2010-12-28 | Articulated Technologies, Llc | Solid state light sheet and bare die semiconductor circuits with series connected bare die circuit elements |

| DE102004021233A1 (de) * | 2004-04-30 | 2005-12-01 | Osram Opto Semiconductors Gmbh | Leuchtdiodenanordnung |

| US20060035036A1 (en) | 2004-08-16 | 2006-02-16 | Telephus Inc. | Anisotropic conductive adhesive for fine pitch and COG packaged LCD module |

| DE102004050371A1 (de) | 2004-09-30 | 2006-04-13 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement mit einer drahtlosen Kontaktierung |

| TWI277222B (en) * | 2004-10-29 | 2007-03-21 | Lighthouse Technology Co Ltd | LED module and method of packing the same |

| US20060124953A1 (en) * | 2004-12-14 | 2006-06-15 | Negley Gerald H | Semiconductor light emitting device mounting substrates and packages including cavities and cover plates, and methods of packaging same |

| US7563658B2 (en) * | 2004-12-27 | 2009-07-21 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US7821023B2 (en) * | 2005-01-10 | 2010-10-26 | Cree, Inc. | Solid state lighting component |

| EP2259318A3 (en) * | 2005-02-04 | 2014-01-08 | Seoul Opto Device Co., Ltd. | Light emitting device having a plurality of light emitting cells and method of fabricating the same |

| KR101047683B1 (ko) * | 2005-05-17 | 2011-07-08 | 엘지이노텍 주식회사 | 와이어 본딩이 불필요한 발광소자 패키징 방법 |

| DE102006023123B4 (de) * | 2005-06-01 | 2011-01-13 | Infineon Technologies Ag | Abstandserfassungsradar für Fahrzeuge mit einem Halbleitermodul mit Komponenten für Höchstfrequenztechnik in Kunststoffgehäuse und Verfahren zur Herstellung eines Halbleitermoduls mit Komponenten für ein Abstandserfassungsradar für Fahrzeuge in einem Kunststoffgehäuse |

| JP2008544540A (ja) * | 2005-06-22 | 2008-12-04 | ソウル オプト デバイス カンパニー リミテッド | 発光素子及びその製造方法 |

| KR100599012B1 (ko) * | 2005-06-29 | 2006-07-12 | 서울옵토디바이스주식회사 | 열전도성 기판을 갖는 발광 다이오드 및 그것을 제조하는방법 |

| TWI285442B (en) * | 2005-08-29 | 2007-08-11 | Gigno Technology Co Ltd | Package structure of light emitting diode |

| US8039849B2 (en) * | 2005-11-23 | 2011-10-18 | Taiwan Oasis Technology Co., Ltd. | LED module |

| JP2007158262A (ja) * | 2005-12-08 | 2007-06-21 | Rohm Co Ltd | 半導体発光素子の製造方法 |

| TWI331406B (en) * | 2005-12-14 | 2010-10-01 | Advanced Optoelectronic Tech | Single chip with multi-led |

| US20070263408A1 (en) * | 2006-05-09 | 2007-11-15 | Chua Janet Bee Y | Backlight module and method of making the module |

| US20100224890A1 (en) * | 2006-09-18 | 2010-09-09 | Cree, Inc. | Light emitting diode chip with electrical insulation element |

| US8350279B2 (en) * | 2006-09-25 | 2013-01-08 | Seoul Opto Device Co., Ltd. | Light emitting diode having AlInGaP active layer and method of fabricating the same |

| US7781781B2 (en) * | 2006-11-17 | 2010-08-24 | International Business Machines Corporation | CMOS imager array with recessed dielectric |

| US20080117619A1 (en) * | 2006-11-21 | 2008-05-22 | Siew It Pang | Light source utilizing a flexible circuit carrier and flexible reflectors |

| DE102007009351A1 (de) * | 2007-02-23 | 2008-08-28 | Noctron Holding S.A. | Leuchtmittel |

| DE102007011123A1 (de) * | 2007-03-07 | 2008-09-11 | Osram Opto Semiconductors Gmbh | Licht emittierendes Modul und Herstellungsverfahren für ein Licht emittierendes Modul |

| US8058669B2 (en) * | 2008-08-28 | 2011-11-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Light-emitting diode integration scheme |

| US8169540B2 (en) * | 2008-09-10 | 2012-05-01 | Panasonic Corporation | Compact camera body to which interchangeable lens unit is mountable |

-

2008

- 2008-09-26 DE DE102008049188A patent/DE102008049188A1/de not_active Withdrawn

-

2009

- 2009-08-25 US US13/121,128 patent/US8461604B2/en active Active

- 2009-08-25 WO PCT/DE2009/001217 patent/WO2010034278A1/de active Application Filing

- 2009-08-25 KR KR1020117009227A patent/KR20110057263A/ko not_active Application Discontinuation

- 2009-08-25 EP EP09740632.6A patent/EP2297780B1/de active Active

- 2009-08-25 CN CN2009801381690A patent/CN102165588B/zh active Active

- 2009-08-25 JP JP2011528181A patent/JP2012503866A/ja active Pending

- 2009-09-24 TW TW098132250A patent/TWI438888B/zh active

-

2013

- 2013-06-06 US US13/911,798 patent/US20140030829A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| TWI438888B (zh) | 2014-05-21 |

| EP2297780A1 (de) | 2011-03-23 |

| EP2297780B1 (de) | 2019-06-12 |

| WO2010034278A1 (de) | 2010-04-01 |

| US8461604B2 (en) | 2013-06-11 |

| DE102008049188A1 (de) | 2010-04-01 |

| CN102165588A (zh) | 2011-08-24 |

| CN102165588B (zh) | 2013-09-25 |

| US20110309377A1 (en) | 2011-12-22 |

| US20140030829A1 (en) | 2014-01-30 |

| TW201019458A (en) | 2010-05-16 |

| JP2012503866A (ja) | 2012-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20110057263A (ko) | 캐리어 기판 및 복수 개의 복사 방출 반도체 소자를 포함한 광전 모듈 및 그 제조 방법 | |

| EP3454372B1 (en) | Light emitting diode | |

| TWI446593B (zh) | 光電半導體組件之製造方法及光電半導體組件 | |

| EP2515353B1 (en) | Light emitting diode package | |

| US8791548B2 (en) | Optoelectronic semiconductor chip, optoelectronic component and a method for producing an optoelectronic component | |

| KR101386303B1 (ko) | 박막 반도체 소자 및 소자 어셈블리 | |

| JP5372009B2 (ja) | オプトエレクトロニクス部品およびその製造方法 | |

| EP2461380B1 (en) | Light emitting diode device package and manufacturing method thereof | |

| EP2477244B1 (en) | Method of manufacturing a light-emitting device package on a wafer level | |

| US20130037830A1 (en) | Light emitting diode package and method for manufacturing the same | |

| CN106796968A (zh) | 用于制造光电子半导体器件的方法和光电子半导体器件 | |

| JP5568476B2 (ja) | オプトエレクトロニクス部品 | |

| US9543479B2 (en) | Method for producing an optoelectronic component and optoelectronic component produced in such a way | |

| KR20110095342A (ko) | 복사 방출 소자 및 그 제조 방법 | |

| US20120228666A1 (en) | Optoelectronic Module | |

| KR20130062985A (ko) | 복사 방출 소자 및 복사 방출 소자의 제조 방법 | |

| US9029902B2 (en) | Optoelectronic semiconductor device comprising a semiconductor chip, a carrier substrate and a film | |

| CN102484186B (zh) | 具有带有辐射出射侧和绝缘层的至少一个第一半导体本体的光电子模块及其制造方法 | |

| WO2014032702A1 (en) | Light-emitting device and method for manufacturing a light- emitting device | |

| US11271140B2 (en) | Method for manufacturing a plurality of surface mounted optoelectronic devices and surface mounted optoelectronic device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |