JP2012156191A - 積層型電子部品及び電子部品の実装構造 - Google Patents

積層型電子部品及び電子部品の実装構造 Download PDFInfo

- Publication number

- JP2012156191A JP2012156191A JP2011012024A JP2011012024A JP2012156191A JP 2012156191 A JP2012156191 A JP 2012156191A JP 2011012024 A JP2011012024 A JP 2011012024A JP 2011012024 A JP2011012024 A JP 2011012024A JP 2012156191 A JP2012156191 A JP 2012156191A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- electronic component

- ferrite bead

- main

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000011324 bead Substances 0.000 claims abstract description 146

- 239000003990 capacitor Substances 0.000 claims description 83

- 229910000859 α-Fe Inorganic materials 0.000 abstract description 119

- 238000000605 extraction Methods 0.000 abstract description 5

- 239000000758 substrate Substances 0.000 abstract description 4

- 239000010410 layer Substances 0.000 description 76

- 239000002131 composite material Substances 0.000 description 15

- 238000010586 diagram Methods 0.000 description 6

- 238000003475 lamination Methods 0.000 description 6

- 230000007547 defect Effects 0.000 description 5

- 230000007847 structural defect Effects 0.000 description 5

- 230000007257 malfunction Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 229910000679 solder Inorganic materials 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 2

- 230000032798 delamination Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 206010013647 Drowning Diseases 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

Images

Landscapes

- Filters And Equalizers (AREA)

- Coils Or Transformers For Communication (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Abstract

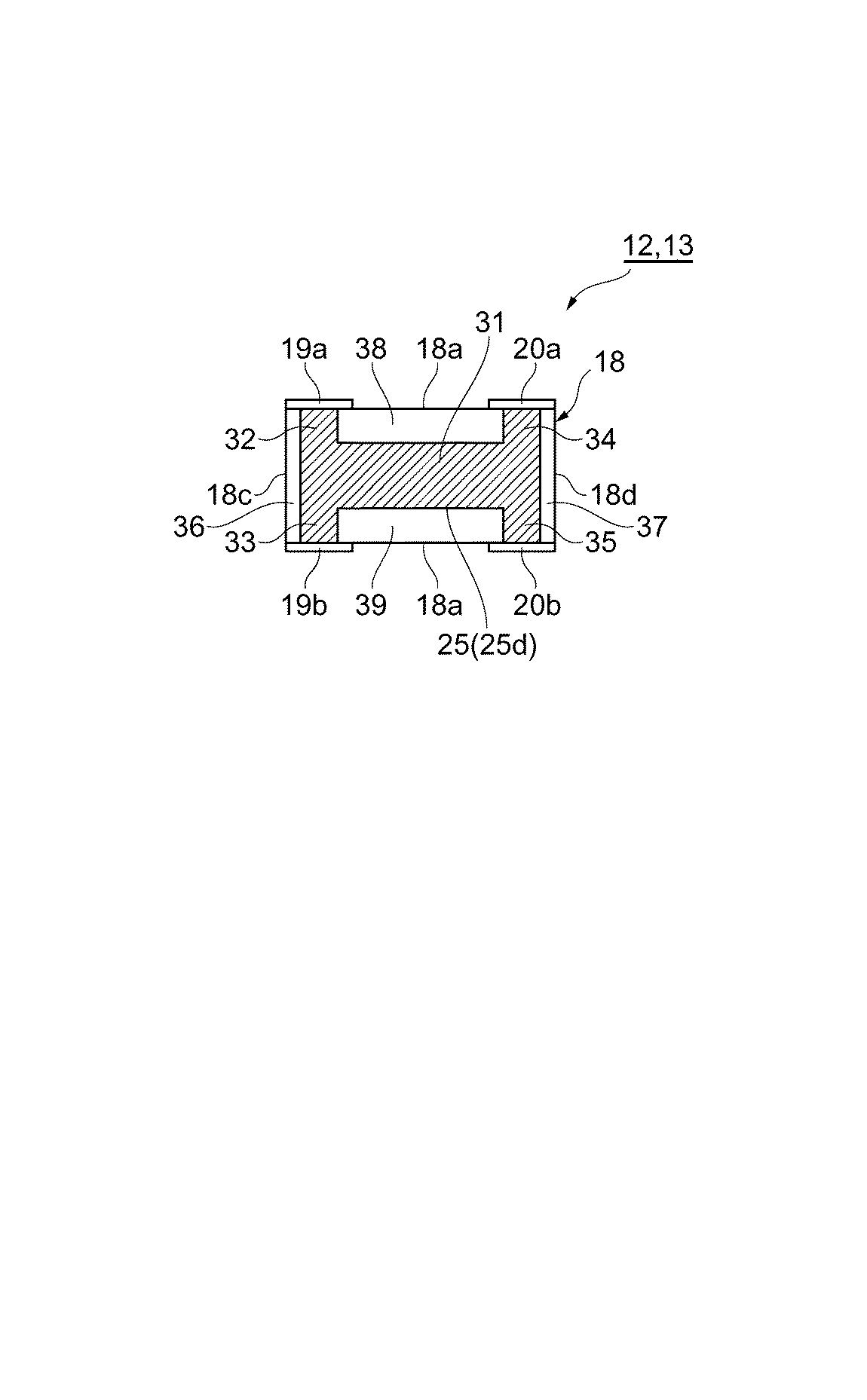

【解決手段】フェライトビーズインダクタ12,13は、磁性体層24と内部電極25a〜25hとが実装基板に対して略垂直になるように主面18aの長辺方向に積層されているフェライトビーズ素体18と、フェライトビーズ素体18の主面18bに互いに離間して配置される第1及び第2の外部電極19b,20bとを備えている。内部電極25a〜25hは、主面18aの短辺方向に伸びる主電極部31と、主電極部31を第1及び第2の外部電極19b,20bそれぞれに接続する引き出し電極部33,35とを有し、主面18a,18bの対向方向において主電極部31の幅t1がフェライトビーズ素体18の厚みTの50%以上の長さとなっている。

【選択図】図6

Description

まず、第1実施形態に係る電子部品の実装構造について説明する。図1は、第1実施形態に係る電子部品の実装構造を示す図である。図1に示すように、電子部品の実装構造では、電源供給用流路を形成する2本の電源ライン1,2、IC(Integrated Circuit)チップ3、第1〜第4のランド電極4〜7及び接続電極8,9が配置された回路に電子部品を実装する。電子部品の実装構造では、電源ライン1,2に接続される電子部品として、複数のコンデンサ(チップコンデンサ)10,11と、複数のフェライトビーズインダクタ12,13とを実装する。コンデンサ10,11及びフェライトビーズインダクタ12,13は、それぞれ2つ実装される。コンデンサ10,11とフェライトビーズインダクタ12,13とは、電源ライン1,2間に直列に接続されている。

次に、第2実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1及び第2の外部電極19,20の形状及び内部電極25の形状が第1実施形態と異なっている。以下、第1実施形態と異なる点を中心に説明する。

Claims (6)

- 第1の方向に対向している第1及び第2の主面と、前記主面間を連結するように前記第1の方向と交差する第2の方向に伸び且つ互いに対向する第1及び第2の側面と、前記主面間を連結するように前記第1及び第2の方向と交差する第3の方向に伸び且つ互いに対向する第3及び第4の側面とを有し、前記第2の方向に磁性体層と内部電極とが積層されている素体と、

前記素体の前記第1及び第2の主面の少なくとも一方に互いに離間して配置される第1及び第2の外部電極と、を備え、

前記内部電極は、前記第3の方向に伸びる主電極部と当該主電極部を前記第1及び第2の外部電極それぞれに接続する引き出し電極部とを有し、

前記主面が対向する前記第1の方向において前記主電極部の幅t1が前記素体の厚みTの50%以上の長さであることを特徴とする積層型電子部品。 - 前記磁性体層と前記内部電極とが積層される前記第2の方向における前記素体の幅寸法Wは、前記主電極部が伸びる前記第3方向における前記素体の幅寸法Lよりも長いことを特徴とする請求項1に記載の積層型電子部品。

- 前記第1の方向において前記主電極部の幅t1が前記素体の厚みTの75%以下の長さであることを特徴とする請求項1又は2に記載の積層型電子部品。

- 前記第1及び第2の外部電極は、前記第1及び第2の主面と当該主面を連結する第1又は第2の側面とに跨って配置されており、

前記内部電極は、それぞれの端部において、前記第1及び第2の主面と前記第1又は第2の側面とに引き出され、各前記引き出し電極部が前記第1又は第2の外部電極に接続されることを特徴とする請求項1〜3の何れか一項に記載の積層型電子部品。 - 前記第1及び第2の主面と前記第1及び第2の側面とが交わる何れかの角部に前記内部電極が形成されていないことを特徴とする請求項1〜4の何れか一項に記載の積層型電子部品。

- 電流を供給するための電源ラインに接続される電子部品の実装構造であって、

前記電子部品として、コンデンサと請求項1〜5の何れか1項に記載の積層型電子部品であるビーズインダクタとを備え、

前記電源ラインの間に、前記コンデンサと前記ビーズインダクタとが直列となるように実装されることを特徴とする電子部品の実装構造。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011012024A JP5267584B2 (ja) | 2011-01-24 | 2011-01-24 | 積層型電子部品及び電子部品の実装構造 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011012024A JP5267584B2 (ja) | 2011-01-24 | 2011-01-24 | 積層型電子部品及び電子部品の実装構造 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012156191A true JP2012156191A (ja) | 2012-08-16 |

| JP5267584B2 JP5267584B2 (ja) | 2013-08-21 |

Family

ID=46837658

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011012024A Active JP5267584B2 (ja) | 2011-01-24 | 2011-01-24 | 積層型電子部品及び電子部品の実装構造 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5267584B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101462767B1 (ko) | 2013-03-14 | 2014-11-20 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 |

| CN104576050A (zh) * | 2013-10-22 | 2015-04-29 | 三星电机株式会社 | 多层陶瓷电子组件和具有多层陶瓷电子组件的印刷电路板 |

| US9524828B2 (en) | 2013-04-22 | 2016-12-20 | Samsung Electro-Mechanics, Co., Ltd. | Multilayered ceramic capacitor and mounting the same |

| US9786434B2 (en) | 2013-10-22 | 2017-10-10 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic electronic component and printed circuit board having the same |

| JP2018026915A (ja) * | 2016-08-09 | 2018-02-15 | 株式会社明電舎 | コンデンサ装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004140183A (ja) * | 2002-10-17 | 2004-05-13 | Murata Mfg Co Ltd | 積層コンデンサ |

| JP2009164513A (ja) * | 2008-01-10 | 2009-07-23 | Murata Mfg Co Ltd | 電子部品 |

| JP2009170873A (ja) * | 2007-12-17 | 2009-07-30 | Murata Mfg Co Ltd | 積層コンデンサ |

| JP2010246075A (ja) * | 2009-03-16 | 2010-10-28 | Tdk Corp | 電子部品の実装構造 |

-

2011

- 2011-01-24 JP JP2011012024A patent/JP5267584B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004140183A (ja) * | 2002-10-17 | 2004-05-13 | Murata Mfg Co Ltd | 積層コンデンサ |

| JP2009170873A (ja) * | 2007-12-17 | 2009-07-30 | Murata Mfg Co Ltd | 積層コンデンサ |

| JP2009164513A (ja) * | 2008-01-10 | 2009-07-23 | Murata Mfg Co Ltd | 電子部品 |

| JP2010246075A (ja) * | 2009-03-16 | 2010-10-28 | Tdk Corp | 電子部品の実装構造 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101462767B1 (ko) | 2013-03-14 | 2014-11-20 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 |

| US9524828B2 (en) | 2013-04-22 | 2016-12-20 | Samsung Electro-Mechanics, Co., Ltd. | Multilayered ceramic capacitor and mounting the same |

| CN104576050A (zh) * | 2013-10-22 | 2015-04-29 | 三星电机株式会社 | 多层陶瓷电子组件和具有多层陶瓷电子组件的印刷电路板 |

| KR20150046712A (ko) * | 2013-10-22 | 2015-04-30 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 |

| KR101659146B1 (ko) * | 2013-10-22 | 2016-09-22 | 삼성전기주식회사 | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 |

| US9786434B2 (en) | 2013-10-22 | 2017-10-10 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic electronic component and printed circuit board having the same |

| JP2018026915A (ja) * | 2016-08-09 | 2018-02-15 | 株式会社明電舎 | コンデンサ装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5267584B2 (ja) | 2013-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20250029788A1 (en) | Electronic component and electronic component device | |

| JP4450084B2 (ja) | 積層コンデンサ及び積層コンデンサの実装構造 | |

| JP2001167969A (ja) | 三次元搭載用多端子積層セラミックコンデンサ | |

| WO2006067939A1 (ja) | 積層コンデンサおよびその実装構造 | |

| US9646767B2 (en) | Ceramic electronic component and ceramic electronic apparatus including a split inner electrode | |

| JP2013211302A (ja) | 積層コイル部品 | |

| JP2022174322A (ja) | 積層セラミック電子部品及びその実装基板 | |

| JP5267584B2 (ja) | 積層型電子部品及び電子部品の実装構造 | |

| JPWO2008044483A1 (ja) | 複合電気素子 | |

| US8325489B2 (en) | Electronic component mounting structure | |

| WO2015037374A1 (ja) | インダクタおよび帯域除去フィルタ | |

| US8994476B2 (en) | Multilayer electronic component and mounted structure of electronic component | |

| JP5170066B2 (ja) | 積層コンデンサ | |

| JP2014183241A (ja) | 貫通型コンデンサ | |

| JP2017034115A (ja) | プリント基板 | |

| JP4992735B2 (ja) | 電子部品 | |

| JP2014220377A (ja) | 積層貫通コンデンサ | |

| JP3832504B2 (ja) | 積層コンデンサおよびその実装構造 | |

| JP4837275B2 (ja) | 積層型コンデンサの実装構造 | |

| JP4961818B2 (ja) | 積層コンデンサ | |

| JP2012129773A (ja) | 電子部品の実装構造 | |

| JP2001155954A (ja) | 三次元搭載用貫通型積層セラミックコンデンサ | |

| JP6142651B2 (ja) | 積層コンデンサ | |

| JP2007123505A (ja) | 積層コンデンサ | |

| JP5397325B2 (ja) | コイル部品 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130409 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130422 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5267584 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |