JP2012084635A - 電子部品の実装構造及び電子機器 - Google Patents

電子部品の実装構造及び電子機器 Download PDFInfo

- Publication number

- JP2012084635A JP2012084635A JP2010228350A JP2010228350A JP2012084635A JP 2012084635 A JP2012084635 A JP 2012084635A JP 2010228350 A JP2010228350 A JP 2010228350A JP 2010228350 A JP2010228350 A JP 2010228350A JP 2012084635 A JP2012084635 A JP 2012084635A

- Authority

- JP

- Japan

- Prior art keywords

- base

- passive element

- mounting structure

- electronic component

- passive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000758 substrate Substances 0.000 abstract description 51

- 229910000679 solder Inorganic materials 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 7

- 239000006071 cream Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 4

- 238000005476 soldering Methods 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- 238000000034 method Methods 0.000 description 3

- 239000010408 film Substances 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

Landscapes

- Shielding Devices Or Components To Electric Or Magnetic Fields (AREA)

Abstract

【課題】電子部品を高密度に配置するとともに装置全体の小型化を図ることが可能な電子部品の実装構造及び電子機器を提供する。

【解決手段】第1基体10と、第1基体10と対向して配置された第2基体20と、第1基体10と第2基体20の間に配置された、両端に電極11a,11bを有する複数の第1受動素子11と、第2基体20の第1受動素子11が配置された側とは反対の側に配置された能動素子21と、を備え、第1受動素子11の両端の電極11a,11bのうち一方の電極11aは、第1基体10と接続されており、他方の電極11bは、第2基体20と接続されるとともに能動素子21と電気的に接続されている。

【選択図】図1

【解決手段】第1基体10と、第1基体10と対向して配置された第2基体20と、第1基体10と第2基体20の間に配置された、両端に電極11a,11bを有する複数の第1受動素子11と、第2基体20の第1受動素子11が配置された側とは反対の側に配置された能動素子21と、を備え、第1受動素子11の両端の電極11a,11bのうち一方の電極11aは、第1基体10と接続されており、他方の電極11bは、第2基体20と接続されるとともに能動素子21と電気的に接続されている。

【選択図】図1

Description

本発明は、電子部品の実装構造及び電子機器に関するものである。

近年、電子機器においては、高性能化、多機能化により、1つのチップで多機能を備えたパッケージ部品が開発されている。多機能なパッケージ部品の出現により、電子機器における能動素子の数は減少している。一方、電子機器において薄膜形成された受動素子では容量に限界があるため、チップ部品化された受動素子の数は増加している。

そのため、電子機器の実装基板においてチップ化された受動素子の占める割合が高くなっており、装置全体の小型化、高機能化のために高密度な電子部品の実装構造が求められている。例えば、特許文献1では、実装基板の上に複数のチップ部品を基板上面と垂直に立てて配置することによりチップ部品が実装される面積を小さくしている。

しかしながら、特許文献1の技術では、複数のチップ部品を一枚の実装基板上のみに配置する構成であるため、チップ部品の実装面積が大きくなり、装置全体の小型化を図るにも限界がある。

一方、キャビティ基板(部品内蔵基板)を用いた構成がある。図8は、キャビティ基板を用いた電子部品の実装構造を示す図である。図8(a)は、キャビティ基板を用いた電子部品の実装構造を示す斜視図である。図8(b)は、キャビティ基板を用いた電子部品の実装構造を示す断面図である。

図8に示すように、キャビティ基板を用いた電子部品の実装構造は、基体1010と、基体1010と対向して配置されたキャビティ基板1020と、キャビティ基板1020のキャビティ部に配置された能動素子1021と、キャビティ基板1020の上に配置された両端に電極を有する複数の受動素子1011,1012と、を備えた構造となっている。各受動素子1011,1012の両端の電極の双方は、キャビティ基板1020と接続されている。

図8に示すように、キャビティ基板を用いた電子部品の実装構造は、基体1010と、基体1010と対向して配置されたキャビティ基板1020と、キャビティ基板1020のキャビティ部に配置された能動素子1021と、キャビティ基板1020の上に配置された両端に電極を有する複数の受動素子1011,1012と、を備えた構造となっている。各受動素子1011,1012の両端の電極の双方は、キャビティ基板1020と接続されている。

しかしながら、キャビティ基板を用いた構成では、能動素子と受動素子との間で配線抵抗が増加したりインダクタ成分の発生によりノイズが生じたりする等の問題がある。また、能動素子(電子部品)を基体とキャビティ基板の間におけるキャビティ部のみに配置する構成であるため、電子部品を高密度に配置するにも限界がある。

本発明はこのような事情に鑑みてなされたものであって、電子部品を高密度に配置するとともに装置全体の小型化を図ることが可能な電子部品の実装構造及び電子機器を提供することを目的とする。

上記の課題を解決するため、本発明に係る電子部品の実装構造は、第1基体と、前記第1基体と対向して配置された第2基体と、前記第1基体と前記第2基体の間に配置された、両端に電極を有する複数の第1受動素子と、前記第2基体の前記第1受動素子が配置された側とは反対の側に配置された能動素子と、を備え、前記第1受動素子の両端の電極のうち一方の電極は、前記第1基体と接続されており、他方の電極は、前記第2基体と接続されるとともに前記能動素子と電気的に接続されていることを特徴とする。

本発明に係る電子部品の実装構造は、基体と、前記基体と対向して配置された導電性のシールド部材と、前記基体と前記シールド部材の間に配置された、両端に電極を有する複数の受動素子と、前記基体の前記受動素子が配置された側とは反対の側に配置された能動素子と、を備え、前記シールド部材は、前記受動素子の両端の電極のうち一方の電極と対向する位置に開口部が形成された天井部と、前記受動素子の側方を覆う側壁部と、を備え、前記受動素子の一方の電極は、前記開口部に圧入された状態で前記シールド部材と接続されており、前記受動素子の他方の電極は、前記基体と接続されるとともに前記能動素子と電気的に接続されていることを特徴とする。

本発明に係る電子機器は、上記電子部品の実装構造を備えることを特徴とする。

本発明によれば、電子部品を高密度に配置するとともに装置全体の小型化を図ることが可能となる。

以下、図面を参照して、本発明の実施の形態について説明する。かかる実施の形態は、本発明の一態様を示すものであり、この発明を限定するものではなく、本発明の技術的思想の範囲内で任意に変更可能である。また、以下の図面においては、各構成をわかりやすくするために、実際の構造と各構造における縮尺や数等が異なっている。

(第1実施形態)

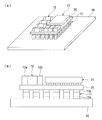

図1は、本発明の第1実施形態に係る電子部品の実装構造を示す図である。図1(a)は、本発明の第1実施形態に係る電子部品の実装構造を示す斜視図である。図1(b)は、本発明の第1実施形態に係る電子部品の実装構造を示す断面図である。

図1は、本発明の第1実施形態に係る電子部品の実装構造を示す図である。図1(a)は、本発明の第1実施形態に係る電子部品の実装構造を示す斜視図である。図1(b)は、本発明の第1実施形態に係る電子部品の実装構造を示す断面図である。

図1に示すように、本実施形態の電子部品の実装構造(電子機器)は、第1基体10と、第1基体10と対向して配置された第2基体20と、第1基体10と第2基体20の間に配置された、両端に電極11a,11bを有する複数の第1受動素子11と、第2基体20の第1受動素子11が配置された側とは反対の側に配置された能動素子21と、を備えた構造となっている。

ここでは、第1基体10及び第2基体20としてプリント回路基板等の電子基板を挙げて説明する。なお、第1基体10及び第2基体20には、電子部品を実装するためのランドが設けられている。また、「受動素子」(受動部品)とは、エネルギーを消費または蓄積する機能をもった電子部品である。受動素子としては、例えば、コンデンサ、コイル、抵抗が挙げられる。「能動素子」(能動部品)とは、エネルギーを発生したり供給したり、あるいは増幅したり変換したりする機能をもった電子部品である。能動素子としては、例えば、IC、トランジスタ、ダイオードが挙げられる。

第1受動素子11は、直方体形状をなし且つその長軸方向に沿う両端に電極11a,11bを有する。第1受動素子11の両端の電極11a,11bのうち一方の電極11aは、第1基体10と接続されている。他方の電極11bは、第2基体20と接続されるとともに能動素子21(裏面の端子)と電気的に接続されている。

複数の第1受動素子11の長軸方向の長さは、互いに同じ長さになっている。つまり、複数の第1受動素子11の両端の電極11a,11b間の距離は、互いに同じ大きさになっている。

第2基体20の能動素子21と対向する部分を除いた領域(第2基体20上の能動素子21が配置されていない領域)には、両端に電極12a,12bを有する複数の第2受動素子12が配置されている。第2受動素子12は、直方体形状をなし且つその長軸方向に沿う両端に電極12a,12bを有する。第2受動素子12の両端の電極12a,12bの双方は、第2基体20と接続されている。

(電子部品の実装構造の製造方法)

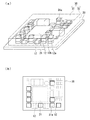

図2〜4は、本発明の第1実施形態に係る電子部品の実装構造(電子機器)の製造工程を示す図である。

図2〜4は、本発明の第1実施形態に係る電子部品の実装構造(電子機器)の製造工程を示す図である。

先ず、第2基体20のパッドの上に、例えばスクリーン印刷機等の装置を用いて、クリーム半田(半田の粉末にフラックスを加えて、適当な粘度にしたもの)を印刷する(図2(a)参照)。

次に、第2基体20のクリーム半田が印刷された領域に、例えばチップマウンター等の設備を用いて、能動素子21及び第2受動素子12を搭載する(図2(b)参照)。

次に、能動素子21及び第2受動素子12が搭載された第2基体20を適宜温度調整されたリフロー炉へ通し、リフロー半田付けを行う。これにより、能動素子21及び第2受動素子12と第2基体20とが接合される(図2(c)参照)。

次に、能動素子21及び第2受動素子12が接合された第2基体20を反転し、反転した第2基体20のパッドの上に、例えばスクリーン印刷機等の装置を用いて、クリーム半田を印刷する(図3(a)参照)。

次に、反転した第2基体20のクリーム半田が印刷された領域に、例えばチップマウンター等の設備を用いて、第1受動素子11を搭載する(図3(b)参照)。このとき、第1受動素子11の長軸方向は第2基体20の上面と直交する方向とする。また、複数の第1受動素子11の長軸方向の長さは、互いに同じ長さになっている。

次に、第1受動素子11が搭載された第2基体20を適宜温度調整されたリフロー炉へ通し、リフロー半田付けを行う。これにより、第1受動素子11(他方の電極11b)と第2基体20とが接合される(図3(c)参照)。

次に、第1基体10のパッドの上に、例えばスクリーン印刷機等の装置を用いて、クリーム半田を印刷する(図4(a)参照)。

次に、第1基体10のクリーム半田が印刷された領域に、例えばチップマウンター等の設備を用いて、第1受動素子11が搭載された第2基体20を搭載する(図4(b)参照)。

次に、第2基体20が搭載された第1基体10を適宜温度調整されたリフロー炉へ通し、リフロー半田付けを行う。これにより、第1受動素子11(一方の電極11a)と第2基体20とが接合される(図4(c)参照)。このようにして、第1基体10と第2基体20とが第1受動素子11を介して電気的、機械的に接続される。

なお、第1受動素子11の他方の電極11bは能動素子21(裏面の端子)と図示しない配線により電気的に接続される。本実施形態の電子部品の実装構造によれば、キャビティ基板を用いた構成に比べて、第1受動素子11と能動素子21との間に引き回される配線の長さを短くすることができる。このため、第1受動素子11と能動素子21との間で配線抵抗が増加することを抑制するとともにインダクタ成分の発生を抑えてノイズが生じることを抑制することができる。

以上の工程により、本実施形態に係る電子部品の実装構造を製造することができる。

本実施形態の電子部品の実装構造によれば、第2基体20の両側に電子部品が配置される(第2基体20の一方の側に第1受動素子11が配置されるとともに他方の側に能動素子21が配置される)ので、特許文献1に示すように複数のチップ部品を一枚の実装基板上のみに配置する構成に比べて、電子部品が三次元的に配置されることとなる。したがって、電子部品を高密度に配置するとともに装置全体の小型化を図ることが可能となる。

この構成によれば、第2基体20の能動素子21と対向する部分を除いた領域に第2受動素子12が配置されているので、第2基体の一方の側のみに受動素子が配置される構成に比べて、受動素子を高密度に配置することができる。

この構成によれば、第1受動素子11が直方体形状をなし且つその長軸方向に沿う両端に電極11a,11bを有するので、第1受動素子11は起立した状態で第1基体10と第2基体20の間に実装されることとなる。このため、受動素子が基体に平行に実装する構成に比べて、第1受動素子11を起立状態に実装した分だけ実装密度を高めることができる。

この構成によれば、複数の第1受動素子11の長軸方向の長さは、互いに同じ長さになっているので、第1基体10と第2基体20の間の距離が一定となる。このため、複数の第1受動素子の長軸方向の長さが互いに異なっている構成に比べて、第1受動素子11を第1基体10と第2基体20の間に安定して実装することができる。

本実施形態の電子機器によれば、上述した電子部品の実装構造を備えているので、電子部品を高密度に配置するとともに装置全体の小型化を図ることが可能となる。

(第2実施形態)

図5は、図1に対応した、本発明の第2実施形態に係る電子部品の実装構造を示す図である。図5(a)は、本発明の第1実施形態に係る電子部品の実装構造を示す斜視図である。図5(b)は、本発明の第1実施形態に係る電子部品の実装構造を示す断面図である。図5に示すように、本実施形態の電子部品の実装構造は、第2基体20の第1基体10(図示略)と対向する側と反対の側に導電性のシールド部材30が配置されている点で、上述の第1実施形態で説明した電子部品の実装構造と異なっている。その他の点は第1実施形態と同様であるので、図1と同様の要素には同一の符号を付し、詳細な説明は省略する。なお、図5においては、便宜上、第1基体10及び第1基体10と第2基体20の間に配置された第1受動素子11の図示を省略している。

図5は、図1に対応した、本発明の第2実施形態に係る電子部品の実装構造を示す図である。図5(a)は、本発明の第1実施形態に係る電子部品の実装構造を示す斜視図である。図5(b)は、本発明の第1実施形態に係る電子部品の実装構造を示す断面図である。図5に示すように、本実施形態の電子部品の実装構造は、第2基体20の第1基体10(図示略)と対向する側と反対の側に導電性のシールド部材30が配置されている点で、上述の第1実施形態で説明した電子部品の実装構造と異なっている。その他の点は第1実施形態と同様であるので、図1と同様の要素には同一の符号を付し、詳細な説明は省略する。なお、図5においては、便宜上、第1基体10及び第1基体10と第2基体20の間に配置された第1受動素子11の図示を省略している。

図5に示すように、第2基体20の第1基体10(図示略)と対向する側と反対の側に導電性のシールド部材30が配置されている。第2基体20とシールド部材30の間には、両端に電極12a,12bを有する複数の第2受動素子12及び能動素子21が配置されている。第2受動素子12は、直方体形状をなし且つその長軸方向に沿う両端に電極12a,12bを有する。第2受動素子12の両端の電極12a,12bのうち一方の電極12aは、シールド部材30と接続されている。他方の電極12bは、第2基体20と接続されている。

例えば、シールド部材30にグラウンド電位をもたせ、第2受動素子12としてバイパスコンデンサ(電子回路において回路が動作する際に直流電源電圧が変動することを回避するために、電源ラインとグラウンドとを接続するコンデンサ)を用いることができる。

シールド部材30は、第2受動素子12の一方の電極12aと接続される天井部31と、第2受動素子12の側方を覆う側壁部32と、を備えている。シールド部材30の天井部31には、第2受動素子12の一方の電極12aと対向する位置に開口部31aが形成されている。第2受動素子12の一方の電極12aは、開口部31aに圧入された状態でシールド部材30と接続されている。

(電子部品の実装構造の製造方法)

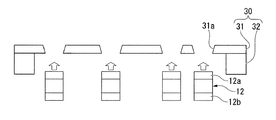

図6は、本発明の第2実施形態に係る電子部品の実装構造(電子機器)の製造工程を示す図である。なお、図6においては、便宜上、第2基体20上に配置された第2受動素子12以外の部品の図示を省略している。また、第1受動素子11(一方の電極11a)と第2基体20とを接合する工程まで(図2〜図4参照)は、上述した第1実施形態に係る電子部品の実装構造の製造工程と同様であるため、その詳細な説明は省略する。

図6は、本発明の第2実施形態に係る電子部品の実装構造(電子機器)の製造工程を示す図である。なお、図6においては、便宜上、第2基体20上に配置された第2受動素子12以外の部品の図示を省略している。また、第1受動素子11(一方の電極11a)と第2基体20とを接合する工程まで(図2〜図4参照)は、上述した第1実施形態に係る電子部品の実装構造の製造工程と同様であるため、その詳細な説明は省略する。

図6に示すように、シールド部材30の天井部31には、第2受動素子12の一方の電極12aを挿通するための開口部31aが形成されている。複数の第2受動素子12の長軸方向の長さは、互いに同じ長さになっている。複数の第2受動素子12とシールド部材30との接続は、複数の第2受動素子12を開口部31aに圧入することにより行う。

開口部31aは、一方の電極12aの導入側(下側)の開口径が一方の電極12aの導出側(上側)の開口径よりも小さくなるように形成されている。このため、開口部31aの導入側(下側)から第2受動素子12(一方の電極12a)を圧入すると、開口部31aの下部が先鋭形状となっているため、一方の電極12aの表面の酸化膜が削られる。これにより、第2受動素子12とシールド部材30とが電気的に接続される。

以上の工程により、本実施形態に係る電子部品の実装構造を製造することができる。

本実施形態の電子部品の実装構造によれば、シールド部材30の開口部31aに第2受動素子12が圧入された状態で接続されるので、隣接する第2受動素子12どうしのショートを抑制することが可能となる。

なお、本実施形態においては、第2基体20とシールド部材30の間に、複数の第2受動素子12及び能動素子21が配置されているが、これに限らない。例えば、第2基体とシールド部材の間に複数の第2受動素子のみが配置された構成であってもよい。

(第3実施形態)

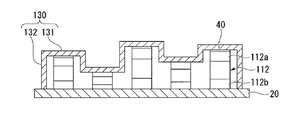

図7は、図5に対応した、本発明の第3実施形態に係る電子部品の実装構造を示す断面図である。図7に示すように、本実施形態の電子部品の実装構造は、受動素子112の一方の電極112aがシールド部材130の天井部131と導電部材40を介して接続されている点、第2基体20とシールド部材130の間に互いに異なる高さの受動素子112が配置されている点、で上述の第2実施形態で説明した電子部品の実装構造と異なっている。その他の点は第2実施形態と同様であるので、図2と同様の要素には同一の符号を付し、詳細な説明は省略する。なお、図7においては、便宜上、第1基体10及び第1基体10と第2基体20の間に配置された第1受動素子11の図示を省略している。

図7は、図5に対応した、本発明の第3実施形態に係る電子部品の実装構造を示す断面図である。図7に示すように、本実施形態の電子部品の実装構造は、受動素子112の一方の電極112aがシールド部材130の天井部131と導電部材40を介して接続されている点、第2基体20とシールド部材130の間に互いに異なる高さの受動素子112が配置されている点、で上述の第2実施形態で説明した電子部品の実装構造と異なっている。その他の点は第2実施形態と同様であるので、図2と同様の要素には同一の符号を付し、詳細な説明は省略する。なお、図7においては、便宜上、第1基体10及び第1基体10と第2基体20の間に配置された第1受動素子11の図示を省略している。

図7に示すように、受動素子112の一方の電極112aがシールド部材130と導電部材40を介して接続されている。例えば、導電部材40としては、異方性導電フィルム(ACF:anisotropic conductive film)や異方性導電ペースト(ACP:anisotropic conductive paste)を用いることができる。この場合、シールド部材130の天井部131に開口部を形成する必要はなく、ACFやACPを介して受動素子112(一方の電極112a)とシールド部材130(天井部131)とを熱圧着させることによって受動素子112とシールド部材130とが電気的、機械的に接続されることとなる。

天井部131と側壁部132と第2基体20とに囲まれる空間には、相対的に長軸方向の長さの長い受動素子112(第3受動素子)と、相対的に長軸方向の長さの短い受動素子112(第4受動素子)と、が配置されている。第3受動素子112と対向する天井部131の第2基体20からの高さは、第4受動素子112と対向する天井部131の第2基体20からの高さよりも高くなっている。

本実施形態の電子部品の実装構造によれば、受動素子112の高さが互いに異なる場合であっても、各受動素子112とシールド部材130とを安定して接続することが可能となる。

なお、本実施形態においては、導電部材としてACFやACPを用いる構成を例に挙げて説明したが、これに限らない。例えば、導電部材としては、半田を用いることもできる。この場合、シールド部材の天井部に開口部を形成する必要はなく、天井部に半田めっきを施し、半田めっきを施した部分に受動素子を搭載してリフロー炉へ通すことによって受動素子とシールド部材とが電気的、機械的に接続されることとなる。

10…第1基体、11…第1受動素子、11a…一方の電極、11b…他方の電極、20…第2基体、21…能動素子、30,130…シールド部材、31,131…天井部、31a…開口部、32,132…側壁部、40…導電部材、112…第3受動素子、第4受動素子

Claims (10)

- 第1基体と、前記第1基体と対向して配置された第2基体と、前記第1基体と前記第2基体の間に配置された、両端に電極を有する複数の第1受動素子と、前記第2基体の前記第1受動素子が配置された側とは反対の側に配置された能動素子と、を備え、

前記第1受動素子の両端の電極のうち一方の電極は、前記第1基体と接続されており、

他方の電極は、前記第2基体と接続されるとともに前記能動素子と電気的に接続されていることを特徴とする電子部品の実装構造。 - 前記第2基体の少なくとも前記能動素子と対向する部分を除いた領域には、両端に電極を有する複数の第2受動素子が配置されていることを特徴とする請求項1に記載の電子部品の実装構造。

- 前記第1受動素子は、直方体形状をなし且つその長軸方向に沿う両端に前記電極を有することを特徴とする請求項1または2に記載の電子部品の実装構造。

- 前記複数の第1受動素子の長軸方向の長さは、互いに同じ長さになっていることを特徴とする請求項3に記載の電子部品の実装構造。

- 前記第2基体の前記第1基体と対向する側とは反対の側には導電性のシールド部材が配置され、

前記シールド部材は、

前記第2受動素子の一方の電極と接続される天井部と、

前記第2受動素子の側方を覆う側壁部と、

を備えていることを特徴とする請求項2に記載の電子部品の実装構造。 - 前記シールド部材の前記天井部には、前記第2受動素子の一方の電極と対向する位置に開口部が形成されており、

前記第2受動素子の一方の電極は、前記開口部に圧入された状態で前記シールド部材と接続されていることを特徴とする請求項5に記載の電子部品の実装構造。 - 前記第2受動素子の一方の電極は、前記シールド部材と導電部材を介して接続されていることを特徴とする請求項5に記載の電子部品の実装構造。

- 前記天井部と前記側壁部と前記第2基体とにより囲まれた空間に、相対的に長軸方向の長さの長い第3受動素子と、相対的に長軸方向の長さの短い第4受動素子と、が配置されており、

前記第3受動素子と対向する前記天井部の前記第2基体からの高さは、前記第4受動素子と対向する前記天井部の前記第2基体からの高さよりも高いことを特徴とする請求項5〜7のいずれか1項に記載の電子部品の実装構造。 - 基体と、前記基体と対向して配置された導電性のシールド部材と、前記基体と前記シールド部材の間に配置された、両端に電極を有する複数の受動素子と、前記基体の前記受動素子が配置された側とは反対の側に配置された能動素子と、を備え、

前記シールド部材は、前記受動素子の両端の電極のうち一方の電極と対向する位置に開口部が形成された天井部と、前記受動素子の側方を覆う側壁部と、を備え、

前記受動素子の一方の電極は、前記開口部に圧入された状態で前記シールド部材と接続されており、

前記受動素子の他方の電極は、前記基体と接続されるとともに前記能動素子と電気的に接続されていることを特徴とする電子部品の実装構造。 - 請求項1〜9のいずれか1項に記載の電子部品の実装構造を備えることを特徴とする電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010228350A JP2012084635A (ja) | 2010-10-08 | 2010-10-08 | 電子部品の実装構造及び電子機器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010228350A JP2012084635A (ja) | 2010-10-08 | 2010-10-08 | 電子部品の実装構造及び電子機器 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012084635A true JP2012084635A (ja) | 2012-04-26 |

Family

ID=46243227

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010228350A Pending JP2012084635A (ja) | 2010-10-08 | 2010-10-08 | 電子部品の実装構造及び電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012084635A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018029921A1 (ja) * | 2016-08-09 | 2018-02-15 | 株式会社村田製作所 | 半導体パッケージ、及び、配線基板 |

-

2010

- 2010-10-08 JP JP2010228350A patent/JP2012084635A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018029921A1 (ja) * | 2016-08-09 | 2018-02-15 | 株式会社村田製作所 | 半導体パッケージ、及び、配線基板 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100616384B1 (ko) | 수직 접속된 캐패시터를 구비하는 전자 어셈블리 및 제조방법 | |

| US8064211B2 (en) | Passive component and electronic component module | |

| US10109576B2 (en) | Capacitor mounting structure | |

| JP2010129877A (ja) | 電子部品モジュール | |

| US8806420B2 (en) | In-grid on-device decoupling for BGA | |

| JP5920634B2 (ja) | プリント基板 | |

| CN108307584A (zh) | 元器件模块 | |

| JP5169800B2 (ja) | 電子装置 | |

| JP6121926B2 (ja) | 半導体装置及びそれを用いた電子機器 | |

| JP2002009229A (ja) | 半導体装置 | |

| JP2013065887A (ja) | 電子装置 | |

| JP2012084635A (ja) | 電子部品の実装構造及び電子機器 | |

| JP4952365B2 (ja) | 両面実装回路基板に対する電子部品の実装構造、半導体装置、及び両面実装半導体装置の製造方法 | |

| JP2010045090A (ja) | Icチップ上への電子部品の実装 | |

| JP6587795B2 (ja) | 回路モジュール | |

| JP5626892B2 (ja) | 3次元実装型半導体装置、および電子機器 | |

| JP2011155199A (ja) | 回路実装基板 | |

| CN111199934B (zh) | 电路装置与电路设计及组装方法 | |

| JP6264721B2 (ja) | 多層配線基板の放熱構造 | |

| US20200152559A1 (en) | Device conducive to reduction of parasitic inductance and method for circuit design and assembly | |

| CN102969292B (zh) | 集成电源模块 | |

| JP2008112941A (ja) | 電子部品モジュール | |

| CN115812241A (zh) | 焊料柱栅格阵列电容器 | |

| JP4950581B2 (ja) | 回路モジュール | |

| JP4985852B2 (ja) | 実装型電子回路モジュール |